# Diseño y evaluación de sistemas de interconexión basados en tecnología óptica integrada en silicio

Juan-Jose Crespo<sup>1</sup>, Francisco J. Alfaro-Cortés<sup>1</sup> y José L. Sánchez<sup>1</sup>

Resumen—Aumentar el número de nodos de cómputo para llegar a sistemas exascale conlleva resolver diversos problemas si se quieren obtener sistemas eficientes en términos de coste económico, consumo de energía y rendimiento. En este tipo de sistemas de computación, el movimiento de datos entre nodos afecta negativamente al rendimiento, y por tanto la red de interconexión se convierte en un elemento clave. Entre las diferentes tecnologías que puede contribuir a mejorar la eficiencia de las comunicaciones, la óptica es una de las más adecuadas por su capacidad para generar, transmitir y recibir señales a un gran ancho de banda y una mayor eficiencia energética. Sin embargo, la comunicación óptica no permite almacenamiento, por lo que las redes construidas usando esta tecnología se implementan usando conmutación de circuitos. Es por ello que se necesitan nuevas arquitecturas de red capaces de satisfacer los requisitos de comunicación entre nodos y los diferentes recursos de cómputo presentes en cada uno de esos nodos multiprocesador. Este trabajo muestra la facilidad del simulador PhotoNoCs para diseñar y evaluar nuevas propuestas de sistemas exascale que implementen sistemas de interconexión ópticos a diferentes niveles de abstracción: Redes on-chip para arquitecturas multiprocesador y redes off-chip para la evaluación del sistema completo.

Palabras clave— Óptica integrada en silicio, Redes on-chip, Sistemas exascale.

#### I. Introducción

El progreso alcanzado en diferentes áreas científicas como energía, biotecnología, clima e investigación aeroespacial, depende de la realización de simulaciones complejas y costosas. La única opción viable para realizar este tipo de trabajo es el uso de supercomputadores, por ello existe un gran interés en la comunidad científica de mejorar las prestaciones de estos sistemas. De hecho, el principal objetivo actualmente es el diseño de sistemas exascale, para los cuales es necesario incrementar significativamente la cantidad de nodos de cómputo. Esto pone de manifiesto numerosos retos que deben resolverse para obtener sistemas eficientes en términos de coste, consumo energético y rendimiento. Algunos de estos retos son: software escalable, tolerancia a fallos y recuperación, nuevos paradigmas de programación, eficiencia energética y propuestas usando diferentes tecnologías de interconexión.

El incremento en el nivel de paralelización de las aplicaciones hace que el rendimiento del sistema esté determinado en gran parte por la comunicación gene-

<sup>1</sup>Grupo de Redes y Arquitecturas de Altas Prestaciones (RAAP), Univ. de Castilla-La Mancha, Web: http://www.i3a.uclm.es/raap, email: jjgcc@dsi.uclm.es, {fco.alfaro, jose.sgarcia}@uclm.es

rada en la ejecución de dichas aplicaciones paralelas. La transferencia de datos existe a diferentes niveles: entre nodos de cómputo y almacenamiento, entre los propios nodos de cómputo, y entre múltiples recursos dentro de cada nodo multiprocesador. Debido a lo cual, el movimiento de datos entre nodos afecta negativamente al rendimiento, y su impacto es mayor en sistemas exascale, por lo que la red de interconexión es uno de los componentes clave en estos sistemas.

La evolución hacia sistemas exascale no puede lograrse adoptando una estrategia incremental, son necesarios cambios cualitativos en el diseño de los sistemas actuales. En el ámbito de la red de interconexión, existen diferentes tecnologías que posibilitan la consecución de este objetivo. La tecnología óptica es una de las más adecuadas por su capacidad para generar, transmitir y recibir señales a un gran ancho de banda y una mayor eficiencia energética.

A lo largo de la última década se ha logrado un gran progreso en la integración de dispositivos ópticos en silicio [1], [2], y [3]. Sin embargo, debido al funcionamiento de los dispositivos ópticos, se requieren nuevos diseños de redes de interconexión (on-chip y off-chip) capaces de aprovechar las ventajas que ofrecen dichos dispositivos. No obstante, adentrarse en este paradigma requiere aportar soluciones a los retos que plantea, por ejemplo, las señales transmitidas a través del medio óptico no pueden ser almacenadas ni procesadas sin convertirlas antes al medio eléctrico.

En este trabajo, presentamos *PhotoNoCs* [4] como una herramienta de diseño capaz de abordar el problema a diferentes niveles, desde redes on-chip, hasta redes off-chip y diseño de switches, basándose en la tecnología óptica integrada en silicio. Además, hemos llevado a cabo la evaluación de un diseño de switch usando *PhotoNoCs* para demostrar su funcionamiento y nuevas características respecto a versiones anteriores.

La estructura del artículo es la siguiente: la sección II ofrece una visión global de la herramienta de simulación *PhotoNoCs* y sus características principales. También proporciona los conceptos necesarios para comprender el funcionamiento de un dispositivo óptico básico, y su uso para la construcción de otros más complejos. La sección III revisa algunas propuestas recientes de switches basados en anillos resonadores, una de las cuales es evaluada en la sección IV usando *PhotoNoCs*. Finalmente se presentan las conclusiones en la sección V.

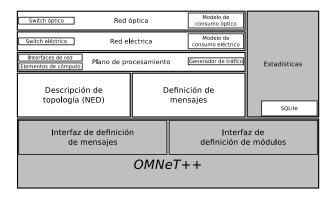

Fig. 1: Diseño de PhotoNoCs.

#### II. HERRAMIENTA PHOTONOCS

El desarrollo de PhotoNoCs se ha llevado a cabo usando  $OMNeT++\ v5.0$ , el cual es un framework de simulación extensible basado en componentes y escrito en el lenguaje de programación C++. Debido a los requisitos de la herramienta PhotoNoCs: reutilización de los modelos, arquitectura modular, y rendimiento escalable entre otros, es lo que ha determinado la elección del framework OMNeT++ para su construcción.

Tal y como muestra la figura 1, PhotoNoCs está compuesto por diferentes bloques, cada uno centrado en un aspecto diferente de la herramienta. Los bloques sombreados se refieren a funcionalidad proporcionada por el framework OMNeT++.

# A. Características principales

Cada bloque mostrado en la figura 1 proporciona nueva funcionalidad a la herramienta. A continuación se describen solamente aquellas características proporcionadas por *PhotoNoCs* que se han usado para este trabajo:

- Red óptica: PhotoNoCs tiene implementados modelos de componentes ópticos, la mayoría de ellos están basados en los modelados por el proyecto PhoenixSim [5]. Utilizando los modelos, es posible estudiar diferentes diseños de switch basados en estos componentes y realizar simulaciones. Al finalizar la simulación, PhotoNoCs ofrece un informe detallado con las métricas descritas en la sección II-C.

- 2. Red eléctrica: Buffers, unidades de arbitraje, crossbars, etc. Son algunos de los componentes de los que la herramienta dispone. Dichos módulos están diseñados para comunicarse entre ellos y diseñar componentes más complejos basados en éstos.

- 3. Plano de procesamiento: Procesadores e interfaces de red también están incluidos en la herramienta. Los procesadores son los encargados de la generación de los mensajes, dicha generación puede derivarse de trazas o tráfico sintético. Las interfaces de red están diseñadas para soportar la comunicación a través del medio eléctrico y óptico presentes en el mismo sistema. En caso de disponer de ambos medios por los que

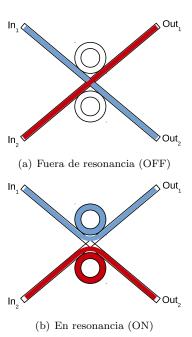

Fig. 2: Switch  $2\times 2$  basado en anillos resonadores.

transmitir un paquete, es necesario configurar una política de selección de red (la herramienta dispone de varias políticas de selección).

4. Descripción de topologías: Debido a la estructura modular de la herramienta, cada módulo, sea un switch óptico o cualquier otro, puede conectarse usando los esqueletos de conexión proporcionados con la herramienta. Así, el programador puede configurar cualquier topología usando el lenguaje de definición Network Description (NED) proporcionado por OMNeT++.

# B. Componente básico: Switch 2×2 basado en anillos resonadores

Esta sección incluye las características del componente básico utilizado en este trabajo. Dicho componente consiste en un switch  $2\times2$  basado en anillos resonadores modelado en la herramienta PhotoNoCs. Se trata del componente en el que se basan otros más complejos.

El diseño del switch se muestra en la figura 2. Está compuesto de dos anillos resonadores y dos guías ópticas que se cruzan en el centro.

Cuando los anillos se encuentran en resonancia (ON) con una longitud de onda determinada, dicha longitud de onda se modula en la guía óptica que intersecta con la guía de origen de dicha longitud de onda. Como se muestra en la figura 2(b), la señal introducida por el puerto  $In_1$  se propaga por la guía óptica que intersecta saliendo por el puerto  $Out_1$ .

#### C. Métricas de rendimiento

Esta sección describe las métricas de rendimiento y atenuación de señal comúnmente utilizadas para la evaluación de diseños utilizando tecnología óptica integrada en silicio. *PhotoNoCs* calcula los valores de dichas métricas e incluye los resultados en el informe final para cada una de ellas. El cálculo de unas

métricas u otras depende de las propiedades físicas de los componentes simulados.

- Insertion loss (IL): Se trata de la atenuación producidas en una señal durante su recorrido, también denominado pérdida por propagación. En las transmisiones realizadas utilizando el medio óptico, la señal transmitida no puede ser regenerada ya que requeriría de amplificadores ópticos integrados en silicio, los cuales son costosos y tienen un impacto negativo en la eficiencia energética. Debido a lo anterior, la pérdida por propagación debe minimizarse todo lo posible. Por tanto, se deduce que la complejidad y el tamaño de una red que haga uso de tecnología óptica, se encuentra limitada por la pérdida de propagación ya que un enlace óptico puede tolerar un máximo de atenuación de señal hasta que la potencia de ésta sea demasiado baja para detectarse en el receptor.

- Optical loss budget: Esta métrica representa la diferencia entre la potencia máxima inyectable por la fuente óptica (láser), y la potencia mínima detectable en el receptor. La potencia máxima que puede ser inyectada en una guía óptica está limitada por el umbral a partir del cual se produce una atenuación no lineal en componentes ópticos integrados en silicio. Dicha atenuación afecta a la integridad de la señal cuando la potencia de ésta es demasiado elevada.

Una técnica utilizada en este tipo de comunicaciones es Wavelength Division Multiplexing (WDM) [6], ya que permite la modulación simultánea de múltiples longitudes de onda, lo que hace posible la transmisión de datos en paralelo. Sin embargo, la potencia total (la suma de la potencia de cada señal modulada) debe mantenerse por debajo del umbral en el que se observan efectos no lineales.

La inecuación 1 se usa para calcular el optical loss budget, donde P representa la potencia entregada por el láser o la fuente de señal, S es la sensibilidad del fotodetector,  $IL_{max}$  representa el peor caso posible, donde la pérdida por inserción es mayor, y n indica la cantidad de longitudes de onda utilizadas usando la técnica WDM.

$$P - S \ge IL_{max} + 10\log_{10}(n) \tag{1}$$

■ Crosstalk: Es la derivación de una pequeña porción de la potencia de una señal a otras señales en guías ópticas que intersecten con la primera durante su recorrido. Dada una intersección entre guías ópticas, aquellas señales transmitidas en diferentes guías, derivarán una pequeña porción de intensidad a las otras guías. Este efecto también ocurre en los switches basados en anillos resonadores debido a imperfecciones en el acoplamiento de las guías y los anillos. Si un dispositivo tiene N puertos desde los que una señal puede ser inyectada o eyectada, entonces dicha señal puede sufrir un acoplamiento de señal residual de los N − 1 puertos restantes,

siempre y cuando haya señales presentes en dichos puertos. Sea M el conjunto de señales presentes en el dispositivo, y  $P_k$  la potencia de la señal k, entonces el cálculo de la métrica crosstalk sobre la señal s viene dada por la ecuación 2.

$$C_s = \sum_{k \in M, k \neq s} \frac{P_k}{IL(p_{k.in}, p_{s.out})}$$

(2)

La función  $IL(p_{k.in}, p_{s.out})$  calcula la pérdida por inserción (porción de la potencia original de la señal) entre un par de puertos del dispositivo.  $p_{k.in}$  representa el puerto de entrada de cualquier señal distinta de s, y  $p_{s.out}$  es el puerto de salida de la señal s.

## III. SWITCHES BASADOS EN ANILLOS RESONADORES

Esta sección revisa las propuestas más recientes de diseños de switches basados en anillos resonadores para redes de interconexión ópticas en sistemas multiprocesador.

El estudio de dispositivos ópticos basados en anillos resonadores como son filtros y switches, diseñados para permitir transmisiones *Multiple-Input Multiple-Output (MIMO)*, ha sido objeto de interés científico durante mucho tiempo. Existen propuestas de diseños de este tipo de estructuras en diferentes materiales incluyendo silicio [7], [8], [9], [10], [11], [12], [13], [14].

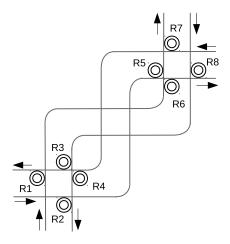

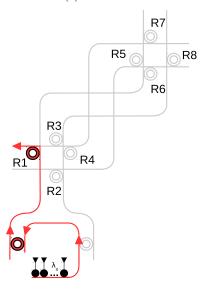

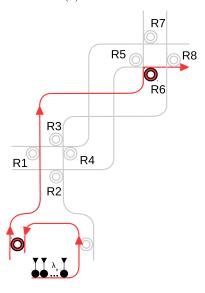

Para demostrar las características de *PhotoNoCs*, se ha escogido un diseño de switch, como el que se muestra en la figura 3. Para este trabajo, solamente se han revisado diseños integrados en *silicon-on-insulator (SOI)*.

## A. Optical hitless switch

El diseño del switch mostrado en la figura 3, propuesto en [13] (optical hitless switch), es un switch óptico  $4\times4$  no bloqueante para uso en redes ópticas integradas en silicio.

El encaminamiento se lleva a cabo utilizando una guía óptica para cada combinación de puertos entrada/salida. Cabe destacar que las señales no pueden ser encaminadas por el mismo puerto de salida que de entrada, ni tampoco en una dirección que esté siendo usada por otra señal.

Debido a lo indicado en el párrafo anterior, la conmutación de múltiples señales a través del switch debe llevarse a cabo tal que una señal s que requiera el puerto de salida o, no debe haber otra señal r que requiera el mismo puerto de salida o.

En la tabla I se muestra la configuración de los anillos resonadores requerida para permitir la comunicación entre cada par de puertos E/S. Por otro lado, existen 9 posibles combinaciones de puertos E/S que no interfieren en las guías ópticas que utilizan (o tramos de éstas). Dichas combinaciones se muestran en la tabla II.

Fig. 3: Diseño switch no bloqueante.

TABLA I: Configuración de anillos para caminos físicos entre cada combinación de puertos E/S.

|        |              | Entrada |              |              |              |  |  |

|--------|--------------|---------|--------------|--------------|--------------|--|--|

|        |              | N       | $\mathbf{S}$ | $\mathbf{E}$ | $\mathbf{W}$ |  |  |

| Salida | $\mathbf{N}$ | -       | none         | R7           | R5           |  |  |

|        | $\mathbf{S}$ | none    | -            | R4           | R2           |  |  |

|        | ${f E}$      | R8      | R6           | -            | none         |  |  |

|        | W            | R3      | R1           | none         | -            |  |  |

TABLA II: Combinaciones de puertos de  $\mathrm{E}/\mathrm{S}$  sin solapamientos.

|               |   | Entrada      |              |              |              |                |

|---------------|---|--------------|--------------|--------------|--------------|----------------|

|               |   | N            | $\mathbf{S}$ | $\mathbf{E}$ | $\mathbf{W}$ | Anillos Usados |

| Configuración | 1 | W            | N            | S            | Е            | R3, R4         |

|               | 2 | W            | E            | N            | S            | R3, R6, R7, R2 |

|               | 3 | W            | E            | $\mathbf{S}$ | N            | R3, R6, R4, R5 |

|               | 4 | $\mathbf{S}$ | N            | W            | $\mathbf{E}$ | none           |

| nfig          | 5 | $\mathbf{S}$ | W            | N            | $\mathbf{E}$ | R1, R7         |

| $C_0$         | 6 | $\mathbf{S}$ | E            | W            | N            | R6, R5         |

|               | 7 | E            | W            | $\mathbf{S}$ | N            | R8, R1, R4, R5 |

|               | 8 | E            | W            | N            | S            | R8, R1, R7, R2 |

|               | 9 | Е            | N            | W            | S            | R8, R2         |

# IV. EVALUACIÓN

Esta sección detalla el estudio llevado a cabo para evaluar el rendimiento del switch mostrado en la sección III-A así como las características de la herramienta PhotoNoCs.

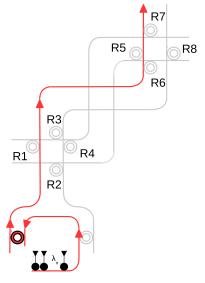

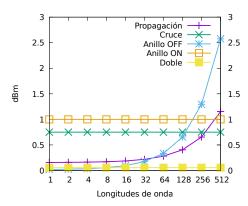

En la figura 4 se muestran las diferentes configuraciones del switch. Como se puede observar, el modulador está localizado en el puerto sur del switch, y es el encargado de modular múltiples longitudes de onda  $\lambda_n$  en la guía óptica de dicho puerto. Los parámetros utilizados para caracterizar las propiedades físicas de los componentes ópticos y fuentes de pérdida de señal se encuentran en las tablas III y IV.

El diseño del switch se ha evaluado utilizando tres escenarios diferentes dependiendo del puerto de sali-

(a) Sur a Norte.

(b) Sur a Oeste.

(c) Sur a Este.

Fig. 4: Configuraciones del switch: (a) Configuración de Sur a Norte; (b) Configuración de Sur a Oeste; y (c) Configuración de Sur a Este.

TABLA III: Propiedades de los componentes ópticos.

| Propiedad                            | Valor             |

|--------------------------------------|-------------------|

| Potencia de láser                    | $10 \mathrm{dBm}$ |

| Diámetro anillos modulador           | $3\mathrm{um}$    |

| Diámetro anillos switch $2 \times 2$ | 50um              |

TABLA IV: Caracterización de los tipos de pérdidas.

| Tipo de pérdida               | Valor               |

|-------------------------------|---------------------|

| Propagación                   | $1.5*10^{-4} dB/um$ |

| Anillo fuera resonancia (OFF) | $5.0 * 10^{-3} dB$  |

| Anillo en resonancia (ON)     | 0.5 dB              |

| Cruce (90°)                   | 0,15dB              |

| Doble                         | $5.0 * 10^{-3} dB$  |

da elegido. El diseño mostrado en la figura 4 tiene el modulador conectado en el puerto de E/S sur. Esto, como se ha dicho, permite probar tres configuraciones diferentes:

- 1. **S-N**: Transmisión de datos desde el puerto Sur al Norte (figura 4(a)).

- 2. **S-O**: Transmisión de datos desde el puerto Sur al Oeste (figura 4(b)).

- 3. **S-E**: Transmisión de datos desde el puerto Sur al Este (figura 4(c)).

Los escenarios anteriores son suficientes para caracterizar el diseño planteado. Debido a que el diseño es simétrico, todas las configuraciones entre cualquier par de puertos E/S se encuentran representadas.

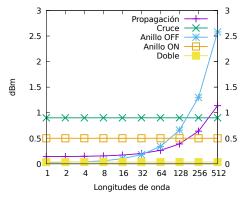

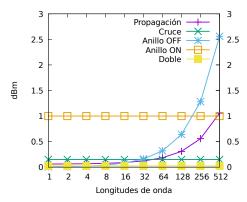

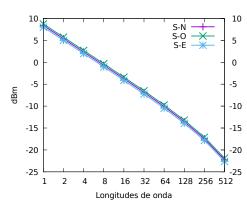

El rendimiento del diseño del switch en términos de atenuación y pérdida de señal se muestra en la figura 5. Los resultados son similares para todas las configuraciones (figuras 5(a), 5(b) y 5(c)). Se observa que la pérdida de señal debido a su paso a través de anillos resonadores fuera de resonancia desarrolla un incremento exponencial con el aumento en la cantidad de longitudes de onda utilizadas. Otras fuentes de pérdida de señal como cruces entre guías ópticas, dobles y el paso a través de anillos en resonancia no dependen de la cantidad de longitudes de onda, lo cual se debe al uso de anillos broadband en el diseño.

El aumento en la pérdida de señal por el paso a través de anillos fuera de resonancia y el aumento en la pérdida por propagación a medida que aumenta la cantidad de longitudes de onda, es debido al modulador. Los anillos resonadores utilizados en el modulador tienen una frecuencia de resonancia fija establecida en el momento de su integración en silicio (denominados narrowband). Debido a lo anterior, son necesarios tantos anillos en el modulador como longitudes de onda se permita utilizar en el diseño, por lo que a medida que aumenta el número de longitudes de onda utilizadas, aumenta también la cantidad de anillos resonadores necesarios en el modulador, y en consecuencia, aumenta la pérdida de señal debido al paso de las señales por anillos fuera de resonancia.

Por otro lado, debido al incremento en la cantidad

(a) Pérdida señal Sur a Norte.

(b) Pérdida señal Sur a Oeste.

(c) Pérdida señal Sur a Este.

(d) Potencia de señal previa al detector.

Fig. 5: Rendimiento y pérdida de señal del diseño del switch conforme aumenta la cantidad de longitudes de onda utilizadas: (a) Pérdida señal Sur a Norte; (b) Pérdida señal Sur a Oeste; (c) Pérdida señal Sur a Este; y (d) Potencia de señal previa al detector para cada configuración.

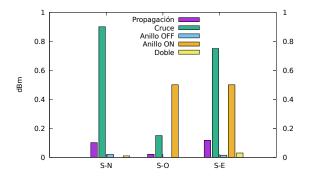

Fig. 6: Fuentes de pérdida de señal para cada configuración del switch.

de anillos necesarios en el modulador, la longitud física de las guías ópticas necesarias para propagar las señales a través de estos anillos también aumenta.

La figura 5(d) muestra que no es posible la transmisión de datos utilizando más de 128 longitudes de onda, si consideramos una sensibilidad del fotodetector de 13,1dBm como se explica en [15].

Finalmente, la figura 6 muestra en detalle cada una de las fuentes de pérdida de señal para cada configuración del switch. Destaca la pérdida de señal debido a cruces entre guías ópticas, especialmente cuando se trata de ir desde un puerto del switch al puerto opuesto como es el caso del escenario S-N (figura 5(a)), también contribuye en gran medida la pérdida por cruces en el escenario S-E (figura 5(c)).

Concluimos que la pérdida de señal debida al modulador como se muestra en las figuras 5(a), 5(b) y 5(c), así como la pérdida de señal debido al cruce entre guías y dobles, como se muestra en la figura 6, son las principales fuentes de pérdida de señal para este diseño de switch.

#### V. Conclusiones

Este trabajo presenta una caracterización detallada de un diseño de switch óptico usando la herramienta PhotoNoCs, un simulador por eventos discretos escrito en C++ usando el framework OMNeT++.

En primer lugar, se ha revisado la herramienta de simulación así como la descripción de sus componentes, mostrando cómo *PhotoNoCs* permite el estudio de redes *on-chip*. Sin embargo, *PhotoNoCs* no se limita a redes *on-chip*, también posibilita el estudio detallado de diseños que utilizan tecnologías emergentes como es el caso de la tecnología óptica. Así, se puede llevar a cabo el estudio y diseño de diferentes dispositivos (como switches) para ser usados en redes *on-chip* y *off-chip*.

Los resultados muestran que *PhotoNoCs* es capaz de simular mecanismos de comunicación con un alto grado de detalle gracias al nivel de precisión de los componentes junto a la flexibilidad de la configuración y su diseño modular. Estas características hacen de *PhotoNoCs* una herramienta de diseño efectiva en el estudio del diseño de sistemas multiprocesador hacia la era *exascale*.

## AGRADECIMIENTOS

El presente trabajo ha sido financiado mediante el proyecto CICYT TIN2015-66972-C5-2-R; y por la JCCM mediante el proyecto PEII-2014-028-P. Juan-Jose Crespo ha sido financiado por el MECD a través de la beca FPU FPU15/03627.

#### Referencias

- [1] Michael R Watts, Douglas C Trotter, Ralph W Young, and Anthony L Lentine, "Ultralow power silicon microdisk modulators and switches," in *Group IV Photonics*, 2008 5th IEEE International Conference, 2008, pp. 4–6.

- [2] Qianfan Xu, Sasikanth Manipatruni, Brad Schmidt, Jagat Shakya, and Michal Lipson, "12.5 gbit/s carrier-injection-based silicon micro-ring silicon modulators," Optics express, vol. 15, no. 2, pp. 430–436, 2007.

- [3] Yurii Vlasov, William MJ Green, and Fengnian Xia, "High-throughput silicon nanophotonic wavelengthinsensitive switch for on-chip optical networks," *Nature* photonics, vol. 2, no. 4, pp. 242–246, 2008.

- [4] Juan-Jose Crespo, Francisco José Alfaro Cortés, and José Luis Sánchez García, "PhotoNoCs: un simulador de redes ópticas para CMPs," Jornadas de Paralelismo, pp. 509–516, 2015, ISBN: 978-84-16017-52-2.

- [5] Johnnie Chan, Gilbert Hendry, Aleksandr Biberman, Keren Bergman, and Luca P Carloni, "Phoenixsim: A simulator for physical-layer analysis of chip-scale photonic interconnection networks," in Proceedings of the Conference on Design, Automation and Test in Europe. European Design and Automation Association, 2010, pp. 691–696.

- [6] Raymond G Beausoleil, J Ahn, N Binkert, Al Davis, David Fattal, Marco Fiorentino, Norman P Jouppi, Moray McLaren, CM Santori, Robert S Schreiber, et al., "A nanophotonic interconnect for high-performance many-core computation," in High Performance Interconnects. HOTI'08. 16th IEEE Symposium on, pp. 182–189.

- [7] Andrzej Kaźmierczak, Emmanuel Drouard, Matthieu Briere, Pedro Rojo-Romeo, Xavier Letartre, Ian O'Connor, Frederic Gaffiot, and Zbigniew Lisik, "Optimization of an integrated optical crossbar in soi technology for optical networks on chip," Journal of Telecommunications and Information Technology, pp. 109–114, 2007.

- [8] Richard A Soref and Brent E Little, "Proposed N-wavelength M-fiber WDM crossconnect switch using active microring resonators," *IEEE Photonics Technology Letters*, vol. 10, no. 8, pp. 1121–1123, 1998.

- Letters, vol. 10, no. 8, pp. 1121–1123, 1998.

[9] BE Little, ST Chu, W Pan, and YAKY Kokubun, "Microring resonator arrays for vlsi photonics," IEEE Photonics Technology Letters, vol. 12, no. 3, pp. 323–325, 2000.

- [10] Shih-Jung Chang, Chi-Yu Ni, Zhipeng Wang, and Yung-Jui Chen, "A compact and low power consumption optical switch based on microrings," *IEEE Photonics Technology Letters*, vol. 20, no. 12, pp. 1021–1023, 2008.

- [11] Yuta Goebuchi, Masahiko Hisada, Tomoyuki Kato, and Yasuo Kokubun, "Optical cross-connect circuit using hitless wavelength selective switch," *Optics express*, vol. 16, no. 2, pp. 535–548, 2008.

- [12] Yuta Goebuchi, Tomoyuki Kato, and Yasuo Kokubun, "Multiwavelength and multiport hitless wavelength-selective switch using series-coupled microring resonators," *IEEE Photonics Technology Letters*, vol. 19, no. 9, pp. 671–673, 2007.

- [13] Nicolás Sherwood-Droz, Howard Wang, Long Chen, Benjamin G Lee, Aleksandr Biberman, Keren Bergman, and Michal Lipson, "Optical 4×4 hitless silicon router for optical Networks-on-chip (NoC)," Optics express, vol. 16, no. 20, pp. 15915–15922, 2008.

- [14] Assaf Shacham, Keren Bergman, and Luca P Carloni, "On the design of a photonic network-on-chip," in Proceedings of the First International Symposium on Networks-on-Chip. IEEE Computer Society, 2007, pp. 53-64.

- [15] Steven J Koester, Clint L Schow, Laurent Schares, Gabriel Dehlinger, Jeremy D Schaub, Fuad E Doany, and Richard A John, "Ge-on-soi-detector/si-cmos-amplifier receivers for high-performance optical-communication applications," *Journal of Lightwave Technology*, vol. 25, no. 1, pp. 46–57, 2007.