The European Chip Ecosystem and Open Source Silicon

AIIIII

# TABLE OF CONTENTS

| Abstract, Terminology and Disclaimer                                | 3  |

|---------------------------------------------------------------------|----|

| Executive Summary and Introduction                                  | 4  |

| Background                                                          | 5  |

| The rising role of open source hardware                             | 5  |

| A focus on open source silicon                                      | 6  |

| The Open Source Silicon Landscape                                   | 7  |

| Open source silicon's position in the semiconductor value chain     | 7  |

| Main components of the open source silicon landscape                | 9  |

| Open Instruction Set Architectures (ISAs)                           | 9  |

| Open Electronic Design Automation (EDA) tools                       | 9  |

| Open Process Design Kits (PDKs)                                     |    |

| Open Intellectual Property blocks                                   | 10 |

| Strategic open innovation and geopolitics                           | 11 |

| Open source silicon under the SWOT lens                             | 14 |

| Key opportunities relevant to open source silicon strategies        |    |

| Boosting semiconductor R&D in Europe                                |    |

| Security through transparency                                       | 15 |

| Bottom-up industrial reinforcement                                  | 16 |

| Threats relevant to open source silicon strategies                  | 17 |

| An opaque gap between academia and industry                         | 17 |

| Missing the opportunity to attract more women to the sector         | 17 |

| Failing to build a critical mass in OSH and open source silicon     | 18 |

| Recommendations for Europe's chip sovereignty by strategic openness | 19 |

| Conclusion                                                          | 25 |

| Background of the expert opinion                                    | 26 |

## ABSTRACT

This policy brief introduces the open source silicon approach in terms of its importance for semiconductor research and development as well as its industrial integration in Europe. The background of this approach and its relations to the semiconductor value chain are investigated in an overview of the open source silicon landscape. The strengths and weaknesses of open source silicon and their implications for Europe's strategic opportunities are consequently examined: a SWOT analysis will form the basis for concrete policy recommendations on the potential of open source silicon to strengthen Europe's semiconductor ecosystem. Here, a focus lies on research and development as well as on start-ups and SMEs in Europe.

## TERMINOLOGY

| AI         | Artificial Intelligence                                                                             | ISA  | Instruction Set Architecture                                                                |

|------------|-----------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------|

| Alliance   | European Alliance on Processors<br>and Semiconductor Technologies                                   | КРІ  | Key Performance Indicator                                                                   |

| ALLPROS.eu | Secretariat for the European Alliance on Proces-<br>sors and Semiconductor Technologies CSA project | LE   | Large Enterprises                                                                           |

| CSA        | Coordination and Support Action                                                                     | PDK  | Process Design Kit                                                                          |

| DEP        | Digital Europe Programme                                                                            | R&D  | Research and Development                                                                    |

| EC         | European Commission                                                                                 | R&I  | Research and Innovation                                                                     |

| EDA        | Electronic Design Automation                                                                        | SME  | Small and Medium-sized Enterprise                                                           |

| EU         | European Union                                                                                      | SWOT | Analysis considering strengths, weaknesses, opportunities and threats of a research subject |

| FET        | Future Emerging Technologies                                                                        | TWGs | Thematic Working Groups                                                                     |

| HE         | Horizon Europe                                                                                      | ОЅН  | Open Source Hardware                                                                        |

| НРС        | High Performance Computing                                                                          | OSS  | Open Source Software                                                                        |

| IPCEI      | Important Project of Common European Inte-<br>rest                                                  | WP   | Work Package                                                                                |

| IC         | Integrated Circuit ("Chip")                                                                         |      |                                                                                             |

ALLPROS.eu has received funding from the European Commission's Digital Europe Programme (DEP), under Grant Agreement No. 101083947. The content of this document does not represent the opinion of the European Union, and the European Union is not responsible for any use that might be made of such content. The European Commission is not liable for any use that may be made of the information contained herein.

LEAD AUTHORS Paula Grzegorzewska Helena Winiger (OpenForum Europe)

### EXECUTIVE SUMMARY

The fundamental importance of semiconductor technologies across various industries, including Al-driven sectors, underscores the need for Europe to reduce its strategic dependencies in the chip sector. In response, there is a growing focus on the open source approach, particularly through open source silicon, to enhance European sovereignty and innovation in semiconductor research and development. This policy brief explores the significance of open source silicon in semiconductor R&D and its integration within the European industrial landscape. It delves into the background of this approach, its relevance within the semiconductor value chain, and its potential to strengthen Europe's semiconductor industry. The brief employs a SWOT analysis to assess the strengths and weaknesses of open source silicon and its implications for Europe. Based on a combination of targeted research, expert interviews, and insights from ALLPROS.eu workshops and webinars, this brief offers valuable insights into how the open source silicon approach can contribute to addressing Europe's semiconductor challenges and fostering innovation.

## INTRODUCTION

Europe's semiconductor or "chip" ecosystem faced geoeconomic crises and geopolitical tensions in recent years such as the disruptions of supply chains in the wake of the COVID-19 pandemic and increased trade disputes.<sup>1</sup> It is semiconductor technologies that provide the foundation for sustaining and growing many industries: not only digital and directly dependent industries such as the healthcare or automotive industry, but also in the future a broader range of allied sectors. Because the role of artificial intelligence (AI) is becoming increasingly critical across sectors, strategic dependencies in the area of semiconductors, which are fundamental to AI technologies, is in turn an increasing risk for Europe. As a result of this fundamental role combined with recent geopolitical events, it has become imperative for the European Union to reduce strategic dependencies in the chip sector.

In a similar way that the open source approach has strengthened the software industry, there is now a focus on this approach for reinforcing the hardware industry in an international context, in particular in the area of semiconductor research and development: through open source silicon. By this rationale, open source hardware is highly relevant to increasing European sovereignty in the field of processors and semiconductor technologies: it can strengthen domestic innovative semiconductor capacities bottom-upandmitigated ependencies on supplying regions.<sup>2</sup>Inparticular, research and academia as well as smaller companies benefit from the accessibility, flexibility, and interoperability that open source silicon brings to this highly specialised and complex ecosystem. But since the approach is still nascent at its core, start-ups and SMEs need to be supported by EC actions in terms of legal certainty and dedicated R&D incentives when it comes to scaling up innovation.

This policy brief aims to explain the open source silicon approach in terms of its importance for semiconductor research and development as well as its industrial integration in Europe. It will examine the background of this approach and how it relates to the semiconductor value chain, as well as its weaknesses and strengths and their consequences for Europe: After an overview of the open source silicon landscape, a SWOT analysis will be presented to identify how the approach of open source silicon can be leveraged to strengthen the European semiconductor industry. The knowledge production process at the basis of this brief involved targeted research, expert interviews and insights gained from ALLPROS.eu workshops and webinars.

E.g., see: Tan (2023). <u>China slaps export curbs on chipmaking metals in tech war warning tu U.S., Europe</u>. CNBC. For the respective geopolitical relevance see also: Webb (2023). <u>In a World Awash in Data, Geopolitics is All About Chips</u>. Bloomberg.

EC Working Group on OSH and OSS (2022). <u>Recommendations and roadmap for European sovereignty on open source hardware, software and RISC-V Technologies</u>.

## BACKGROUND

Various policies for fostering sovereignty in the digital sectors seem to be in contradiction with each other when it comes to their stance on open technologies. On the one hand, there are policies that concentrate on the race for closed innovation through patenting strategies; on the other hand, there is an approach that adheres to the rationale of technological openness. However, the history of digitalisation in the European Union has, on closer examination, outgrown this dichotomy, which spurs and expands global competition, enabling it to create a level playing field for European actors. In recent decades, open technologies have introduced competitive advantages to both open source as well as proprietary products, which in turn has led to greater economic capacity for industrial adoption.<sup>3</sup>

# The rising role of open source hardware

Open source software (OSS) has played a significant role in the European and international private and public sectors in the past two decades. The implementation of openness principles in competitive digital markets is now slowly taking off in the open source hardware (OSH) space. This is particularly visible in the field of semiconductors and processor technologies: this complex environment has been significantly enhanced and stimulated by open source silicon. Most notably, the prominent and open RISC-V standard has generated a large open source trend in the semiconductor domain. Numerous start-ups basing their innovative efforts to a large extent on these open chip architectures have emerged in Europe and around the world.<sup>4</sup> Open source approaches offer new opportunities for the highly interdependent stakeholders within the semiconductor ecosystem.

In light of the European Chips Act and further legislative acts that seek to mitigate certain strategic dependencies in critical digital industries, it is important to be ahead of this open source silicon curve that is embraced around the globe. Leveraging this open innovation is instrumental to expanding and strengthening the regional ecosystem and boosting Europe's industry in areas where its potential is not yet being realised, such as chip design capacities. Recognising this opportunity, various initiatives on the EU level are generating roadmaps, analyses, reports and recommendations that jointly aim to develop a consistent strategy to integrate heterogeneous practices within the open source silicon landscape in Europe.<sup>5</sup> This strategic use of technological openness, combined with Europe's inventive power, can help overcome disadvantages that have already materialised in the chips sector. This open approach is, thus, strategically relevant when it comes to strengthening the sovereignty of Europe's semiconductor industry and to mitigating dependencies.

For instance, the HE initiated TRISTAN consortium is working on unified application strategies for European semiconductor technologies on the basis of RISC-V, see: Horizon Europe (2023). <u>Together for RISc-V Technology and ApplicatioNs</u>.

<sup>3.</sup> Blind et al. (2021). The impact of Open Source Software and Hardware on technological independence, competitiveness and innovation in the EU economy. Final Study Report.

<sup>4.</sup> See: EE Times (2023). Silicon 100: Startups Worth Watching in 2023, but also start-up members within the RISC-V foundation.

### A focus on open source silicon

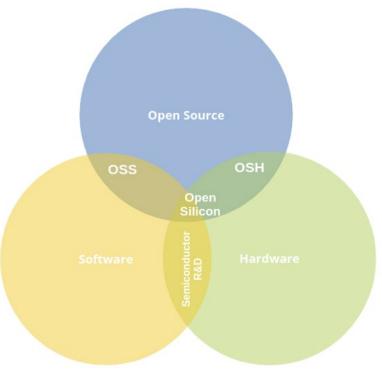

In the chip sector, the term "open source silicon"<sup>6</sup> is used in a colloquial manner to refer to open source, i.e. disclosed and publicly accessible hardware designs and components in integrated circuit (IC) design processes by the means of software.<sup>7</sup> This means that while open source silicon is understood as OSH, it still involves software (see Figure 1).<sup>8</sup> Furthermore, it can refer to the openness of semiconductor manufacturing requirements and hardware components necessary for chip integration in general. "Open" here refers to the freedom to access, use, modify, and distribute these designs or technologies. The term can also include the absence of royalty fees or licensing fees. Synonyms exist, including "free hardware (design)"<sup>9</sup> or "free and open source silicon"<sup>10</sup>, indicating the above-mentioned freedoms. To create an inclusive understanding of strategies to bridge the gap between academia and industry, open source silicon is understood more broadly in this document, so that absence from royalty or licensing fees may or may not be designated.

While OSS has already become ubiquitous, OSH's increased popularity and industrial relevance is a more recent phenomenon. Within OSH, open source silicon is growing rapidly, especially since the release of RISC-V in 2015 – a free and open instruction set architecture (ISA) standard that has fueled innovation in the field.<sup>11</sup> Additionally, OSS innovation and trends are spilling over into the open source silicon field, as advances in OSS not only inspire software and hardware engineers working in chip design, but are also instrumental to the various pieces of software involved in chip design. This new wave of innovation led to the emergence of start-ups and technologies worldwide, including free and open source as well as proprietary cores. The integration of RISC-V and related open solutions is often seen as a catalyst for innovation.

Figure 1 - Open source silicon within software and hardware domains

- 6. Often shortened to "open silicon". The term is to be distinguished from an US-based chip design company Open-Silicon, now part of SiFive.

- 7. This does not mean that all semiconductor technologies and components that are referred to with "open source silicon" are actually primarily based on the material of silicon. Other materials could also be used, such as gallium nitride (GaN) and silicon carbide (SiC).

- OSH or sometimes also called OSHW is <u>defined by the Open Source Hardware Association</u> (although the organisation does not focus on silicon applications). A prominent OSH licence, CERN OHL, is provided by CERN, see: CERN Knowledge Transfer (2023). <u>CERN Open Hardware Licence</u>. It comes with a specific applicability for printed circuit boards (PCBs).

- 9. Stallman (n.d.) Free Hardware and Free Hardware Designs, Free Software Foundation.

- 10. See, e.g., defined by the FOSSi foundation.

<sup>11.</sup> Semico Research (2022). Analyzing the RISC-V CPU Market for SIP, SoCs, AI and Design Starts.

### THE OPEN SOURCE SILICON LANDSCAPE

As already mentioned, RISC-V is a prominent constituent of open source silicon that is now making its way into the mainstream of innovation in microelectronics. However, it is meanwhile situated within, and interdependent on, a broader ecosystem that can be called the open source silicon landscape. Below is a brief overview of its main components and constituents.

# Open source silicon's position in the semiconductor value chain

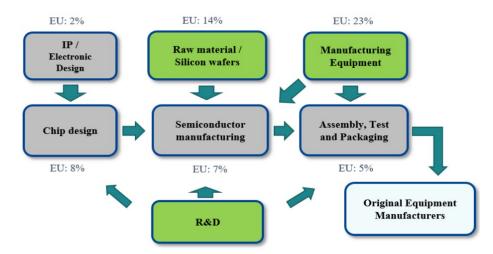

The general semiconductor value chain includes various production steps and inputs. Briefly, these comprise chip design, manufacturing<sup>12</sup> and ATP (assembly, test, and packaging)<sup>13-14</sup>. Chip designers rely on a multitude of R&D processes and intellectual property (IP) blocks, while chip manufacturers depend on a variety of specialised equipment, materials, chemicals, and other resources. The majority of these production steps, processes and inputs is highly specific and high-cost, which generates high barriers to entry for new entrants. The investment needed in semiconductor R&D, for example, is very high compared to other sectors.<sup>15</sup> Although Europe is particularly strong in inputs such as equipment and chemicals, as well as innovative research conducted in leading Research and Technology Organisations (RTOs), strategic weaknesses are located in the production processes itself, including chip design.<sup>16</sup>

Figure 2 - Semiconductor supply chain: EU global market shares of relevant segments (source: European Chips Act)<sup>17</sup>

- 12. Manufacturing can either be conducted in-house by the design entity of the chip, as in the case of Integrated Device Manufacturers (IDMs) or in a fab. A "fab" is a single fabrication plant of a company specialised in the fabrication of chips, i.e., a foundry. In contrast, a company that specialises in chip design and outsources all manufacturing processes is called "fabless".

- 13. ATP can either be conducted in-house by IDMs, in-house by foundries, or by a specialised company. This company model is called Outsourced Semiconductor Assembly and Test (OSAT).

- 14. For an introduction to the semiconductor value chain, see: Baisakova & Kleinhans (2020). The Global Semiconductor Value Chain: A Technology Primer for Policy Makers. Policy Brief. SNV Berlin.

- 15. In 2020, the semiconductor industry allocated about 15 percent of its revenue on R&D. For an in-depth understanding of the semiconductor value chain's characteristics, see: Hess & Kleinhans (2021). <u>Understanding the global chip shortages</u>. Policy Brief. SNV Berlin.

- 16. For a thorough analysis, see: Kleinhans (2021). The lack of semiconductor manufacturing in Europe. Policy Brief. SNV Berlin.

- 17. EC (2022). European Chips Act: Communication, Regulation, Joint Undertaking and Recommendation

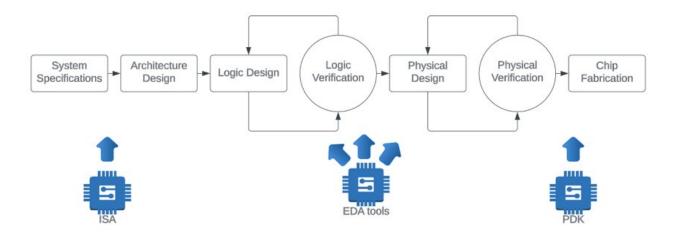

Within the value chain, the open source silicon landscape essentially encompasses the field of chip design. Different architectures, standards, IP cores, and pieces of software are needed to deliver a valid design.

Electronic design automation (EDA) tools are used for simulating the behaviour of the intended chip architecture and design on the basis of its representation in a hardware description language, such as Verilog. These same EDA tools are also instrumental for designing the individual chip, and for verifying the logical and physical composition of the chip.

After the completion of these steps, the design is transferred to production adjusted to a specialised blueprint, a so-called process design kit (PDK). The PDK is provided by the manufacturing entity i.e., foundry and contains essential design rules, data, and libraries. The overall chip design flow is indicated in Figure 3.

Figure 3 - The chip design process steps and tools in the design of processors<sup>18</sup>

After this brief overview of the production steps of the semiconductor value chain that are relevant to the approach of open source silicon, key components of the open source silicon landscape are outlined in the following.<sup>19</sup>

Here, their degree of maturity of open source solutions, their profitability, and relevance for education and skills, is addressed.

<sup>19.</sup> The open source silicon landscape's components follow the publications of the PULP project at ETH Zurich, in particular: Gürkaynak (2023). <u>Special session on RISC-V and OSH. Presentation</u>.

<sup>18.</sup> The presentation of the process design steps follows the detailed overview of Any Silicon (n.d.): Chip Design.

# Main components of the open source silicon landscape

#### **Open Instruction Set Architectures (ISAs)**

- Maturity of open source solutions: high

- Profitability of open source solutions: high

- Relevance for education and skills: high

The RISC-V ISA, which is giving open source silicon development a big boost at the moment, was developed at the University of California in 2010 and made accessible to the OS community and the public since 2015. Its popularity has been increasing and its community growing ever since. It is based on the principle of a reduced instruction set computer (RISC), striving for simplicity, modularity, and extensibility. The standard is accessible licence- and royalty-free and allows for the design, integration, and modification of RISC-V-based processors.<sup>20</sup> The diverse ecosystem emerging from it unites engineers from various backgrounds, both hardware and software, that customise and advance applications for different fields, including low-power processing and high-performance computing (HPC). Large enterprises as well as leading research institutions actively support the ecosystem.<sup>21</sup> Universities are adopting this ISA for educational purposes, allowing for up-to-date and highly applied research scenarios that help to attract talent.<sup>22</sup> Innovation that is based on the RISC-V ISA can be both OS and proprietary, since the standard is open to all and does not exclude commercialising.

#### **Open Electronic Design Automation (EDA) tools**

- Maturity of open source solutions: low

- Profitability of open source solutions: low-moderate

- Relevance for education and skills: high

Open EDA tools refer to electronic design automation tools that are open source and used for chip design, simulation, layout, and verification. They offer advantages for chip designers such as the educational support from the OS community and low barriers to entry for innovation due to their affordability. Available at no or low cost, this difference is significant given that proprietary EDA tools' licensing costs are often five to ten times the general IT infrastructure costs for smaller companies, and are also substantial even for large enterprises.<sup>23</sup> Most open EDA tools are still only at the level of modelling design rather than physical design.<sup>24</sup> For this purpose, specific hardware description languages (HDLs) are used that enable a representation of the future chip. Prominent examples of open EDA tools include OpenROAD and Verilator. Many EDA processes covered in the design step such as processes done with simulators are still dependent on proprietary software that is provided by an oligopoly of three companies (Synopsys, Cadence, and Mentor/Siemens). European incentives for open innovation in the EDA domain are therefore advocated for in the community of semiconductor R&D.<sup>25</sup>

- 22. RISC-V International (n.d.). RISC-V technical specifications.

- 23. Gopal et al. (2022). Economics of EDA on AWS: License Cost Optimization. Aws blog.

- 24. This level is referred to as the register transfer level (RTL).

- 25. An impression of this community feedback was received in the semi-structured interview process on the basis of this policy brief. For an overview of open EDA tools for different purposes, see: Any Silicon (n.d.). <u>The Ultimate Guide to Open Source EDA Tools</u>, and Payne (2020). <u>EDA Open Source and Free Tools Wiki</u>. SemiWiki.

<sup>20.</sup> While the RISC-V ISA itself is only a design architecture open to be implemented in hardware, the actual implementations integrating it can be open or closed. Since the standard is foundational to various open source silicon components and, when it comes to the concept of open source silicon, broadly discussed at the moment it was given a stand-alone category here.

<sup>21.</sup> See, e.g.: Infineon (2023). Leading Semiconductor Industry Players Join Forces to Accelerate RISC-V.

#### **Open Process Design Kits (PDKs)**

- Maturity of open source solutions: low

- Profitability of open source solutions: low

- Relevance for education and skills: high

With the trend of chip design being opened up more in general, the number of initiatives where chip designers and fabs are working together to open up PDKs is increasing too: while the maturity of open source solutions is still low, a subtle trend toward the opening of PDKs can be observed. In an international and industrial context, the releases of the GlobalFoundries PDKs are historically influential. Google recently started a program around open PDKs in a joint initiative with Efabless, SkyWater, and GlobalFoundries that fosters the design process of chips and covers manufacturing costs for students and OS developers.<sup>26</sup>

It was received positively by OSH developers, and other stakeholders of the European semiconductor ecosystem. For instance, Antmicro actively participated in the program. When it comes to R&D initiatives in Europe, the Leibniz Institute for High Performance Microelectronics (IHP) recently opened one of its PDKs which will be integrated in research and education modules. The hope is that the release will inspire similar initiatives aiming at research or educational impact.<sup>27</sup>

#### **Open Intellectual Property blocks**

- Maturity of open source solutions: low

- Profitability of open source solutions: low-moderate

- Relevance for education and skills: high

An existing bottleneck to use OSH assets for innovation in European research and development are IP blocks as required inputs. These can be soft IP (initial design steps and requirements such as code, simulation models, tools) or hard IP (subsequent design steps and requirements such as masks or analogue blocks). The majority of open source silicon is situated in the domain of soft IP at the moment. The trend of specialisation in semiconductor innovation increases the amount and complexity of IP blocks needed for designing chips in various integrations such as chiplets. For instance, these blocks are necessary for the system's peripherals but can also be relevant for specific processor applications.

Not only are IP blocks traditionally closed but also dependent on closed tools and PDKs. This creates high licensing costs as well as dependencies on suppliers and foundries' non-disclosure agreements (NDAs) that can be significant access barriers for small companies and research projects interested in chip design. The technical functions of the IP in question are non-transparent, creating difficulties for engineers when it comes to the verification of processes closely related to the IP.<sup>28</sup> Activities targeted at the improvement of interoperability, accessibility, modularity, and reusability of IP blocks are therefore already encouraged by researchers and developers, including the EC-initiated thematic working group on OSS, OSH and RISC-V.<sup>29</sup> A starting point to tackle the bottleneck of closed hard IP would be more open EDA tools as well as the open access to the foundries' PDKs.

By and large, the open source silicon approach constitutes a key enabler in chip design that is reinforced by an active R&D community. The advantages that open source brings in the semiconductor ecosystem when it comes to talent and competition, education, and mitigation of costly dependencies are already recognised by policy and funding in Europe. However, at the European level, there is also a need for strategic incentives for open innovation in this domain to compensate for existing bottlenecks and increase interoperability in the landscape. The most critical bottlenecks reported by open source silicon experts during the knowledge acquisition process in interviews and webinars were the degrees of openness of EDA tools and PDKs that constitute further difficulties for small entities.

<sup>29.</sup> See: EC Working Group on OSH and OSS (2022). Recommendations and roadmap for European sovereignty on open source hardware, software and RISC-V Technologies. A detailed list on open IPs required for System on Chip (SoC) designs is given on pp. 42f.

<sup>26.</sup> This is called the OpenMPW shuttle program. For more information, see: Google (2022). GlobalFoundries joins Google's open source silicon initiative. Google OS Blog.

<sup>27.</sup> See the release of IHP's PDK: IHP (2022). <u>IHP Open Source PDK</u>.

<sup>28.</sup> Bailey (2023). IP Becoming More Complex, More Costly. Semiconductor Engineering.

### STRATEGIC OPEN INNOVATION AND GEOPOLITICS

In recent years, geopolitics has led to complex international scenarios directed at the economic decoupling of regions.<sup>30</sup> This included siloed research and technology developments accompanied by international trade policy and foreign policy interventions. Intense trade conflicts exist in particular between China and the US.<sup>31</sup> However, the EU is also acknowledging China as a systemic rival whose "clear goal is a systemic change of the international order with China at its centre".<sup>32</sup>

Hence, the EU is increasingly involved in these trade disputes, e.g., through restricting the supply of equipment to China,<sup>33</sup> to which China has responded with export restrictions on materials which are essential for the EU's semiconductor industry.<sup>34</sup> Overall, these geopolitical developments led to a paradigmatic shift in the international collaboration within the semiconductor value chain.

The Chinese government highlighted ambitious goals concerning the domestic semiconductor industry in its Made in China 2025 strategy<sup>35</sup> concerning an independent domestic supply chain, as well as governmental incentives in its "State Council Notice on the Publication of Certain Policies to Promote the High-Quality Development of the Integrated Circuit Industry and the Software Industry in the New Period".<sup>36</sup> These strategies are backed by a governmental investment plan established in 2014, incorporated in the China Integrated Circuit Industry Investment Fund ("the Big Fund").

It raised nearly fifty billion USD to serve investments in the domestic semiconductor sector and contributed to the success of the state's strongest foundry SMIC.<sup>37</sup> Although these strategies have been successful when it comes to increasing the share of global sales, the industry is still very dependent on the import of tools and equipment from the US and Europe. The Chinese foundry SMIC is not able to keep up with the leading edge in manufacturing and was affected by several U.S. export controls.<sup>38</sup> However, China is still investing strongly in early innovation of its domestic semiconductor ecosystem, especially in the chip design sector which is thought to enable high revenue.<sup>39</sup>

While the Quadrilateral Security Dialogue's (Quad) trade share with China has increased,<sup>40</sup> long-standing trade partnerships and cooperations between international regions and geographically-concentrated industries have been eroded in strategic sectors such as the chip industry. In response to China's quests for technological dominance in the chip sector and its unfair behaviour in international competition, new geoeconomic alliances and agreements have been formed, especially between the United States, India, Japan, and Europe.<sup>41</sup>

<sup>41.</sup> See, e.g., the <u>EU-US Trade and Technology Council (TTC)</u> as well as the <u>EU-India TTC</u>. India and the US are <u>moving closer together</u>, and Japan and EU recently declared new strategic cooperations in semiconductor areas: Nussey (2023). <u>EU, Japan to deepen chip cooperation, Breton says</u>. Reuters.

<sup>30.</sup> World Economic Forum (2019). The rise of techno-nationalism - and the paradox at its core.

<sup>31.</sup> Robinson (2023). US mulls retaliation for China blacklisting Micron without evidence of security threat. The Register.

<sup>32.</sup> EC (2023). Speech by President von der Leyen on EU-China relations to the Mercator Institute for China Studies and the European Policy Centre.

<sup>33.</sup> Haeck (2023). Dutch slap new restrictions on chips exports to China. Politico.

<sup>34.</sup> Aarup et al. (2023). China's threat on mineral exports knocks EU off balance. Politico.

<sup>35.</sup> PRC State Council (2015); Etcetera Language Group, Inc. (2022). Notice of the State Council on the Publication of "Made in China 2025". CSET.

<sup>36.</sup> PRC State Council (2020); Etcetera Language Group, Inc. (2020). <u>State Council Notice on the Publication of Certain Policies to Promote the High</u> <u>Quality Development of the Integrated Circuit Industry and the Software Industry in the New Period</u>. CSET.

<sup>37.</sup> Liu & White (2022). China's Big Fund corruption probe casts shadow over chip sector. Financial Times. As reported in the article, the fund was under state investigation for corruption.

<sup>38.</sup> Lee & Kleinhans (2021). Mapping China's semiconductor ecosystem in a global context. SNV Berlin.

<sup>39.</sup> Hess et al. (2023). Who is funding the chips of the future? SNV Berlin.

<sup>40.</sup> Economist Intelligence (2023). Conflict over Taiwan: assessing exposure in Asia. EIU Report.

Internationally, regions that are leading in the international semiconductor ecosystem foster governmentbacked investment and policy strategies on this issue that has been set against a backdrop of increasing tensions due to supply shortages and the trade conflicts. These strategies focus on providing subsidies of several tens of billions USD to increase national or regional sovereignty and competitiveness.<sup>42</sup> While the initiatives include standardisation- and patent-oriented strategies, they also promote strategic open innovation related to the semiconductor ecosystem, especially with respect to R&D initiatives.

The growing importance of open source silicon is recognised by the regions highly active in semiconductor R&D. China was a relatively late adopter of open source, but has since recognised the relevance of open source to its technological sovereignty and is making strong strategic use of it. When it comes to the chip sector, it grasped the opportunity to adopt RISC-V for broad industrial R&D in open source silicon and now invests heavily in an innovative infrastructure of open source silicon.<sup>43</sup> Furthermore, open source silicon is utilised to counterbalance the significant U.S. export controls that China faces at the moment and to grow an independent domestic semiconductor ecosystem.<sup>44</sup> The Chinese government is systematically subsidising this and is deploying dedicated public-private partnerships within the sector to spur innovation and increase self-reliance.<sup>45</sup>

In the US, incentives for open source silicon are not only provided on an industrial level (see open PDK section above), but also on a government level. On the one hand, the Creating Helpful Incentives to Produce Semiconductors and Science Act (CHIPS for America Act) has the objective of reshoring and near-shoring manufacturing and innovative R&D processes that are considered relevant for its supply chain resilience.<sup>46</sup> It takes into account the benefits of open source and open science for the domestic semiconductor ecosystem.<sup>47</sup>

For instance, within the scope of a Request for Information (RFI), the Act's implementation strategy reflects methods to provide free and open access to important inputs and processes, such as EDA tools and IP. It recognises the accelerating role of openness in R&D as well as in lowering market entry barriers for small, fabless companies.<sup>48</sup> In light of China's OS efforts in its domestic chip sector, however, the US is partly considering ways to limit its OS developments to like-minded international partners, e.g., through export controls on open design platforms.<sup>49</sup>

In contrast, the U.S. Department of Defense's (DoD) Research Agency, DARPA, has been betting on open source silicon for longer in various projects. While its POSH project, for instance, funds the development of open source hardware IP and respective symbolic verification tools,<sup>50</sup> its toolbox initiative is targeted to facilitate easy access to tools and IP at low cost for DARPA funded research programs. It involves several open source silicon stakeholders, such as SiFive. Although knowledge sharing is accelerated within the toolbox infrastructure, the use of corresponding knowledge may be subject to non-disclosure agreements (NDAs) and is not considered open source as such.<sup>51</sup>

India<sup>52</sup> aims at enabling a broad domestic infrastructure around RISC-V, leading to a strong OSH innovation ecosystem, and is providing support on the governmental level. The Ministry of Electronics and Information Technology officially fosters efforts to grow a large open source silicon talent pool, and to boost chip design capacities in India. The undertakings include the establishment of the Digital India RISC-V (DIR-V) programme that is to support Indian start-ups and bridge the gap from academia to commercialisation.<sup>53</sup>

44. Hess et al. (2023). Who is funding the chips of the future? SNV Berlin.

<sup>53.</sup> Economic Times Telecom. <u>RISC-V becoming a global movement with India as leading player: MoS IT</u>, and: Jain (2023). <u>Open-Source Movement in India Gets Hardware Update</u>. Analytics India Mag.

<sup>42.</sup> An overview of international semiconductor incentives and fab announcements (as of 2022) is provided by the U.S. Semiconductor Industry Association (2022): Global Semiconductor Incentives.

<sup>43.</sup> Shah (2023). How China is Building an Open National Chip Plan Around RISC-V. HPCwire.

<sup>45.</sup> Arcesati & Meinhardt (2021). China bets on open-source technologies to boost domestic innovation. Merics.

<sup>46.</sup> The White House (2022). FACT SHEET: CHIPS and Science Act Will Lower Costs, Create Jobs, Strengthen Supply Chains, and Counter China.

<sup>47.</sup> NIST. U.S. Department of Commerce (2023). A Vision Strategy for the National Semiconductor Technology Center. CHIPS Research and Development Office.

NIST. U.S. Department of Commerce (2022). <u>Incentives, Infrastructure, and Research and Development Needs to Support a Strong Domestic</u>. <u>Semiconductor Industry</u>. Summary of Responses to Request for Information.

<sup>49.</sup> Congressional Research Service (2023). Frequently Asked Questions: CHIPS Act of 2022 Provisions and Implementation.

<sup>50.</sup> Lim (n.d.) Posh Open Source Hardware (POSH). DARPA.

<sup>51.</sup> DARPA (n.d.) DARPA Toolbox Initiative

<sup>52.</sup> See, e.g., Indian Institute of Technology Madras (2023). SHAKTI. Open Source Processor Development Ecosystem.

The UK's National Semiconductor Strategy is focusing more on deepening significant existing strengths than mitigating weaknesses. While ensuring the important role of IP supplier and chip designer Arm, the UK also explicitly supports the broad uptake of and community-building around the RISC-V standard, especially regarding education, R&D and security by design approaches.<sup>54</sup>

In the context of Europe's digital sovereignty goals<sup>55</sup> and aligned with its goal of Open Strategic Autonomy, Europe is seizing the opportunity that open source silicon provides: The European Chips Act (pillar I)<sup>56</sup> focuses on the intensification of joint collaboration within Europe, with a focus on the integration of the RISC-V standard and openly-accessible research. Concrete capacity-building actions, i.e., the Chips for Europe Initiative, are enabled through the Chips Joint Undertaking (Chips JU) that absorbs the entities and activities of the current Key Digital Technologies Joint Undertaking (KDT JU). It combines Horizon Europe (HE) and Digital Europe Programme (DEP) efforts as well as resources of Member States and third countries.<sup>57</sup>

The EC already initiates and funds several foundational R&D projects through HE that integrate or even focus on RISC-V, such as the European Processor Initiative (EPI)<sup>58</sup> or the TRISTAN consortium that enables joint efforts of large enterprises.<sup>59</sup> Furthermore, a design platform foreseen by the Act is enabling a large-scale design infrastructure for integrated semiconductor technologies and is to include open source design solutions. Its access is intended to be open, non-discriminatory, and transparent.<sup>60</sup>

Overall, numerous regions that are relevant to various inputs, processes or steps in the value chain of semiconductor technologies focus on reinforcing strategies that build on R&D and industry support. They recognise the important role of open source in this hardware domain for increasing resilience and fostering national or regional R&I activities on open source silicon.

For the EU, it seems clear that regional chip sovereignty should be led by openness angles in OSH innovation areas that are already mature, such as RISC-V. In integrating openness in its reinforcement strategies in a geopolitical context, the EU is aware of the significance of international cooperation within a highly complex and interdependent value chain. It focuses on collaborations and alliances that share its democratic understanding, working together with allies and partners in this field to advance common interests and ensure fundamental democratic values and ethical standards.

54. UK Department for Science, Innovation & Technology (2023). National Semiconductor Strategy.

<sup>60.</sup> EC (2022). Proposal for a Regulation establishing a framework of measures for strengthening Europe's semiconductor ecosystem (Chips Act).

<sup>55.</sup> These goals are set in the EC's 2030 Digital Compass and include an intended 20% share of the global "cutting-edge and sustainable" semiconductor production in the EU by 2030. See: EC (2021). Europe's Digital Decade: digital targets for 2030.

<sup>56.</sup> The Chips Act outlines three pillars: the Chips for Europe initiative, the security of supply, and monitoring and crisis. Since open source silicon is instrumental to capacity building and R&D advances, it is tied to pillar I.

<sup>57.</sup> EC (2022). European Chips Act: Communication, Regulation, Joint Undertaking and Recommendation.

<sup>58.</sup> See the European Processor Initiative (2022).

<sup>59.</sup> Horizon Europe (2023). Together for RISc-V Technology and ApplicatioNs.

### OPEN SOURCE SILICON UNDER THE SWOT LENS

Besides semi-structured interviews as well as webinars with relevant experts, this policy brief's recommendations are based on a SWOT analysis of open source silicon for strengthening the European semiconductor ecosystem. The main takeaways from this knowledge gathering are that the open source silicon approach brings significant strengths in enhancing the academic sector and thus in reinforcing the foundation of innovation in the industry. This is primarily a result of open source silicon providing a catalyst for innovation in the production step of chip design. However, it must be pointed out that this area of OSH is still nascent and therefore often lags behind leading-edge proprietary tools or processes. Nevertheless, it offers a large potential for high-level integrations, which should be recognised as strategically relevant. Forming the foundation of the concrete recommendations, this section briefly explains the opportunities and threats that are derived from strengths and weaknesses.

| SWOT analysis                                                                    | Beneficial – open source silicon as a strategy for<br>strengthening the EU semiconductor ecosystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Adverse – open source silicon as a strategy for<br>strengthening the EU semiconductor ecosystem                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                  | Strengths                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Weaknesses                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Internal (structural-organisational,<br>within Europe's semiconductor ecosystem) | <ul> <li>Research and skills advantages by OSH and open science dynamics (academic support)</li> <li>Research and education benefits of open source silicon components (e.g., PDKs)</li> <li>Innovation boost by academic and industrial OS community support and OS ecosystem</li> <li>Competition increase in the chip ecosystem</li> <li>Low cost and low access barriers to innovation</li> <li>Simplicity and interoperability of designs</li> <li>Security through transparency (possible source code analysis and open data)</li> <li>Less affected by geopolitical tensions</li> </ul>                                                                                                                                                                                                                                                                                                                                              | <ul> <li>Legal expertise needed for small players</li> <li>Lack of mature industry IP</li> <li>Lack of clear business cases in early stage OSH</li> <li>Insufficient OSH-specific industry support</li> <li>Unforeseen security, maintenance and compliance needs posed by OSH and its R&amp;D dynamics</li> <li>Unforeseen market dynamics</li> <li>Women are underrepresented in the semiconductor industry and open source</li> </ul> |

|                                                                                  | Opportunities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Threats                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| External (contextual, focus on Europe<br>within the global value chain)          | <ul> <li>Boosting the academic foundation of the EU semiconductor ecosystem (talent and innovation)</li> <li>Research and education opportunities by open source silicon (e.g., PDKs)</li> <li>Supporting academia-industry exchange through OSH within the EU</li> <li>Lowering and sharing of costs (R&amp;D, community support)</li> <li>Novel licensing schemes for hardware innovation</li> <li>Progress in security</li> <li>Support of small players, i.e. start-ups and SMEs (cost, compliance, interoperability, etc.)</li> <li>Windows for European innovation advances (analogies with OSS)</li> <li>Strengthening like-minded cooperations by open source silicon initiatives within policy frameworks such as TTCs</li> <li>Finding reasonable positions for EU within geopolitical tensions</li> <li>Synergies of European Chips Act and open source silicon in international collaboration with alliance partners</li> </ul> | <ul> <li>Falling short of a OSH critical mass to scale up innovation</li> <li>Market dynamics weakening the EU standpoint within the global value chain due to innovation head start by other regions integrating open source silicon</li> <li>Missing the opportunity to attract more women to the sector</li> <li>Unrecognised and unaddressed security, maintenance and interoperability requirements</li> </ul>                      |

| Derived policy considerations                                                    | <ul> <li>Steps for policy and funding</li> <li>Incentivise R&amp;D openness</li> <li>Foster security through transparency</li> <li>Strongly collaborate with like-minded regions</li> <li>Create early industrial support</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <ul> <li>Steps for policy and funding</li> <li>Monitor and address new maintenance and compliance needs</li> <li>Create legal certainty through research, funding, and policy</li> <li>Aim at critical mass in OSH</li> <li>Encourage women in STEM and encourage openness regarding diversity</li> </ul>                                                                                                                                |

Table 1 - SWOT analysis, one degree of abstraction: Open source silicon for EU sovereignty in the semiconductor industry

#### Key opportunities relevant to open source silicon strategies

An industry similar in size and maturity of the OSS ecosystem has not yet emerged in OSH. The ventures that are mature enough to reach the mainstream stages, such as RISC-V, are still in the early stages of their development. However, in expert circles, the phenomenon of OSH is described as being at a stage similar to that of OSS twenty years ago.<sup>61</sup> In order to achieve network effects by opening and initiating overt exchange of innovation inputs rooted in open source, it is relevant to take advantage of the broad collaboration, participation and community of OS dynamics and to nurture and cultivate them institutionally at European universities and research institutes.

#### **Boosting semiconductor R&D in Europe**

On the one hand, key opportunities that should be exploited include recognising the important role of open source silicon to support and extend semiconductor R&D in Europe. Being situated within a broader open science framework, open source silicon enables both the support of the open source community as well as the academic community, accelerating development and revision of ideas by both collaborative and competitive means. The open source approach in the semiconductor field enables a significant lowering of barriers to entry in research and development, with prospects for easier market entry once the approach is taken from the academic lab to the fab. This is instrumental in improving the attractiveness of studies relevant to innovation in the processor and semiconductor technology sectors.

Requirements for chips are becoming ever more specialised in the age of artificial intelligence (AI) and the possibilities for combining multiple processors with different sets of special purposes for a higher-level task are on the rise. Research efforts worldwide have broadly embraced open source silicon advances due to their innovative strengths, in particular on the basis of RISC-V.<sup>62</sup> European academia is already an important location for open source hardware (OSH) and, more specifically, also open source silicon-based innovation. However, on the one hand, several open source silicon components are still missing to go full speed. On the other hand, there is still a severe shortage of foundational skills in the microelectronics industry, in particular, a shortage of software engineers, and advanced systems architecture designers.<sup>63</sup> Open source can be beneficial for research and education since it allows for real-life examples of innovation, community support as well as low access barriers for new talent.<sup>64</sup>

#### Security through transparency

When it comes to semiconductor technology, cybersecurity and hardware security-related questions are of strategic importance throughout the industry and its stakeholders.<sup>65</sup> The notion of openness in hardware may evoke greater technological vulnerability to compromise attempts in some audiences. It is important to remember, however, that open source silicon is located primarily in the chip design step. This production step is characterised by a low level of national security risks, including cybersecurity and hardware security risks. In contrast, it comes with a high level of geoeconomic competitiveness dimensions.<sup>66</sup>

<sup>66.</sup> According to Kleinhans, it is mainly the ATP production step, in particular assembly processes, that allow for the implementation of hardware-specific threats, e.g., backdoors. In the design step, threats could be specific malware – which might be discovered more likely under OS conditions. See the overview of competitiveness benefits, national security risks, and resilience reflections of the strategic dimensions of the chip value chain provided by SNV Berlin: Lee & Kleinhans (2021). Mapping China's semiconductor ecosystem in a global context (p.11). SNV Berlin.

<sup>61.</sup> See, e.g.: Davis (2022). RISC-V in Europe: The Road to an Open Source HPC Stack. Barcelona Supercomputing Center.

<sup>62.</sup> See: EC Working Group on OSH and OSS (2022). <u>Recommendations and roadmap for European sovereignty on open source hardware, software and RISC-V</u> <u>Technologies</u>.

<sup>63.</sup> For more detail see: Coulon et al. (2022). Yearly Monitoring Report 2022. METIS.

<sup>64.</sup> Often it is the heritage in tradition and sincere commitment of universities that allows projects to be continuously nurtured and to create long-term breeding grounds for an enrichment of activities as well as for a transfer of knowledge of academic discoveries into industrial projects. However, the open source character is in general such a strong advantage, because it also allows a high speed and flexibility of innovation. Traditions are important but are constantly revised in OSS and OSH by emerging trends that originate in the real world and allow a realo check of conducted innovation projects. Open source enables a qualitative benchmark, which generates intense competitiveness, as research, knowledge, development and innovation are continuously verified by peer reviewers and contributing developers. This competitive strength should be recognized and exploited as a great potential for both students, researchers, developers as well as faculty and the projects they are involved in. Hence, it is important to harmonise the university context with these intrinsic open source features – to cultivate a vibrant research base that is open to competitive exchange with the industry as well as application-specific feedback from the open source community. This could be also achieved by adjusting university quality standards to modern requirements. Often, for instance, papers are in the spotlight when it comes to making academic success visible. However, aligned with the strengths as well as benchmarks of open source, other achievements such as completed projects should be considered equally important KPIs.

<sup>65.</sup> Blind et al. (2021). The impact of Open Source Software and Hardware on technological independence, competitiveness and innovation in the EU economy. Final Study Report.

Problems that OSH brings forth are rooted rather in the firmware and hardware in general than in their OS nature, thus they are also an issue of closed technologies.<sup>67</sup> Still, the potential of a chip being compromised is a remaining risk within the semiconductor industry that should be tackled throughout the value chain and should be thoroughly investigated, studied and considered when it comes to reinforcing Europe's semiconductor ecosystem. In comparison to software hacking attempts, exploiting vulnerabilities at a hardware level is achieved primarily in highly-targeted and mature cyber threats. This may relate to the underlying processor architecture, which should ideally prove to be particularly resilient. Notably, architectures that are disclosed upfront are subject to continuous evaluation by developers, experts and contributors. In contrast, undisclosed architectures are primarily reviewed by company internal security assessments and do not benefit from the rapid revision processes and collaborative improvements of the OS community. Hence, without these OS revision mechanisms, security issues in proprietary hardware architectures might be communicated to the end consumer later than necessary.

The subject can best be explained by contrasting two concepts: security through obscurity and security through transparency. The concept of security through obscurity relies on secrecy about the inner mechanisms, algorithms, or implementations of a system, with the assumption that it is more secure because potential attackers cannot see the design and its details. However, this concept constitutes only a weak form of security because it relies solely on keeping the design secret, which can be compromised as soon as the details are accidentally or intentionally unveiled. On the other hand, the concept of security through transparency refers to technologies that are transparent by design – i.e. open source to a significant degree – and thereby enabling the public examination and third-party review as an important source of security. This openness allows OS communities composed of experts from different stakeholder groups such as academia or industry to be part of a thorough auditing and peer review process of the system's design and code. This not only ensures an accelerated and broad identification of vulnerabilities but also increases public awareness and trust in the systems. Indeed, open source silicon offers the possibility of qualitative feedback and collective quality assessment and control through the collaborative dynamics associated with the approach.<sup>68</sup>

#### Bottom-up industrial reinforcement

The general modularity and interoperability of open source is also characteristic for the open source silicon approach. A further opportunity is, hence, that this promotes the bottom-up strengthening of the industry from a macroeconomic perspective. In the current era where chiplets are becoming ever more paramount and higher interoperability and embedding requirements must be met, open source is particularly important to innovation. Open access to knowledge, community support as well as lower barriers to enter an innovation segment and the market in general comes with many opportunities for smaller players such as start-ups and SMEs.<sup>69</sup>

New niches in the landscape can be easily recognised, openly communicated and covered by smaller players such as research projects that develop a business case, start-ups, scale-ups and SMEs. If Europe has a strong OSH ecosystem, these industrial players can move faster on such opportunities overall, and build quickly and in a complementary way on the existing ecosystem. Without being tied to a proprietary vendor, companies can purchase licences from several vendors and be more flexible to develop and customise their own IP while also increasing interoperability in the ecosystem.

After start-up phases and early innovation stages have been accelerated by open source, European start-ups and SMEs can seek best practices to expand market share and scale up. Since open source silicon creates new challenges in terms of different compliance issues, however, legal uncertainties need to be addressed strategically by expertise provided by coordinated entities.

<sup>69.</sup> While this policy brief focuses on smaller players, i.e. start-ups and SMEs, open source silicon is also beneficial to large enterprises. Especially in vertical industries where the design requirements are expected to increase significantly in the upcoming decades, such as automotive, the cost effectiveness of the open source silicon approach reinforces domestic industries. See for more information on chiplets as well as applications for verticals: EC Working Group on OSH and OSS (2022). Recommendations and roadmap for European sovereignty on open source hardware, software and RISC-V Technologies.

<sup>67.</sup> See, e.g.: Davis (2022). RISC-V in Europe: The Road to an Open Sour See, e.g., the recent Zenbleed bug of AMD's x86 processor family, affecting Ryzen and Epyc Zen 2 chips: Ormandy (2023). Zenbleed. In contrast, it was discovered and discussed by the OS community. OS security repositories are very valuable for cybersecurity, such as: Google (n.d.) Security Research. Project. ce HPC Stack. Barcelona Supercomputing Center.

<sup>68.</sup> Goldmann (2023). How Secure Are RISC-V Chips? Semiconductor Engineering.

# Threats relevant to open source silicon strategies

## An opaque gap between academia and industry

As indicated in the SWOT analysis, several threats should be considered and mitigated. Market dynamics can weaken the EU's position in the global value chain if the open source silicon strengths remain untapped by domestic industrial uptake while other regions gain an edge in innovation by integrating them. Obstacles to integration should be identified and overcome. Although several European universities and research institutes are at the leading edge of open source silicon research,<sup>70</sup> and some European SMEs are taking up the research results at scale, many innovations based on the research are carried out elsewhere.

Start-ups are emerging around the world but European start-ups are sometimes struggling to integrate the open source approach in their product portfolio due to a lack of local legal expertise, fragmentation of solutions or struggles with commercialising. In contrast, China-based start-ups are flourishing by adapting quickly and successfully to the new innovation scheme enabled by open source silicon, strengthening China's national competitiveness.<sup>71</sup> The existing gap between academia and industry, i.e. commercialisation in Europe, should not be left opaque but should be analysed in-depth. Some challenges are already identifiable and need to be addressed ad-hoc in this course.

## Missing the opportunity to attract more women to the sector

Gender disparity at an academic level is, from an international perspective, particularly evident in STEM study fields and related professions,<sup>72</sup> resulting in a tremendous amount of talent and innovation at risk of remaining unrealised. As of 2022, in its global monitoring of the annual progress of the Sustainable Development Goals (SDGs), the United Nations report a share of only 35 percent women in STEM studies and only 20 percent of women in science and engineering professions. Consequently, this underrepresentation of women in STEM fields has significant economic implications that also materialise in the semiconductor industry.

According to survey results by Accenture and GSA, only 10-15 percent of technical positions and only 13 percent of executive positions are held by women in the international semiconductor industry in 2022.<sup>73</sup> The lack of gender diversity in the industry, in particular the underrepresentation of women leads to a loss of valuable talent and ideas, which hinders innovation and slows down digital sovereignty overall. This is surprising, since the role of women in the technological history of computation and semiconductor development – thus the formation of silicon valley was decisive.<sup>74</sup> However, this role is not elucidated and emphasised enough.

72. UN Women (2022). Progress on the Sustainable Development Goals: The gender snapshot 2022.

74. See, e.g., Hempel (2016). A women's history of silicon valley. Wired.

<sup>70.</sup> Leading research in open source silicon approaches, often with a focus on low-power or a focus on HPC is done, e.g., at the University of Bologna, at ETH Zurich, at the University of Turin, at the Barcelona Supercomputing Center (BSC), at the University of Cambridge, and at CERN.

<sup>71.</sup> Shah (2023). How China is Building an Open National Chip Plan Around RISC-V. HPCwire.

<sup>73.</sup> Accenture (2023). Unlocking the Value of Women in Semiconductor as well as GSA Brief: Women in the semiconductor industry 2022.

Similarly, women are underrepresented in open source.<sup>75</sup> For instance, women's participation in various OSS communities only represent a proportion between 4 and 14 percent.<sup>76</sup> Several efforts have been made to identify the reasons for this or to provide incentives for more women in open source, e.g., through competitions. One key issue is that the culture of open source is still too discouraging for women.<sup>77</sup> Hence, a threat of open source silicon is that it fails to mobilise and motivate women, adding an additional disincentive for more women in the ecosystem. Therefore, a broader theme of openness and diversity should be encouraged in the integration of open source silicon and open source in general to ensure that the approach is successfully inclusive. This can be achieved, for instance, by creating synergies with the realisation of open science that is allowing for cultural changes in universities, and in which women participate more strongly.<sup>78</sup>

## Failing to build a critical mass in OSH and open source silicon

Failing to build a critical mass in OSH and open source silicon can be a threat to European semiconductor sovereignty strategies because it hampers collaboration, interoperability and innovative roots. Furthermore, alternative open technologies to third party IP can support building a robust domestic ecosystem that is open to R&I impetus from active academic projects. Such a failure could be the case when open source projects are not continued, repositories not maintained and collaborative communities not incentivised enough. Fostering a critical mass in OSH and open source silicon can be achieved by communities, organisations, and environments that mediate between public entities, industry, and academia. Their efforts to track needs and best practices, monitor developments and risks, recognise new windows of opportunity and study the complex legal challenges of open source are highly relevant for controlling these threats.

In the following section, detailed advice for increasing European chip sovereignty by an open approach refers to how to shape efforts that are based on and informed by these main opportunities that the EC should seize, and threats that the EC should be aware of when developing policy and funding strategies that integrate open source silicon. These recommendations complement key points of the more specific technical requirements outlined in the OSS and OSH roadmap, and highlight a multi-stakeholder R&I path shaped by education and skills.<sup>79</sup>

77. Trinkenreich et al. (2022). Women's Participation in OSS: A survey of the Literature. ACM.

<sup>75.</sup> Grzegorzewska (2021). There are fewer women in open source than in the ICT sector overall. EC Open Source Observatory (OSOR).

<sup>76.</sup> Trinkenreich et al. (2022). Women's Participation in OSS: A survey of the Literature. ACM.

<sup>78.</sup> Murphy et al. (2020). Open science, communal culture, and women's participation in the movement to improve science. PNAS. Psychological and Cognitive Science.

<sup>79.</sup> EC Working Group on OSH and OSS (2022). Recommendations and roadmap for European sovereignty on open source hardware, software and RISC-V Technologies.

### RECOMMENDATIONS FOR EUROPE'S CHIP SOVEREIGNTY BY STRATEGIC OPENNESS

The following policy recommendations follow the course of insights gained within the first stakeholder engagement within ALLPROS.eu, a series of expert interviews, and are derived from the SWOT analysis. While the overarching topic is related to why and how open source silicon can be used to strengthen innovation in the European semiconductor ecosystem, areas were highlighted that follow the emerging synergies of ALLPROS.eu. For instance, ALLPROS.eu's joint efforts with the EC and the KDT JU elaborated a shared focus on skills. This important focus, backed by insights gained within the semi-structured interview process and webinars, is embraced and related to open source silicon in the following recommendations, to enable a bottom-up approach for Europe's chip sovereignty through strategic openness that is rooted in education.

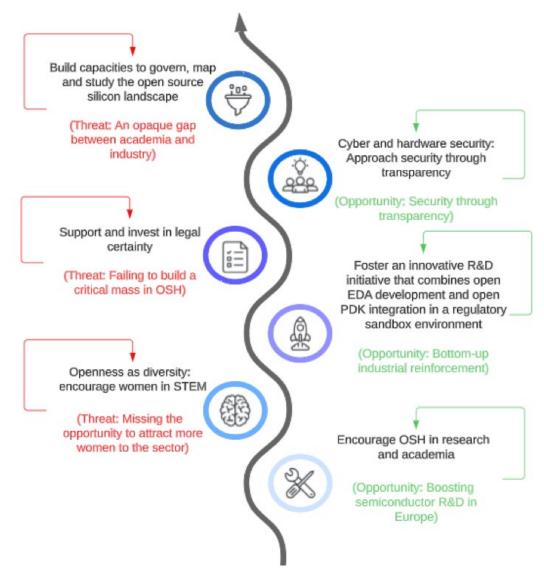

Figure 4 -Recommendations for Europe's chip sovereignty by strategic openness

# 1. Encourage open source hardware in research and academia

Initiatives and frameworks providing funding and policies for open source silicon and OSH at European research institutions should be overall encouraged.

Research, academia, and education as a stakeholder group with major impact for OSH innovation and in the European semiconductor sector should be accompanied by state-of-the-art funding and support strategies. Initiatives and frameworks providing funding and policies for open source silicon and OSH at European research institutions should be overall encouraged.<sup>80</sup> Within the framework of open source and synergies achieved through international collaboration, initiatives should also be realised in European universities by public-private partnerships that aim to involve universities for triple helix oriented R&I activities enabled by the EU's Chips for Europe initiative and associated programmes. Existing EU frameworks focussing on open innovation concepts that are rooted in research, academia and education should be supported to build synergies with these initiatives.<sup>81</sup>

It is important for European universities to approach related graduate studies, such as microelectronics or embedded systems related fields, with the application-tied approach of OSH to leverage and successfully integrate these advantages. To that end, the EC should encourage research and education stakeholders to integrate open source in the academic curriculum.<sup>82</sup> RISC-V is allowing this to be realised in the design of processors, and universities are increasingly adopting the RISC-V ISA already. The EC and relevant research programs funded by the EC, for instance during HE, should encourage the use of RISC-V in research, academia and education. Within funding and policy frameworks, incentives at the academic level should be considered to motivate OS integration in an open ecosystem of higher education, such as awards for research organisations, groups, and individual researchers. Funding activities should be inclusive in such a way that universities that have strong ties with those in the EU should be included and international collaboration encouraged.<sup>83</sup>

# 2. Openness as diversity: Encourage women in STEM

To prevent an additional barrier to attract more women to the semiconductor sector within the implementation of open source silicon, openness has to be communicated and promoted within a strong understanding of the sociotechnical relevance of diversity. Concrete synergies should be created between women in STEM initiatives and semiconductor R&D.

<sup>80.</sup> Standardised study modules could be developed within a targeted EU policy format such as a thematic working group (TWG), which aims to define and explain the modules so that universities can easily incorporate them. These modules should include legal courses in the area of OSH licensing, commercial questions in the area of open source silicon, as well as socio-technical issues such as reflection of socially related topics, e.g., inclusive skills acquisition and sustainable manufacturing solutions.

<sup>81.</sup> A suitable format would, e.g., be EU-backed clusters of excellence at European Universities such as LERU.

<sup>82.</sup> Suggestions concerning a successful integration are also made by Sarancio (2023): <u>Supporting Open Science Hardware in Academia: Policy</u> <u>Recommendations for Science Funders and University Managers</u>. Zenodo.

<sup>83.</sup> For instance, centres of innovation at the University of Cambridge and ETH Zurich, which play a crucial role for the open source silicon network of the EU and for the research strength of the EU in the domain.