# Linearized Track-Fitting on an FPGA Joachim Zinßer, Dr. Sebastian Dittmeier, Prof. André Schöning Physikalisches Institut Heidelberg

For the ATLAS experiment at the High-Luminosity LHC, a hardware-based track-trigger was originally envisioned, which performs pattern recognition via AM ASICs and track fitting on an FPGA. A linearized track fitting algorithm is implemented in the Track-Fitter that receives track candidates as well as corresponding fit-constants from a database and performs the  $\chi^2$ -test of the track as well as calculates the helix-parameters. A prototype of the Track-Fitter has been set-up on a Intel Stratix 10 FPGA. Its firmware was tested in simulation-studies and verified on the hardware. The performance of the Track-Fitter has been evaluated in extensive simulation studies.

# Problem

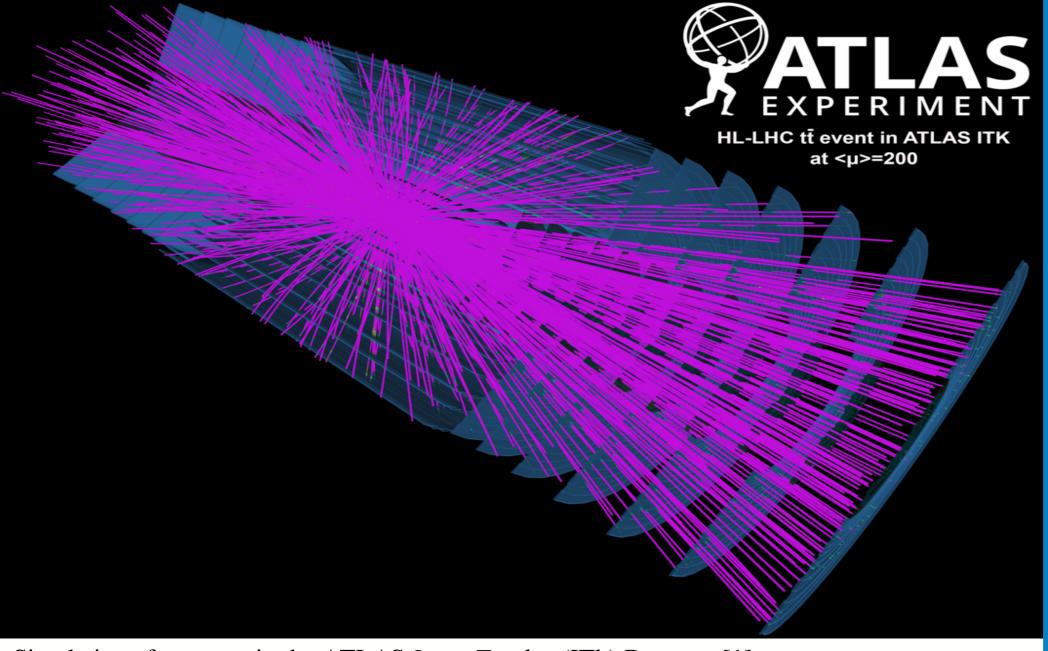

Track-Seeding Problem - Huge Combinatorical Background: In the ATLAS Phase-II Upgrade for the High-Luminosity LHC, the Inner Tracker Detector (ITk) is in development. It is expected that the detector will observe a pileup of 200 proton-proton collisions. To gain information about the types of particles present in the event, each particle's helix track has to be reconstructed.

Each of the thirteen detector layers detects each particle independently. Track-Seeding describes the process of associating hits of different layers to a track candidate. That leads to an incredibly large set of possible combinations.

Simulation of an event in the ATLAS Inner Tracker (ITk) Detector [1].

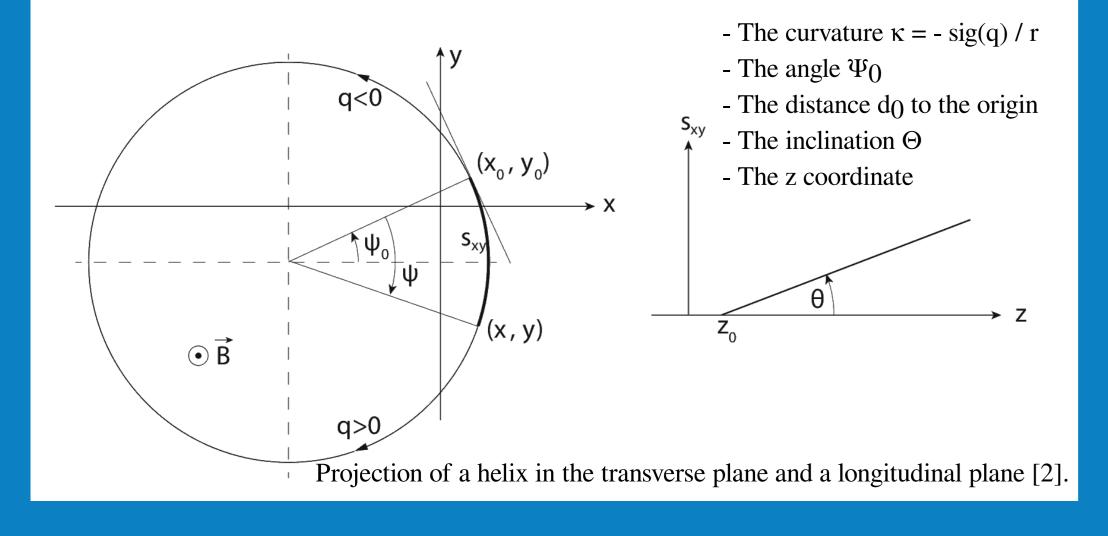

## Second problem is the complexity of a non-linear five parameter fit:

## ATLAS-TDAQ dataflow and datarate

| Detector System                                                  | Level 0 Trigger rate of 1 MHz.                                                                                      |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|--|--|

| Inner Tracker Calorimeters Muon System                           | The detector is divided up into several regions and the data is distributed over 576 PRMs.                          |  |  |

| Data Aquisition System Readout Dataflow                          | Each Track-Fitter gets a event<br>rate of 270 KHz.                                                                  |  |  |

|                                                                  | $\xrightarrow{\text{Permanent Storage}} \text{That corresponds to a rate of} \\ \text{matched patterns of 80 MHz.}$ |  |  |

| Event Filter System                                              | Originally, the Hardware-Track-Trigger (HTT) was de-                                                                |  |  |

| Processor Farm HTT                                               | signed to be also usable as part of a Level 1 Trigger. That                                                         |  |  |

| imposed a latency requirement of $\approx 1 \mu s$ onto the PRM. |                                                                                                                     |  |  |

Firmware Diagram of the PRM [4].

Photograph of the HTT-PRM prototype board [5].

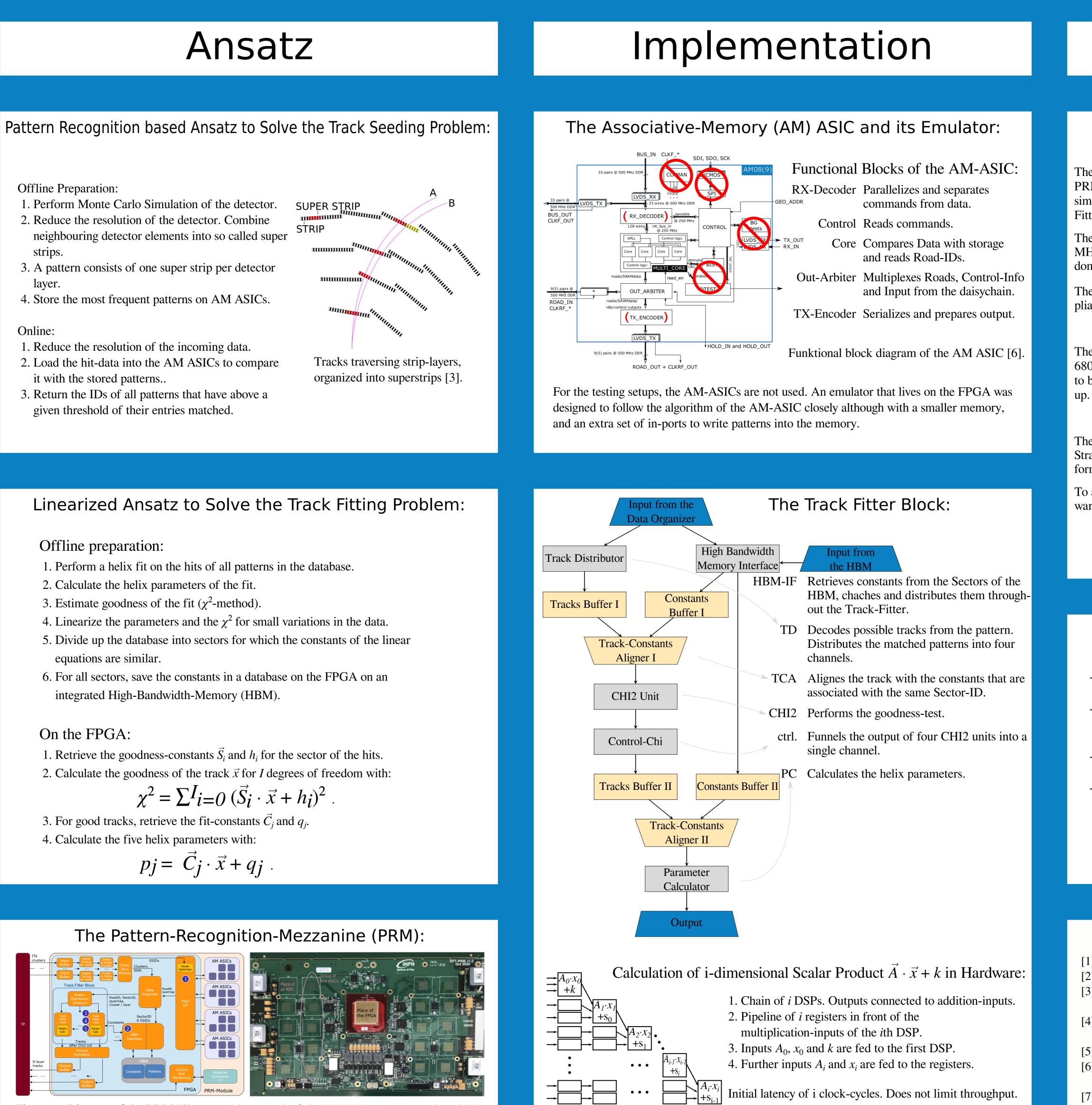

| Input from the<br>Data Organizer                                                                                                                   | The Track Fitter Block:                                                                                 | To achieve the ware, further              |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------------------|

| stributor High Bandwid<br>Memory Interf                                                                                                            |                                                                                                         |                                           |

| Buffer I     Constants       Buffer I                                                                                                              | HBM, chaches and distributes them through-<br>out the Track-Fitter.                                     |                                           |

| Track-Constants<br>Aligner I                                                                                                                       | TD Decodes possible tracks from the pattern.<br>Distributes the matched patterns into four<br>channels. |                                           |

| CHI2 Unit                                                                                                                                          | TCA Alignes the track with the constants that are associated with the same Sector-ID.                   | - The linea<br>type hard                  |

|                                                                                                                                                    | CHI2 Performs the goodness-test.                                                                        | - Even tho                                |

| Control-Chi                                                                                                                                        | ctrl. Funnels the output of four CHI2 units into a single channel.                                      | further de<br>vent filter<br>- Investigat |

| Tracks Buffer II Constants Buffe                                                                                                                   | r II                                                                                                    | ducted.<br>- A publica                    |

| Aligner II<br>Parameter                                                                                                                            |                                                                                                         |                                           |

| Calculator                                                                                                                                         |                                                                                                         |                                           |

| Output                                                                                                                                             |                                                                                                         |                                           |

| Output                                                                                                                                             |                                                                                                         |                                           |

| Calculation of i-dimensional Scalar Product $\vec{A} \cdot \vec{x} + k$ in Hardware:                                                               |                                                                                                         | [1] THE ATI<br>[2] HERMA                  |

| 1. Chain of <i>i</i> DSPs. Outputs connected to addition-inputs.                                                                                   |                                                                                                         | [3] THE ATI<br>ATLAS Ti                   |

| 2. Pipeline of <i>i</i> registers in front of the                                                                                                  |                                                                                                         | [4] THE ATI                               |

| $\begin{array}{c} \bullet \\ \bullet $                     |                                                                                                         | Run 1 of a                                |

| ••• $A_{i-1} \cdot x_{i-1}$ 4. Furt                                                                                                                | her inputs $A_i$ and $x_i$ are fed to the registers.                                                    | [5] PAOLO ]<br>[6] THE AM                 |

| $\rightarrow$                                                                                                                                      |                                                                                                         | Scientific                                |

| $\rightarrow \qquad \qquad$ | atency of i clock-cycles. Does not limit throughput.                                                    | [7] Intel Web<br>develor                  |

PHYSIKALISCHES NSTITU

#### Results and Current State of the Project:

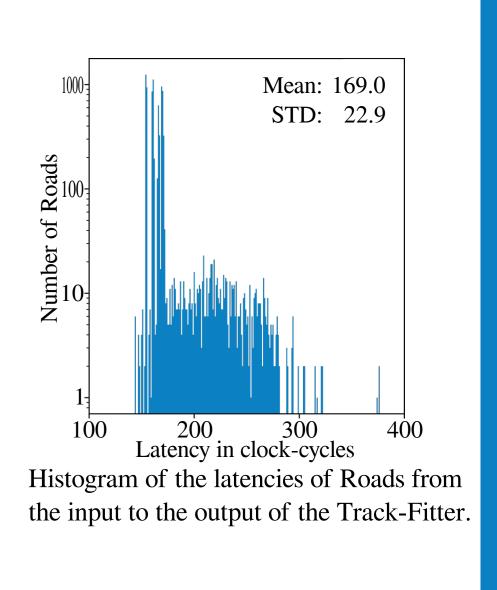

There are two simulation setups: one for the entire PRM with the AM-ASIC emulators and an HBM simulation model, the other one just for the Track-Fitter with an HBM emulator.

The simulation is running with a frequency of 250 MHz. The long-latency regime of the histogram is dominated by the HBM.

The Track-Fitter simulation was shown to be compliant with a road-rate of 80 MHz.

The Track-Fitter simulation has a mean latency of 680 ns. That would fulfills the latency requirement to be used as part of HTT in the Level 1 trigger set-

The PRM successfully runs on a prototype Intel Stratix 10 FPGA, although no tests have been performed with a frequency exceeding 100 MHz.

> he same speed on the prototype hardoptimization would be necessary.

Intel Stratix 10 MX Development Kit [7].

#### Summary and Outlook:

arized track-fitting approach was proven to be viable in simulation and on protod-ware

bugh, the HTT project was cancelled, the design presented here is a starting point for levelopments and can possibly be used in a modified form as part of the ATLAS e-

ations on the performance of the Track-Fitter without the HBM are currently con-

cation about the development of the PRM firmware is in preparation.

#### References:

LAS COLLABORATION: Event Displays from Upgrade Physics Simulated Data; 2018. NN KOLANOSKI & NORBERT WERMES: *Teilchendetektoren*; 2016.

LAS COLLABORATION: Technical Design Report for the Phase-II Upgrade of the *Trigger and Data Acquisition System*; 2018.

LAS COLLABORATION: Performance of the ATLAS Transition Radiation Tracker in *the LHC*; 2017.

FRANCAVILLA: PRM HW Status; 2021

I DESIGN TEAM: Phase-II Associative memory ASIC Specifications and Technical/ *Report*; 2019.

bsite:www.intel.com/content/www/us/en/products/details/fpga/ pment-kits/stratix/10-mx.html; 2022.