# Computer Architecture: Memory Organization and System Design

Deepak Prajapat<sup>1</sup>\*, Saurabh Mittal<sup>2</sup> <sup>1,2</sup>Department School of Engineering, Ajeenkya D.Y. Patil University, Pune, Maharashtra, India

> \*Corresponding Author E-mail Id:-deepak27prajapat@gmail.com

### ABSTRACT

In figuring, a variety of distinct storage components are used to create the memory system of general-purpose computers. This article's goal is to outline how these components are organized and the technologies that are utilized to put them into practice. There are numerous speeds at which semiconductor RAMs can be accessed. Their execution times range from 100 ns to less than 10 ns. Any device group that makes use of PC handling technology uses semiconductor memory. Semiconductor memory is now more widely used, and these memory cards have grown in size as larger and larger amounts of capacity have become necessary. Compared to capacity, which is slower but more inexpensive and has a higher limit, PC memory operates at a high speed. In addition to closing active programs, computer memory serves as a plate storage and composition support for reading and writing operations. As long as running applications do not require it, working frameworks receive the Slam limit in terms of reservation. If essential, items in the computer storage can be moved to backup; Utilizing virtual memory, a type of memory system is a popular way to accomplish this.

Unexpected and non-unstable semiconductor memory is the two basic types. Streak memory, A few examples of non-unstable storage are ROM, PROM, EPROM, and EEPROM. Static irregular access memory (SRAM), which is used for central processor storage, and dynamic arbitrary access memory (Measure), are examples of unstable memory that are used for essential capacity

**Keywords:**– RAM, ROM, Dynamic RAM (DRAM), Erasable Programmable only memory for reads EEPROM, EPROM, and Programmable only memory for reads, Flesh memory, Static Random Access Memory and cache memory.

### **INTRODUCTION**

Memory is the uniqueness of the individual or the material that is encoded, dispersed, and gathered when necessary. If a past event cannot be remembered, the preservation of data across time will determine how future action will be taken. If a past event cannot be remembered, the preservation of data across time will determine how future action will be taken.

Neglect is typically depicted as cognitive decline. A tactile processor, which is part

of memory, is frequently seen as a helpful handling framework with distinct and verifiable functioning. both short-term memory and long-term memory. This may be related to neurons. The tactile processor accommodated various levels of attentiveness and expectation and allowed data from the outside world to be distinguished between synthetic and real boosts. An alternative encoding and recovery processor is working memory. The operating memory processor encodes data as enhancements in accordance with

clear or verifiable capabilities. The working memory can also retrieve info from recently stored material. Last but not least, long-term memory has the ability to store data using several direct models or frameworks.

## RAM

The RAM, or irregular access memory is a sort of semiconductor memory, as its name suggests technology that is used to read and write information in any request in other words, as the processor requires it. Applications like the PC or processor memory use it, where components are stored and expected on an ad hoc basis. Information is frequently stored in and reads from this type of memory. To connect the information lines to the tendency to stockpile for reading or composing the section, RAM incorporates multiplexing and demultiplexing circuitry. Typically, a similar region can reach more than the tiniest bit of capacity, and Smash regularly devices have several information bars and are marketed as "8digit" or "16-bit," for example, devices.

Fig.1:-Example of RAM [2]

## ROM

ROMs are frequently use it for functions and data tabular that must exist when power is first introduced to the computer. ROMs can be classified as either fixed or programmable. Bit patterns for fixed maskor programmable ROMs are preprogrammed into the memory matrix of the chip during manufacturing. specific Transistors are made at intersections between row and column lines using the right photographic mask

Mask-programmable ROMs are only utilised for large-scale manufacture because they are expensive to make in small quantities. Making the data into the ROM at an early stage can require special equipment, depending on the innovation employed in the ROM. Regardless of the method via which the data might typically be changed, this gains the uncommon equipment that is required to destroy the data set up for new data to be written in.

Fig.2:-Example of ROM [3]

#### STATIC RAM

Arbitrary Access Memory that is static. This particular type of semiconductor memory gets its name from the fact that, not at all like Measure, the data shouldn't even be concerned about being successfully revived. It can continue immediate examination and creation processes faster than Measure (generally 10 ns as opposed to 60 ns for Measure), and because it does not have to halt when it reaches a destination, the length of its action is also significantly shorter. It uses more energy and isn't as thick but is more costly because of this, measure. Because of this, it is typically utilised for saves, whereas Measure is the fundamental breakthrough in semiconductor memory.

Fig.3:-Example of SRAM [4]

On the opposite hand, a virtual machine called a static RAM uses the same CPU's logic components. Bitwise values are stored in an SRAM with conventional flip-flop logic-gate topologies. (For further information about flip-flops, read books). As long as power is provided, a static RAM will continue to store its contents. SRAM's power consumption varies significantly depending on how frequently it is accessed.

### DYNAMIC RAM

Each digit of information is stored in a memory cell via a type of computer memory known as dynamic unpredictable access memory. generally opted for metal-oxide-semiconductor (MOS) enhancement, consistently containing a small capacitance and a semiconductor

Fig.4:-Example of DRAM [5]

The supporting refresh circuitry is necessary for a DRAM. In greater memory, the reduced fixed cost of DRAM units more than offsets the higher set price of the update circuits. DRAMs are typically preferred for big memory space as a result. SRAMs are a bit quicker than DRAMs, which brings us to our final point. Because of these comparative traits, Memory for caches is made of SRAM (both on and off-chip), and main memory is made of DRAM. Without assistance, the information on the capacitor would eventually be lost since the electric charge

on the capacitors dependably transmits away. In order to prevent this, Activity needs an external memory to restore the circuit that occasionally modifies the data stored in the capacitors, returning them to their outstanding charge The primary characteristic of dynamic arbitrary access memory is this restore cycle, rather than static irregular access memory (SRAM), which does not expect data to be animated. The measure is irregular memory as opposed to streak memory (versus non-shaky memory), as it loses its info quickly when electricity is wiped out. Measure, however, reveals limited data persistence.

### PROM

The PROM can only be worded once and is non-volatile. An outside source or customer can complete the electrically powered writing operation for the PROM after the initial chip manufacture. To facilitate authoring or programming, specialized equipment is needed. PROMs offer convenience and flexibility. The ROM is still desirable for large-scale production runs. An equivalent to readonly storage is read-mostly storage. This is helpful for applications that require non-volatile media but when reading occurs significantly more frequently than writing.

Fig.5:-Example of PROM [6]

computerized memory called а А programmable read-just memory (PROM) allows the contents to be altered once the device has been made. The information is then permanent and unchangeable. It is one kind of perused just memory (ROM). In computerized electrical objects, such as small-code or firmware, the data is composed into a ROM during manufacture, which is a major difference from a typical ROM. whereas with a PROM, the data is altered after production. Subsequently, ROM will often only be used for large creation runs with completely verified information. When the volume required prevents a plant-customized ROM from being effective, PROMs may be used, or when creating a framework that will eventually be totally converted to ROMs in a wellproduced version.

## **EPROM**

Electrical signals are used to read and write data from optically erasable programmable read-only memory (EPROM), similar to PROM. But prior to a write operation, by exposing the chip packed to Ultraviolet light, It is necessary to reset each collection cell to its start point.

To delete data, a window cut into the memory stick is exposed to a powerful UV light. It can take as much as twenty minutes to finish one wiping. This erase procedure can be repeated. So, Multiple changes can be made to the EPROM and hold its data for almost as long as the ROM and PROM. For equal amounts of backups, the price of the EPROM exceeds that of the PROM. However, it has the advantage of allowing for numerous revisions. The simple integrated quartz (or pitch, on later versions) window on the topmost point of the bundle successfully makes EPROMs stand out, this allows for openness to bright light when erasing and via which the silicon chip is visible.

Fig.6:-Example of EPROM [7]

#### **EEPROM**

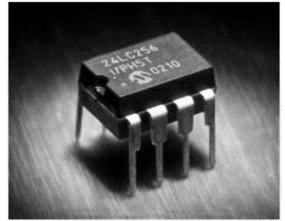

A more desirable variety of read-mostly memory is electrically erasable programmable read-only storage (EEPROM). Updates to this read-only memory can be made at any moment without wiping out previous data; the only modified bytes are the ones that were addressed. a few hundred microseconds per byte around, the read procedure is faster, but the write operation is much slower. the use of conventional bus control, data and address. The advantages of nonvolatility are combined in the EEPROM with the adaptability being capable of updates while in use in contrast to EPROM. A smaller number of bits can be supported per chip and EEPROM is much costlier. Combinations of semiconductors from drifting doors make EEPROM. The drifting up door semiconductors that make up EEPROM are coordinated. Initially, EEPROM could only perform single-byte tasks, which made them slower; however, modern EEPROM now supports multi-byte page operations. A current EEPROM has a limited lifespan for erasing and rebuilding data, which is currently 1,000,000 jobs. The presence of the EEPROM is a convincing plan thought in an EEPROM that is periodically rebuilt.

Fig.7:-Example of EEPROM [8]

### FLASH MEMORY

A different kind of semiconductor memory is called flash memory. Beginning in the midst of the 1980s, flash memory falls between comparing the pricing and functionality of an EPROM and an EEPROM. A similar electrical erasing method is used by flash memory and EEPROM. Flash memory can be entirely cleaned in a fraction of the time compared to an EPROM. It is also possible to erase storage sections instead of a full chip. Because a microchip may erase a block of memory cells in a single operation or "flash," this is how the term "flash memory" is derived. Flash memory, however does not support byte-level erasing. Like EPROM, a portable per bit is all that flash memory needs, and a way that it achieves the high density of EPROM (relative to EEPROM).

Fig.8:-Example of Flesh Memory [9]

### MEMORY INTERLEAVING

Pipeline and vector killing usually call for simultaneous access to memory from at least two sources. A navigation pipeline may need the simultaneous delivery of a guide and input from two different fragments. Similarly, to this, a pipeline used for computing numbers typically needs at least two operands to enter it at the same time. The space can be partitioned into different modules linked to a standard space address and information transports rather than using two space means of transport for simultaneous access. A space module is a space cluster with its own registers for position and data.

The benefit of a measured space is that it enables the use of a tactic known as interleaving. Various space modules in an inter-leaved space are given different sets of addresses. The event addresses might be in one unit and the odd addresses in the other, for instance, in a two-set system.

### HIERARCHICAL MEMORY ORGANIZATION CONCEPT:

There are two different types of this memory hierarchy design:

1. Peripheral storage devices are found in the external space, commonly referred to as the second region such as magnetic discs, A processor input and output unit provides access to magnetic media, optical media, and other media.

2. Primary or inner space includes the CPU's registers, the main area, and the cache area. This region has immediate access to the slaughter.

#### Cache Memory

Between the primary memory and the central processing unit, there is a little but incredibly quick memory called the cache memory. Its goal is to make the processor think that the main memory is much faster than it actually is. The viability of this approach depends on a property of PC programs called the region of reference.

Examination of projects shows that the vast majority of their execution time is

spent in schedules in which numerous directions are executed over and over. These guidelines might comprise a basic circle, settled circles, or a couple of systems that over and over call one another. A "miss" occurs and the slower memory is accessed in the event that the information is not present in the cache. The information is recovered from primary memory following a miss and kept in memory space in case it will be required again shortly. At the point when the store is full and a memory word (guidance or information) that isn't in the reserve is referred to, the reserve control equipment should conclude which block ought to be eliminated to make space for the new block that contains the referred to word. The assortment of rules for going with this choice comprises the reserve's substitution calculation.

## CONCLUSION

Memory is a machine or system used in processing that stores data for assured usage in a computer or related equipment and computerized electronic machine. The terms "memory" and "essential capacity" or "primary memory" are commonly used interchangeably. The term "store" is the archaic counterpart to the word "memory". Compared to slower, cheaper, and highercapacity capacity, PC memory operates more quickly. In addition to closing open programs, In order to work on both reading and writing execution, Desktop memory serves as a plate keep and compose cradle. As long as running code does not necessitate it, working libraries are given a storage limit.

## REFERENCES

- 1. Jameson A, Martinelli, L., Vassberg, J.C. The memory management of computer fundamental. *International Committee of Aeronautical Sciences*, 2019.

- 2. Duesterwald, E., Cascaval, C., Dwarkadas, S. Portraying and

PredictingProgram Conduct and Its Fluctuation. (2018). Proc.12th Int'l Conf. Equal Structures and Compilation Techniques(PACT 03), IEEEPress: 220-231.

- 3. Bose, P.(2019). Computer Designing Handbook, V. Oklob-dzija, ed., CRC Press.

- 4. Srinivasan V(2018). The power of advancing pipelining and Execution. Proceedings of the 35th ACM/IEEE International Symposium on Microarchitecture (MICRO-35), IEEE CS Press :333-344.

- 5. Zruban P.(2004). The architectural part of computer. IEEE Trans. PCs, vol.53, no.8, August 2004, pp. 1004–1016.

- 6. Bose, P. (2001). Designs for Low Power. Computer Designing Handbook. V. Oklob-dzija, ed., CRC Press.

- Creeks D, Martoanosi, M(2015). Advanced functional part of computer. ACM Trans. ComputerSystems,18(2): 89-126, are the authors of the study referenced in [8].

- 8. Power-efficient issue queue design. *Power Aware Computing*, 35-58.

- 9. Streams D.M.(2018). Power-Mindful Microar-chitectures: Plan and Difficulties for Cutting edge Microchips.20(6):26-44.

- Skadron K. et al.(2015). Temperature-Mindful Com-puter Frameworks: Open doors and Challenges. IEEE Miniature. 23(6):52-61.

- 11. ].Fu Z. (2018). Micro-architectural Techniques for Power Gating of Execution Units. *Process International Symp. Low Power Devices and Design*(ISLPED 04), IEEE Press:32-37.

- Hu Z, Kaxiras, S. and Martonosi, M.(2002). LetCaches Rot: Lessening Spillage Energy via Abuse of Store Generational Behavior. ACM Trans. PC Systems.20(2):161-190.

- 13. Tendler J.(2019). Power for Structurul Scaled bottom architecturul, *IBM J. Research and Makement*, 46(1):5-26.

- Kalla, R,. Sinharoy, B,. Tendler, J(2016). IBMPower5 Chip: A Double Center Multithreaded Processor. IEEE Miniature.24(2).: 40-47.

- 15. Carlson W.W.(2019). Prologue to UPC andLanguage Specification, tech. report CCS-TR-99-157, Lawrence Livermore Nat'l Lab., 2019.

- 16. "A Multi-Stage Co-Exhibit Fortran Compiler," Proceedings of the Thirteenth International Conference on Parallel Architectures and Assemblage Techniques (PACT 04), IEEE CS Press, 2021, pp. 29–40.

- 17. Vectorization for SIMD Structures with Alignment Limitations, A.E. Eichenberger, P. Wu, and K. O'Brien, Proc. ACM SIG-PLAN Conf. Programming Language Designand Implementation(PLDI 04), ACM Press, 2016, pp. 82–93..

- R.C. Whaley, A. Petitet, and J.J. Dongarra, "Automated Observational Improvement of Delicate product and the Map book Undertaking," Equal Com-puting, vol. 27, no. 1-2, Jan. 2018, pp. 3-35.

- 19. Yotov K. (2018). An Examination of Empiricaland Model-Driven Enhancement. Proc. ACMSIGPLAN Conf. Programming LanguageDesign and Implementation(PLDI 03), ACMPress, :3-76.

- 20. Allen R, Kennedy K.(2019). Enhancing Com-pilers for Current Models, Morgan Kaufmann..