# A Wideband High-Gain Power Amplifier Operating in the D Band

Vasileios Manouras

School of Electrical and Computer Engineering

National Technical University of Athens

Athens, Greece

vasileiosmanouras@mail.ntua.gr

Ioannis Papananos

School of Electrical and Computer Engineering

National Technical University of Athens

Athens, Greece

papan@elab.ntua.gr

Abstract—In this paper the design, analysis and implementation of a 3-stage, broadband power amplifier (BPA), is presented. The device is suitable for medium-distance wireless and wireline gigabit communication in the D-band (110 – 170 GHz). A pseudo-differential cascode topology is adopted for each stage leading to optimized broadband performance. The PA is integrated in a 0.13  $\mu m$  SiGe BiCMOS technology with  $f_T/f_{max} = 250/370$  GHz, achieving a saturation output power  $P_{sat} > 9$  dBm and a maximum large-signal power gain  $G_P > 29.5$  dB, over the entire D-band. The chip size is  $1.150 \times 0.467$  mm<sup>2</sup> including all pads.

Keywords—D-band power amplifier, broadband amplifier, differential cascode PA, 6G, 145 GHz, SiGe PA.

#### I. INTRODUCTION

The ever increasing demand for higher data-rate communications, supporting applications beyond current mobile use scenarios, such as short-range gigabit communication over dielectric waveguides [1], medical imaging, and biosensing [2], impelled research community to a further investigation of the sub-THz region [3]. Currently, referring to the high mm-wave band of 5G auctions, the developed systems use 28 GHz, while some additional bands up to 100 GHz, are planned [4]. However, higher frequency bands up to 300 GHz attract unique attention for the further data-rate extension, arising the potential of beyond 5G and 6G systems [5].

One of the most critical parts of the mm-wave and sub-THz transmitter chain in terms of maximum output power, linearity and broadband behavior, is the PA [6]. Highly linear silicon PAs operating in D-Band, able to provide reasonable output power back-off (OPBO) for wide frequency range in order to support modulated signals with bandwidth up to tens of GHz, is challenging because of the limited power performance of the transistors.

In this paper a 3-stage, pseudo-differential, broadband, cascode PA is presented. Based on the EM simulations of the designed passive structures, the PA achieves an almost flat and broadband response over the entire D-band. The paper is organized as follows: In Section II, key characteristics concerning the used SiGe process are presented with emphasis on the HBTs' performance. In Section III, the proposed D-band PA architecture is introduced, while the simulation results are denoted in Section IV.

This work was financially supported by Infineon Technologies AG. Infineon Technologies also provided the fabrication of the designed integrated circuit. Furthermore, this work was partially funded by the H2020-ICT-07-2018 Project No. 824962 "Car2TERA".

### II. HBT PERFORMANCE CAPABILITIES

The proposed D-Band PA was designed and fabricated in Infineon's 130 nm SiGe BiCMOS process. The layer stackup profile includes 6 copper metal layers and 1.0 µm aluminum layer as top metal. Moreover, the technology offers heterojunction bipolar transistors (HBTs) with breakdownvoltages  $BV_{CEO} = 1.8 V$ ,  $BV_{CBO} = 5.3 V$  and a maximum unity gain frequency  $f_T$  as well as a maximum frequency of oscillation  $f_{max}$  of 250 GHz and 370 GHz, respectively, making the designing of mm-wave integrated circuits (ICs) for 5G-and-beyond applications, feasible. However, aiming to D-Band applications, a careful selection of the size and configuration of the active modules (HBTs) is required not only due to inherent trade-off between break-down voltages and maximum speed [7] but also because of the reliability of the provided HBT models from the foundry at such high frequencies.

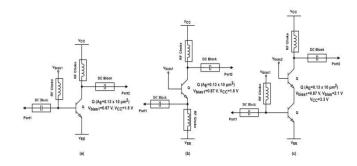

The maximum available/stable gain (MAG/MSG) for the common emitter (CE) (Fig. 1a), common base (CB) (Fig. 1b) and cascode topology (CT) (Fig. 1c) are shown in Figure 1d. For comparison reasons, all the aforementioned topologies are consisted of the same HBT in multi-base configuration with an emitter mask size of  $A_{eff} = 0.22 \times 10 \ \mu m^2$ .

The MAG/MSG simulation results of the various amplifying topologies demonstrate that the CT shows superior power gain in D-band  $(110-170\ GHz)$  at the expense of higher supply voltage and thus power consumption. Since, the proposed PA is intended for the RF front-end of a high-data rate wireline link in which the preceding Mixer block drives the PA with limited power, the highest possible power gain of the latter is necessary, leading us to the CT selection for our main active module. Furthermore, CT offers an inherent reduction of Miller's effect, enforcing the stability of our amplifying core [8].

**Fig 1.** Schematic of (a) common-emitter (CE), (b) common base (CB), (c) cascode topology (CT). (d) Maximum Available/Stable gain (MAG/MSG).

### III. D-BAND PA ARCHITECTURE

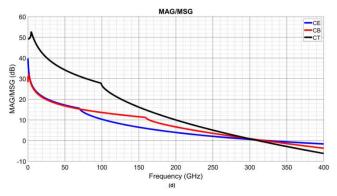

The proposed D-Band PA is shown in Figure 2. It is consisted of 3 pseudo-differential, cascode stages aiming to a broadband behavior of a 3-dB bandwidth up to 50~GHz, able to support high-data rate modulated signals with high peak-to-average power ratios (PAPR). Inductive  $g_m$  boosting technique is used in order to enhance the maximum available power gain. The single-to-differential conversion in both input and output is performed via Marchand Baluns (MBL), described in subsection III-B.

### A. Broadband PA Design Consideration

Aiming to the highest possible saturated power as well 1dB compression point, the double base (BEBC) HBTs of each cascode stage have the same emitter size of  $A_{eff} = 0.22 \times 10 \ \mu m^2$ , while each one of the CE HBTs is biased via 200  $\Omega$  TaN resistors ( $R_b$ ) at the optimum current density of  $J_{copt} = 11.5 \ mA/\mu m^2$  for maximum  $f_T$ , leading the cascode topology to a Class A operating point. Such a bias condition offers maximum linearity and output power for the desired 1st harmonic at the expense of power consumption. Since the transmission of broadband modulated signals with data rates up to tens or hundreds of Gbps requires the highest possible linearity both in terms of frequency and power, the conventional Class A operation offers a safe yet effective choice [8].

The 3 stages of the designed PA are based on a peudo-differential topology that provides excellent stability through the exploitation of the AC virtual grounds. Furthermore, it offers higher power gain compared to a conventional differential stage, since it takes advantage of the larger output voltage swings, via the elimination of the tail current source. It should be noted that much higher voltage swings compared to  $BV_{CEO}$  can be applied on the CB HBT, if its base node provides a low impedance path to ground, accomplished by decoupling capacitors.

Several techniques can be used to further increase the power gain of the cascode topology, based on the compensation of the voltage and frequency-depended collector-base capacitance  $C_{CB}$ . The majority of these techniques use positive or negative feedback on the CB stage of the cascode topology [6]. However, feedback should be used with caution, since the base node of the CB active module is sensitive to stability issues. In this work, a kind of inductive positive feedback is used  $(g_m$  boosting technique) through the insertion of a 5pH inductor  $L_b$  on the base of each CB HBT of the differential cascode stages, as Figure 2 shows.

A D-band design pushes the HBTs operating close to  $f_{max}/2$ , where the via contacts and intrinsic interconnects of the HBTs can be proven crucial not only to efficiency but also, to the optimal selection of the load of the various stages. Thus, the via interconnects were EM simulated and their effects were taken into consideration for an accurate modelling of the HBTs. Additionally, the optimum load of the output stage  $R_{opt}$  was determined via Load-Pull simulations at the middle frequencies of the D-Band. The impedance transformation to the 100  $\Omega$  differential termination was performed though the output matching network (OMN), consisted of 50  $\Omega$  transmission lines ( $TL_{2,3,4}$ ) and MIM capacitors ( $C_1$ ).

The broadband behavior of the proposed PA is based on the stagger tuned amplifier theory, described in [9] and it is realized via the inter-stage matching networks (ISMN) which comprises the  $50\,\Omega$   $TL_{5,6,7}$  and  $C_2$ . It is worth mentioning that the accurate modelling of the passive matching networks is necessary in order to achieve the desired gain behavior over frequency. Therefore, the ISMNs were EM simulated over the whole band of interest and all the existing cross-talk and coupling effects were taken into consideration.

Fig 2. Schematic of the proposed D-Band PA.

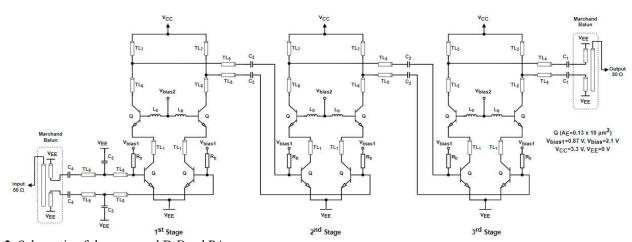

The contribution of each stage in the final simulated small-signal gain is shown in Figure 3. As follows, the combination of the output stage (3<sup>rd</sup>) and the intermediate stage (2<sup>nd</sup>) generates the broadband behavior of the proposed PA, while the input stage (1<sup>st</sup>) contributes to gain flatness over the entire D-band.

**Fig 3.** Small-signal gain of the various PA stages over the D-band.

As for the input matching between the differential  $100~\Omega$  output of the MBL and the bases of the CE HBTs of the first stage, the  $50~\Omega$  transmission lines  $TL_{8,9}$  and MIM capacitors  $C_{3,4}$  are used, since compared to a conventional T-type network, provide a wideband matching. Table I summarizes the values of the PA's passive components.

TABLE I

SUMMARY OF THE PASSIVE COMPONENTS

| $TL_1$ | 16.4 μm | $TL_9$          | 168 μm      |  |  |

|--------|---------|-----------------|-------------|--|--|

| $TL_2$ | 56.4 μm | $\mathcal{C}_1$ | 80 fF       |  |  |

| $TL_3$ | 67 μm   | $C_2$           | 60 fF       |  |  |

| $TL_4$ | 51 μm   | $C_3$           | 85.6 fF     |  |  |

| $TL_5$ | 37.1 μm | $C_4$           | 30.3 fF     |  |  |

| $TL_6$ | 88 µm   | $L_b$           | 5 <i>pH</i> |  |  |

| $TL_7$ | 38 µm   | $R_b$           | $200\Omega$ |  |  |

| $TL_8$ | 38.6 µm | •               |             |  |  |

# B. Marchand Balun Design

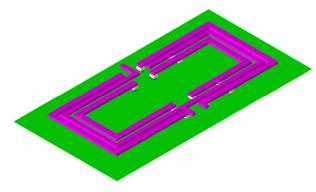

Several on-chip, transformer-based and Marchand Baluns that perform the required single to differential conversion at the D-band, have been published recently [2], since the measurements for differential circuits in sub-THz frequencies are, in general, performed single-ended [10]. Figure 4 shows the 3D view of the MBL used in this work and based on [11].

Fig 4. 3D view of the designed Marchand Balun (MBL).

The signal path is realized with the top copper layer (M6) for the minimization of the resistive losses and the capacitive coupling to ground, while the bottom layer (M1) is used as return path, providing a well-defined reference ground plane and thus enforcing the accuracy of its EM simulation. In order the MBL to perform the single to differential conversion, the M6 lines are placed in close proximity for a strong inductive and capacitive coupling between them.

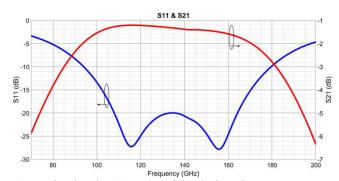

Figure 5 shows the simulated S11 and S21 of the designed MBL. For the s-parameter simulation,  $50 \Omega$  and  $100 \Omega$  terminations were used in the unbalanced and balanced port, respectively. Simulation results denote that the presented MBL shows a broadband behavior with S11 < -15 dB and an almost flat S21 for the entire D-band. Furthermore, it is worth mentioning that the simulated insertion loss is around 1.5 dB for the same frequency band.

Fig 5. Simulated S11 & S21 of the designed MBL.

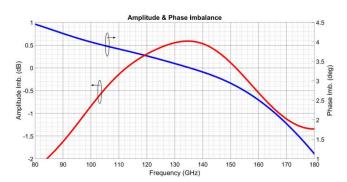

Considering the designed MBL as a 3-port network, the simulated amplitude and phase imbalances between the differential ports are shown in Figure 6. The balun shows an amplitude imbalance ranged from -1.5 to  $1\,dB$  as well as a phase imbalance between -2.5 and 4 degrees, over the entire D-band.

**Fig 6.** Simulated amplitude and phase imbalances of the designed MBL.

## IV. CHIP FABRICATION & SIMULATION RESULTS

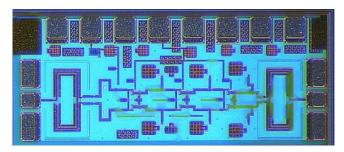

Figure 7 shows the photograph of the chip fabricated in 130 nm SiGe process from Infineon. The chip area is  $1.150 \times 0.467 \ mm^2$ , including the MBLs and all the rf pads. The small/large- signal measurements for the presented D-band balanced cascode amplifier are pending.

Fig 7. Chip photograph.

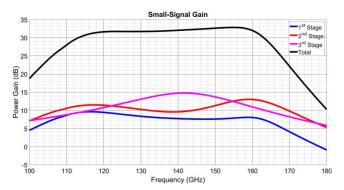

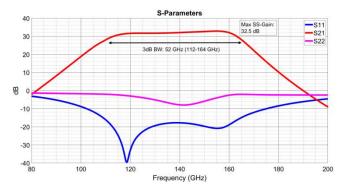

The simulated s-parameters of the total 3-stage PA design are presented in Figure 8. The S21 plot shows a 3dB bandwidth of 52 GHz, covering almost the entire D-Band and ensuring the wideband behavior of the presented PA. Moreover, the maximum S21 is almost flat at 32.5 dB, while  $S11 < -18 \, dB$  in the range  $105 - 162 \, \text{GHz}$ . The PA is unconditionally stable over all frequencies.

Fig 8. Simulated S-parameters of the designed PA.

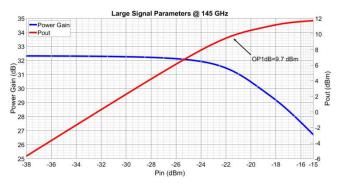

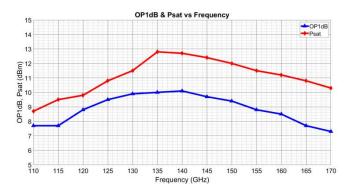

As for the large-signal simulation (Fig. 9), the proposed PA exhibits a large signal Power Gain > 32 dB at the operating frequency of 145 GHz, as well as an output 1-dB compression point  $OP_{1dB} \approx 9.7 \ dBm$  and a saturation delivered power  $P_{sat} \approx 12.4 \ dBm$ . Furthermore, Figure 10 shows the  $OP_{1dB}$  and  $P_{sat}$  over the D-band.The results denote that the designed PA performs high enough  $OP_{1dB} > 7 \ dBm$  and  $P_{sat} > 9 \ dBm$  for the whole band of interest. Other important specifications arising from our simulations results at 145 GHz, are the  $IIP_3 \approx -14 \ dBm$  as well as the  $PAE \approx 5 \%$ . The power consumption  $(P_{DC})$  of our PA approaches 345 mW.

**Fig 9.** Simulated *Power Gain* and  $P_{out}$  versus Input Power  $P_{in}$ .

Fig 10. Simulated  $OP_{1dB}$  &  $P_{sat}$  over frequency.

Table II shows the performance summarization and the comparison with other state-of-the-art D-band PAs, fabricated in 130 nm SiGe processes.

TABLE II COMPARISON TABLE OF PUBLISHED D-BAND PAS FABRICATED IN SIGE BICMOS PROCESS

| Reference      | BW<br>(GHz) | f <sub>T</sub> / f <sub>max</sub><br>(GHz) | Topology                | SS-Gain<br>(dB) | P <sub>sat</sub><br>(dBm) | OP1dB<br>(dBm) | PAE<br>(%) | P <sub>DC</sub><br>(mW) | Area<br>(mm²) |

|----------------|-------------|--------------------------------------------|-------------------------|-----------------|---------------------------|----------------|------------|-------------------------|---------------|

| This<br>Work** | 52          | 250/370                                    | 3-stage<br>differential | 32.5            | 9-13                      | 7-10           | 5          | 345                     | 0.537         |

| [12]*          | 60          | 300/500                                    | 3-stage<br>single-ended | 21              | 11.8-13.9                 | 9.2-12.5       | 5.1        | 379                     | 0.3           |

| [6]*           | 49          | 250/300                                    | 5-stage<br>differential | 27              | 12-14                     | -              | 5.5        | 440                     | 0.48          |

| [13]*          | 80          | 250/370                                    | 4-stage<br>differential | 24.8            | 7.5-11                    | -              | 4.8        | 262                     | 0.42          |

| [14]*          | 25          | 300/500                                    | 4-way<br>combining      | 30.2            | 18                        | 15.6           | 4          | -                       | 0.85          |

| [15]*          | 21          | 300/500                                    | 2-stage<br>single-ended | 16.7            | 15                        | 11             | 7.8        | 300                     | 0.44          |

| [16]*,+        | 34          | 320/370                                    | 4-stage<br>single-ended | 24              | 17.6                      | 16.8           | 17.5       | 286                     | 0.18          |

| [16]*,+        | 25          | 320/370                                    | 4-stage<br>differential | 22.4            | 19.3                      | 18.5           | 13         | -                       | 0.26          |

<sup>\*</sup> measurement results

\*\* simulation results

#### V. CONCLUSION

This brief presents a high-gain, 3-stage, broadband PA, integrated in a 130 nm SiGe BiCMOS process, suitable for D-band applications. The cascode, pseudo-differential topology is used as the main amplifying core, while gm boosting technique is adopted for further gain enhancement. The PA achieves a record simulated power gain of 32.5 dB in an operating bandwidth of 52 GHz.

## REFERENCES

- J. W. Holloway, G. C. Dogiamis and R. Han, "11.9 A 105Gb/s Dielectric-Waveguide Link in 130nm BiCMOS Using Channelized 220to-335GHz Signal and Integrated Waveguide Coupler," 2021 IEEE International Solid- State Circuits Conference (ISSCC), 2021, pp. 196-198

- [2] H. Li et al., "A 250-GHz Differential SiGe Amplifier With 21.5-dB Gain for Sub-THz Transmitters," in IEEE Transactions on Terahertz Science and Technology, vol. 10, no. 6, pp. 624-633, Nov. 2020.

- [3] M. Kucharski, J. Borngraber, D. Wang, D. Kissinger and H. J. Ng, "A 109–137 GHz power amplifier in SiGe BiCMOS with 16.5 dBm output power and 12.8% PAE," 2017 12th European Microwave Integrated Circuits Conference (EuMIC), 2017, pp. 281-284.

- [4] K. Okada, "CMOS THz Phased-Array Transceivers for Beyond 5G," 2021 IEEE International Symposium on Radio-Frequency Integration Technology (RFIT), 2021, pp. 1-2.

- [5] P. Rodríguez-Vázquez, J. Grzyb, B. Heinemann and U. R. Pfeiffer, "A 16-QAM 100-Gb/s 1-M Wireless Link With an EVM of 17% at 230 GHz in an SiGe Technology," in IEEE Microwave and Wireless Components Letters, vol. 29, no. 4, pp. 297-299, April 2019.

<sup>\*\*</sup> simulation results +55 nm SiGe BiCMOS

- [6] M. Furqan, F. Ahmed, B. Heinemann and A. Stelzer, "A 15.5-dBm 160-GHz High-Gain Power Amplifier in SiGe BiCMOS Technology," in IEEE Microwave and Wireless Components Letters, vol. 27, no. 2, pp. 177-179, Feb. 2017.

- [7] X. Xu et al., "A 28 GHz and 38 GHz High-Gain Dual-Band Power Amplifier for 5G Wireless Systems in 22 nm FD-SOI CMOS," 2020 50th European Microwave Conference (EuMC), 2021, pp. 174-177.

- [8] S. C. Cripps, "Linear Power Amplifier Design," in RF Power Amplifiers for Wireless Communications, 2nd ed., Norwood, MA, USA: Artech House, 2006, pp. 27–31.

- [9] S. Voinigescu, "High-frequency devices," in *High-Frequency Integrated Circuits*, Cambridge, U.K.: Cambridge University Press, 2013, pp. 335-336.

- [10]A. -M. Schrotz et al., "Design Methodology for Automatically Designed, Integrated Marchand Baluns with Low Insertion Loss at Lowest Phase Imbalance," 2019 IEEE Asia-Pacific Microwave Conference (APMC), 2019, pp. 771-773.

- [11]A. Ali, J. Yun, H. Jalli Ng, D. Kissinger, F. Giannini, and P. Colantonio, "High Performance Asymmetric Coupled Line Balun at Sub-THz Frequency," Applied Sciences, vol. 9, no. 9, p. 1907, May 2019.

- [12]A. Karakuzulu, M. H. Eissa, D. Kissinger and A. Malignaggi, "A Broadband 110–170-GHz Stagger-Tuned Power Amplifier With 13.5dBm Psat in 130-nm SiGe," in IEEE Microwave and Wireless Components Letters, vol. 31, no. 1, pp. 56-59, Jan. 2021.

- [13]F. Ahmed, M. Furqan, K. Aufinger, and A. Stelzer, "A SiGe-based broadband 100–180-GHz differential power amplifier with 11 dBm peak output power and >1.3 THz GBW," in Proc. 11th Eur. Microw. Integr. Circuits Conf. (EuMIC), Oct. 2016, pp. 257–260.

- [14]M. Kucharski, H. J. Ng and D. Kissinger, "An 18 dBm 155-180 GHz SiGe Power Amplifier Using a 4-Way T-Junction Combining Network," ESSCIRC 2019 - IEEE 45th European Solid State Circuits Conference (ESSCIRC), 2019, pp. 333-336.

- [15]K. Aksoyak, M. Möck, M. Kaynak and A. Ç. Ulusoy, "A D-Band Power Amplifier with 15 dBm Psat in 0.13 μm SiGe BiCMOS Technology," 2022 IEEE 22nd Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), 2022, pp. 5-8.

- [16]Petricli, D. Riccardi and A. Mazzanti, "D-Band SiGe BiCMOS Power Amplifier With 16.8dBm P<sub>1</sub>dB and 17.1% PAE Enhanced by Current-Clamping in Multiple Common-Base Stages," in IEEE Microwave and Wireless Components Letters, vol. 31, no. 3, pp. 288-291, March 2021.