## Performance Analysis of Full Adder using Ganged CMOS Threshold Element with Different Technologies

N. Ramanjaneyulu\*, C. Venkataiah, M. Chennakesavulu, Anchula Sathish Rajeev Gandhi Memorial College of Engineering and Technology, Nandyal, India

> \*Corresponding Author E-Mail Id: rams9ganguly@gmail.com

### ABSTRACT

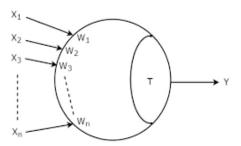

A threshold gate is a type of digital logic gate that has multiple inputs and a single output. The output of the gate is determined by the number of inputs that are at a high (or 1) state. The threshold value, or number of inputs required to be at a high state, is set by the design of the gate. These gates are used in digital circuits to perform Boolean logic operations and are commonly used in computer processors and other digital devices. The inputs are multiplied by weights ( $W_i$ ) and added to produce a resultant sum, which is then compared with threshold value 'T' to get the output Y. The values of weights and threshold should be real, finite, positive or negative numbers. In this paper we have designed a Ganged Complementary Metal Oxide Semiconductor Field Effect Transistor (GCMOS) 1- bit Full-Adder (FA) circuit. For all the simulations, A, B and C<sub>in</sub> are taken as three binary inputs. The major advantage of this Ganged CMOS logic based FA circuit is its simplicity and lower transistor count. The circuit is simulated using Microwind tool with 50nm, 70nm and 90nm CMOS technologies.

Keywords: Threshold logic gate, GCMOS, CMOS, full adder

### **INTRODUCTION**

Synapse is a structure in the nervous system that allows a signal to pass from one neuron to the next or to a target effecter cell. A mathematical function conceived as a model of biological neurons is an artificial neuron. Threshold Logic Gate (TLG) or Linear Threshold Unit was the first artificial neuron proposed by Warren McCulloch and Walter Pitts in

$$Y = \text{Sign} \{F(x)\} = 0, \text{ if } F(x) < 0$$

= 1, if  $F(x) \ge 0$  (1)

Where,  $F(\mathbf{x}) = \sum \mathbf{W}_i * \mathbf{X}_i - \mathbf{T}$

Various logic functions can be implemented just by changing the values of  $W_i$  and T. TLG circuits designed so far used resistor, capacitor, tunnel-diodes, MOSFET, memristor and negative resistance devices. But owing to the 1943[1-5]. A TLG is having more than one binary Inputs and a single binary output. The inputs are multiplied by weights  $(W_i)$ and added to produce a resultant sum, which is then compared with threshold T to get the output Y. The values of weights and threshold should be real, finite, positive or negative numbers. Threshold function can be represented by Eq.1.

extremely low power consumption and fast signal propagation property, CMOS are considered here as the most versatile component

[6-11] also used for designing threshold

### HBRP PUBLICATION

logic gates. Threshold logic-based design can operate at high speed in the range of 400MHz. The logic symbol of TLG is shown in Fig.1.

Fig. 1: Threshold Logic Gate.

#### SYNTHESIS OF THRESHOLD FUNCTIONS

Because threshold gates can be used to implement any Boolean function, they are also referred to as universal gates. It may not always be possible to use a single Threshold gate to implement many logic gates and Boolean functions. Multiple threshold gates may be required in that scenario.

To use a single Threshold gate to implement a Boolean function, follow these steps.

Step1: Create a Truth table for the Boolean function you're given.

Step2: Add one more column to the Truth table above to show the relationship between weighted sums and the threshold value.

Step3: Write down the relationship between the threshold and weighted sums for each  The weighted sum for those input combinations will be greater than or equal to the Threshold value if the Boolean function's output is 1.

The weighted sum for those input

2. The weighted sum for those input combinations will be lower than the threshold value if the Boolean function's output is 0.

Step4: Choose the weights and threshold values in such a way that they should satisfy all of the relationships in the table's last column.

Step5: With those weights and threshold values, draw the Threshold gate symbol.

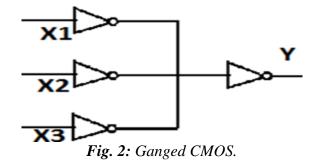

### Ganged-CMOS Logic

Ganged-CMOS logic (GCMOS) is a method that drives one or more encoding inverters by using CMOS inverters with their outputs shorted together. Quantifying the non-binary signal at the "ganged" node with these encoding inverters effectively buffers it from external circuitry, allowing for locally smaller noise margins.

Combination of the following inputs:

### HBRP PUBLICATION

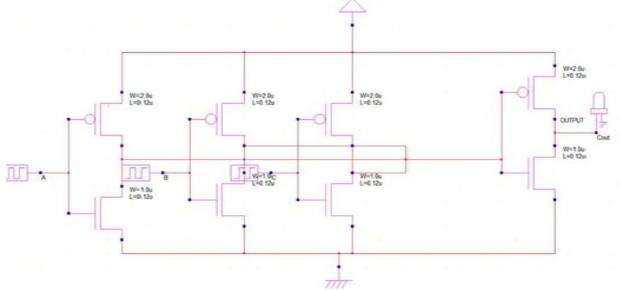

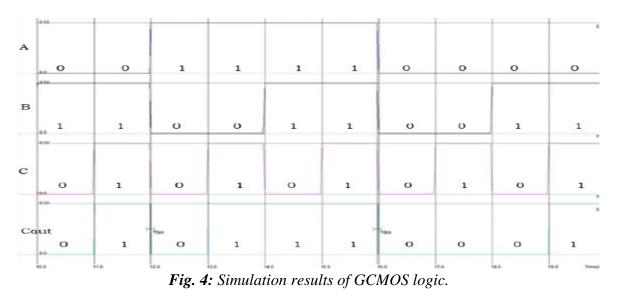

There are a few benefits to buffering the ganged node with a straightforward CMOS inverter. First and foremost, the ganged node is effectively isolated from external circuitry because its value is not transmitted via long interconnect wires and corrupted by noise, nor does it drive complex gates, where a logic error can be caused by voltages exceeding a transistor threshold [12-19]. In essence, noise margins at a local node are much lower than at a global node. The inverter's inherent encoding action, which results in a clear distinction between low and high inputs thanks to its high gain, amplifies this advantage. Additionally, despite the fact that the inverter's switching point is determined by the square root of the p-n ratio. transistor geometries can be sufficiently varied. **GCMOS** logic implementation of three input threshold function is shown in Fig.3 which needs transistors. The schematic eight of **GCMOS** threshold logic element, simulation results and layout is shown in Fig.3, Fig.4 and Fig.5 respectively.

Fig. 3: Realization of GCMOS logic using MOSFET.

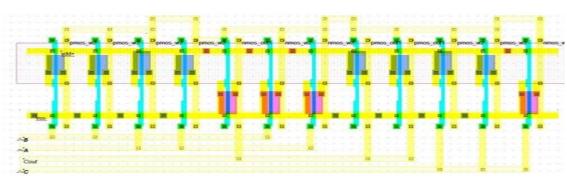

Fig. 5: Layout of GCMOS logic element.

### Full Adder using GCMOS Logic

HBRP

**PUBLICATION**

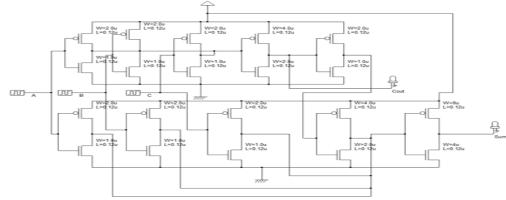

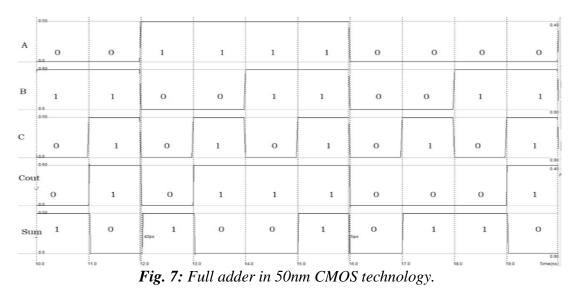

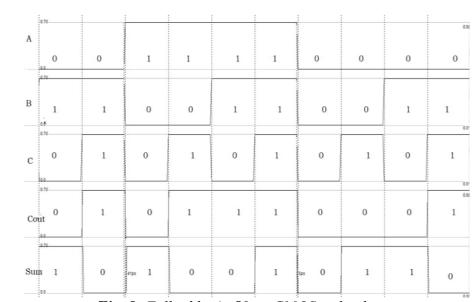

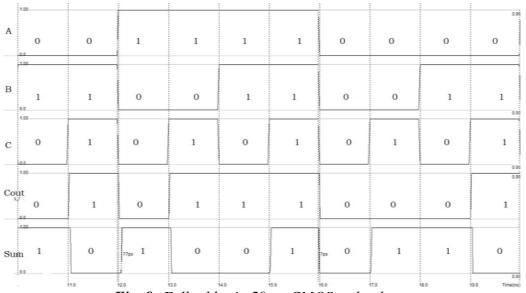

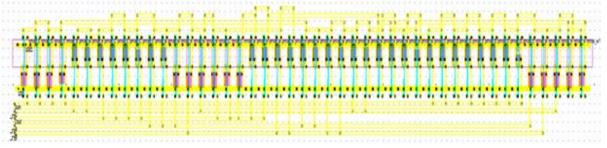

A Full Adder is a digital circuit that performs the operation of addition of two binary numbers. It consists of three inputs (A, B, and Cin) and two outputs (Sum and Cout). The input A and B represents the two binary numbers to be added and Cin is the carry input. The output Sum represents the sum of the two binary numbers and Cout is the carry output.Fig.5 shows the realization of FA circuit using GCMOS Threshold Logic. The realization of Full Adder circuit using GCMOS logic is shown in Fig.6.The simulation results of FA with different technologies as shown in Fig.7, 8 and 9 respectively. Fig.10 shows the Full Adder circuit layout in 50nm CMOS technology.

Fig. 6: Full adder using GCMOS Threshold Logic.

Fig. 8: Full adder in 50nm CMOS technology.

Fig. 9: Full adder in 50nm CMOS technology.

Fig. 10: Full Adder layout in 50nm CMOS technology.

Table 1 shows the simulation results of GCMOS Logic element with different CMOS technologies like 50nm, 70nm and 90nm.

**HBRP**

**PUBLICATION**

Table 2 shows the simulation results ofFullAdderAddercircuitusingGCMOSThresholdLogicLogicelementwithdifferentCMOStechnologieslike50nm, 70nm

# 90nm. The simulation results shows that 50nm technology node gives the 25% accurate than the 70nm and 90nm

technology nodes. It has the less power

HBRP

**PUBLICATION**

consumption, delay time and area is less when compared with 70 and 90nm technologies.

Table 1: Simulation results of GCMOS Threshold Logic element.

| Technology (nm) | Power (mW) | Delay (ps) | PDP (fJ) | Area (nm <sup>2</sup> ) |

|-----------------|------------|------------|----------|-------------------------|

| 50nm            | 0.515      | 46         | 2.575    | 0.02872                 |

| 70nm            | 2.060      | 45         | 12.36    | 0.05583                 |

| 90nm            | 4.247      | 87         | 38.223   | 0.11585                 |

Table 2: Simulation results Full Adder using GCMOS Threshold Logic element.

| Technology (nm) | Power (mW) | Delay (ps) | PDP (fJ) | Area (nm <sup>2</sup> ) |

|-----------------|------------|------------|----------|-------------------------|

| 50nm            | 0.69       | 5          | 3.45     | 0.112                   |

| 70nm            | 2.060      | 6          | 12.36    | 0.223                   |

| 90nm            | 4.535      | 9          | 40.815   | 0.455                   |

### CONCLUSION

In this paper GCMOS Logic threshold element and 1-bit Full Adder circuit using GCMOS threshold Logic element is simulated with different CMOS technologies like 50nm, 70nm and 90nm. The simulation results shows that Full Adder circuit with 50nm technology node gives the 28% accurate than the 70nm and 90nm technology nodes. In this work simulation results are verified using Micro wind tool.

### REFERENCES

- Venkataiah, C., Chennakesavulu, M., Ramanjaneyulu, N., Rao, Y.M., Sathish, A., Jayamma, M. (2023). Ternary logic full adder circuit using 3×1 multiplexer. Journal of advancement in electronics design, 6(1), 1-9.

- 2. Venkataiah, C., Ramanjaneyulu, N., Rao, Y. M., Prakash, V. S., Murthy, M. L., & Rao, N. S. (2022). Design and performance analysis of buffer inserted on-chip global nano interconnects VDSM in technologies. Nanotechnology for Environmental Engineering, 7(3), 775-781.

- Venkataiah, C., Satyaprasad, K., & Jayachandra Prasad, T. (2019). Insertion of an Optimal Number of

Repeaters in Pipelined Nanointerconnects for Transient Delay Minimization. *Circuits, Systems, and Signal Processing, 38,* 682-698.

- **4.** Venkataiah, C., Satyaprasad, K., & Prasad, T. J. (2018). FDTD algorithm to achieve absolute stability in performance analysis of SWCNT interconnects. *Journal of computational electronics*, *17*, 540-550.

- 5. Venkataiah, C., Setty, D.R., Ramanjaneyulu, N., Rao, Y.M. (2023). Crosstalk peak overshoot analysis of VLSI interconnects. *International Journal of Emerging Research in Engineering, Science, and Management, 2*(1), 8-12.

- VENKATAIAH, C., Sathish, A., Ramanjaneyulu, N., & Rao, Y. M. (2023). Peak Overshoot Analysis of On-Chip Interconnects for Different Technologies. *Journal of Advancement in Communication System*, 6(1).

- 7. Venkataiah, С., Sathish, A., Ramanjaneyulu, N., Rao, Y.M. (2023). Crosstalk noise analysis of on-Journal chip interconnects. of advancement in communication systems, 6(1), 1-6.

- 8. Venkataiah, C., Jayamma, M., Rao, Y. M., Ramanjaneyulu, N., & Sathish, A.

(2023). An Advanced Technique for Performance Improvement in VLSI Interconnects. *Journal of VLSI Design and Signal Processing (e-ISSN: 2581-8449)*, 9(1), 1-6.

- Venkataiah, C., Satyaprasad, K., & Prasad, T. J. (2018). Crosstalk Induced Performance Analysis of Single Wall Carbon Nanotube Interconnects Using Stable Finite-Difference Time-Domain Model. Journal of nanoelectronics and optoelectronics, 13(6), 846-855.

- 10. Venkataiah, C., Satyaprasad, K., & Prasad, T. J. (2018). Signal integrity analysis for coupled SWCNT interconnects using stable recursive algorithm. *Microelectronics journal*, 74, 13-23.

- Reddy, R. R. K., & Ramanjaneyulu, N. (2012). High performance cmos schimitt trigger. *International Journal* of Engineering Research and Applications (IJERA), ISSN, 2248-9622.

- Venkataiah, C., Bharathi, C.V., Narasimhulu, M. (2013). Power Efficient Weighted Modulo 2n+1 Adder. International Journal of Computer & Organization Trends, 3(11).

- Reddy, K.V.S., Venkataiah, C. (2012). Design of Adder in Multiple Logic Styles for Low Power VLSI. International Journal of Computer Trends and Technolgy, 3(3).

- 14. SaikumarReddy, C. V., Venkataiah, C., Kumar, V. R., Maheshwaram, S., Jain, N., Dasgupta, S., & Manhas, S. K. (2018). Design and simulation of CNT based nano-transistor for

greenhouse gas detection. Journal of Nanoelectronics and Optoelectronics, 13(4), 593-601.

- 15. Govindarajulu, S., Prasad, T. J., & Ramanjaneyulu, N. (2010). Design of high performance arithmetic and logic circuits in DSM technology. *International Journal of Engineering and Technology*, 2(4), 285-291.

- 16. Ramanjaneyulu, V. N., Satyanarayana, D., & Prasad, K. S. (2017). Design of a Three Stage Ring VCO in 0.18 μm CMOS under PVT Variations. International Journal of Computer Applications, 170(8), 35-39.

- 17. Ramanjaneyulu, N., Satyanarayana, D., & Satya Prasad, K. (2017). Design of a 3.4 GHz Wide-Tuning-Range VCO in 0.18 μm CMOS. In *Computer Communication, Networking and Internet Security: Proceedings of IC3T 2016* (pp. 227-234). Springer Singapore.

- Ramanjaneyulu, N., Satyanarayana, D., Prasad, K.S. (2020). Analysis of a delay cell based Voltage Controlled Ring Oscillator in CMOS. *Journal of Mechanics of Continua and Mathematical Sciences*, 5, 342-356.

- Ramanjaneyulu, N., Satyanarayana, D., Prasad, K.S. (2018). A 3.4 GHz Fast-locking PLL using Transmission Gate charge-pump in 0.18 μm CMOS for HDMI applications. *ARPN Journal of Engineering and Applied Sciences*, 13(8).