Vol. 13, No. 4, December 2022, pp. 2226~2234

ISSN: 2088-8694, DOI: 10.11591/ijpeds.v13.i4.pp2226-2234

# A 1 MHz soft-switching boost DC-DC converter with matching network

## Hur Jedi, Ghasan Ali Hussain

Department of Electrical Engineering, University of Kufa, Kufa, Iraq

#### **Article Info**

## Article history:

Received Jun 29, 2022 Revised Aug 22, 2022 Accepted Sep 20, 2022

## Keywords:

Boost converter Matching network Soft-switching Zero-voltage switching (ZVS)

#### **ABSTRACT**

This paper introduces a high-performance zero-voltage-switching (ZVS) boost converter, which is capable to operate under different load currents. By utilizing matching network, the proposed topology can achieve ZVS over a wide range of input voltages. Due to the switching loss is minimized, the proposed circuit is suitable for operation at switching frequencies on the order of several MHz. Steady-state analysis and detailed description of the proposed circuit are discussed. The power-loss and design procedure are introduced. The proposed converter has been simulated to verify the presented analytical approach at 1 MHz and deliver 80 W output. The peak power efficiency achieves 94.2%.

This is an open access article under the CC BY-SA license.

2226

## Corresponding Author:

Hur Jedi

Department of Electrical Engineering, University of Kufa

Kufa, Najaf, 540011, Iraq Email: hur.jeddi@uokufa.edu.iq

# 1. INTRODUCTION

Increasing the frequency leads to improve power density, fast response, and state-of-the-art DC-DC power converters with high efficiency. Due to high frequencies, power converters have become lighter and small in size [1]-[5]. However, high frequencies cause increasing in switching losses. As a result, the efficiency of the whole system is decreased. Among various topologies, many schemes have been previously presented ZVS converters using resonance to perform soft-switching technique [6]-[11]. Some resonant converters utilize auxiliary circuit to enable soft-switching for the main switch of the converters while the switch of auxiliary circuit operates with hard switching [12]. Moreover, the auxiliary circuit increases the complexity of the circuit. Thus, the whole efficiency of system decreases due to switching losses.

Various converters were demonstrated to achieve zero-voltage switching (ZVS) operation by adjusting the impedance of resonant network or using matching network [13]-[17]. This paper proposes a soft-switching boost DC-DC power converter with matching network circuit. The matching network consists of two capacitors and one inductor. It modifies the drain-source voltage of the main switch of the converter to perform soft-switching under ZVS condition.

Moreover, the matching network can bring benefit, such as maximize the transferred power between the supply and load, decrease the reflection and prevent the returns for the load of the converter [18]-[21]. The steady-state operational principle and power loss of the proposed converter are analyzed in detail. In order to fully characterize the proposed topology, a design procedure has been provided. Then, simulation results are presented to confirm ZVS condition for the main switch of the converter at 1 MHz.

Journal homepage: http://ijpeds.iaescore.com

## 2. TOPOLOGY ANALYSIS AND DESCRIPTION OF THE PROPOSED CONVERTER

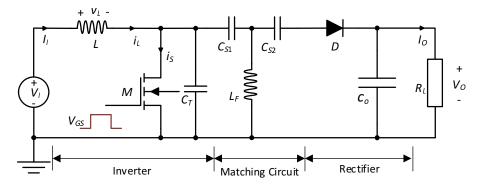

A schematic of the proposed boost dc-dc power converter is depicted in Figure 1. It comprises of an inductor L, a main switch M, a capacitor  $C_T$ , a matching network, an output capacitor  $C_O$  and a load  $R_L$ . The matching network comprises of two capacitors ( $C_{S1}$  and  $C_{S2}$ ) and an inductor  $L_F$ . The main switch M of the converter operates with soft-switching technique by tuning the elements of matching network. The converter has two operating modes: when the power transistor M is closed, the majority of main inductor current  $i_L$  flows through the switch current  $i_L$ . When the switch M is opened, the switch voltage will ring up at the half of switching period then back to zero.

Figure 1. Proposed topology of boost DC-DC power converter

# 2.1. Configuration of the proposed boost converter

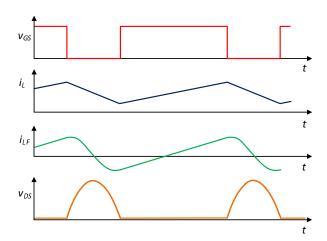

A T-shaped matching network is connected between the inverter and the rectifier of the power boost DC-DC converter as depicted in Figure 1. The proposed converter enables soft-switching through matching network by modifying the switch voltage drain-source voltage  $(V_{DS})$ . The idealized voltage and current waveforms are shaped in Figure 2 to explain the principle operation of the proposed topology.

Figure 2. Idealized waveforms of the proposed boost DC-DC power converter

During time interval  $0 < t \le d$ T, the voltage across the inductor L equals the DC input voltage  $V_I$ . Hence, the inductor current starts from an initial value and increases linearly. At the same time, the diode D is switched from forward to reverse biased and the voltage across the diode D is  $V_D = -V_O$ . During the interval dT  $< t \le T$ , the power transistor M is opened by the gate-source voltage  $V_{GS}$ . Thus, the voltage across the inductor is  $v_L = V_I - V_O$  and the main inductor current  $i_L$  waveform decreases linearly. At the end of period T, the power transistor M is closed again. In this topology, the current waveform  $i_L$  of inductance L operates

2228 ISSN: 2088-8694

in continuous current mode (CCM). Therefore, the change in inductor current during [0, dT] is expressed as:

$$\Delta i_L = \frac{V_I}{L} dT,\tag{1}$$

where d is the duty cycle of the power transistor M and T is the switching period. During the interval time [dT, T], the estimated inductor ripple current is:

$$\Delta i_L = \frac{V_O - V_I}{L} dT. \tag{2}$$

from (1) and (2), the output voltage of the proposed boost dc-dc converter can be given as:

$$V_O = \frac{V_I}{d_1},\tag{3}$$

where  $d_1$  is the interval time when the power transistor is opened under condition  $(d + d_1 = 1)$ .

# 2.2. Impedance analyze

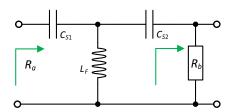

A T-shaped matching network, which is considered high-pass and combined of two capacitors and one inductor, transforms the resistance of the inverter to the rectifier. Figure 3 shows the equivalent circuits of the matching network, which provides DC blocking and allows for fast transient response of the converter. Moreover, the matching network transforms maximum power to the output stage of the proposed DC-DC converter. In order to make the converter achieves soft-switching technique, the matching network is analyzed using s-domain to obtain the frequency response of the equivalent circuit.

Figure 3. Equivalent impedance of network matching circuit

The output resistance  $R_a$  of the inverter can be expressed as:

$$R_a = \frac{s^3 L_F C_{S1} C_{S2} R_b + s^2 (L_F C_{S1} + L_F C_{S2}) + s C_{S2} R_b + 1}{s^3 L_F C_{S1} C_{S2} + s^2 C_{S1} C_{S2} R_b + s C_{S1}},$$

(4)

where  $R_b$  is the input resistance of the rectifier. The coefficients of the real and imaginary components of the above equation are equivalent. The input resistance of the inverter is given as (5).

$$R_a = \frac{1 - \omega^2 (L_F C_{S1} + L_F C_{S2})}{-\omega^2 C_{S1} C_{S2} R_b}.$$

(5)

The relationship between the capacitance  $C_{S1}$  and the capacitance  $C_{S2}$  is:

$$C_{S1} = AC_{S2}. (6)$$

where A is a constant. Based on equation (5), (6), the equation (7) can be expressed as (7).

$$R_a R_b = \frac{\omega^2 L_F C_{S2}(A+1) - 1}{A\omega^2 C_{S2}^2}.$$

(7)

The components of matching network can be obtained as:

$$C_{S2} = \frac{1}{A\omega} \sqrt{\frac{R_a A^2 - R_b}{R_a R_b (R_a - R_b)}},$$

(8)

$$C_{S1} = \frac{1}{\omega} \sqrt{\frac{R_a A^2 - R_b}{R_a R_b (R_a - R_b)}},$$

(9)

and the inductance  $L_F$  is defined as (10).

$$L_F = \frac{1}{\omega^2 C_{S2}} \frac{R_b A R_b}{A(R_b - R_a)}. (10)$$

According to [22], the output resistance of the inverter can express as:

$$R_a = \frac{\left(\frac{4}{\pi}V_I\right)^2}{2P_I},\tag{11}$$

and the input capacitance of the rectifier expressed as (12).

$$R_b = \frac{\left(\frac{4}{\pi}V_O\right)^2}{2P_O}.\tag{12}$$

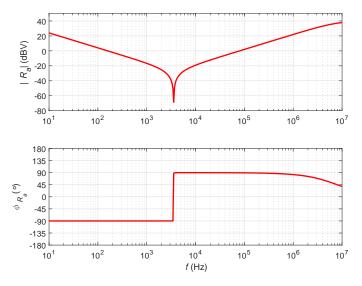

The bode plot and phase margin of the matching network is depicted in Figure 4. It can be noticed that maximum value of the input resistance is -70 when the frequency is changed from 1 Hz to 10 MHz.

Figure 4. Bode plot of matching network circuit

### 2.3. Power losses

The power dissipation of the proposed boost DC-DC power converter is presented. The switching losses are significant in the megahertz range of power converters [23]-[25]. Since the main switch M of the proposed converter operates in ZVS operation, the switching losses are eliminated in the converter. To estimate the losses of the converter, it is considered that the ripple of the main inductor current is free. Thus, the inductor current  $i_L$  equals to the input current  $I_I$ . During the interval  $0 < t \le dT$ , the current that flows through the main power switch is approximated as (13).

$$i_S = I_I = \frac{I_O}{1 - d}.$$

(13)

The rms current value of the power switch M can be expressed as (14).

$$i_{S(rms)} = \sqrt{\frac{1}{T} \int_{0}^{dT} i_{S}^{2} dt} = \frac{I_{O}}{1 - d} \sqrt{\frac{1}{T} \int_{0}^{dT} dt} = \frac{I_{O}\sqrt{d}}{1 - d}.$$

(14)

2230 □ ISSN: 2088-8694

Hence, the power conduction of the switch is given by (15).

$$P_{FET} = i_{S(rms)}^2 r_{on} = \frac{I_O^2 r_{on} d}{(1 - d)^2} = \frac{r_{on} dP_O}{R_L (1 - d)^2}.$$

(15)

During the interval time  $dT < t \le T$ , the current flows through the diode is expressed as (16).

$$i_D = I_I = \frac{I_O}{1 - d}.$$

(16)

Thus, the rms value can be given as (17).

$$i_{D(rms)} = \sqrt{\frac{1}{T} \int_{dT}^{T} i_{D}^{2} dt} = \frac{I_{O}}{1 - d} \sqrt{\frac{1}{T} \int_{dT}^{T} dt} = \frac{I_{O}\sqrt{d}}{1 - d}.$$

(17)

Therefore, the dissipated power in the diode D is approximated as (18).

$$P_D = i_{D(rms)}^2 R_F = \frac{I_O^2 R_F d}{(1-d)} = \frac{R_F P_O}{R_L (1-d)}.$$

(18)

The inductor current is approximated as (19).

$$i_L = i_{L(rms)} \approx I_I = \frac{I_O}{1 - d}.\tag{19}$$

Then, the dissipated power by conduction in the inductors of the proposed topology is given by (20).

$$P_L = i_{L(rms)}^2(r_L + r_{LF}) = \frac{I_O^2(r_L + r_{LF})}{(1 - d)^2} = \frac{(r_L + r_{LF})P_O}{R_L(1 - d)^2}.$$

(20)

The conduction current that flows through the output capacitor  $C_O$  is approximated as (21).

$$i_C = I_I - I_O = \frac{dI_O}{1 - d}.$$

(21)

Therefore, the rms current value of the capacitor is determined as (22).

$$i_{C(rms)} = \sqrt{\frac{1}{T} \int_{0}^{T} i_{C}^{2} dt} = I_{O} \frac{d}{1 - d}.$$

(22)

The conduction power loss, which is dissipated in the capacitors of the power converter, is expressed as (23).

$$P_C = i_{C(rms)}^2 (r_{CO} + r_{CS1} + r_{CS2}) = \frac{dI_O^2 (r_{CO} + r_{CS1} + r_{CS2})}{(1 - d)} = \frac{d(r_{CO} + r_{CS1} + r_{CS2})P_O}{R_L (1 - d)}.$$

(23)

The overall dissipated power of the proposed boost dc-dc power converter can be approximated by (24).

$$P_{LOSS} = P_{FET} + P_D + P_L + P_C. \tag{24}$$

Thus, the efficiency  $\eta$  of the proposed topology is given by (25).

$$\eta = \frac{P_O}{P_O + P_{Loss}}. (25)$$

## 2.4. Design procedure

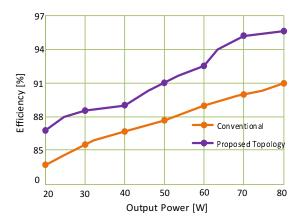

A design procedure for the proposed boost DC-DC power converter is presented at operating switching frequency  $f_s=1$  MHz. The design is applied to calculate the values of the components for the proposed boost converter and matching network  $(C_{S1}, C_{S2}, \text{ and } L_F)$ . The output power  $P_O$  and the duty cycle d were selected to be 80 W and 62%, respectively. The input voltage of the converter is  $V_I=150$  V. From (3), the output voltage of the converter is  $V_O=400$  V. According to (11) and (12), the values of  $R_a=228$   $\Omega$  and  $R_b=1622$   $\Omega$ . It is assumed that the value of constant A=1. Based on (9) and (8), the value of  $C_{S1}$  and  $C_{S2}$  are 26 nF and 26 nF, respectively. From (10), the inductance  $L_F$  of matching network is 258  $\mu$ H. According to subsection (2.3.), the dissipated power by conduction of the proposed boost dc-dc power converter is determined. From (15), the conduction power loss, which is dissipated in the MOSFET (IXFH34N65X3), is  $P_{FET}=1.21$  W. According to (18), the dissipated power in the diode (MUR1560) is  $P_D=1.71$  W. Based on (20) and (23), the power loss of the proposed topology is calculated  $P_{Loss}=4.92$  W. Figure 5 shows the relationship between the efficiency  $\eta$  and the output power  $P_O$  for the proposed topology and the conventional converter. The specification of components for the proposed converter are shown in Table 1.

Figure 5. Output power and efficiency of conventional boost and proposed topology

| Table 1. Performance parameters of proposed DC-I | C power converter |

|--------------------------------------------------|-------------------|

|--------------------------------------------------|-------------------|

| Components                                     | Value                                                                              |

|------------------------------------------------|------------------------------------------------------------------------------------|

| Supply voltage $V_I$                           | 150 V                                                                              |

| Output voltage $V_O$                           | 400 V                                                                              |

| Load resistance $R_L$                          | $2~\mathrm{K}\Omega$                                                               |

| Output power $P_O$                             | 80 W                                                                               |

| Inductors $L, L_F$                             | 90 $\mu$ H ( $L$ ), 258 $\mu$ H ( $L_F$ )                                          |

| Capacitors $C_T$ , $C_{S1}$ , $C_{S2}$ , $C_O$ | 25 $\mu$ F ( $C_T$ ), 26 nF ( $C_{S1}$ ), 26 nF ( $C_{S2}$ ), 35 $\mu$ F ( $C_O$ ) |

# 3. RESULTS AND DISCUSSIONS

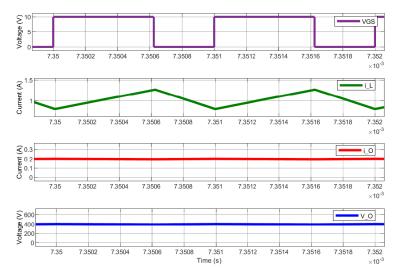

Figure 8 shows the switch signal  $V_{GS}$ , the inductor current  $i_L$ , the output current of the converter  $i_O$ , and the output voltage  $V_O$  waveforms. It is clear that the output voltage of the proposed topology is constant at 1 MHz operating switching frequency. Thus, the proposed circuit is eligible to operate at high frequencies with low switching losses. The proposed circuit was also tested at full power with the input voltage  $V_I = 170$  V. Under this condition, the efficiency of the converter is  $\eta = 94\%$ .

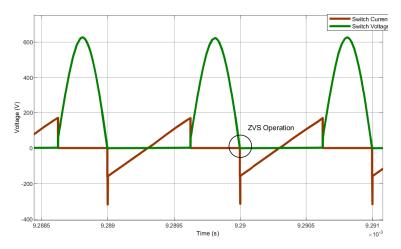

Figure 6. Gate-source voltage and switch voltages with ZVS technique

Figure 7. Voltage and current waveforms for the main switch M of the proposed converter

Figure 8. Inductor current, output current, and output voltage waveforms of the proposed converter

## 4. CONCLUSION

A soft-switching boost DC-DC converter has been introduced in this paper that uses a matching network as interface circuit between the rectifier and the inverter. The main switch of the converter performs ZVS condition by using the matching network to modify the switch voltage of the converter. The proposed topology has been analyzed and designed in details. It has high flexibility of design and low number of passive elements. A 1 MHz prototype has been confirmed by simulation to demonstrate ZVS operation. It is shown that the performance of the proposed boost dc-dc power converter is better than the conventional boost converter. The proposed converter is suitable for applications, such as, high-frequency converters, battery chargers, and photovoltaic DC-DC power converters.

#### REFERENCES

- [1] Y. Wang, O. Lucia, Z. Zhang, S. Gao, Y. Guan, and D. Xu, "A review of high frequency power converters and related technologies," in *IEEE Open Journal of the Industrial Electronics Society*, vol. 1, pp. 247-260, 2020, doi: 10.1109/OJIES.2020.3023691.

- [2] A. Chlaihawi, A. Sabbar, and H. Jedi, "A high-performance multilevel inverter with reduced power electronic devices," *International Journal of Power Electronics and Drive System (IJPEDS)*, vol. 11, no. 4, pp. 1883-1889, 2020, doi: 10.11591/ijpeds.v11.i4.pp1883-1889

- [3] H. Jedi, T. Salvatierra, A. Ayachit, and M. K. Kazimierczuk, "High-frequency single-switch ZVS gate driver based on a class-Φ<sub>2</sub> resonant inverter," in *IEEE Transactions on Industrial Electronics*, vol. 67, no. 6, pp. 4527-4535, Jun. 2020, doi: 10.1109/TIE.2019.2927192.

- [4] A. Chlaihawi, A. Al-Modaffer, H. Jedi, "Minimal switching of multiple input multilevel output DC-DC converter," *International Journal of Power Electronics and Drive System (IJPEDS)*, vol. 12, no. 2, pp. 968-974, 2021, doi: 10.11591/ijpeds.v12.i2.pp968-974.

- [5] J. M. Rivas, O. Leitermann, Y. Han and D. J. Perreault, "A very high frequency DC–DC converter based on a class-Φ<sub>2</sub> resonant inverter," in *IEEE Transactions on Power Electronics*, vol. 26, no. 10, pp. 2980-2992, Oct. 2011, doi: 10.1109/TPEL.2011.2108669.

- [6] Y. Guan, C. Liu, Y. Wang, W. Wang, and D. Xu, "Analytical derivation and design of 20-MHz DC-DC soft-switching resonant converter," in *IEEE Transactions on Industrial Electronics*, vol. 68, no. 1, pp. 210-221, Jan. 2021, doi: 10.1109/TIE.2020.2965508.

- [7] J. M. Burkhart, R. Korsunsky, and D. J. Perreault, "Design methodology for a very high frequency resonant boost converter," in *IEEE Transactions on Power Electronics*, vol. 28, no. 4, pp. 1929-1937, Apr. 2013, doi: 10.1109/TPEL.2012.2202128.

- [8] N. Bertoni, G. Frattini, R. G. Massolini, F. Pareschi, R. Rovatti, and G. Setti, "An analytical approach for the design of class-E resonant DC-DC converters," in *IEEE Transactions on Power Electronics*, vol. 31, no. 11, pp. 7701-7713, Nov. 2016, doi: 10.1109/TPEL.2016.2535387.

- [9] M. Thompson and J. K. Fidler, "Determination of the impedance matching domain of impedance matching networks," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 51, no. 10, pp. 2098-2106, Oct. 2004, doi: 10.1109/TCSI.2004.835682.

- [10] M. Daryaei, S. A. Khajehoddin, J. Mashreghi, and K. K. Afridi, "A new approach to steady-state modeling, analysis, and design of power converters," in *IEEE Transactions on Power Electronics*, vol. 36, no. 11, pp. 12746-12768, Nov. 2021, doi: 10.1109/TPEL.2021.3076745.

- [11] Y. Huang, S. -C. Tan, and S. Y. Hui, "Multiphase-interleaved high step-up DC/DC resonant converter for wide load range," in *IEEE Transactions on Power Electronics*, vol. 34, no. 8, pp. 7703-7718, Aug. 2019, doi: 10.1109/TPEL.2018.2880803.

- [12] S. -H. Park, S. -R. Park, J. -S. Yu, Y. -C. Jung, and C. -Y. Won, "Analysis and design of a soft-switching boost converter with an HI-bridge auxiliary resonant circuit," in *IEEE Transactions on Power Electronics*, vol. 25, no. 8, pp. 2142-2149, Aug. 2010, doi: 10.1109/TPEL.2010.2046425.

- [13] H. Jedi, "Analysis and design of resonant class- $\Phi_2$  inverter with low-voltage stress," 2021 22nd IEEE International Conference on Industrial Technology (ICIT), 2021, pp. 316-321, doi: 10.1109/ICIT46573.2021.9453468.

- [14] K. Zhang, T. Ye, Z. Yan, B. Song, and A. P. Hu, "Obtaining maximum efficiency of inductive power-transfer system by impedance matching based on boost converter," in *IEEE Transactions on Transportation Electrification*, vol. 6, no. 2, pp. 488-496, Jun. 2020, doi: 10.1109/TTE.2020.2987487.

- [15] W. Inam, K. K. Afridi, and D. J. Perreault, "High efficiency resonant DC/DC converter utilizing a resistance compression network," in *IEEE Transactions on Power Electronics*, vol. 29, no. 8, pp. 4126-4135, Aug. 2014, doi: 10.1109/TPEL.2013.2282626.

- [16] H. Jedi and M. K. Kazimierczuk, "High-frequency single-switch ZVS inverter for driving capacitive loads," IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society, 2018, pp. 1255-1260, doi: 10.1109/IECON.2018.8592685.

- [17] K. -H. Lee, E. Chung, Y. Han and J. -I. Ha, "A family of high-frequency single-switch DC-DC converters with low switch voltage stress based on impedance networks," in *IEEE Transactions on Power Electronics*, vol. 32, no. 4, pp. 2913-2924, Apr. 2017, doi: 10.1109/TPEL.2016.2580154.

- [18] M. K. Kazimierczuk, Radio-frequency power amplifiers, 2nd ed., Chichester, UK: John Wiley and Sons, 2014.

- [19] D. Gerber and J. Biela, "Interleaving of a soft-switching boost converter operated in boundary conduction mode," in IEEE Transactions on Plasma Science, vol. 43, no. 10, pp. 3374-3380, Oct. 2015, doi: 10.1109/TPS.2015.2422476.

- [20] A. Mondzik, R. Stala, S. Piróg, A. Penczek, P. Gucwa, and M. Szarek, "High efficiency DC–DC boost converter with passive snubber and reduced switching losses," in *IEEE Transactions on Industrial Electronics*, vol. 69, no. 3, pp. 2500-2510, Mar. 2022, doi: 10.1109/TIE.2021.3063874.

- [21] R. C. N. Pilawa-Podgurski, A. D. Sagneri, J. M. Rivas, D. I. Anderson, and D. J. Perreault, "Very-high-frequency resonant boost converters," in *IEEE Transactions on Power Electronics*, vol. 24, no. 6, pp. 1654-1665, Jun. 2009, doi: 10.1109/TPEL.2009.2016098.

- [22] L. Gu, W. Liang, L. C. Raymond, and J. Rivas-Davila, "27.12 MHz GaN Bi-directional resonant power converter," 2015 IEEE 16th Workshop on Control and Modeling for Power Electronics (COMPEL), 2015, pp. 1-7, doi: 10.1109/COMPEL.2015.7236440.

- [23] B. Kou, J. Wei, and L. Zhang, "Switching and conduction loss reduction of dual-buck full-bridge inverter through ZVT soft-switching under full-cycle modulation," in *IEEE Transactions on Power Electronics*, vol. 35, no. 5, pp. 5031-5046, May 2020, doi:

2234 □ ISSN: 2088-8694

10.1109/TPEL.2019.2943700.

[24] M. K. Kazimierczuk, Pulse-width modulated DC-DC power converters, Chichester, U. K.: John Wiley and Sons, 2015.

[25] C. Bai and M. Kim, "Bidirectional resonant converter with minimized switching loss over wide operating voltage range," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 10, no. 3, pp. 2975-2988, Jun. 2022, doi: 10.1109/JESTPE.2021.3117558.

## **BIOGRAPHIES OF AUTHORS**