ISSN: 2502-4752, DOI: 10.11591/ijeecs.v28.i3.pp1345-1354

# Hysteresis control of the new split-packed-U-cell inverter

## Ayoub El Gadari<sup>1</sup>, Hind El Ouardi<sup>1</sup>, Youssef Ounejjar<sup>1</sup>, Kamal Al-haddad<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Higher School of Technology, Moulay Ismail University, Meknes, Morocco <sup>2</sup>Department of Electrical Engineering, School of Higher Technology, Montreal, Canada

#### **Article Info**

#### Article history:

Received Feb 10, 2022 Revised Aug 26, 2022 Accepted Sep 8, 2022

#### Keywords:

Hystetesis control Neutral point clamped Packed-U-cell Split packed-U-cell Total harmonic distortion

#### **ABSTRACT**

The authors provide a novel hysteresis control method for the SPUC inverter in this paper. The suggested system, which consist of the SPUC inverter and the balancing algorithm can offer eleven levels at output voltage using only seven switches, a closed loop is applied to maintain capacitors voltage at desired values, another hysteresis control that ensures capacitors voltage self-balancing is implemented in open loop which result in the proposed SPUC9 inverter .No voltage sensor or filtering is needed, as a consequence the inverter and installation expenses are kept to a minimum. The authors utilized MATLAB/Simulink environment to simulate the proposed converters. Simulation results prove all the concepts given in this paper. Total harmonic distortion remains reduced and depends on the hysteresis bandwidth.

This is an open access article under the CC BY-SA license.

1345

#### Corresponding Author:

Ayoub El Gadari

Department of Electrical Engineering, Higher School of Technology, Moulay Ismail University

Meknes 50000, Morocco

Email: a.elgadari@edu.umi.ac.ma

# 1. INTRODUCTION

In recent years, multilevel inverters have recieved a lot of attention because of their benifits including, low electromagnetic interference (EMI), decreased voltage stress (dv/dt), minimal total harmonics distortion (THD) and high power conversion. Three basic topologies are considered, namely, Neutral Point Clamped (NPC) [1], cascaded H-Bridge (CHB) [2] and the flying capacitor (FC) [3]. Many topologies have borne, such as packed-U-cell (PUC) [4], and split-packed-U-cell (SPUC) [5], and they become very competitive due to their capacity for producing high levels of voltage while utilizing a minimal amount of power components.

However, the major problem in multilevel converter topologies is balancing capacitors voltages, in fact, their imbalance can seriously harm semiconductors and passive components. As solutions, three ideas are proposed, the first option consist of applying a closed loop regulation [6]–[20] using proportional integral (PI) regulators and sensors but this solution is incompatible with several industrial uses. Some electronics circuits are includes in the second option, resulting in hefty converters [21], [22]. However, in the third option redundant states are used to provide capacitors voltage self-balancing ,as a result, a very simple implementation is obtained [23]–[25].

In this paper, the authors provide a novel hysteresis control method for the SPUC inverter, the later which is designed using two converters which are PUC and NPC may provide a high number of levels with few device components. Firstly, a closed loop control is used to maintain capacitors voltages at desired values, as a result, the inverter offers eleven levels using only seven switches, another hysteresis controller is applied on the SPUC inverter, this method insures capacitors voltage self-balancing without the need of filters or a voltage feed-back sensor.

Journal homepage: http://ijeecs.iaescore.com

#### 2. RESEARCH METHOD

In this section, a closed loop regulation is applied on the SPUC inverter. This method which is based on hysteresis control provides eleven levels at the output voltage, another multilevel hysteresis technique that assures self balancing of capacitors voltages is related to the proposed inverter. By taking advantage of redundant states, it can offer nine levels in open loop operation without the usage of any regulators or filters.

# 2.1. Eleven level SPUC inverter structure, switching states and closed loop capacitors voltage balancing method

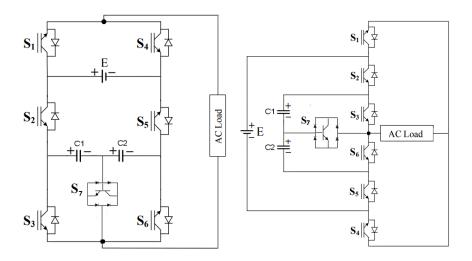

The SPUC inverter is inspired by the original seven-level PUC converter. As indicated in Figure 1, an extra four quadrant power device is placed and linked to the lower capacitor mid-point. When Vc1=Vc2=E/5, the topology provides a maximum of eleven voltage levels.

Figure 1. SPUC Inverter Circuit diagram

Table 1 presents the eleven required levels operations. The third column gives an example when direct current (DC) source is equal to 300 V. All possible situations are presented in the second column. One can remark the two redundant states 6 and 6'.

| State | Interconnection | Voltage (V) | S1 | S2 | S3 | S4 | S5 | S6 | S7 |

|-------|-----------------|-------------|----|----|----|----|----|----|----|

| 11    | E               | 300         | 1  | 0  | 0  | 0  | 1  | 1  | 0  |

| 10    | E-Vc2           | 240         | 1  | 0  | 0  | 0  | 1  | 0  | 1  |

| 9     | E-(Vc1+Vc2)     | 180         | 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 8     | Vc1+Vc2         | 120         | 1  | 1  | 0  | 0  | 0  | 1  | 0  |

| 7     | Vc1             | 60          | 1  | 1  | 0  | 0  | 0  | 0  | 1  |

| 6     | 0               | 0           | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 6'    | 0               | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 0  |

| 5     | -Vc2            | -60         | 0  | 0  | 0  | 1  | 1  | 0  | 1  |

| 4     | -Vc1-Vc2        | -120        | 0  | 0  | 1  | 1  | 1  | 0  | 0  |

| 3     | (Vc1+Vc2)-E     | -180        | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

Table 1. Switching sequence for the eleven level SPUC inverter.

The following equation can be used to presente the reference of the AC load voltage:

-240

$$V_{L} = K_{p}\widetilde{i}_{L} + K_{i} \int \widetilde{i}_{L} dt \tag{1}$$

When:

$$\widetilde{\mathbf{I}_{\mathbf{L}}} = \mathbf{i}_{\mathbf{L}}^* - \mathbf{i}_{\mathbf{L}} \tag{2}$$

Vc1-E

The load current reference is represented by  $i_L^*$ . A PI controller adjusts the capacitor voltage in such a way that:

$$i_L *= (K_{p1}\widetilde{v_1} + K_{i1} \int \widetilde{v_1} dt) + (K_{p2}\widetilde{v_2} + K_{i2} \int \widetilde{v_2} dt)$$

(3)

$$\widetilde{v_1} = v_{c1} * - v_{c1}$$

,  $\widetilde{v_2} = v_{c2} * - v_{c2}$  (4)

where  $v_{c1}^*$ ,  $v_{c2}^*$  are the capacitors voltages references.

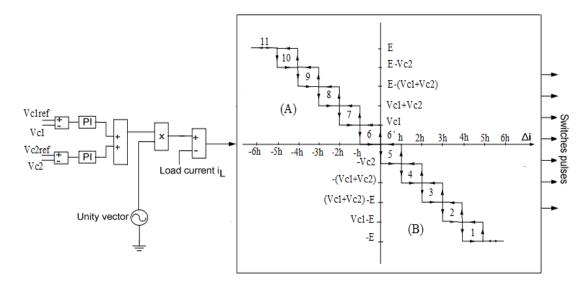

Table 1 is thus used to obtain the eleven voltage levels. The suggested control technique is depends on the ten band hysteresis method, when  $\Delta i$  which is the current error is negative. Positive voltages are applied (part A in Figure 2). Inversely, when the  $\Delta i$  is positive, negative voltages are used (part B in Figure 2).  $\Delta i$  presents the real load current minus the current reference. Figure 3 depicts the eleven states and their transition conditions.

Figure 2. Proposed capacitors voltages balancing technique

Figure 3. Proposed hysteresis controller

#### 2.2. Nine level SPUC inverter structure, switching states and voltage balancing method

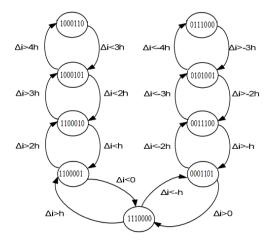

The proposed 9-level inverter was derived from the eleven-level SPUC inverter presented above. However, using closed loop regulation is incompatible with several industrial uses. So, the idea is to decrease voltage levels number, allowing for additional redundant states. These latter are used to guarantee that capacitors voltages self balance without any regulation operation. Assuming that Vc1=Vc2=E/4. Three redundant states which are states 3', 5' 7' are created in addition to the nine required levels operations as is indicated in the Table 2. The three redundant states were produced in the following manner.

- (7):E-(Vc1+Vc2) positive output (first E/2): (S1 is ON), and linked to the positive terminal of the load, while (S3 is ON)+(S5 is ON), and linked to the negative terminal of the load. Capacitor 1 and 2 are charging.

- (7'):Vc1+Vc2 positive output (second E/2): (S1 is ON)+(S2 is ON), and linked to the positive terminal of the load, while (S6 is ON), and linked to the negative terminal of the load. Capacitor 1 and 2 are discharging.

- (5):Zero output (0): (S1 is ON)+(S2 is ON)+(S3 is ON). No effect on capacitor 1 or capacitor 2.

- (5'):Zero output (0): (S4 is ON)+(S5 is ON)+(S6 is ON). No effect on capacitor 1 or capacitor 2.

- (3):-Vc1-Vc2 negative output (first -E/2): (S4 is ON) + (S5 is ON and linked to the positive terminal of the load, while (S3 is ON), and linked to the negative terminal of the load. Capacitor 1 and 2 are discharging.

- (3'):(Vc1+Vc2)-E negative output (second -E/2): (S4 is ON) + (S2 is ON), and linked to the positive terminal of the load, while (S6 is ON), and linked to the negative terminal of the load. Capacitor 1 and 2 are charging.

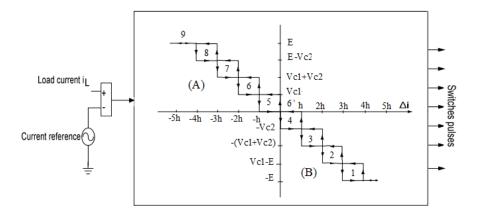

Table 2 shows the levels that where kept, that decision is based on different situations of capacitors and takes states that according to proposed capacitors voltages balancing technique (Figure 4) they provide nine levels with capacitors voltages self-balancing.

The suggested control strategy is depends on the eight band hysteresis method, when  $\Delta i$  which is the current error is negative, positive voltages are applied (part A in Figure 4). Vice versa, when the  $\Delta i$  is positive, negative voltages are used (part B in Figure 4),  $\Delta i$  presents the real load current minus the current reference. Figure 5 depicts the nine different states and their transition conditions.

Table 2. Switching sequence for the nine-level SPUC inverter

| Tuble 2. Bwitching bequence for the finite fever by ele inverter |                 |             |    |    |    |    |    |    |    |

|------------------------------------------------------------------|-----------------|-------------|----|----|----|----|----|----|----|

| State                                                            | Interconnection | Voltage (V) | S1 | S2 | S3 | S4 | S5 | S6 | S7 |

| 9                                                                | Е               | 400         | 1  | 0  | 0  | 0  | 1  | 1  | 0  |

| 8                                                                | E-Vc2           | 300         | 1  | 0  | 0  | 0  | 1  | 0  | 1  |

| 7'                                                               | E-(Vc1+Vc2)     | 200         | 1  | 0  | 1  | 0  | 1  | 0  | 0  |

| 7                                                                | Vc1+Vc2         | 200         | 1  | 1  | 0  | 0  | 0  | 1  | 0  |

| 6                                                                | Vc1             | 100         | 1  | 1  | 0  | 0  | 0  | 0  | 1  |

| 5                                                                | 0               | 0           | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| 5'                                                               | 0               | 0           | 0  | 0  | 0  | 1  | 1  | 1  | 0  |

| 4                                                                | -Vc2            | -100        | 0  | 0  | 0  | 1  | 1  | 0  | 1  |

| 3                                                                | -Vc1-Vc2        | -200        | 0  | 0  | 1  | 1  | 1  | 0  | 0  |

| 3'                                                               | (Vc1+Vc2)-E     | -200        | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| 2                                                                | Vc1-E           | -300        | 0  | 1  | 0  | 1  | 0  | 0  | 1  |

| 1                                                                | -E              | -400        | 0  | 1  | 1  | 1  | 0  | 0  | 0  |

Figure 4. Proposed capacitors voltages balancing technique

Figure 5. Proposed hysteresis controller

#### 3. RESULTS AND DISCUSSION

Simulation of the proposed eleven level and nine level SPUC inverters was obtained utilizing the MATLAB/Simulink environment. The eleven level SPUC inverter was simulated with constant DC source and load operation. Whereas, simulation of the nine level SPUC inverter was performed in constant and changing load operations, other parameters, including hysteresis bandwidth, remain unchanged.

#### 3.1. Eleven level SPUC inverter

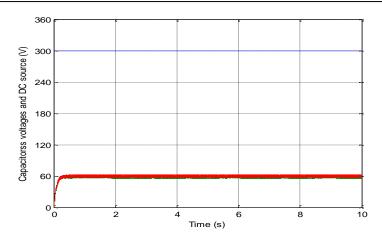

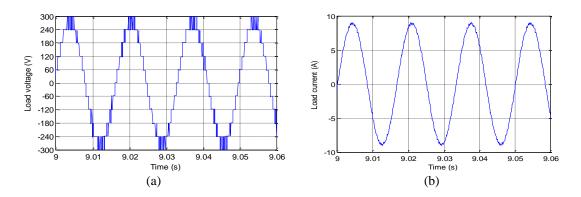

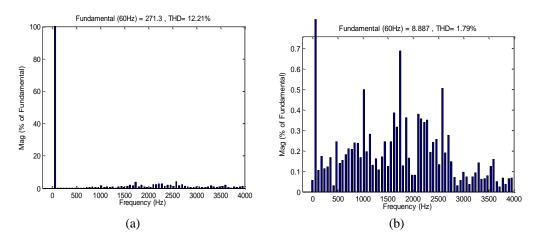

As shown in the Figure 6, the capacitors appear to have attained the appropriate voltage values, thus, Vc1 and Vc2 are maintained exactly on the fifth of the DC source. Figure 7 depicts the voltage and current load waveforms, output voltage of the SPUC inverter proposed is constituted from eleven voltage levels as is presented in Figure 7(a), parameters utilized in the simulation are shown in Table 3.

As presented in Figure 7(b), a nearly sinusoidal load current is achived, it depends on Hysteresis bandwidth. The THD level is very low. Figure 8 displays the load voltage and current harmonics content, it is about 12.21% for the load voltage (Figure 8(a)) and 1.79% for the load current waveform (Figure 8(b)). Reducing the hysteresis bandwidth help to reduce the load current THD.

#### 3.2. Nine level SPUC inverter

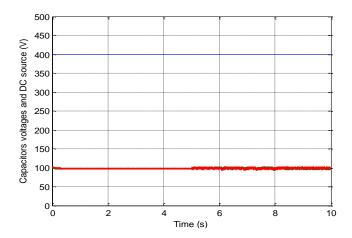

The simulation is run under constant and variable load operations to validate the proposed inverter and its balancing algorithm. As well as to demonstrate the high dynamics of the proposed concept, no PI regulators, filters or voltage feed-back are used. All other parameters, including hysteresis bandwidth, stay constant during simulation, capacitors voltages are self-balanced around the desired values.

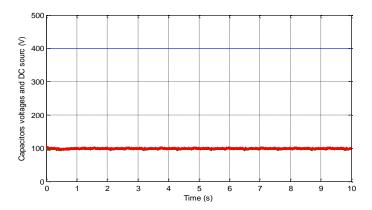

#### 3.2.1. Constant load and DC source operation

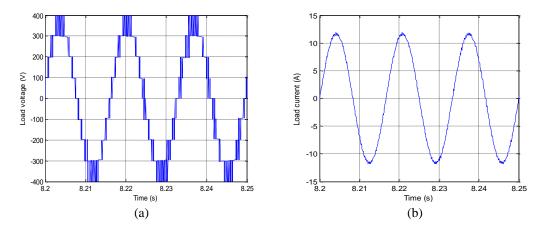

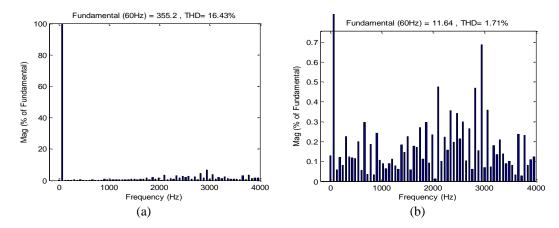

As shown in Figure 9, the capacitors voltages are attained their desired values, thus, Vc1 and Vc2 are maintained around the fourth of DC source, no voltage sensor or closed loop is needed. Figure 10 depicts the voltage and current load waveforms, the output voltage of the inverter proposed, it is constituted from nine voltage levels as is presented in Figure 10(a). A nearly sinusoidal load current is detected as represented in Figure 10(b), parameters utilized in the simulation are shown in Table 4.

The THD level which is very low is obtained without any voltage sensor or regulation loop. Figure 11 displays the load voltage and current harmonics content; we observe a 16.43% for output load voltage (Figure 11(a)) and 1.71% for load current (Figure 11(b)). Reducing the hysteresis bandwidth help to reduce the load current THD.

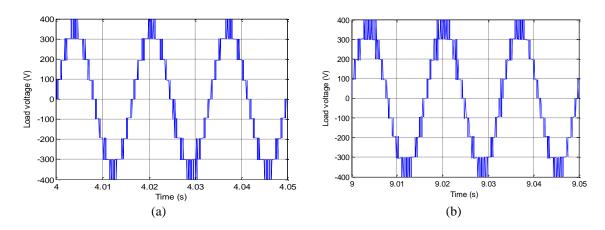

## 3.2.2. Changing load operation

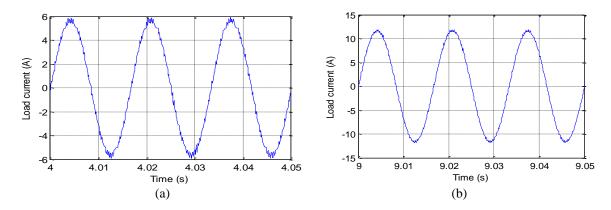

To demonstrate the high dynamics of the nine-level SPUC inverter, another simulation is realized. Hence, at t=5 s load resistor value is changed from 60  $\Omega$  to 30  $\Omega$ , other parameters keep the same values which are 400 V for DC source voltage and 15 mH for load inductance. As illustrated in Figure 12 capacitors voltages values are balanced after t=5 s. A fast response is detected, (Vc1 and Vc2) are fixed around the fourth of DC source. The voltage load waveform is depicted in Figure 13, it maintains nine levels before (Figure 13(a)) and after (Figure 13(b)) load change. However, Figure 14 displays the current load which appears almost sinusoidal before (Figure 14(a)) and after (Figure 14(b)) load change.

Figure 6. DC source and capacitors voltages

Figure 7. Load waveforms (a) voltage and (b) current

Table 3. Parameters utilized in the simulation

| Parameters           | Value         |  |  |  |

|----------------------|---------------|--|--|--|

| Hysteresis bandwidth | 0.25          |  |  |  |

| Voltage source DC    | 300V          |  |  |  |

| Load resistor        | $30 \Omega$   |  |  |  |

| Load inductance      | 15 mH         |  |  |  |

| SPUC11 capacitors    | $4~000~\mu F$ |  |  |  |

Figure 8. Harmonics content of load (a) voltage and (b) current

Table 4. Parameters for simulation

| Parameters                 | Value         |

|----------------------------|---------------|

| Hysteresis bandwidth       | 0.25          |

| E (DC source voltage)      | 400V          |

| Load resistor              | $30 \Omega$   |

| Load inductance            | 15 mH         |

| Auxiliary DC bus capacitor | $4~000~\mu F$ |

Figure 9. DC source and capacitors voltages

Figure 10. Load waveforms (a) voltage and (b) current

Figure 11. Harmonics content of load (a) voltage and (b) current

Figure 12. DC source and capacitors voltages

Figure 13. Load voltage waveform (a) before and (b) after load change

Figure 14. Load current waveform (a) before and (b) after load change

# 4. CONCLUSION

A novel hysteresis control is applied on the SPUC inverter. The SPUC inverter can offer eleven levels at output voltage, however, a closed loop is used to maintain capacitors voltage at desired values. Another method of control is presented, the later helps to achieve capacitors voltage balancing in open loop operation without using any sensors or regulators, output current is nearly sinusoidal and it can be ameliorated by reducing the hysteresis bandwidth. The high dynamics of the proposed inverter was verified by simulation.

#### REFERENCES

- [1] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Transactions on Industry Applications*, vol. IA-17, no. 5, pp. 518–523, 1981, doi: 10.1109/TIA.1981.4503992.

- [2] F. Z. Peng, "A multilevel voltage-source inverter with separate DC sources for static var generation," *IEEE Transactions on Industry Applications*, vol. 32, no. 5, pp. 1130–1138, 1996, doi: 10.1109/28.536875.

- [3] T. A. Meynard and H. Foch, "Multi-level conversion: High voltage choppers and voltage-source inverters," in PESC Record -IEEE Annual Power Electronics Specialists Conference, 1992, pp. 397–403, doi: 10.1109/PESC.1992.254717.

- [4] Y. Ounejjar, K. Al-Haddad, and L. A. Grégoire, "Packed U cells multilevel converter topology: Theoretical study and experimental validation," *IEEE Transactions on Industrial Electronics*, vol. 58, no. 4, pp. 1294–1306, 2011, doi: 10.1109/TIE.2010.2050412.

- [5] A. El Gadari et al., "New nine-level SPUC inverter using single DC source," in IECON Proceedings (Industrial Electronics Conference), 2019, vol. 2019-October, pp. 1892–1897, doi: 10.1109/IECON.2019.8927358.

- [6] A. K. Chauhan, S. T. Mulpuru, M. Jain, and S. K. Singh, "A Cross-Regulated Closed-Loop Control for Hybrid L-Z Source Inverter," *IEEE Trans. Ind. Appl.*, vol. 55, no. 2, 2019, doi: 10.1109/TIA.2018.2873531.

- [7] S. T. B. Shalini, J. J. Jawhar, and M. Ramachandra, "A closed loop eleven level inverter with heuristic search algorithm based tuning of PI controller for the regulation of the output voltage," *J. Green Eng.*, vol. 10, no. 3, 2020.

- [8] Y. X. Dai, H. Wang, and G. Q. Zeng, "Double Closed-Loop PI Control of Three-Phase Inverters by Binary-Coded Extremal Optimization," *IEEE Access*, vol. 4, pp. 7621–7632, 2016, doi: 10.1109/ACCESS.2016.2619691.

- [9] A. Nami, F. Zare, A. Ghosh, and F. Blaabjerg, "A hybrid cascade converter topology with series-connected symmetrical and asymmetrical diode-clamped H-bridge cells," *IEEE Transactions on Power Electronics*, vol. 26, no. 1, pp. 51–65, 2011, doi: 10.1109/TPEL.2009.2031115.

- [10] A. Shukla, A. Ghosh, and A. Joshi, "Improved multilevel hysteresis current regulation and capacitor voltage balancing schemes for flying capacitor multilevel inverter," *IEEE Trans. Power Electron.*, vol. 23, no. 2, 2008, doi: 10.1109/TPEL.2007.915788.

- [11] X. H. Zhang and W. K. Yue, "Neutral point potential balance algorithm for three-level NPC inverter based on SHEPWM," Electronics Letters, vol. 53, no. 23, pp. 1542–1544, 2017, doi: 10.1049/el.2017.3191.

- [12] R. Chen et al., "Modeling, analysis, and reduction of harmonics in paralleled and interleaved three-level neutral point clamped inverters with space vector modulation," *IEEE Transactions on Power Electronics*, vol. 35, no. 4, pp. 4411–4425, 2020, doi: 10.1109/TPEL.2019.2939727.

- [13] A. N. Babadi, O. Salari, M. J. Mojibian, and M. T. Bina, "Modified multilevel inverters with reduced structures based on PackedU-Cell," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 6, no. 2, pp. 874–887, 2018, doi: 10.1109/JESTPE.2017.2767499.

- [14] S. Devaraj and G. S. Anitha, "Closed loop system of a flying capacitor multilevel inverter using POD-PWM," in 2016 Biennial International Conference on Power and Energy Systems: Towards Sustainable Energy (PESTSE), 2016. doi: 10.1109/PESTSE.2016.7516519.

- [15] I. Lopez *et al.*, "Modulation strategy for multiphase neutral-point-clamped converters," *IEEE Transactions on Power Electronics*, vol. 31, no. 2, pp. 928–941, 2016, doi: 10.1109/TPEL.2015.2416911.

- [16] C. Q. Xiang, C. Shu, D. Han, B. K. Mao, X. Wu, and T. J. Yu, "Improved Virtual space vector modulation for three-level neutral-point-clamped converter with feedback of neutral-point voltage," *IEEE Transactions on Power Electronics*, vol. 33, no. 6, pp. 5452–5464, 2018, doi: 10.1109/TPEL.2017.2737030.

- [17] M. Ali et al., "Genetic algorithm based PI control with 12-band hysteresis current control of an asymmetrical 13-level inverter," Energies, vol. 14, no. 20, Oct. 2021, doi: 10.3390/en14206663.

- [18] J. Wang, X. Yuan, and B. Jin, "Carrier-based closed-loop DC-link voltage balancing algorithm for four level NPC converters based on redundant level modulation," *IEEE Transactions on Industrial Electronics*, vol. 68, no. 12, pp. 11707–11718, Dec. 2021, doi: 10.1109/TIE.2020.3039225.

- [19] D. Upadhyay, M. Ali, M. Tariq, S. A. Khan, B. Alamri, and A. Alahmadi, "Thirteen-Level UXE-Type Inverter With 12-Band Hysteresis Current Control Employing PSO Based PI Controller," *IEEE Access*, vol. 10, 2022, doi: 10.1109/ACCESS.2022.3146355.

- [20] K. Wang, Z. Zheng, L. Xu, and Y. Li, "Neutral-point voltage balancing method for five-level NPC inverters based on carrier-overlapped PWM," *IEEE Transactions on Power Electronics*, vol. 36, no. 2, pp. 1428–1440, Feb. 2021, doi: 10.1109/TPEL.2020.3006960.

- [21] M. Mazuela, I. Baraia, A. Sanchez-Ruiz, I. Echeverria, I. Torre, and I. Atutxa, "Simple voltage balancing method to protect series-connected devices experimentally verified in a 5L-MPC converter," *IEEE Transactions on Industrial Electronics*, vol. 65, no. 5, pp. 3699–3707, 2018, doi: 10.1109/TIE.2017.2760843.

- [22] J. Y. Lee, H. J. Choi, and J. H. Jung, "Three level NPC dual active bridge capacitor voltage balancing switching modulation," in INTELEC, International Telecommunications Energy Conference (Proceedings), 2017, vol. 2017-October, pp. 438–443, doi: 10.1109/INTLEC.2017.8214175.

- [23] Y. Ounejjar and K. Al-Haddad, "New nine-level inverter with self balancing of capacitors voltages," in IECON 2018-44th Annual Conference of the IEEE Industrial Electronics Society, 2018, vol. 1, pp. 4467–4472, doi: 10.1109/IECON.2018.8591555.

- [24] Y. Ounejjar, A. El Gadari, M. Abarzadeh, and K. Al-Haddad, "PWM sensor-less balancing technique for the fifteen-level PUC converter," in 2018 IEEE Electrical Power and Energy Conference, EPEC 2018, 2018, pp. 1–6, doi: 10.1109/EPEC.2018.8598443.

- [25] M. Sharifzadeh and K. Al-Haddad, "Packed E-Cell (PEC) converter topology operation and experimental validation," IEEE Access, vol. 7, pp. 93049–93061, 2019, doi: 10.1109/ACCESS.2019.2924009.

#### **BIOGRAPHIES OF AUTHORS**

Ayoub El Gadari was born in Meknes, Morocco, in November 1994. He received the engineer degree in mecatronics engineering. Now is a Ph.D. student in Physical Sciences and Engineering at the Faculty of Sciences of Meknes. His current research interests are the multilevel power converters. He can be contacted at email: a.elgadari@edu.umi.ac.ma.

Youssef Ounejjar was born in Meknes, Morocco, in 1971. He received the B.Ing. and M.S. degrees in electrical engineering from the Ecole Nationale d'Ingénieurs de Sfax, Sfax, Tunisia, in 1996 and 1998, respectively, and the Ph.D. degree in electrical engineering from the École de Technologie Supérieure, Montréal, QC, Canada, in 2011. His current research interests are the multilevel power converters. He is associate professor at the Moulay Ismail University, Meknes, Morocco. He can be contacted at email: ounejjar@gmail.com.

Kamal Al-haddad received the B.Sc.A. and M.Sc.A. degrees from the University of Québec à at Trois-Rivières, Trois-Rivières, QC, Canada, in 1982 and 1984, respectively, and the Ph.D. degree from the Institute National Polytechnique, Toulouse, France, in 1988. He ispProfessor at School of Higher Technology, Montreal, Canada. He can be contacted at email: kamal.al-haddad@etsmtl.ac.