EVIDENT

WILEY

# Impact on Biological Systems and the Environment

This eBook is dedicated to the research of Professor David Wertheim. In collaboration with various groups, Professor Wertheim uses confocal microscopy to analyse the impact of different types of particles on human health and the environment, with a focus on human health-hazardous particles detected with solid-state nuclear track detectors (SSNTD). Download for free, today.

## **Graphene-Based Microwave Circuits: A Review**

Mohamed Saeed,\* Paula Palacios, Muh-Dey Wei, Eyyub Baskent, Chun-Yu Fan, Burkay Uzlu, Kun-Ta Wang, Andreas Hemmetter, Zhenxing Wang, Daniel Neumaier, Max C. Lemme, and Renato Negra

Over the past two decades, research on 2D materials has received much interest. Graphene is the most promising candidate regarding high-frequency applications thus far due to is high carrier mobility. Here, the research about the employment of graphene in micro- and millimeter-wave circuits is reviewed. The review starts with the different methodologies to grow and transfer graphene, before discussing the way graphene-based field-effecttransistors (GFETs) and diodes are built. A review on different approaches for realizing these devices is provided before discussing the employment of both GFETs and graphene diodes in different micro- and millimeter-wave circuits, showing the possibilities but also the limitations of this 2D material for highfrequency applications.

## 1. Introduction

The performance increases in recent communications standards in combination with the revolutionary research in new materials result in new application spaces and opportunities in high-frequency electronics. Particularly, 2D materials have attracted great attention due to their flexibility and ability for integration alongside with different substrates and form factors. Graphene, in particular, exhibits a high charge-carrier mobility,<sup>[1]</sup> which makes it interesting for high-frequency

```

M. Saeed, P. Palacios, M.-D. Wei, E. Baskent, C.-Y. Fan, R. Negra

Chair of High Frequency Electronics

RWTH Aachen University

Koppernikusstr. 16, 52074 Aachen, Germany

E-mail: melsayed@hfe.rwth-aachen.de

B. Uzlu, K.-T. Wang, A. Hemmetter, Z. Wang, D. Neumaier, M. C. Lemme

AMO GmbH

Otto-Blumenthal-Str. 25, 52074 Aachen, Germany

B. Uzlu, K.-T. Wang, A. Hemmetter, M. C. Lemme

Chair of Electronic Devices

RWTH Aachen University

Otto-Blumenthal-Str. 25, 52074 Aachen, Germany

D. Neumaier

Chair of Smart Sensor Systems

University of Wuppertal

Lise-Meitner-Str. 13, 42119 Wuppertal, Germany

The ORCID identification number(s) for the author(s) of this article

can be found under https://doi.org/10.1002/adma.202108473.

© 2022 The Authors. Advanced Materials published by Wiley-VCH

```

GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/adma.202108473

applications such as radio frequency identification (RFID) and near field communications (NFC) but also for intelligent reflecting surfaces (IRS). In addition, 2D materials have been shown to be excellent for sensing applications such as bio-, chemical-, nano-electro-mechanical, or high-bandwidth optoelectronic sensors.<sup>[2-4]</sup> These properties could be utilized in flexible electronic systems and smart wearable devices for biomedical purposes, environmental monitoring, and general sensor fusion and, when combined with 2D-based wireless communications, for applications in the Internet of Things or even 6G. In this review, we focus on the

high-frequency potential of graphene-based devices and circuits and refer to the widely available literature on 2D sensors.

Graphene is a promising candidate for electronic applications among the family of 2D materials due to its outstanding electrical and mechanical properties. The high charge-carrier mobility and saturation velocity,<sup>[1,5]</sup> together with the ability for large-scale integration on different substrates make graphene a prime candidate for RF, millimeter-, and sub-millimeter-wave circuit applications. One advantage of graphene as an emerging technology that makes it appealing for new high-frequency applications is its mechanical flexibility due to its 2D nature. Last but not least, graphene can be integrated on different substrates without substantially changing the device operation characteristics and can thus be an add-on to cost-effective technologies which do not provide comparable highfrequency performance on their own. Nevertheless, graphene also has some drawbacks when used as a channel material in field effect transistors.<sup>[6,7]</sup> These are mainly associated with the lack of an electronic bandgap as will be discussed in this review.

**Table 1** shows a comparison of the electrical properties between intrinsic CVD-grown graphene,<sup>[8]</sup> silicon (Si), gallium nitride (GaN), and gallium arsenide (GaAs) at room temperature. Here, the focus is on properties relevant for high performance devices, that is, effective charge-carrier mass ( $m^*/m_0$ ), electron ( $\mu_e$ ), and hole mobility ( $\mu_h$ ), peak velocity ( $\nu_{peak}$ ), and energy bandgap ( $E_G$ ). The graphene properties are clearly superior compared to the established semiconductor materials that are used widely to realise high-frequency devices, with substantially one exception, the lack of an energy bandgap.

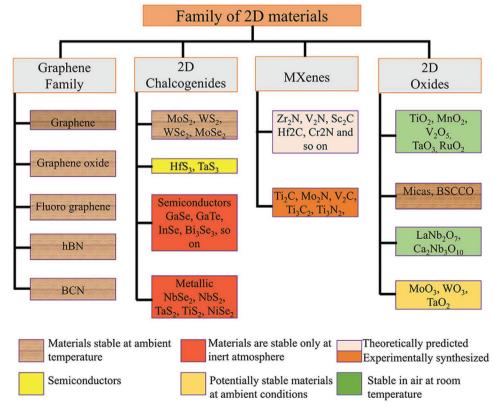

Beyond graphene, the family of 2D materials is growing constantly. The main branches are summarized in the graph in **Figure 1** and classified according to their stability in various environments and temperatures. Of these, graphene

Table 1. Comparison between intrinsic graphene and other semiconductors in terms of  $m^*/m_0$ ,  $\mu_e$ ,  $\mu_h$ ,  $v_{peak}$ , and  $E_G$ .

|                                                         | Si   | GaN  | GaAs  | Graphene <sup>[8]</sup> |

|---------------------------------------------------------|------|------|-------|-------------------------|

| m*/m <sub>0</sub>                                       | 0.98 | 0.19 | 0.063 | ≈0                      |

| $\mu_{\rm e}  [{\rm cm^2 \ V^{-1} \ s^{-1}}]$           | 1400 | 1600 | 8000  | 320 000                 |

| $\mu_{\rm h}  [{\rm cm}^2  {\rm V}^{-1}  {\rm s}^{-1}]$ | 500  | 200  | 400   | 350 000                 |

| $ u_{\rm peak}$ [×10 <sup>7</sup> cm s <sup>-1</sup> ]  | 1    | 2.4  | 1.8   | 10                      |

| E <sub>G</sub> [eV]                                     | 1.12 | 3.4  | 1.43  | 0                       |

has received most of the attention with respect to high-frequency devices and circuits. Table 2 compares the measured electrical properties of graphene versus other 2D materials. The comparison clearly shows that graphene has the highest potential to be employed in high-frequency applications due to its outstanding carrier mobility compared to all other 2D materials in the table.<sup>[12,13]</sup> Nevertheless, these reported numbers are all below the theoretical intrinsic limit. Better results are typically obtained from 2D materials that are peeled off natural crystals versus materials grown by conventional semiconductor growth methods. Hence, the influence of material growth and subsequent processing is discussed in the first part of this review. We present different methods of growing and transferring graphene, with a focus on the quality, reproducibility, and variability of the grown graphene, because these aspects are crucial for device modeling and variabilitytolerant circuit design. The second part of the review covers the current state-of-the-art of graphene-based devices in

microwave circuits. We discuss the reported graphene-based devices and circuit components, and in particular their modeling approaches for circuit design. In the following, we present and describe the implementation of different microwave circuits employing graphene-based devices and evaluate their performance with respect to commercial technologies. Our perspective on the potential and feasibility of graphene for realizing high-frequency circuits and for enabling applications beyond what is possible with classic semiconductors concludes this review.

## 2. Growth and Transfer of Scalable Graphene

Commercial applications of graphene-based electronic devices and circuits rely on the availability of high-quality, large-scale, and single-layer graphene. Meanwhile, wafer-scale process technology for transfer (or transferless growth), dielectric encapsulation, and electrical contacts<sup>[16–19]</sup> play also a significant role.

State-of-the-art devices in laboratory environment frequently employ exfoliated single-layer graphene flakes. However, this material is not scalable for high throughput or large graphene areas, especially on wafer-scale. Exfoliated graphene flakes typically have a maximum area of  $3 \times 10^5 \,\mu m^{[20]}$  and cannot be placed deterministically across a wafer, therefore preventing industrial, wafer-scale fabrication processes.

In this section, we will review scalable technology for graphene growth and transfer, which is crucial for the application in microwave circuits.

Figure 1. 2D materials family.<sup>[9-11]</sup> Reproduced with permission.<sup>[12]</sup> Copyright 2020, American Chemical Society.

Table 2. Comparison between intrinsic graphene and other 2D materials in terms of:  $\mu_{\rm e},\,\mu_{\rm h},$  and  $E_{\rm G}.$

|                                                         | MoS <sub>2</sub> <sup>[14]</sup> | WS <sub>2</sub> <sup>[14]</sup> | BP <sup>[15]</sup> | B <sub>2</sub> Se <sub>2</sub> <sup>[15]</sup> | Graphene <sup>[8]</sup> |

|---------------------------------------------------------|----------------------------------|---------------------------------|--------------------|------------------------------------------------|-------------------------|

| $\mu_{\rm e}  [{\rm cm}^2  {\rm V}^{-1}  {\rm s}^{-1}]$ | 200                              | 120                             | 68 810             | 510                                            | 320 000                 |

| $\mu_{\rm h}  [{\rm cm^2 \ V^{-1} \ s^{-1}}]$           | 152                              | 210                             | 26 050             | 11 400                                         | 350 000                 |

| E <sub>G</sub> [eV]                                     | 1.8                              | 1.54                            | 0.91               | 4.94                                           | 0                       |

#### 2.1. Graphene Growth by CVD

Large-area chemical vapor deposition (CVD) of graphene has been steadily improved upon in the form of graphite layer growth, even before the discovery of the field-effect in singlelayer graphene. During a standard graphene growth process, a metallic substrate (typically Cu) is heated inside a deposition chamber in a hydrocarbon-containing atmosphere. The elevated temperature and surface chemistry of the substrate causes the hydrocarbon precursor to decompose. Carbon settles on the Cu surface at nucleation sites and grows into single-layer graphene flakes at various orientations. Individual graphene patches originating from different nucleation sites eventually meet and cover the entire surface of the Cu substrate with the formation of grain boundaries.<sup>[21]</sup> The resulting large-area graphene is, therefore, typically of polycrystalline nature with domains ranging up to several millimeters.<sup>[21–24]</sup>

Graphene grain boundaries present defects which lower the overall charge-carrier mobility of the active channel in elec-

tronic devices.<sup>[21,25]</sup> A significant amount of research has therefore been aimed at the enlargement of domain sizes, with the ultimate goal of CVD-grown, wafer-scale, single-crystal, singlelayer graphene.<sup>[26,27]</sup> This has been mainly accomplished by a reduction of nucleation sites through adjustments in the CVD process parameters, prepatterning of the Cu surface, or seeding with exfoliated graphene flakes.<sup>[21]</sup>

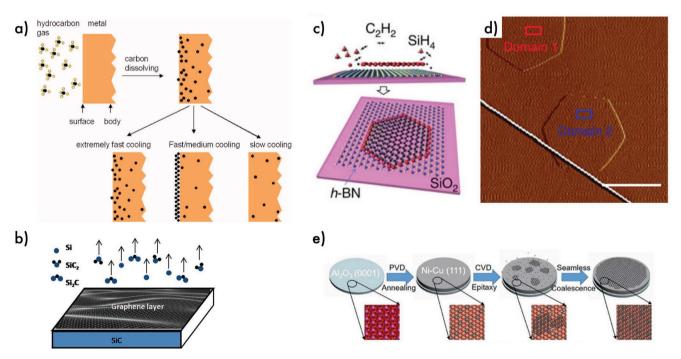

Growth on other metals has also been demonstrated to obtain uniform and large-area coverage of graphene on the growth substrate. However, the solubility of C in many metals other than Cu is comparatively high. C dissolved in the metal is released during the cooling step and precipitates at the metal surface in a process called "segregation growth mechanism" (**Figure 2a**). Unlike the surface adsorption-based growth process on Cu, growth on metals like Ni, Fe, or Au is therefore more challenging in terms of layer control.<sup>[21,28]</sup>

CVD-grown graphene has demonstrated charge-carrier mobility above 350 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1,[8]</sup> but the size of such material is still limited. However, a great effort has been devoted into this research direction to further improve the quality of scalable material, which is crucial for circuits applications.

#### 2.2. Graphene Growth on Nonmetallic Substrates

For graphene-based electronics it is often necessary to deposit graphene on an insulator. The transfer step from Cu or other metallic surfaces also introduces additional chemical dopants

**Figure 2.** a) Schematic of segregation graphene growth on other metals with high carbon solubility. Carbon dissolves in the metal and migrates toward the surface during cooling, forming a graphene layer. Reproduced with permission.<sup>[29]</sup> Copyright 2008, American Institute of Physics. b) Epitaxial growth of graphene on SiC. Reproduced with permission.<sup>[30]</sup> Copyright 2016, Wiley-VCH. c) Schematic of graphene growth on hBN. d) AFM image of graphene domains on top of a hBN substrate. Reproduced under the terms of the CC-BY Creative Commons Attribution 4.0 International license (https://creativecommons.org/licenses/by/4.0).<sup>[31]</sup> Copyright 2015, The Authors, published by Springer Nature. e) Multi-step graphene growth on a sapphire substrate, involving the deposition of a sacrificial crystalline metal layer and growth of the graphene. The crystalline metal layer makes seamless coalescence of the individual graphene flakes from different nucleation sites possible. Reproduced with permission.<sup>[32]</sup> Copyright 2021, Wiley-VCH.

and mechanical stress, which further degrade the electrical characteristics of graphene.<sup>[26,32,33]</sup> Therefore, growth on insulating substrates is intensely researched.

#### 2.2.1. Growth on SiC Substrate

www.advancedsciencenews.com

Large-scale graphene can be synthesized by epitaxial growth on SiC surfaces (Figure 2b). During the decomposition process, Si sublimates off the surface, leaving the remaining C atoms to rearrange themselves into a mono-atomic layer. While this growth mode results in graphene with good mobility, the strong adhesion between substrate and graphene limits this process for many applications.<sup>[26,34]</sup>

#### 2.2.2. Growth on Hexagonal Boronitride Substrate

Hexagonal boronitride (hBN) is suitable as a growth substrate because of its minimal lattice mismatch to graphene and good insulating properties.<sup>[35]</sup> Graphene growth has been demonstrated on Cu foils covered in exfoliated hBN flakes (Figure 2c,d), which (at a thickness of a few mono-atomic layers) shield the catalytic capacity of the underlying Cu surface only a little.<sup>[28,31]</sup> Nevertheless, graphene growth on hBN faces the challenge of high-quality, large-scale hBN growth instead.

#### 2.2.3. Growth on Sapphire Substrate

Metal-free, direct graphene growth on sapphire (Figure 2e) still poses a challenge, with state-of-the-art processes only recently reaching graphene diameters of up to 6 with mobilities around 2000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>.<sup>[26]</sup> Compared to Cu, sapphire shows less of a catalytic effect and thus makes higher process temperatures nec-

www.advmat.de

The ultimate goal of growing wafer-scale, single-crystal, and single-layer graphene has not been reached yet and although many other alternative growth approaches have been demonstrated with varying advantages and disadvantages, CVD growth of graphene on Cu remains as the most promising for large-area, scalable, and low-cost growth with enabled transfer on arbitrary substrates (e.g., dielectrics, flexible substrate) for device fabrication.

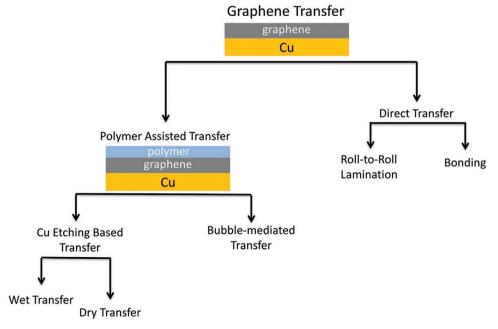

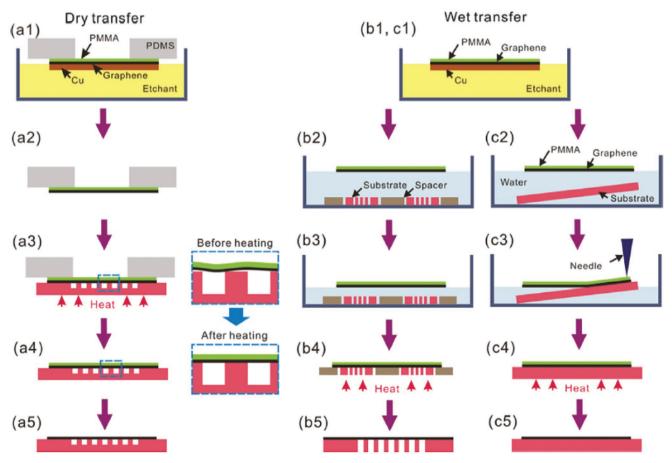

#### 2.3. Graphene Transfer

The transfer processes of CVD graphene have been investigated widely in literature,<sup>[36–38]</sup> as the quality of this processing step plays a significant role in attaining the unique electrical properties in high-performance devices. Figure 3 shows the commonly used large-area graphene transfer methods, where the methods are divided into two main categories as polymerassisted and direct-transfer methods. The polymer-assisted transfer indicates that the graphene is transferred to a target substrate with a polymer-based carrier material or supporting layer, which will be removed by chemical or physical means afterward to complete the transfer process. On the other hand, the direct transfer takes advantage of the binding force of the pretreated target substrate with the graphene to achieve the transfer process without involving an additional support layer. In the following, transfer methods listed in Figure 3 are explained.

#### 2.3.1. Polymer-Assisted Transfer

Polymer-assisted transfer relies on coating of the graphene surface with a polymer such as poly(methyl methacrylate) (PMMA)

Figure 3. Large-area transfer methods of CVD graphene.

as a protective layer and also for providing easy handling during the transfer. After the polymer coating, the Cu is removed in Cu etchants solutions, which leaves a floating PMMA–graphene stack on the surface of the solution, this process refers to Cu-etching-based transfer. The PMMA–graphene stack is then carried to DI water to rinse the etching solution leading to a clean graphene surface.

For wet transfer, after this step, the stack is transferred onto a target substrate and gradually heated to remove the water molecules trapped between the graphene and the substrate and to provide a good adhesion. This method is commonly referred to in the literature because known as reliable method. However, water molecules trapped in between the graphene and the transfer substrate can influence the characteristics of graphene and graphene devices as water molecules will cause additional doping.<sup>[39,40]</sup>

For dry transfer, PMMA–graphene stack floating on DI water is taken out and dried before the transfer and stamped on the preheated target substrate. This method is also referred as semi-dry transfer since the Cu is etched by wet chemistry before the transfer and eliminates the additional doping on graphene surface due to water molecules. However, adhesion between the graphene and transfer substrate is the limiting factor and the quality of transfer, in comparison with the wet transfer, is not as reliable.<sup>[36]</sup> **Figure 4** summarizes the above discussion comparing the wet and dry transfer.

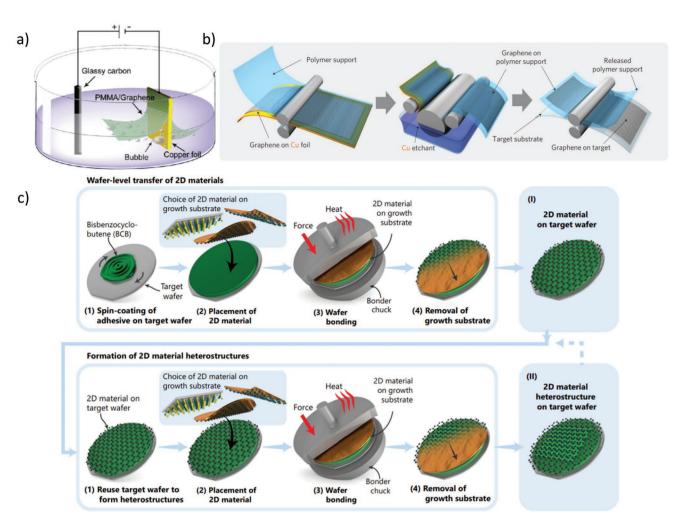

Bubble-mediated transfer (Electrochemical delamination) (Figure 5a) is a technique to attain etching-free transfer of graphene. CVD graphene with supporting layer is placed at the cathode of an electrolysis cell, then the bubbles (H<sub>2</sub>) generated by water electrolysis provide the peeling force to delaminate the supported PMMA/graphene layer from Cu. Delaminated PMMA/Cu stack then moves to the surface of the electrolyte due to the hydrophobic nature of PMMA and graphene, which can be transferred to the target substrate eventually. This transfer method is known to be low cost and time efficient. However, water electrolysis and thus bubble formation can cause damage on the graphene surface, which limits the reliability and scalability of the method.<sup>[42]</sup>

#### 2.3.2. Direct Transfer

*Roll-to-Roll Lamination*: The roll-to-roll lamination method (Figure 5b) allows transferring of large-area graphene with low cost while enabling the reusability of the growth substrate. In this method, graphene on Cu passing through hot rollers is laminated on the target substrate and the Cu is mechanically peeled off (or chemically etched). The roll-to-roll transfer technique has the potential to realize the large-scale industrialization of graphene transfer. However, the transfer is performed on thermally active lamination

**Figure 4.** Schematic illustration of dry and wet graphene transfer processes. Reproduced under the terms of the CC-BY Creative Commons Attribution 4.0 International license (https://creativecommons.org/licenses/by/4.0).<sup>[41]</sup> Copyright 2017, The Authors, published by Beilstein-Institut.

www.advmat.de

**ADVANCE**

**Figure 5.** a–c) Schematic illustrations of electrochemical delamination (a), roll-to-roll (b), and the wafer bonding transfer process (c). a) Reproduced with permission.<sup>[42]</sup> Copyright 2011, American Chemical Society. b) Reproduced with permission.<sup>[48]</sup> Copyright 2010, Springer Nature. c) Reproduced under the terms of the CC-BY Creative Commons Attribution 4.0 International license (https://creativecommons.org/licenses/by/4.0).<sup>[49]</sup> Copyright 2021, The Authors, published by Springer Nature.

foils such as polyethylene (PE) or poly(vinyl chloride) (PVC) or onto an arbitrary substrate which is coated with thermal lamination glue. This limits the substrate choice and also the cleanliness of the graphene. Additionally, for thin-film fabrication processes, temperature requirements are generally not satisfied by the laminating substrates and thermal lamination glue.<sup>[43–47]</sup>

*Wafer Bonding*: In a recent study by Quellmalz et al.,<sup>[49]</sup> largearea integration and wafer scale transfer of 2D materials was demonstrated by a wafer bonding method (Figure 5c). In this method, the target substrate is spin-casted by an adhesive layer and the bonding of the graphene on Cu foil is provided by controlling the process temperature and pressure to enhance the bonding energy between the graphene and the substrate layer, where the growth substrate Cu is removed afterward to accomplish the transfer. This method satisfies all ICCC standards defined above, and also allows stacking several layers of 2D materials such as hBN or MoS<sub>2</sub> to form heterostructures in a scalable way. One drawback of this method is the permanently remaining adhesive layer on the substrate after the transfer, which interfaces with the transferred 2D material and may affect the electrical properties of the 2D material due to doping and can limit the maximum usable temperature for further fabrication steps. However, the authors successfully showed a uniform graphene transfer and fabricated top-gated graphene-based fieldeffect transistors (GFETs) with moderate mobility. This method promises scalable transfer compatible for a wide range of application areas, spanning over electronics, sensing, and photonics.

## 3. Graphene-Based Devices and Their Modeling

In order to use graphene devices in circuit design, the graphenebased devices have to be characterized and modeled. In this section the structure as well as the different modeling approaches of reported state-of-the-art graphene devices is discussed.

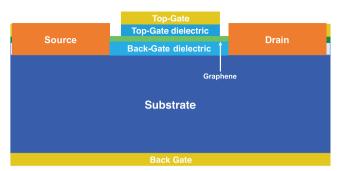

#### 3.1. Common Graphene Transistors

GFETs are mainly developed either as bottom-gated and topgated configurations. Each arrangement has unique development procedures, either regarding the synthesis methods of www.advancedsciencenews.com

graphene, such as mechanically exfoliation and CVD growth, or regarding the fabrication processes such as photolithography and electron beam lithography.

#### 3.1.1. Bottom-Gated Configuration

The first GFET in the literature was developed in 2004 with a global bottom-gate configuration.<sup>[1]</sup> Since then, the bottomgated structure is widely used to form GFETs mainly due to two reasons. As illustrated in Figure 6, the final arrangement of a bottom-gated GFET leaves the graphene channel at the top forming thus conveniently an interface between the transistor and the environment. The overall device structure lends itself thus to sense and detect biomarkers or light, since the interaction between the exposed graphene layer and the light/biomarker alters the electrical characteristics of the graphene as function of type and amount of target substance. The presence of the substance can thus be quantitatively evaluated through measuring the change in the transport characteristics of the channel. The second reason is that after the graphene has been transferred, the amount of processing steps before encapsulation is minimized, resulting in higher quality graphene and thus better performing devices.

Despite the promising potential of graphene for high-frequency electronics, it is difficult to achieve high transconductance  $(g_m)$  with the bottom-gated GFET topology due to the resulting small gate capacitance. Moreover, it is challenging

www.advmat.de

Figure 6. Generic GFET structure with top and back gate.

to attain current saturation in GFETs, which absence leads to poor DC gain ( $A_V$ ) and large channel conductance ( $g_{DS}$ ).<sup>[52]</sup> As a consequence, extremely high control voltages are required to reach usable  $g_m$ -values and the maximum frequency of oscillation ( $f_{max}$ ), yet such large input voltages are not likely to be seen in ordinary electronic applications. In order to improve  $g_m$  and facilitate the integration of bottom-gated GFETs in RF electronics, it is either needed to engineer the bandgap, leading to low carrier mobility ( $\leq 0.05 \text{ m}^2 \text{ V}^{-1} \text{ s}^{-1}$ ),<sup>[53]</sup> or to engineer the velocity saturation to improve  $f_{max}$ , for example, up to 70 GHz,<sup>[54]</sup> or the saturation current ( $I_{sat} \approx 20 \text{ A cm}^{-1}$ ).<sup>[55]</sup>

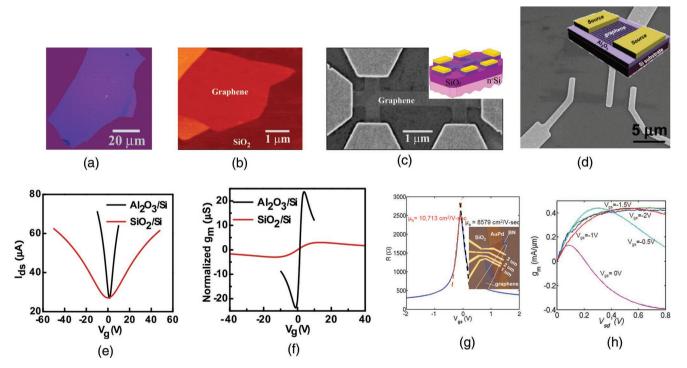

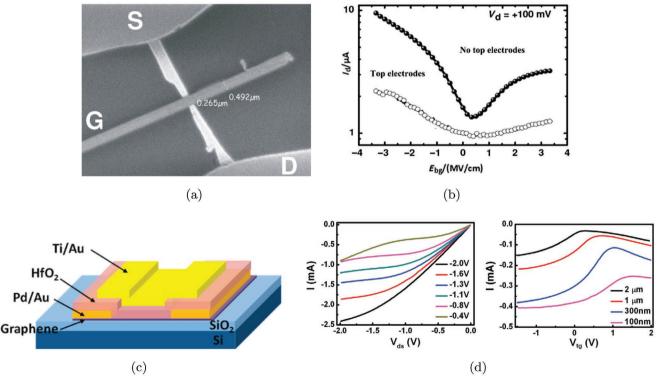

As depicted in **Figure 7**d, a single-layer graphene (SLG)based bottom-gated GFET has been developed to prove the effect of a dielectric layer on  $g_m$  and the transfer characteristics.<sup>[50]</sup> It is clear from Figure 7e,f that the improvements in

**Figure 7.** a) Optical image of a multilayer graphene flake on top of a Si wafer, b) AFM image of SLG, c) SEM image of an experimental device with the schematic view of the same GFET as inset. a-c) Reproduced with permission.<sup>[1]</sup> Copyright 2004, The American Association for the Advancement of Science. d) SEM image of a bottom-gated GFET on a 72 nm Al<sub>2</sub>O<sub>3</sub>/Si substrate, and the inset display schematics of the device. e) Transfer characteristics of GFET on 300 nm SiO<sub>2</sub>/Si and 72 nm Al<sub>2</sub>O<sub>3</sub>/Si substrate and f) transconductance of GFET on 300 nm SiO<sub>2</sub>/Si and 72 nm Al<sub>2</sub>O<sub>3</sub>/Si substrate. e,f) Reproduced with permission.<sup>[50]</sup> Copyright 2009, IOP Publishing. g) Transport characteristics of h-BN based GFET with optical image inset and h) small-signal transconductance. Reproduced with permission.<sup>[51]</sup> Copyright 2010, IEEE.

performance have been achieved by using a thin (72 nm) high-k dielectric (Al<sub>2</sub>O<sub>3</sub>). The usual V-shape transfer characteristics and significant improvement in the transconductance have been realized with much lower control voltages. Alternatively, h-BN has been used to improve the performance of GFETs further. A chip microscopy image of a bottom-gated GFET based on a h-BN gate dielectric is depicted in Figure 7g. As shown in Figure 7g,h, this approach boosted the carrier mobility to above  $1 \text{ m}^2 \text{ V}^{-1} \text{ s}^{-1}$  with an associated intrinsic  $g_{\text{m}}$  above 400 sM mm<sup>-1</sup>. In another study, the saturation velocity has been increased by exploiting h-BN.<sup>[56]</sup> Thus, one can conclude that the introduction of high-k materials offers superior performances compared to plain SiO<sub>2</sub>.

#### 3.1.2. Top-Gated Configuration

The other configuration for graphene transistor is the top-gated structure, which also is the most commonly employed device configuration used in RF applications.<sup>[57–59]</sup> This topology is the best choice for processes providing a thin oxide layer. A thin oxide layer is essential to enable stronger control over the doped carriers in the channel. Thus, channel modulation can be achieved with relatively low gate control voltages. However, developing the oxide layer on top of the graphene while preserving the graphene lattice structure and mobility is laborious. The first developed top-gated GFET from SLG is depicted in **Figure 8**a, where the inferior carrier mobility due to scattering

introduced by the top-gate oxide is evident, as also demonstrated in Figure 8b.<sup>[60]</sup> Moreover, the mobility can be significantly degraded because of the charged impurities confined in the graphene–insulator interface.<sup>[51]</sup>

There are studies on how to overcome the mobility degradation via the development of an alternative insulator layer on top of the graphene. Although h-BN has a dielectric constant of  $\approx$ 3.4, it has been one of the most appealing materials used as an oxide layer due to its hexagonal lattice structure, which is compatible with the one of SLG.[51] It has been demonstrated that the high mobility of graphene is preserved even if the SLG is sandwiched between layers of h-BN.<sup>[62]</sup> In another study, HfO<sub>2</sub> has been employed as insulating layer in a top-gated GFET structure, as shown in Figure 8c. The current saturation of the resulting device has been investigated for various gate lengths with values down to 100 nm, as presented in Figure 8d. The transfer curves of the GFETs in Figure 8e clearly indicate a shift of the Dirac point to positive voltage values for decreasing gate lengths. As shorter graphene channels require larger drain voltages, it has become necessary to apply high gate voltages to achieve the lowest Dirac point.<sup>[63]</sup>

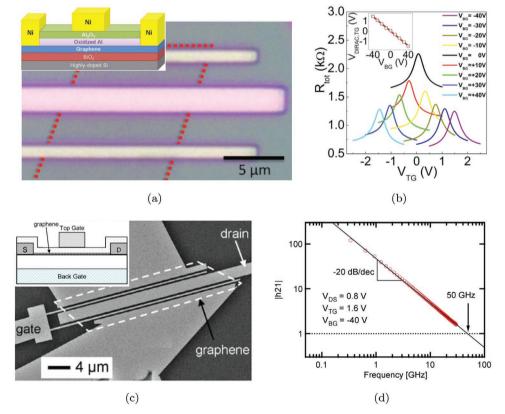

Control over the position of the Dirac point is crucial to adjust the operation of the transistor. In order to facilitate such control over the Dirac point, bottom gates have been fabricated together with top gates in GFETs.<sup>[64,65]</sup> As a consequence of this improved control, the series resistance could be reduced via the electrostatic dope of graphene, providing superior RF performance compared to top-gated GFETs. Moreover, high carrier mobility<sup>[64]</sup> and improved cutoff frequency<sup>[65]</sup> have been

**Figure 8.** Top-gated GFET topologies. a) SEM image of first top-gated GFET and b) the electrical measurement in GFETs with and without top-gate electrodes. a,b) Reproduced with permission.<sup>[60]</sup> Copyright 2007, IEEE. c) Schematic of GFET with HfO<sub>2</sub> gate dielectric, and d) output characteristics, showing the current saturation and transfer characteristics of transistor with various channel lengths. c,d) Reproduced with permission.<sup>[61]</sup> Copyright 2011, American Chemical Society.

demonstrated using a dual-gated device configuration. **Figure 9**a illustrates such a fabricated dual-gated GFET and its corresponding schematic. Figure 9b clearly indicates the control of the Dirac point by the integration of the bottom gate into the transistor. Figure 9c is the chip microscopy image of a specially designed dual-gated GFET optimized for RF applications that reaches a cutoff frequency of 50 GHz, as shown in Figure 9d, which exceeds that of a Si MOSFET with the same gate length.

DVANCED

www.advancedsciencenews.com

Alternative GFET topologies have also been studied resulting in some improvements. Since the top gate introduces a parasitic capacitance, the gate has been buried into the substrate, lowering the fringing capacitance to improve the RF performance by increasing the vertical separation between the gate metal and the source/drain contacts.<sup>[66]</sup> Since the oxide deposition on top of the graphene is no longer needed in the buriedgate configuration, carrier mobility degradation is prevented.<sup>[67]</sup> On the other hand, the carrier mobility profile of graphene transistors has been improved by suspended gate configurations. A high carrier mobility of  $4.4 \text{ m}^2 \text{ V}^{-1} \text{ s}^{-1}$  has been achieved with a suspended graphene topology, as it provides an optimal interface to overcome substrate-associated scattering.<sup>[68]</sup>

#### 3.1.3. Performance Assessment Based on Graphene Transistor Modeling

It is highly desired to have a physics-based model before a new device or system is development in order to predict the behavior of the device. Models generally facilitate the capabilities to test the theoretical aspect and soundness of the process in question, before the actual realization of the process. Specifically, a model allows assessing the performance of the overall structure. Since the models reflect the intrinsic transistor behavior, additional extrinsic capacitances are added to complete the model for high-frequency applications.

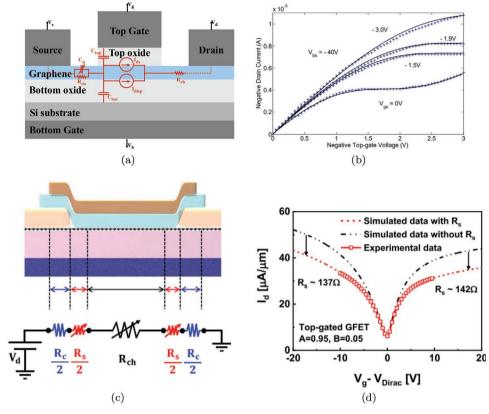

Both analytical and numerical models have been developed to reflect the behavior of real graphene transistors.<sup>[69]</sup> Figure 10a shows a dual-gated GFET structure, alongside with its detailed transistor model. The quantum capacitance  $C_q$  has been implemented to represent variations due to the channel charge density and charge impurities around the Dirac point. The model has proven to be accurate by comparison with experimental data, as shown in Figure 10b.

As discussed in the previous section, the superior performance of the buried-gated arrangement in comparison to its top-gated counterparts has been additionally confirmed by corresponding device model representations.<sup>[67]</sup> The cross-section schematic of a top-gated transistor with its resistance model is depicted in Figure 10c. The series resistance,  $R_s$ , is generated due to the top-gated topology, which disappears in the buriedgated structure. Moreover, Figure 10d exhibits the improvements of the transfer characteristics of the GFET by significant reduction of the specific access resistance with the buried gate. Such models have been developed and implemented using commonly employed platforms for circuit design and simulations

**Figure 9.** a) Chip microscopy image and schematic view of dual-gated GFET and b) total resistances with respect to top gate voltage at various bottom gate potentials. a,b) Reproduced with permission.<sup>[64]</sup> Copyright 2009, AIP Publishing. c) SEM image of double channel graphene transistor with schematic view and d) RF performance of GFET, showing the current gain and cutoff-frequency ( $f_1$ ). c,d) Reproduced with permission.<sup>[65]</sup> Copyright 2010, IEEE.

**Figure 10.** Various GFET model representations and transistor performances. a) Dual-gated topology with intrinsic transistor model, and b) experimental data (+) and proposed model (-) comparison in terms of output characteristics. a,b) Reproduced with permission.<sup>[69]</sup> Copyright 2013, IEEE. c) Top-gated graphene transistor structure including resistance model and d) transfer characteristics of experimental data and model, emphasizing the influence of series resistance. c,d) Reproduced with permission.<sup>[67]</sup> Copyright 2019, IOP Publishing.

such as MATLAB, VHDL-AMS, and Verilog.<sup>[70]</sup> An extension of the dual-gated transistor model, provided in Figure 5a, to top or bottom-gated topologies can simply be realized by either addition or removal of the respective equivalent lumped elements.

#### 3.2. Common Graphene Diodes

Diodes are indispensable circuit elements for RF electronic devices and are typically used as nonlinear devices for RF signal detection, frequency multiplication, and frequency translation. Schottky diodes have been the main components in high-frequency applications for a span of time because of their excellent characteristics. However, their incompatibilities with thin-film technology have restricted their applications in emerging technologies such as flexible electronics. On the contrary, metalinsulator-metal (MIM) diodes, due to their compatibility with thin-film processes, have become popular devices. Moreover, MIM diodes provide low zero-bias resistance, which results in higher operating frequencies compared to Schottky diodes. However, MIM diodes exhibit inferior performance compared to semiconductor-based diodes in terms of asymmetry and nonlinearity.<sup>[71]</sup> Therefore, graphene diodes based on the MIM diodes structure have been introduced by replacing one metal electrode with graphene.

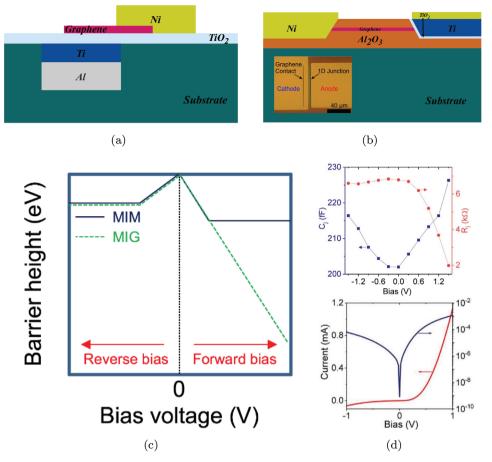

The 2D metal-insulator-graphene (MIG) diode topology, the operation principle of the device, and the extension of the diode concept to a 1D MIG diode are covered in the following section.

#### 3.2.1. 2D MIG Diode

A typical MIG diode configuration is given schematically in **Figure 11a**. The thin-film compatibility of the MIG diode and its low series resistance has enabled the exploitation of MIG diodes in RF applications due to the high carrier mobility of graphene.<sup>[72–74]</sup> Moreover, the low junction capacitance and the low-energy-barrier oxide layer increased the potential of MIG diodes to be used in millimeter-wave (mmWave), sub-mmWave and terahertz (THz) applications.

Although the idea of the MIM diode configuration is exploited, the MIG diode employs a distinct operation principle. The functionality of the MIG diode is dominated by the modulation of the barrier height at the insulator-graphene interface via an applied bias.<sup>[77]</sup> As shown in Figure 11c, in the reverse bias the barrier height for electrons to transfer from M1 to M2 in the MIM structure, and from M to G in the MIG decreases with increasing reverse voltage until it reaches the potential difference between the work function ( $\phi_M$ ) of M1 and the conduction band edge of the insulator. In forward bias, the barrier height for electrons to Transfer from M2 to M1 in the

**Figure 11.** a) Schematic view of 2D MIG diode, b) schematic cross-section of 1D MIG diode and chip microscopy image is shown in the inset, c) barrier height versus applied bias voltage for both MIM and MIG diodes with their structure as inset. a–c) Reproduced with permission.<sup>[75]</sup> Copyright 2018, IEEE. d) Extracted junction resistance and junction capacitance values, and *I–V* characteristics of typical 1D MIG diode. Reproduced with permission.<sup>[76]</sup> Copyright 2019, American Chemical Society.

MIM structure is reduced until it reaches the potential difference between the work function of M2 and the conduction band-edge of the insulator. This creates the necessary asymmetry between forward and reverse operation. In the case of the MIG diode, the barrier height for electrons to transfer from graphene, G, to metal, M, decreases with increasing forward bias, which explains the high on-current and higher asymmetry for MIG diodes compared to MIM diodes. Thus, this different charge transfer method, that is, the lowering of the barrier with the induced bias in the MIG diode, solves the required trade-off between current density and asymmetry in MIM diodes. Therefore, the MIG diode yields higher performance than the MIM diode concerning asymmetry and nonlinearity. Moreover, MIG diodes have also been developed on top of flexible substrates such as Kepton and polyimide, paving the way for wearable graphene-based RF electronics.<sup>[78]</sup>

#### 3.2.2. 1D MIG Diode

Although the diffusion junction capacitance in typically stacked MIM and MIG diodes is acceptable low, the intrinsic junction capacitance in such diodes is large due to the parallel plate capacitance resulting from the configuration. As such, the maximum operation frequencies are limited by this capacitance. Moreover, since the capacitance and series resistance are inversely proportional in terms of area, a scaling of the diode does not improve the frequency of operation. Therefore, the 1D MIG diode was devised by exploiting the carrier emission from the edges of graphene to reduce the series resistance and improve  $f_{\text{max}}$  and  $f_{\text{t}}^{[76,79]}$  The arrangement of the 1D MIG diode is given schematically in Figure 11b. As it can be inferred from Figure 11d, the junction capacitance is significantly reduced by scaling down the junction area to a product of the SLG atom thickness times the contact width. Furthermore, the 1D MIG diode exhibits not only similar DC response as the 2D MIG diode, but provides approximately two orders of magnitude higher on current, as a result of its low junction capacitance and access resistance.

Based on published results, 1D MIG diodes outperform 2D counterparts also in terms of RF performance. The 1D diode cutoff frequency is calculated theoretically as 2.4 THz from numerical and experimental data.<sup>[80]</sup> Recently power detection via rectennas based on 1D MIG diodes on a flexible substrate has been demonstrated with a measured maximum responsivity of 80 V/W at 167 GHz and a minimum noise equivalent

power (NEP) of 80 pW Hz<sup>-0.5</sup>.<sup>[81]</sup> These results prove the feasibility of energy harvesting and terahertz power detection on flexible substrates for application in, for example, wearable electronic devices enabled by graphene electronics.

#### 3.2.3. Graphene-Based Diode Modeling

M2

www.advancedsciencenews.com

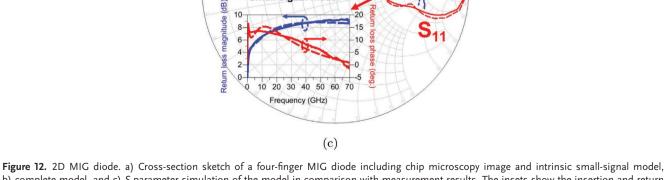

As graphene is a nonlinear material, simulation of graphenebased devices is not straight forward. Therefore, equivalent circuit models need to be extracted in order to predict the performance of devices and circuits based on these devices. The sketch of the cross-section of a four-finger MIG diode is depicted in Figure 12a alongside with an optical microscopy image and the small-signal model parameters of the intrinsic diode as inset.

A literature review reveals the limited effort has been put in so far in modeling MIG diodes. The most realistic, detailed, and well-developed model has been reported in ref. [82]. The overall small-signal model including the extrinsic parasitics is given in Figure 12b. The diode has been modeled as a series combina-

anhen

MI

magnitude (dB) 40 30

loss 10

20

Ó

M2

(a)

TiO

.M2

10 20 30 40 50 60

Frequency (Hz) Measurements Small-signal model

M2

tion of a linear capacitance,  $C_1$ , and a bias-dependent, nonlinear capacitance,  $C_2$ . In addition, a DC bias-dependent nonlinear junction resistance which is composed of the series combination of the leakage resistances,  $R_1$  and  $R_2$ , and the graphene sheet resistance, R<sub>G</sub>, has been included. For the diode, the physical implementation ensures that the linear series capacitance,  $C_1$ , is larger than the nonlinear capacitance,  $C_2$ , so that C2 dominates the equivalent capacitance. On-wafer S-parameter measurements have been carried out from 10 MHz-70 GHz for fabricated diodes with different bias voltages ranging from -2 to 2 V. The accuracy of this model over the wide frequency range can be seen in Figure 12c where simulation and measurement data are compared. Accordingly, less than 1 dB of mismatch in magnitude and better than 2° of phase mismatch for return and insertion loss have been achieved, as shown in the insets.

www.advmat.de

## 4. Graphene-Based Microwave Circuits

Graphene circuits have been reported covering the frequency range from DC up to 200 GHz and employing GFETs. This

11

Cf\_pad

(b)

Intrinsic diode

20

40

-60 80

**S**<sub>21</sub>

70

b) complete model, and c) S-parameter simulation of the model in comparison with measurement results. The insets show the insertion and return loss comparison. a-c) Reproduced with permission.<sup>[82]</sup> Copyright 2018, IEEE.

M2

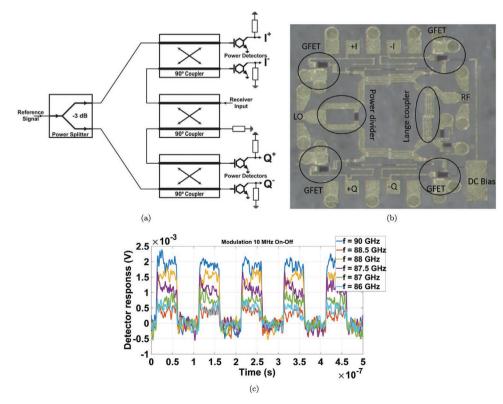

includes frequency mixers, frequency multipliers, power detectors, amplifiers, and oscillators. On the other hand, due to the poor gain provided by GFETs, only few receiver and transmitter systems have been reported. The limited  $f_{\rm T}$  and  $f_{\rm max}$  of GFETs restricts the frequency of operation in GFET-based amplifiers. While in the reported frequency conversion circuits the nonlinearities of GFETs have been utilized to be able to operate the devices beyond their  $f_{\rm T}$  and  $f_{\rm max}$ . Another issue which affects the employment of GFETs in complex circuits and systems is the low reproducibility of matched devices as well as the low yield especially for GFETs with mechanically exfoliated graphene. Accordingly, the circuits and systems to date comprise only a low number of active devices within a single circuit. Circuits reported in literature based on graphene diodes operate at higher frequency. Since CVD-based graphene diodes have good reproducibility some of the reported circuits employ a few active components.

#### 4.1. Amplifiers

ADVANCED SCIENCE NEWS \_\_\_\_\_ www.advancedsciencenews.com

Despite the already established promising characteristics of graphene, the performance regarding the design of amplifiers is intrinsically dependent and limited by the behavior of GFETs. Recently, the microwave performance of these devices has been improved significantly.<sup>[83]</sup> Nonetheless, graphene amplifiers have a quite limited power gain due to the zero bandgap in graphene, which leads to low current saturation. Moreover, parasitic resistances also degrades the maximum frequency of oscillation because of the fabrication contamination and imperfections.

In ref. [84], the first high-frequency GFET amplifier with a common-source configuration was demonstrated. This GFET amplifier employed an embedded metal gate structure to obtain a clear drain current saturation and thus, achieves a voltage gain of  $\approx$ 5 dB and a 3 dB bandwidth greater than 6 GHz. However, a high output impedance was required in this design.

The first GFET amplifier with a 2 dB power gain was shown in ref. [85], and was achieved by optimizing the gate dielectrics and doping in the graphene channel under a 50  $\Omega$  load impedance. In 2011, a GFET amplifier with a power gain of 10 dB at 1 GHz was demonstrated in ref. [86], where an external inductor was used as an input matching network. Furthermore, the noise figure, NF = 6.4 dB, could be measured because the circuit provided sufficient power gain. In ref. [87], also an amplifier with a single-section LC input matching network was reported with a power gain of 1.84 dB at 191 MHz.

In conjunction with the gain, linearity parameters, such as the 1 dB gain compression ( $P_{1dB}$ ) or the third-order intercept point ( $IP_3$ ), are also important factors in amplifier design. The linearity of GFET transistors has been discussed in refs. [84, 88].

In order to enhance the operation bandwidth, a distrusted configuration can be adapted in microwave circuit designs. By means of this topology a significant bandwidth can only be reached, at the expense of large circuit size and high power consumption. Most importantly, the characteristics of each transistor used to form the artificial transmission lines must be as similar as possible, which is still a challenge in less mature technologies. A four-stage distributed GFET amplifier has been designed in ref. [89] based on CVD-graphene devices. Although a power gain of 4 dB over a 3.5 GHz-bandwidth has been simulated, no power gain could be measured in the fabricated design.

In ref. [90], a 3.4 dB GFET-based amplifier at 14.3 GHz was reported, where integrated transmission lines were used as matching networks. An amplifier design with a power gain of 8.34 dB at 5.5 GHz from the same research group has been reported in 2021.<sup>[91]</sup>

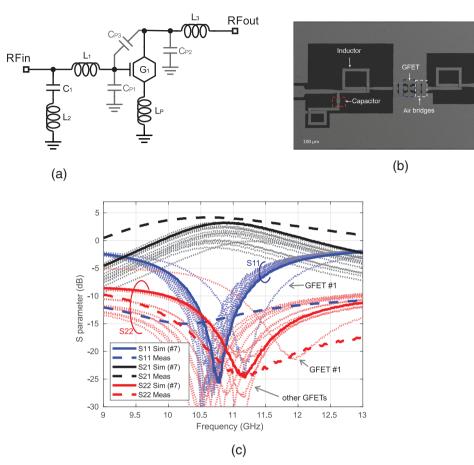

The general challenge of implementing GFET amplifiers is that the graphene process is still immature and has many manufacturing difficulties, which lead to poor yield and large variation in the parameters of the device. The negative-image equivalent circuit technique<sup>[92]</sup> has been applied for a GFET amplifier design in ref. [93] in order to estimate the device parameters without developing a detailed device model and to manage process variations from fabrication run to fabrication run.

Several GFET transistors have been measured and the data analyzed to find a representative performance and estimate the spread in gain and impedance. The results show good prospects for future microwave and millimeter-wave amplifiers based on graphene technology. A fully integrated microwave GFET amplifier, as shown in **Figure 13**a, has been designed, fabricated, and characterized to demonstrate this design procedure. Its microscopy image is shown in Figure 13b. The measured results are plotted in Figure 13c where the transistor variations can be observed. Measured peak power gain of 4.2 dB at 10.6 GHz are achieved. **Table 3** summarizes the performances of recent GFET amplifiers.

#### 4.2. Power Detectors and Rectifiers

Power detectors are one of the direct applications for exploring the high carrier mobility in graphene. They are crucial elements in wireless communication systems, and many applications such as: RFID, automatic gain control, and energy harvesting, require sensitive, low-voltage drop, and low capacitance power detectors.

Employing GFETs in common-source (CS) configuration as linear power detector devices has been reported in refs. [95–97]. The demonstrated GFET power detectors are leveraging the nonlinear channel resistance property above the extrinsic  $f_{\rm T}$  and  $f_{\rm max}$  limitations of the employed device.

The main challenges of employing GFETs in power detectors are:

The 3 dB detection bandwidth of GFET detectors is given by  $1/(2\pi C_t R_t)$  where  $C_t$  is the total gate capacitance which consists of the gate-to-source capacitance,  $C_{gs}$ , and gate-to-drain capacitance,  $C_{gd}$ .  $R_t$  is here the total resistance formed by the gate resistance,  $R_g$ , in series with the source resistance,  $R_s$ . Consequently, one limitation of using GFETs as power detectors comes from the excess capacitance,  $C_{gs}$ , which limits the 3-dB detection bandwidth of the power detector.

Poor tangential signal sensitivity (TSS) and responsivity for frequencies where the transistor acts as a passive element with low current responsivity.

Graphene diodes have been successfully used also as power detectors.<sup>[99–101]</sup> In refs. [98] and [99], linear power detectors have

Figure 13. GFET amplifier. a) Schematic of a GFET amplifier, b) microphotograph of an integrated GFET amplifier circuit, and c) measured and simulated S-parameters of the integrated GFET amplifier. The gray lines are simulations with other GFET transistors. Reproduced under the terms of the CC-BY Creative Commons Attribution 4.0 International license (https://creativecommons.org/licenses/by/4.0/).<sup>[93]</sup> Copyright 2021, The Authors, published by IEEE.

been reported based on a single-graphene diode. Moreover, a linear-in-dB power detector employing three metal–insulator– graphene diodes and designed for the frequency range 40–70 GHz has also been reported. In order to obtain both good input matching over a large bandwidth and high detection sensitivity, a linear distributed detector employing three graphene-diodes in an artificial transmission-line has been reported in ref. [101].

|  | Table 3. | Performance | comparison | of GFET | amplifiers. |

|--|----------|-------------|------------|---------|-------------|

|--|----------|-------------|------------|---------|-------------|

| Ref. | Freq. [GHz] | Power gain [dB] | Noise figure [dB] | Matching<br>(yes/no) |

|------|-------------|-----------------|-------------------|----------------------|

| [84] | 6           | 5 (voltage)     | n.a.              | no                   |

| [85] | n.a.        | 2               | n.a.              | no                   |

| [86] | 1           | 10              | 6.4               | yes                  |

| [87] | 0.191       | 1.84            | n.a.              | yes                  |

| [89] | 2.5         | 4 (sim)         | n.a.              | yes                  |

| [90] | 14.3        | 3.4             | 6.2               | yes                  |

| [94] | 10.2        | 2.6             | 6.1               | yes                  |

| [91] | 5.5         | 8.34            | 5                 | yes                  |

| [93] | 10.6        | 4.2             | n.a.              | yes                  |

The power detector provides state-of-the-art performance from very low frequencies up to 70 GHz.

**Table 4** shows a performance comparison between different reported graphene-based power detectors.

Wireless power transfer (WPT) is highly demanded recently because it is able to provide energy without wired charging of devices. One of the key components in WPT is a rectifier which is used to convert the received alternating current (AC) to direct current (DC). The power conversion efficiency (PCE) of a rectifier, defined as  $\eta = P_{\rm DC}/P_{\rm AC}$ , where  $P_{\rm DC}$  is the output DC power and  $P_{\rm AC}$  is the input AC power, is one of the critical circuit parameters. Besides PCE, input matching, that is, the reflection coefficient, is also important for an RF/microwave rectifier. The difference between a power detector and a rectifier is the capability of providing output power, that is,  $V_{\rm DC}I_{\rm DC}$  instead of only voltage in detectors. Most of graphene rectifiers currently however require a high impedance output load, so that up to now basically only DC output voltage capability has been experimentally demonstrated.

Ballistic- and diode-based graphene rectifiers are two major approaches to realise a nonlinear device. Graphene is a suitable material to obtain ballistic transport which can be used to obtain ballistic-based rectifiers.<sup>[102–106]</sup> For ballistic transport the

## www.advancedsciencenews.com

Table 4. Performance comparison of graphene-based power detectors.

| Ref.  | Technology | Substrate | Dynamic range [dB] | Frequency [GHz] | Responsivity (V/W) |

|-------|------------|-----------|--------------------|-----------------|--------------------|

| [95]  | GFET       | SiC       | 40                 | 8.5             | 33 at 110 GHz      |

| [96]  | GFET       | Glass     | 40                 | 3               | NA                 |

| [97]  | GFET       | SiC       | NA                 | 96              | 1–2 at 96 GHz      |

| [98]  | MIG        | Quartz    | NA                 | 49.4            | 1.1 at 49.4 GHz    |

| [99]  | MIG        | Quartz    | 45                 | 2.1–2.7         | 168 at 2.5 GHz     |

| [100] | MIG        | Quartz    | 50                 | 40-70           | 15 at 60 GHz       |

| [101] | MIG        | Quartz    | 60                 | 70              | 87 at 70 GHz       |

devices must be planar and the active region should be smaller than a carrier mean free path to be in the ballistic operation regime. The operation principle is different than a diode-based rectifier because a ballistic rectifier does not require a doped junction or barrier structure. In  $2015^{[103]}$  has presented a graphene rectifier in a semiballistic regime on a SiO<sub>2</sub> substrate. It showed a mobility of  $1810 \text{ cm}^2 \text{ V}^{-1}\text{s}^{-1}$  which is much lower than the theoretical limit in graphene . The reduction in mobility was explained as the result of the forming of puddles on the SiO<sub>2</sub> substrate.

In ref. [104], graphene was transferred on h-BN as substrate instead of SiO<sub>2</sub> to design a rectifier in full ballistic transport regime. Due to the encapsulation in h-BN a mobility of  $\approx$ 200 000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> at room temperature was achieved. This significant improvement in mobility enabled the use of such devices in applications such as imaging.<sup>[105]</sup>

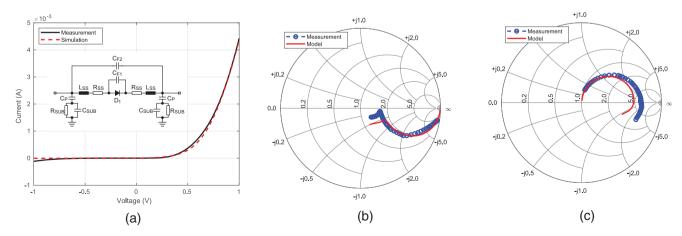

Alternatively, diode-based graphene rectifiers have been reported on either rigid<sup>[107]</sup> or flexible substrates,<sup>[108–110]</sup> which rely on the nonlinear behavior of the device. The highest operation frequency is restricted by the parasitic capacitance and parasitic resistance of the device. By reducing the series resistance of the diode, for example, by employing the 1D MIG diode, terahertz diode-based rectifiers<sup>[107,109]</sup> have been achieved. A SPICE-compatible large-signal graphene-diode model, as illustrated in **Figure 14**, has been proposed in ref. [111] to carry out the circuit design as well as its optimization. With the large-signal model techniques to improve efficiency, for example, through harmonic tuning, become possible. In addition, to improve the

power conversion efficiency, care has to be taken also in the design of the input matching.<sup>[112]</sup>

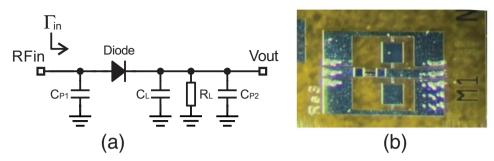

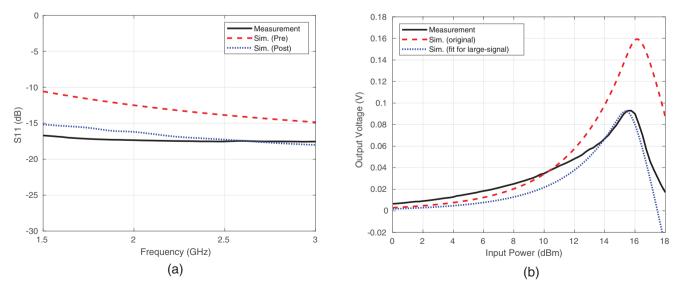

Fan et al.<sup>[110]</sup> demonstrated a fully integrated and well matching CVD graphene rectifier, as shown in Figure 15. A measured reflection coefficient of -17.5 dB and output voltage of 93 mV has been achieved, as plotted in Figure 16. Note that by using a finite output load of 2.8 k $\Omega$  instead of a very high impedance load, DC output power could be obtained.<sup>[110]</sup> Nevertheless, all reported graphene rectifiers up to date hardly provide sufficient  $P_{DC}$  which restricts their application in WPT. However, as suggested in ref. [110], with good reproducibility of CVD-graphene MMIC process, a rectifier array could become feasible to harvest sufficient energy at least for low-energy applications such as medical implants. Besides these two major rectifications, an alternative approach is to employ geometric asymmetry, that is, from a layout perspective, to obtain a significant nonlinearity as presented in ref. [113] where the device has a trapezoidal layout.

#### 4.3. Frequency Multipliers

In the pursuit of achieving higher working frequencies, frequency multipliers are gaining an ever-increasing relevance in all technologies. They relax the requirements for the implementation of oscillators that can then be designed at lower frequencies, ultimately reducing the complexity of the circuit. Frequency multipliers can be implemented either to multiply

**Figure 14.** Measured and modeled results. a) DC current–voltage (*IV*) curve of the MIG diode and its equivalent circuit, and b)  $S_{11}$  and c)  $S_{21}$  from 10 MHz to 20 GHz. a–c) Reproduced with permission.<sup>[110]</sup> Copyright 2021, IEEE.

Figure 15. A fully integrated graphene rectifier. a) Schematic and b) microphotograph. a,b) Reproduced with permission.<sup>[110]</sup> Copyright 2021, IEEE.

the frequency of the local oscillator directly, or to replace a mixer in the upconversion of the already modulated signal.<sup>[114]</sup> As they are usually passive designs, they are typically followed or preceded by an amplifier stage.

The working principle in general is based on the nonlinearity of an active device to generate harmonics at multiples of the input frequency. Then, the harmonic component of interest is filtered out. Traditionally, diodes were used for this purpose, and later on in integrated designs transistors have also been used.<sup>[115]</sup> The nonlinearity of conventional diodes and transistors is reflected in the exponential relation of their I-V characteristics, between the input and output of the diode and between  $I_{ds}$ and  $V_{gs}$  in FETs. Nevertheless, in emerging technologies such as graphene, circuit design needs to be planned hand in hand with the intrinsic characteristics of the material in order to take full advantage of its promising new properties. Graphene alone presents a high nonlinear behavior under the influence of an electromagnetic field. In ref. [116], a linear metallic coplanar waveguide (CPW) is deposited directly on a monolayer graphene flake. The system under test presents the expected linear *I–V* relation, however, when characterized under a signal input up to 10 GHz and a DC bias voltage, the presence of harmonics is verified up to at least 40 GHz. The same structure without

graphene presents no harmonic generation, as expected. The power level of the harmonic components is strongly dependent on the applied DC voltage, which is explained by the authors as coming from the strong nonlinear electromagnetic dependency of the Dirac fermions in the material (**Table 5**).

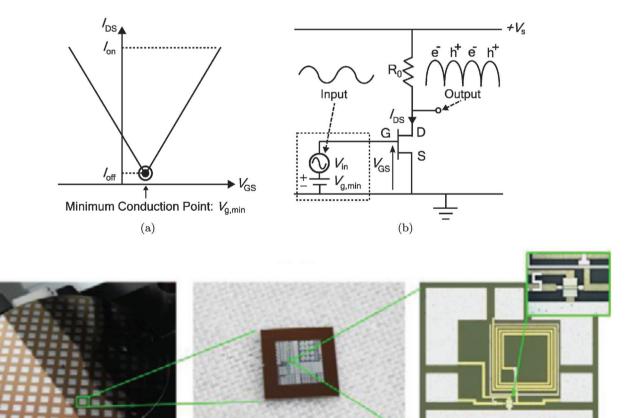

One year prior to this work, in 2009, the first frequency multiplier based on GFETs was reported in ref. [117]. The GFET presented a back gate and employed exfoliated graphene, the rest of the components were externally connected. In this case, the circuit takes advantage of the ambipolar behavior of GFET devices, that is, the conduction of both holes and electrons that entail a symmetrical I-V relation with respect to the Dirac point, as shown in the V-shaped function in **Figure 17**a. As the function is even, the second-order term dominates and most of the power is expected to be transferred to the first harmonic frequency at the output, instead to the fundamental. This effect makes of GFETs excellent candidates for frequency doubling, without requiring complex differential topologies or highly selective filters.

Later on, in 2010 an improvement on the GFET by employing a top gate instead of back gate, led to an increase of the frequency response from 10 kHz to 200 kHz for a frequency doubler.<sup>[119]</sup> That same year, a top-gate GFET grown by

Figure 16. a,b) Simulated and measured input reflection coefficient (a) and output DC voltage versus input power (b). a,b) Reproduced with permission.<sup>[110]</sup> Copyright 2021, IEEE.

www.advancedsciencenews.com

Table 5. Summary of graphene rectifiers.

| Ref.  | Туре           | Bias requ. (y/n) | Matching (y/n) | Flexible (y/n) |

|-------|----------------|------------------|----------------|----------------|

| [103] | Ballistic      | n                | n              | n              |

| [104] | Ballistic      | n                | n              | n              |

| [107] | Diode          | у                | n              | n              |

| [108] | Diode          | у                | n              | У              |

| [109] | Diode          | у                | у              | У              |

| [110] | Diode          | n                | у              | У              |

| [113] | Geo. asymmetry | n                | n              | n              |

CVD is used in a hybrid circuit and achieves frequency doubling in the gigahertz range.<sup>[120]</sup> In 2012, the first work that reports a frequency doubler beyond the transit frequency of the GFET was published.<sup>[121]</sup> This is possible since the nonlinearity comes from the variable channel resistance caused by the graphene. Thus, since no transconductance is required, these designs can work beyond the  $f_T$  of the used device. That same year, the first frequency doubler based on a GFET on flexible substrate was reported in ref. [122]. Again, in 2012, a direct application of the nonlinearities of graphene was approached in ref. [123]. A gap is created in a microstrip line

and covered by a few-layer graphene film in order to design a frequency tripler. This same year, the first frequency tripler based on GFETs was demonstrated in ref. [124]. Whereas a single FET biased at the minimum conducting point results advantageous in doubler designs, in order to favor a tripling behavior this work presents a design built from two GFETs connected in series. The superposition of the two V-shaped transfer characteristics of graphene changes the I-V relation of the system to a W-shaped one. The new characteristics enable a modulation with higher power delivered to the third harmonic. A similar working principle is achieved in the design based on a double-gate GFET, as reported in ref. [125]. This work presents a frequency quadrupler that benefits from the symmetry of the transfer function of the transistor in order to achieve up to 50% of the output power transferred to the harmonic of interest. Further study regarding the purity of the harmonic of interest was carried out in ref. [126]. This work studied in simulation a frequency doubler based on three ambipolar GFETs, where the transistors are connected in series and their gates are shorted. Research in this regard is also continued in ref. [127], where an *M*-shape  $R-V_g$  relation employing a single GFET is achieved. Here, the transistor is used to implement a frequency tripler for the first time with only one device and a spectral purity of 80%.

**Figure 17.** Ambipolar-GFET frequency multiplier. a) Transfer characteristics of ambipolar GFETs. b) GFET-based circuit for frequency multiplication. a,b) Reproduced with permission.<sup>[117]</sup> Copyright 2009, IEEE. c) Photograph of the first integrated GFET-based frequency doubler. Reproduced with permission.<sup>[118]</sup> Copyright 2014, IEEE.

All GFET-based works mentioned so far are hybrid circuits, that is, only the active device is on-wafer and further components are connected externally or the circuit fully relies on the intrinsic behavior of the active device. The first and so far only fully monolithic integrated frequency doubler based on GFETs was reported in ref. [118] in 2014, as besides the GFET it also includes an on-chip spiral inductor used to apply the drain DC bias voltage, as shown in Figure 17c. Hence, this circuit does without additional components.

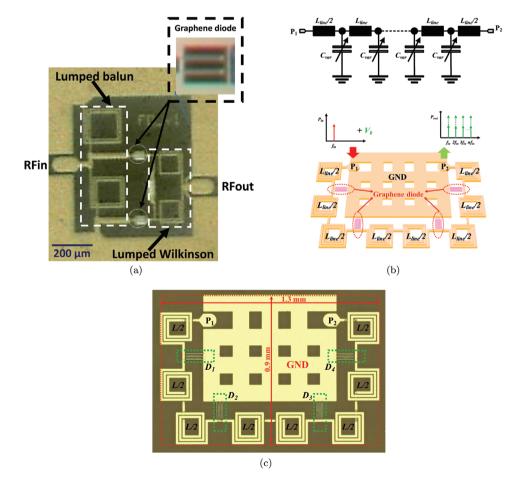

Two additional fully integrated designs based on MIG diodes have been presented so far. The first one, in ref. [128], is a single-balanced design implemented on quartz. It consists of two graphene diodes with an integrated BALUN and power combiner, as shown in **Figure 18**a. The second design, in ref. [72], uses a nonlinear transmission-line (NLTL) always on quartz to provide frequency multiplication. The concept of the NLTL relies on implementing an artificial transmission line with a characteristic impedance of 50  $\Omega$  as in Figure 18b. The variable capacitances to ground in the artificial line lowpass topology are provided by the MIG diode. The circuit contains a total of four diodes, as shown in Figure 18c, and performs either as doubler or tripler. The harmonic behavior of a different graphene-based diode has been reported in

ref. [108]. Without additional matching, the spectral characteristics of a reduced graphene oxide diode (r-GO) are demonstrated for the third harmonic.

The performance comparison of the different cited designs is summarized in **Table 6**. As it has been shown, frequency multipliers in graphene are and have been intensively studied. This is due to the beneficial properties of graphene in order to intrinsically suppress spurious harmonic frequency components with reduced circuit complexity. Nevertheless, all this systems require an external signal generator, which leads to the next section, the need of frequency sources.

#### 4.4. Oscillators

Oscillators are fundamental blocks of electronic systems. Their range of application encompasses from clock generation in microprocessors to carrier synthesis in communication transceivers, each requiring different topologies and performance. In general terms, an oscillator consists of a self-sustaining mechanism that is capable to grow its own noise until eventually a periodic output is generated. There are two ways of interpreting this working principle, either as a negative-feedback

**Figure 18.** MIG-diode-based integrated frequency multiplier designs. a) Photograph of the MIG-diode-based balanced frequency doubler. Reproduced with permission.<sup>[128]</sup> Copyright 2019, IEEE. b) NLTL circuit diagram based on diodes. c) Photograph of the NLTL frequency multiplier based on a total of four MIG diodes. b,c) Reproduced with permission.<sup>[72]</sup> Copyright 2021, IEEE.

www.advancedsciencenews.com

| Table 6. | Performance | comparison | of graphene-based | frequency multipliers. |

|----------|-------------|------------|-------------------|------------------------|

|----------|-------------|------------|-------------------|------------------------|

| Work  | Device               | Graphene   | Substrate            | Tech.      | $f_{in}$ | P <sub>in</sub> | DC $V_{\text{tuning}}$ | CG            | Ν |

|-------|----------------------|------------|----------------------|------------|----------|-----------------|------------------------|---------------|---|

| [116] | CPW                  | NA         | SiO <sub>2</sub> /Si | Integrated | 10 GHz   | 0 dBm           | 0.4 V                  | -42 dB        | 3 |

| [117] | Back-gated GFET      | Exfoliated | SiO <sub>2</sub> /Si | Hybrid     | 10 kHz   | 30 dBm          | 22.7 V                 | -46 dB        | 2 |

| [119] | Top-gated GFET       | Exfoliated | SiO <sub>2</sub> /Si | Hybrid     | 200 kHz  | 2.5 dBm         | 40 V                   | -37 dB        | 2 |

| [120] | Top-gated GFET       | CVD        | SiO <sub>2</sub> /Si | Hybrid     | 0.7 GHz  | 8 dBm           | 3.61 V                 | -30 dB        | 2 |

| [121] | Top-gate GFET        | CVD        | Quartz               | Hybrid     | 3 GHz    | 10 dBm          | 1.4 V                  | -25 dB        | 2 |

| [122] | GFET                 | CVD        | PEN                  | Hybrid     | 8 GHz    | NA              | NA                     | NA            | 2 |

| [123] | Microstrip           | Exfoliated | Arlon 25N            | PCB        | 3 Ghz    | 16 dBm          | NA                     | -27 dB        | 3 |

| [124] | 2 top-gated<br>GFETs | Exfoliated | NA                   | Hybrid     | 200 Hz   | 25 dBm          | 2.2                    | -40 dB        | 3 |

| [125] | Dual-gated GFET      | CVD        | SiO <sub>2</sub> /Si | Hybrid     | 200 kHz  | 2.3 dBm         | -22 to -2 V            | -28 dB        | 4 |

| [127] | Back-gated GFET      | CVD        | SiO <sub>2</sub> /Si | Hybrid     | 1.5 kHz  | 33 dBm          | 16.8 V                 | -33 dB        | 3 |

| [118] | GFET                 | CVD        | SiO <sub>2</sub> /Si | Integrated | 3 GHz    | 0 dBm           | 0.5 V                  | -26 dB        | 2 |

| [128] | MIG diode            | CVD        | Quartz               | Integrated | 5 GHz    | 10 dBm          | 0 V                    | -25 dB        | 2 |

| [72]  | MIG diode            | CVD        | Quartz               | Integrated | 1.7 GHz  | 5 dBm           | 1 V                    | -21 dB        | 2 |

|       |                      |            |                      |            | 1.05 GHz | 5 dBm           | 1 V                    | —31 dB        | 3 |

| [108] | r-GO diode           | DEP        | PEEK                 | NA         | 2–6 GHz  | -3 dBm          | 0 V                    | –47 to –62 dB | 3 |

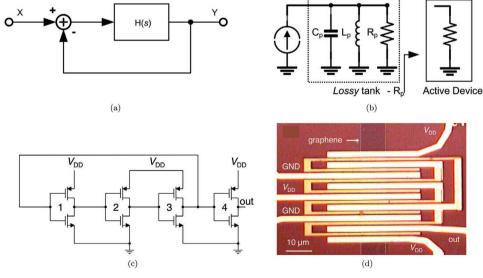

amplifier or as a one-port negative-resistance system.<sup>[129]</sup> Deepening in the extensive oscillator theory is beyond the scope of this work, nevertheless, an overview of the foundations is covered and shown in **Figure 19**. In Figure 19a, a linear unity-gain negative-feedback system where

$$\frac{Y(s)}{X(s)} = \frac{H(s)}{1+H(s)} \tag{1}$$

is considered. When  $H(s = jw_0)$  becomes equal to -1 the gain goes to infinity, and allows the circuit to sustain an output at  $w_0$ . This is known as the "Barkhausen criteria" for oscillation, so that

$$\angle H(jw_0) = 180^{\circ} \tag{3}$$

The second interpretation is presented in Figure 19b. A resonant tank is stimulated by a current impulse and the circuit is lossy due to the resistance,  $R_p$ , that forces a decay in the oscillation. However, if this is compensated by an equivalent negative resistance,  $R_p$ , in parallel, so that  $R_p ||(R_p) = \infty$ , the oscillation would be sustained indefinitely over time. This negative resistance behavior has to be provided by an active circuit. Therefore,

**Figure 19.** a,b) Working principle of the oscillator as a unity-gain negative-feedback system (a) and a negative-resistance oscillator (b), together with the first integrated RO based on GFETs, with a total of three inverter stages and eight transistors. c) Three-stage GFET-based RO diagram. d) Optical microscopy image of the integrated RO. a–d) Reproduced with permission.<sup>[130]</sup> Copyright 2013, American Chemical Society.

ADVANCED SCIENCE NEWS \_\_\_\_\_

Table 7. Performance comparison of graphene-based ROs.

| Ref.  | Frequency   | Substrate            | Inverter N | L      | $ A_v $ |

|-------|-------------|----------------------|------------|--------|---------|

| [130] | 1.22 GHz    | SiO <sub>2</sub> /Si | 4          | lμm    | 4       |

| [131] | 17–39.5 MHz | SiO <sub>2</sub> /Si | 6          | 1.8 µm | 5–14    |

| [132] | 4.3 GHz     | SiO <sub>2</sub> /Si | 4          | 0.9 μm | 5       |

the theory establishes that an oscillator system requires an active device or a combination of devices capable of providing positive gain,  $|A_v|$ , that is, present a negative resistance over a particular frequency range.

Two main categories of oscillator circuits can be distinguished, ring oscillators (ROs) and LC-oscillators. Whereas ring oscillators are easier to integrate, LC oscillators require that the technology allows the implementation of resonant structures, that is, planar spiral inductors, plate or finger capacitors, and other complex high-Q components. Thus far, the only integrated reported designs for oscillators in graphene are ROs based on GFETs. Their best reported performance is compared in **Table 7**.

These three designs present a similar architecture that consists of an odd number of inverters, each with two GFETs, cascaded in a loop that provides the needed feedback. In addition, another inverter serves as buffer to isolate the oscillator from the loading by the measurement equipment, as shown in Figure 19c. The challenge of this topology when implemented with GFETs is to obtain transistors with sufficient positive voltage gain, and with repeatable performance over multiple devices. Ultimately, ROs represent the limit in performance for an IC technology, as the total inverter gate delay in ROs,  $\tau$ , is used as the main speed metric of such technology. The sum of all single-stage delays,  $\tau_i$ , is the total delay,  $\tau$ , and its inverse equals the maximum oscillation frequency,  $f_{\rm o}$ . In contrast to  $f_{\rm T}$  and  $f_{\rm max}$ ,  $\tau$ , which is mainly dependent on the on-state resistance, is valid in the large-signal regime and contemplates nonidealized and multiple-transistor conditions. Since the channel resistance and the gate capacitance scale with L, a theoretical  $f_0 \propto L^{-2}$  relation is expected. Nevertheless, due to parasitic resistances and capacitances that do not follow the idealized dependency, both refs. [130] and [132] prove a  $f_0 \propto L^{-1}$  dependency. However, ROs based on GFETs with lengths under 0.8  $\mu$ m<sup>[133]</sup> have yet not been reported, as the achievable gain of those devices is not sufficient for sustaining an oscillation.<sup>[132]</sup>

The only reported LC oscillator in graphene is an hybrid design working at 72 MHz.<sup>[122]</sup> The GFET is on-wafer, while the feedback is provided by external components and the circuit is tuned by a mechanical tuner. Interestingly, negative differential resistance (NDR) architectures based on a single and multiple GFETs have been reported.<sup>[134,135]</sup> Nevertheless, although they are promising for oscillators, among other circuits, these topologies have been only demonstrated as stand alone systems. Other graphene-based devices analogue to Gunn devices or tunnel diodes, which present negative resistance characteristics, are still lacking the literature. Therefore, progress in the development of oscillators is conditioned by intrinsic constraints of the GFET devices itself.

#### 4.5. Mixers

The currently reported GFET mixers are realized as FET-resistive mixers which exploited the GFET nonlinear resistance rather than its transconductance. Additionally, the lack of current saturation in GFETs result in a high linearity of GFETbased resistive mixers. The passive nature of this approach enables the demonstration of mixers operating at frequencies above  $f_{\rm T}$  and  $f_{\rm max}$  of the used GFETs. However, the reported conversion loss (CL) of GFET-based mixers is relatively high compared to other technologies. This is caused by the dependence of the conversion efficiency of the FET-resistive mixers on the drain-to-source resistance,  $R_{ds}$  which ideally changes from zero in the on-state to infinite in the off-state. In case of the GFET and because of its ambipolar behavior the on-off resistance-ratio is always low with high on-resistance and low offresistance. As a consequence, the reported CL values vary from 45 dB<sup>[136]</sup> to 18 dB<sup>[137]</sup> for a local oscillator power (LO) power  $(P_{10})$  of 8 dB m. This is the minimum reported CL so far for integrated GFET-based mixers. GFET-resistive mixers are implemented as either fundamental or subharmonic mixers employing mostly, a single-transistor due to yield and repeatability issues of the fabrication process. The used GFET is either connected to high-Q external passive components<sup>[136,138-141]</sup> or integrated with passive lumped components or microwave filters.<sup>[137,142-144]</sup> Graphene-diode-based mixers were reported in refs. [128,145]. In ref. [145], a single-diode-based downconversion mixer has been reported. The RF frequency range for this mixer is 1.7–4 GHz and the reported CL is 15 dB. In ref. [128], a double-balanced upconversion mixer was reported. The operation frequency is 6–12 GHz and the reported CL is 10 dB. The employment of graphene-diodes in mixer circuits resulted in lower conversion loss compared to GFET-based mixers due to the more favorable on-off resistance ratio of state-of-the-art graphene diodes.

www.advmat.de

Table 8 summarizes the performance of the reported graphene-based mixer circuits.

Table 8. Performance comparison of graphene-based mixer circuits.

| Ref.  | Technology          | Scheme      | $f_{	extsf{rf}}$ | $P_{\rm LO}$ | Conversion<br>loss (CL) |