| 1<br>2   | Article                                                                                         |

|----------|-------------------------------------------------------------------------------------------------|

| 3<br>4   | Single-bit full adder and logic gate based on synthetic                                         |

| 5        | antiferromagnetic bilayer skyrmions                                                             |

| 6<br>7   | Kai Yu Mak, Jing Xia, Xichao Zhang, Li Li, Mouad Fattouhi, Motohiko Ezawa <sup>*</sup> , Xiaoxi |

| 8        | Liu, and Yan Zhou <sup>*</sup>                                                                  |

| 9        | K.Y. Mak, L. Li, Y. Zhou*                                                                       |

| 10       | School of Science and Engineering, The Chinese University of Hong Kong, Shenzhen,               |

| 11       | Guangdong 518172, China                                                                         |

| 12       | email: zhouyan@cuhk.edu.cn                                                                      |

| 13<br>14 | J. Xia                                                                                          |

| 15       | College of Physics and Electronic Engineering, Sichuan Normal University, Chengdu 610068,       |

| 16       | China                                                                                           |

| 17       |                                                                                                 |

| 18       | X. Zhang, X. Liu                                                                                |

| 19       | Department of Electrical and Computer Engineering, Shinshu University, 4-17-1 Wakasato,         |

| 20       | Nagano 380-8553, Japan                                                                          |

| 21       |                                                                                                 |

| 22       | M. Fattouhi                                                                                     |

| 23       | Department of Applied Physics, University of Salamanca, 37008 Salamanca, Spain                  |

| 24       |                                                                                                 |

| 25       | M. Ezawa*                                                                                       |

| 26       | Department of Applied Physics, University of Tokyo, Hongo 7-3-1, Tokyo 113-8656, Japan          |

| 27       | email: ezawa@ap.t.u-tokyo.ac.jp                                                                 |

### 29 Abstract

30 Skyrmion-based devices are promising candidates for non-volatile memory and low-delay time 31 computation. Many skyrmion-based devices execute operation by controlling skyrmion 32 trajectory, which can be impeded by the skyrmion Hall effect. Here, the design of skyrmion-33 based arithmetic device built on synthetic antiferromagnetic (SyAF) structures are presented, 34 where the structure can greatly suppress skyrmion Hall effect. In this study, the operations of 35 skyrmion-based half adder, full adder and XOR logic gate are executed by introducing 36 geometric notches and tilted edges, which can annihilate or diverge skyrmion. Performance of 37 these skyrmion-based devices are evaluated, where the delay time and energy-delay product of the single-bit full adder are 1.95 ns and  $2.50 \times 10^{-22}$  Js, which are only 12% and 79% of the 38 39 previously proposed skyrmion-based adder. This improvement is significant in the construction 40 of ripple-carry adder and ripple-carry adder-subtracter. Therefore, our skyrmion-based SyAF 41 arithmetic device are promising candidate to develop high-speed spintronic devices.

42 Keywords skyrmion; full adder; synthetic antiferromagnet; low delay time electronics;

43 micromagnets

44

## 45 **1 Introduction**

46 A magnetic skyrmion is a stable topologically non-trivial configuration that possess particle-47 like properties [1-3]. There are many advantages that make skyrmion a promising technology 48 for beyond-CMOS computing device and future data storage devices, including its small size, stable properties and easy current driveability [4-6]. In 2009, the existence of magnetic 49 50 skyrmion has been demonstrated experimentally in bulk MnSi exhibiting the Dzyaloshinskii-51 Moriya interaction (DMI) [7-9]. Inspired by the experimental realizations of skyrmion, many 52 skyrmion-based logic gates and computational devices have been proposed [10-21]. However, 53 skyrmion-based arithmetic devices are relatively less discussed.

54 Conventional arithmetic devices are usually constructed using single-bit full adder [22, 55 23]. With appropriate matching of single-bit full adders and logic gates, basic arithmetic 56 operations such as addition, subtraction and multiplication can be realized in electronic circuit. 57 Therefore, the speed and energy consumption of arithmetic devices strongly depend on the 58 efficiency of the single-bit full adder [22-23]. In CMOS circuit, the single-bit adder is usually 59 constructed by the matching of multiple logic gates. With similar approach, Chauwin et. al. 60 group proposes the design of an efficient single-bit full adder by matching skyrmion-based logic 61 gates [10]. Alternatively, Song et. al. group demonstrates that the performance of single-bit full 62 adder can be further improved by performing logical operations concurrently by taking 63 advantages of the skyrmion annihilation properties [13]. However, both designs of single-bit 64 full adder rely heavily on precise control of skyrmion Hall effect, which can be challenging in 65 operation. As demonstrated in recent studies, the skyrmion Hall angle is sensitive to the 66 fluctuation of applied current density [24-26] and temperature [27, 28], causing changes in the 67 skyrmion trajectory and unintentionally annihilation. On the other hand, studies also describe 68 the issues of stabilizing skyrmions below 10 nm in ferromagnetic multilayers and ferromagnetic 69 thin films [29, 30].

70 To resolve these problems, synthetic antiferromagnets (SyAF) have been introduced. The 71 SyAF bilayer system is a ferromagnet / heavy-metal spacer / ferromagnet trilayer structures, 72 where the two ferromagnetic (FM) layers are strictly exchange-coupled in an antiferromagnetic 73 (AFM) configuration [31]. By using the SyAF structure, the skyrmion Hall effect is greatly 74 suppressed [32], and skyrmions with the size below 10 nm are stabilized without applying 75 magnetic field [33-34]. These properties are important to stabilize skyrmion in high speed 76 skyrmion-based devices, avoiding accidental skyrmion annihilation and allowing more 77 compact devices to be fabricated. Therefore, it is important to perform study on designing a 78 single-bit full adder based on the SyAF structure. Indeed, other racetrack fabrication methods based on local modification of magnetic properties [35-36] are also important for buildingskyrmion-based devices.

81 In this paper, we propose designs of skyrmion-based single-bit half adder, single-bit full 82 adder and XOR logic gate on SyAF bilayer structure. These designs execute computation by 83 controlling skyrmion trajectory and annihilation with simple geometry. Since the skyrmion Hall 84 effect is greatly suppressed on SyAF, our proposed devices are less sensitive to electric current 85 and thermal fluctuation. We also demonstrate that the delay time and energy-delay product (EDP) of the single-bit full adder can be reduce to 1.95 ns and  $2.50 \times 10^{-22}$  Js per each 86 87 operation, which is only 12% and 79% of the previously proposed skyrmion adder. Our results 88 provide guidelines for the design of quick response skyrmion-based logic gate and single-bit 89 full adder device.

## 90 2 Model and methods

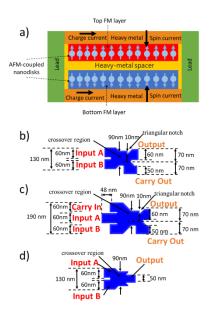

91 Fig. 1a shows the schematic diagram of the proposed device. Two heavy metal layers (HM) 92 sandwiches the patterned trilayer SyAF structure. The patterned trilayer SyAF are shown in Fig. 93 1b-d and are used as the skyrmion conduit. Magnetic tunnel junctions (MTJ) are installed on 94 top of the SyAF/HM layer for skyrmion nucleation and detection. This MTJ-based skyrmion 95 nucleation and detection circuit are adopted from previous skyrmion devices and are spice-96 compatible [17, 37]. The skyrmion in the patterned SyAF layers is driven by spin-orbit torque 97 (SOT), which is induced by applying electric current to the HM layers to produce vertical spin 98 currents to the SyAF structure. [38]. Thus, skyrmion moves in the electric current direction.

99 The operation of the proposed devices is designed based on the analysis of SOT driven

100 skyrmion motion properties described by Thiele equation [13, 32]:

101

$$\mathbf{G} \times \mathbf{v} - D\alpha \mathbf{v} + \mathbf{F}_{st} + \mathbf{F}_{ext} = \mathbf{0}$$

(1)

102 with the gyromagnetic vector  $\mathbf{G} = \hat{z}G = \hat{z}(4\pi Q)M_s d/\gamma$ , the topological charge Q, the 103 gyromagnetic ratio  $\gamma$  and dissipation constant  $D = -(\frac{16}{3})\pi M_s d/\gamma$ . The first term is the 104 gyroscopic force related to the skyrmion Hall effect and the second term is the dissipative forces 105 that oppose the skyrmion movement in the direction of the velocity  $\boldsymbol{v}$ . The third term  $\boldsymbol{F}_{st} =$ 106  $\sigma \kappa j \hat{z} \times \hat{p}$  is spin torque force, with spin Hall angle dependent constant  $\sigma = -\pi \hbar \theta_{SH}/2e$ , 107 characteristic length of skyrmion  $\kappa$  and  $\hat{p} = -\hat{y}$  in our simulation. The fourth term  $\boldsymbol{F}_{ext}$  is an 108 external force; including forces induce by the conduit's boundary, notches or tilted edge.

109 Skyrmions movement on the FM layer are determined by the balances of these four 110 forces. Considering the skyrmion in the free space moving along the x-axis, i.e.  $\mathbf{F}_{\text{ext}} = 0$ :

111

$$\mathbf{v}_{x} = \frac{\alpha D}{G^{2} + \alpha^{2} D^{2}} \mathbf{F}_{st} \qquad \mathbf{v}_{y} = \frac{\mathbf{G}}{G^{2} + \alpha^{2} D^{2}} \mathbf{F}_{st}$$

(2)

112 Thus, the skyrmion transverse movement  $\mathbf{v}_y$  is related to G and its direction depends on the 113 topological charge of the skyrmion Q. In SyAF, the skyrmions on top FM layer and bottom FM 114 layer are strictly exchange-coupled in an antiferromagnetic (AFM) configuration. Hence, the 115 skyrmions have opposite sign of Q and the transverse movement will cancel out each other. As 116 a result, with balance of the three forces: gyroscopic force ( $\mathbf{G} \times \mathbf{v}$ ), dissipative force ( $D\alpha\mathbf{v}$ ), 117 and spin torque force ( $\mathbf{F}_{st}$ ), skyrmion moves in a straight line in free space.

118 When the skyrmion is close to the boundary of the conduits, changes of magnetization at 119 the boundary induced repulsive force ( $\mathbf{F}_{ext} = \mathbf{F}_{b}$ ) to the skyrmion. For titled edge, transverse 120 force ( $\mathbf{F}_{b} = \mathbf{F}_{b}\hat{y}$ ) is extracted from the boundary, causing the skyrmions to move along the 121 boundary. When the forces exceeds the threshold value, a skyrmion annihilates at the boundary 122 [39, 40].

The adders and logic gate operation are demonstrated using micromagnetic simulations performed on the GPU-accelerated open-source micromagnetic simulator software package MuMax3 [41], which have been used in simulating SyAF system as reported in Ref. [42-45]. In real experimental samples, a spacer layer is added to adjust the interlayer exchanges coupling between two ferromagnetic layers. In the simulation, we focus on the magnetic layers and ignore the physical thickness of the nonmagnetic spacer layer, as the spacer is nonmagnetic and is usually much smaller than 1 nm in experiments [46]. However, we do consider the interlayer

exchange coupling based on the RKKY-type exchange interaction. Therefore, in the simulation,

we applied interlayer exchange coupling between two Ferromagnetic layer and and ignore the

thickness of nonmagnetic spacer layer. The software simulates the magnetization dynamics by

solving the Landau–Lifshitz–Gilbert (LLG) equation augmented with SOT [47-48].

134

$$\frac{d\boldsymbol{m}}{dt} = -\gamma_0 \boldsymbol{m} \times \boldsymbol{H}_{\text{eff}} + \alpha \left( \boldsymbol{m} \times \frac{d\boldsymbol{m}}{dt} \right) - \frac{\hbar\theta_{\text{SH}J}}{2meM_s t_{\text{FM}}} \boldsymbol{m} \times \left( \boldsymbol{m} \times \boldsymbol{\sigma} \right)$$

(3)

with normalized magnetization  $\boldsymbol{m}$ , the gyromagnetic ratio  $\gamma_0$ , effective field vector  $\boldsymbol{H}_{eff}$ , 135 136 damping constant  $\alpha$ , spin Hall angle  $\theta_{SH}$ , current density J, saturation magnetization  $M_s$ , thickness of the FM layer  $t_{\rm FM}$ , and  $\sigma = -\vec{u_y}$  in our model. The intrinsic magnetic material 137 138 parameters used in our simulation are adopted from experimental data of Co/Pt materials 139 reported in Ref. [48] and are used in simulations reports [49-53]: Exchange stiffness  $A_{intra}$  = 15 pJ m<sup>-1</sup>, Gilbert damping coefficient  $\alpha = 0.3$ , saturation magnetization  $M_s = 580$  kA m<sup>-1</sup>, 140 perpendicular magnetic anisotropy (PMA) constant  $K = 0.8 \text{ MJ m}^{-3}$ , DMI strength D = 3.5 MJ141 142 m<sup>-2</sup> and spin Hall angle  $\theta_{SH} = 0.2$ . To balance the accuracy and efficiency, all models are 143 discretized into tetragonal elements with the size of  $2 \text{ nm} \times 2 \text{ nm} \times 2 \text{ nm}$ .

146 Fig. 1 Schematics diagram of the proposed SyAF bilayer single-bit half adder, single-bit full 147 adder and logical XOR gate. (a) The XZ cut of the SyAF bilayer used. The thickness of each 148 Ferromagnetic layer (FM) is 2 nm and two layers are separated by an Ru layer. The skyrmion 149 motion is driven by the current perpendicular to the plane (CPP) approach. Charge current flows 150 through heavy-metal layers along the x-direction, which gives rise to a spin current (P = +z) 151 perpendicularly injected to the bottom and top FM layer because of spin Hall effect. These 152 Heavy metal layer's geometry is tetragonal in shape and are different from the FM layer. Hence, 153 the skyrmion in the FM layers are driven by the spin current and move in the x direction. (b) 154 The FM layer design of the single-bit half adder, the Input A and Input B are on the left. The 155 Output is located on the top right of the channel and the Carry is located on the bottom right of 156 the channel. Two 45° tilted edges are located beneath the center line of the channel to deflect 157 skyrmions. (c) The FM layer design of the single-bit full adder, the Input A, Input B and Carry 158 In are located on the left. The Output and Carry Out are located on the right. Two 45° tilted 159 edges are located beneath the center line of the channel to deflect skyrmions. An edge is located 160 on the top of the channel to annihilate unwanted skyrmions. (d)The FM layer design of the 161 XOR logic gate. For the XOR logic gate, the Input A, Input B are located on the left. The 162 Output is located on the centre right end of the channel.

### 163 **3 Results and discussion**

### 164 **3.1 Skyrmion-based single-bit half adder device**

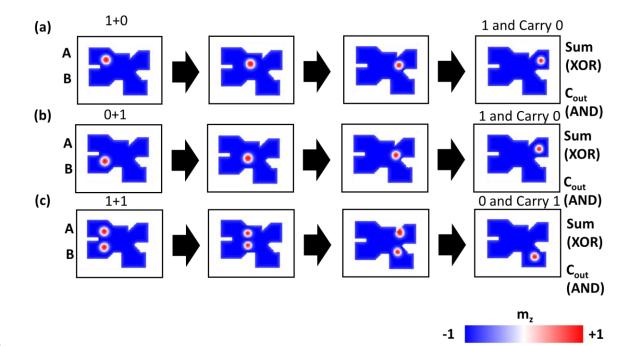

165 A half adder is operated by compiling XOR and AND logical operation simultaneously 166 to generate SUM and CARRY outputs, respectively. Realization of half adder in conventional 167 CMOS circuit require 18 transistors with complex circuit connections [13]. Here, we propose 168 a different approach to realize single-bit half adder device using simple geometry and magnetic 169 skyrmions. The design of the half adder device includes two inputs and outputs with a crossover 170 region (Fig. 1b). Fig. 2 shows the operation of the proposed single-bit half adder. Skyrmions 171 present at the left input terminals travels to the right terminals for detection. For input (1, 0)172 (Fig. 2a and supplementary video S1), the skyrmion nucleated at the upper input terminal is 173 diverged to the crossover region by a 45° tilted edge. Due to the skyrmion-edge repulsion, the 174 skyrmion moves in the centre of the crossover region and passes the triangular notch. Then, the 175 skyrmion is diverged by the second 45° tilted edge and is detected at the output terminals, 176 resulting in an output (1, 0). Similarly, for input (0, 1) (Fig. 2b and supplementary video S2), 177 the skyrmion nucleated at the lower input terminal is diverged to the crossover region by a 45° 178 tilted edge. Due to the skyrmion-edge repulsion, the skyrmion moves in the centre of the 179 crossover regions and passes the triangular notch. Then, the skyrmion is diverged by the second 180  $45^{\circ}$  tilted edge and is detected at the output terminals, resulting in an output (1, 0). Finally, for 181 input (1, 1) (Fig. 2c and supplementary video S3), two skyrmions encounter at the crossover 182 region and repel each other, due to skyrmion-skyrmion repulsion. Subsequently, the upper 183 skyrmion is annihilated at the triangular notch, and the lower skyrmion is diverged to the lower 184 output terminal by the second  $45^{\circ}$  tilted edge. Therefore, the input (1, 1) results in an output (0, 185 1). Input (0, 0) obviously generates an output (0, 0). The upper and lower output terminals are 186 corresponded to SUM and CARRY, respectively. As a result, the simple geometry shown in 187 Fig. 1b can perform the XOR and AND operation concurrently and can operate as a single-bit 188 half adder with delay time 1.1 ns.

Fig 2. Skyrmion-based single-bit full adder device operation for each input case. The device size is 150 nm  $\times$  300 nm, and the applied current density j = 140 MA cm<sup>-2</sup>. The operation time of the half adder is 1.1 ns.

## 195 **3.2 Skyrmion-based single-bit full adder device**

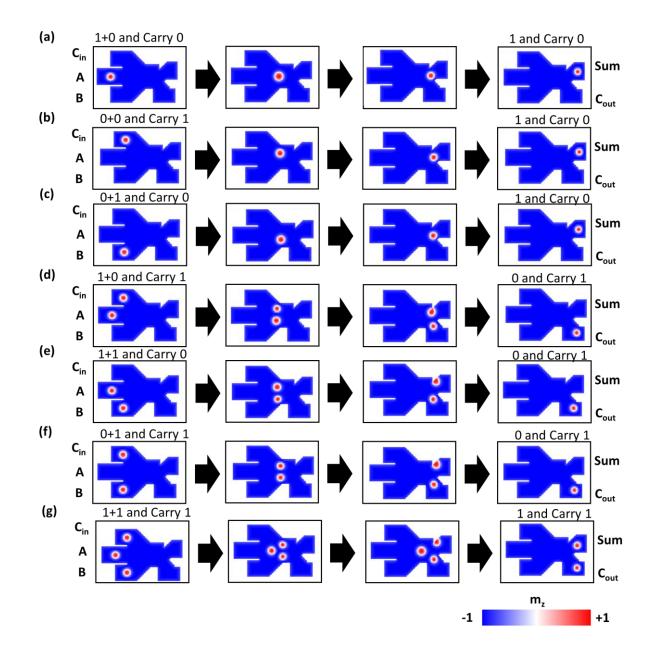

196 A single-bit full adder is operated by compiling two binary inputs and a carry-in digit to 197 generate SUM and CARRY-OUT outputs. Hence, it comprises three inputs and two outputs. 198 The previous skyrmion-based full adders are constructed by connecting two half adders and 199 one OR gate properly [10, 13]. Here, we implement single-bit half adder device using simple 200 geometry with design similar to the half adder, as shown in Fig. 1c. Fig. 3 and Supplementary 201 Movies S4-S10 shows the operating process of the full adder. The skyrmions presented at the 202 left input terminals travel to the right for detection at the output terminals. The final outputs 203 represent SUM (upper branch) and CARRY-OUT (lower branch).

204 We first demonstrate the operation of full adder with input (0,1,0), (1,0,0) and (0,0,1). For 205 input (0, 1, 0), the skyrmion nucleates on the left terminal will pass through the triangular notch 206 and is diverged to the SUM region by the second 45° tilted edge, as show in Fig. 3a (see 207 Supplementary Movies S4). For Input (1, 0, 0) and (0, 0, 1), the skyrmion nucleates on the left terminal will be diverged to the crossover region by the 45° tilted edge. Due to the skyrmion-208 209 edge repulsion, the skyrmions will align to the centre of the crossover region and pass through 210 the triangular notch. The skyrmion will be diverged to the upper output terminal for detection 211 by the second 45° tilted edge, as shown in Fig 3b and Fig. 3c (see Supplementary Movies S5-212 S6). Therefore, the input (0,1,0), (1,0,0) and (0,0,1) results in an output (1,0).

The operation of full adder with input (1,0,1), (0,1,1) and (1,1,0) is demonstrated in Fig. 3d-3f (see Supplementary Movies S7-S9). Similar to the operation with input (0,1,0), (1,0,0)and (0,0,1), skyrmions nucleated in the input terminals enter the crossover region. Within the crossover region, two skyrmions encounter and repel each other, due to skyrmion-skyrmion repulsion. Subsequently, the upper skyrmion is annihilated at the triangular notch. The lower skyrmion is diverged by the 45° tilted edge to the lower output terminal. Therefore, the input (1,1,0), (0,1,1) and (1,1,0) results in an output (0,1).

220 The operation of full adder with input (1,1,1) is demonstrated in Fig. 3g (see 221 Supplementary Movies S10). Similar to the operation with input (1,1,0), (0,1,1) and (1,0,1), 222 skyrmions nucleated in the inputs enters the crossover region. Within the crossover region, three 223 skyrmions encounter and repel each other. Two skyrmions travel simultaneously with one 224 skyrmions is repel backwards. Thus, the upper skyrmion is annihilated at the triangular notch. 225 The lower skyrmion and the skyrmions at the back are diverged by the 45° tilted edge to the 226 lower and upper output terminal, respectively. Therefore, the input (1,1,1) results in an output 227 (1,1). In addition, Input (0,0) obviously generates an output (0,0). We have investigated the 228 reliability of the full adder and found the proper range of the operation current density to be from 120-145 *MA* cm<sup>-2</sup>. 229

230 It is interesting to note that the skyrmion arrive the upper and lower output terminal in 231 1.95 ns and 1.7ns, respectively. Therefore, the CARRY-OUT result can be read and pass to the 232 subsequent adder 0.25 ns before the OUTPUT is computed, which can further reduce the delay 233 time in constructing multi-bits adder. On the other hand, when we compare it with the full 234 adders that are constructed by combination of half adders, our design does not have the 235 synchronizing issue of arrival time between two half adders and one OR gate. Therefore, the 236 full adder is more robust and scalable. Additionally, ref. [13] suggests that cascading single-bit 237 skyrmion adders can realize energy efficient multi-bits adder without wire connection. Similar 238 cascading approach is also feasible to build energy efficient multi-bits adder with our proposed 239 adder, information can be found in supporting information 1.

In addition, we have performed simulations on our design when the notch is displaced by  $\pm 5$  nm in the x direction (Supporting information Figure S2 and S3). The execution of addition operation is not affected by the displace notch, showing there is tolerance for defects to some degree in our design.

Fig 3. Skyrmion-based single-bit full adder device operation for each input case. The device size is 190 nm  $\times$  300 *nm*, and the applied current density j = 140 MA cm<sup>-2</sup>. The operation time of the full adder is 1.95 ns.

# 248 **3.3 Skyrmion-based XOR logic gate**

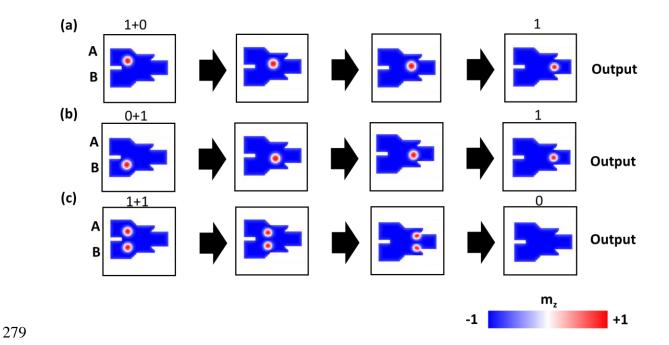

A half adder is a combination of XOR and AND logic gate, as demonstrated in section A. However, for high-speed computation, we designed an alternative version of XOR logic gate that operate faster than the half adder. The proposed Skyrmion-based XOR logic gate is shown in Fig. 4. Input A and Input B are located on the left and the output are located on the right. Different from the half adder, the output region is at the centre of the channel. We first Page 12 of 22 254 demonstrate the XOR logic gate operation in Fig.4 (see Supplementary Movies S11-S13). The 255 logical XOR gate is operated such that 0 + 0 = 0, 1 + 0 = 1, 0 + 1 = 1 and 1 + 1 = 0. The process 256 of 0 + 0 = 0 in XOR gate is trivial, where no skyrmions are presents in input and output. We 257 interpret the process 1 + 0 = 1 and 0 + 1 = 1 as follow: When a skyrmion is placed on either 258 Input A or Input B, the skyrmion is diverged to the crossover region. Due to skyrmion edge 259 repulsion, the skyrmion travels at the centre and reaches the output terminal for detection. On 260 the other hand, the important process 1 + 1 = 0 is represented as follow: Skyrmions are placed 261 on both Input A and Input B, both skyrmions enter the crossover region and repel each other. 262 Then, two skyrmions travel simultaneously and are annihilated by the edges of the output 263 terminal. Thus, no skyrmions reaches the output region, representing logical 0 as the output of 264 XOR gate. The operation time for the XOR logic gate is 0.7 ns, which is much lower than 1.1 265 ns in half adder.

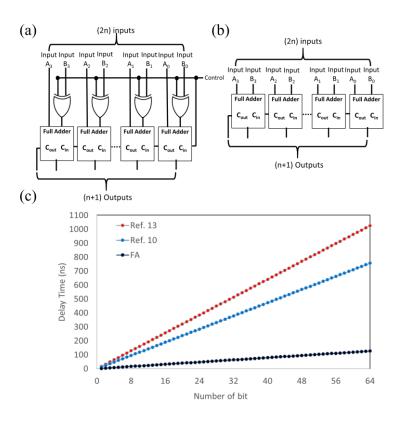

266 XOR logic gate is important in constructing adder-subtractor. A multi-bit ripple-carry 267 adder-subtractor is demonstrated in Fig. 5a, where the circuit is composed of multiple full 268 adders and XOR logic gate, in which the carry-out of each full adder is the carry-in of the 269 subsequent full adder. XOR logic gate provide Control input to the adder-subtractor logic 270 circuit. When the Control Input is logical 0, the XOR logic gate is a connection line. Thus, the 271 logical state in Input B is passed to the full adder without alternation and addition operation is 272 executed. On the other hand, when Control Input is logical 1, XOR logic gate is turn into a NOT 273 gate. Thus, the logical state in Input B will be flipped and passes to the full adder. In such condition, the logical computation  $A - B = A + \overline{B} + 1$  is realized in circuit and subtraction 274 275 operation is executed. Hence, by cascading or wire-connected the full adder and XOR logic 276 gate proposed in this study, a quick response skyrmion-based multi-bit ripple-carry adder-277 subtractor can be realized.

Fig. 4. Skyrmion-based XOR logic gate operation for each input case. The device size is 130 nm × 200 nm, and the applied current density j = 140 MA cm<sup>-2</sup>. The operation time of the XOR logic gate is 0.7 ns.

## 284 **3.4 Performance analysis of the proposed devices**

The operation of half adder, full adder and XOR logic gate that operate without skyrmion Hall effect have been demonstrated on SyAF structure. We first estimate the total delay time of our full adder and half adder using the following equation:

288

$$t_{operation} = t_{nucleation} + t_{propagation} + t_{dectection} \tag{4}$$

The  $t_{nucleation}$  of one skyrmion nucleation by MTJ is about 20 ps and the  $t_{dectection}$  by MTJ is about 5 ps [35]. Therefore, the operation time of our full adder and half adder is 1.98 ns and 1.13 ns, which is only about 12% and 19% of the previous skyrmion-based adder [13]. The difference is contributed by the SyAF structure, which allows skyrmion to be diverged by the conduct's edge in high current density without annihilation, and can make great impact on computational devices. For example, ripple-carry adder is constructed by series connection of single-bit adder, as shown in Fig. 5b. In such configuration, the delay time of the n-bit ripple296 carry adder is the sum of all single-bit full adder delay times. Fig. 5c shows the total delay time 297 of the n-bit ripple-carry adder for previous proposed devices [10, 13]. The blue and red symbols 298 correspond to the delay time consumption based on [10] and [13], respectively. The Black 299 symbols correspond to the delay time consumption of our design. Obviously, our adder design 300 response quicker than the previous proposal [10] and [13]. For a 64-bit system (n = 64), the 301 time delay in our design is about 126.4 ns, which is about 899 ns lower than previous skyrmion-302 based adder design [13]. The delay time can be further reduced to 110.65 ns by taking 303 advantages of the 0.25 ns delay time different between the OUTPUT and CARRY-OUT of the 304 single-bit adder. Since our proposed device are built on SyAF structure, it is possible to further 305 increase the operation speed by minimizing the device for sub-10 nm skyrmion [33, 34].

We then evaluate the energy efficiency of our adder devices using the Energy-delay product  $EDP_{operation} = E_{operation} \times t_{operation}$ , where  $E_{operation}$  is the energy during nucleation (Input), propagation and detection (Output), which are given by the following equation:

310

$$E_{operation} = E_{nucleation} + E_{propagation} + E_{detection}$$

(5)

311 The  $E_{Nucleation}$  of one skyrmion nucleation by MTJ is about 3.1 fJ, while the  $E_{Detection}$ 312 by MTJ is about 0.8 fJ [17].  $E_{Propagation}$  is calculated from the energy dissipation caused by the 313 electric resistance of the HM layer:

314

$$E_{propagation} = I^2 R_{HM} \Delta t = \rho_{HM} V_{HM} j^2 t_{propagation}$$

(6)

where  $\rho_{HM}$  is the resistivity of the HM (Resistivity of Pt =  $10.6 \times 10^{-8} \Omega \cdot m$ ), *j* is the current density,  $V_{HM}$  is the volume of the HM layer ( $190 \times 300 \times 2.5 nm^3$  for Full adder) and the  $t_{propagation}$  of full adder is 1.95 ns. Therefore, the EDP of full adder, including I/O, are estimated to be  $2.5 \times 10^{-22}$  Js, which are only about 79% of the previous proposed skyrmionbased adders [13]. The difference in energy efficiency is contributed by the smaller propagation area and shorter propagation time in our design, which allows the same functionality with a 321 smaller number of logic gates than the previous proposal. On the other hand, the size of our full 322 adder is 190 nm  $\times$  300 nm, which is only 48% of the previous proposed skyrmion based full 323 adder and 0.06% of the transistor based full adder [54]), which is significant for making 324 compact computer chips.

On the other hand, our design of the skyrmion-based adder is implemented by the skyrmion trajectory that is driven by SOT, which is one of the most commonly used methods applied in skyrmion-based devices to manipulate the magnetization. Recently, other approaches, such as the piezospintronics and topological anomalous Hall effect, have been predicted and experimentally demonstrated to switch magnetization with lower energy and less Joule heating effect [55-57]. These approaches on skyrmion-based device are worth studying due to their potential to further improve the energy efficiency of our proposed full-adder.

Fig. 5. (a) Diagram of wire-connected n-bit ripple-carry adder-subtractor (b) Diagram of wireconnected n-bit ripple-carry adder (c) Time delay of various skyrmion-based n-bit-ripple-carry adder. Red squares represent estimated Time delay for [13], blue squares correspond to the estimated time delay for [10] and black squares correspond to our proposed full adder design.

## 339 4 Conclusion

340 In summary, novel designs of the skyrmion-based arithmetic circuits and logic gates on SyAF 341 structure have been demonstrated. By introducing geometric notches and tilted edges on 342 patterned nanotracks, we have successfully constructed the half adder, the full adder and the 343 XOR logic gate based on skyrmions. Due to the simple geometries, the proposed logic gates 344 have the advantage of low delay time and high energy efficient when compared with the 345 conventional CMOS-based logic gates or skyrmion-based logic devices that have been 346 proposed. Since the skyrmion Hall effect is suppressed on the SyAF structure, our proposed logic gate is less sensitive to electric current fluctuation. We have also demonstrated the 347 348 strength of our proposed single-bit full adder by calculating the delay time and energy-delay Page 17 of 22

349 product of a multi-bit ripple carry adder circuit. Our proposed arithmetic circuit is compossible 350 with semiconductor fabrication technology in the industry. Therefore, the skyrmion-based 351 arithmetic circuit on the SyAF structure is a promising candidate for spintronics devices.

## 352 Acknowledgments

353 X.Z. was an International Research Fellow of Japan Society for the Promotion of Science 354 (JSPS). X.Z. was supported by JSPS KAKENHI (Grant No. JP20F20363). M.E. acknowledges 355 the support by the Grants-in-Aid for Scientific Research from JSPS KAKENHI (Grant Nos. 356 JP18H03676 and JP17K05490) and the support by CREST, JST (Grant Nos. JPMJCR20T2 and 357 JPMJCR16F1). X.L. acknowledges the support by the Grants-in-Aid for Scientific Research 358 from JSPS KAKENHI (Grant Nos. JP20F20363 and JP21H01364). Y.Z. acknowledges the 359 support by Shenzhen Fundamental Research Fund (Grant No. JCYJ20210324120213037), 360 Guangdong Special Support Project (Grant No. 2019BT02X030), Shenzhen Peacock Group 361 Plan (Grant No. KQTD20180413181702403), Pearl River Recruitment Program of Talents 362 (Grant No. 2017GC010293), and National Natural Science Foundation of China (Grant Nos. 363 11974298 and 61961136006). J.X. acknowledges the support by the National Natural Science Foundation of China (Grant No. 12104327). M.F. acknowledges the funding from the European 364 365 Union's Framework Program for Research and Innovation Horizon 2020 (2014-2020) under 366 the Marie Skłodowska-Curie Grant Agreement No. 860060 (ITN MagnEFi).

367

## 368 **References**

- 369 [1] Fert A, Cros V, Sampaio J, Skyrmions on the track, Nat. nanotechnol., 2013; 8:152-156.

- [2] Skyrme THR, A non-linear field theory, Selected Papers, With Commentary, Of TonyHilton Royle Skyrme, World Scientific1994; 195-206.

- [3] Skyrme THR, A unified field theory of mesons and baryons, Nucl. Phys; 1962; **31**:556-569.

- 373 [4] Khanh ND, Nakajima T, Yu X, Gao S, Shibata K, Hirschberger M, Yamasaki Y, Sagayama

- H, Nakao H, Peng L, Nanometric square skyrmion lattice in a centrosymmetric tetragonal

magnet, Nat. nanotechnol., 2020; 1-6.

- Page 18 of 22

- 376 [5] Jonietz F, Mühlbauer S, Pfleiderer C, Neubauer A, Münzer W, Bauer A, Adams T, Georgii

- R, Böni P, Duine RA, Spin transfer torques in MnSi at ultralow current densities, Sci., 2010;

- **378 330**:1648-1651.

- [6] Garcia-Sanchez F, Sampaio J, Reyren N, Cros V, Kim J, A skyrmion-based spin-torque

nano-oscillator, New J. Phys., 2016; 18:075011.

- [7] Muhlbauer S, Binz B, Jonietz F, Pfleiderer C, Rosch A, Neubauer A, Georgii R, Boni P,

Skyrmion Lattice in a Chiral Magnet, Sci., 2009; **323**: 915-919.

- 383 [8] Romming N, Hanneken C, Menzel M, Bickel JE, Wolter B, von Bergmann K, Kubetzka A,

- Wiesendanger R, Writing and deleting single magnetic skyrmions, Sci.,2013; **341**:636-639.

- 385 [9] Tokura Y, Kanazawa N, Magnetic Skyrmion Materials, Chem. Rev.;2020, 121, 5, 2857–

386 2897.

- 387 [10] Chauwin M, Hu X, Garcia-Sanchez F, Betrabet N, Paler A, Moutafis C, Friedman JS,

- 388 Skyrmion logic system for large-scale reversible computation, Phys. Rev. Appl., 2019;12:

389 064053.

- [11] Liu JP, Zhang Z, Zhao G, Skyrmions: topological structures, properties, and applications,

CRC Press2016.

- [12] Zhang X, Ezawa M, Zhou Y, Magnetic skyrmion logic gates: conversion, duplication and

merging of skyrmions, Sci. Rep., 2015; 5: 9400.

- [13] Song M, Park MG, Ko S, Jang SK, Je M, Kim KJ, Logic Device Based on Skyrmion

Annihilation, IEEE Trans Electron Devices, 2021, 4:1939-1943.

- [14] Xing X., Pong P. W. and Zhou Y., Skyrmion domain wall collision and domain wall-gated

skyrmion logic, Physical Review B, 2016, 94(5), 054408.

- [15] He Z., Angizi S. and Fan D., Current-induced dynamics of multiple skyrmions with

domain-wall pair and skyrmion-based majority gate design, IEEE Magnetics Letters, 2017, 8,15.

- 401 [16] Luo S., Song M., Li X., Zhang Y., Hong J., Yang X., Zou X., Xu N. and You L.,

402 Reconfigurable skyrmion logic gates, Nano letters, 2018, 18(2), 1990 1996.

- [17] Mankalale M. G., Zhao Z., Wang J.-P. and Sapatnekar S. S., SkyLogic—A proposal for a

skyrmion-based logic device, IEEE Transactions on Electron Devices, 2019, 66(4).

- [18] Zhang Z., Zhu Y., Zhang Y., Zhang K., Nan J., Zheng Z., Zhang Y. and Zhao W.,

Skyrmion-based ultra-low power electric-field-controlled reconfigurable (SUPER) logic gate,

IEEE Electron Device Letters, 2019, 40(12), 1984-1987.

- 408 [19] Al Azim Z., Chen M. C. and Roy K., Skyrmion Sensor-Based Low-Power Global 409 Interconnects, Ieee Transactions on Magnetics, 2017, **53**(1),1-6.

- [20] Zhang H., Zhu D., Kang W., Zhang Y. and Zhao W., Stochastic computing implemented

by skyrmionic logic devices, Physical Review Applied, 2020, 13(5), 054049-054061.

- [21] Luo S. and You L., Skyrmion devices for memory and logic applications, APL Materials,

2021, 9, 050901.

- [22] Jiang Y, Al-Sheraidah A, Wang Y, Sha E, Chung JG, A novel multiplexer-based lowpower full adder, IEEE Trans. Circuits Syst. II Express Briefs., 2004; **51**: 345-348.

- 416 [23] Bhattacharyya P, Kundu B, Ghosh S, Kumar V, Dandapat A, Performance Analysis of a

- Low-Power High-Speed Hybrid 1-bit Full Adder Circuit, IEEE Trans Very Large Scale Integr

VLSI Syst., 2015; 23:2001-2008.

- [24] Litzius K, Lemesh I, Krüger B, Bassirian P, Caretta L, Richter K, Büttner F, Sato K,

Tretiakov OA, Förster J, Skyrmion Hall effect revealed by direct time-resolved X-ray

microscopy, Nat. Phys., 2017;13:170-175.

- [25] Juge R, Je SG, de Souza Chaves D, Buda-Prejbeanu LD, Peña-Garcia J, Nath J, Miron IM,

Rana KG, Aballe L, Foerster M, Current-driven skyrmion dynamics and drive-dependent

skyrmion Hall effect in an ultrathin film, Phys. Rev. Appl.,2019;12: 044007.

- 425 [26] Jiang W, Zhang X, Yu G, Zhang W, Wang X, Benjamin Jungfleisch M, Pearson JE, Cheng

- 426 X, Heinonen O, Wang KL, Zhou Y, Hoffmann A, Suzanne G.E. te Velthuis, Direct observation

- 427 of the skyrmion Hall effect, Nat. Phys.,2016; **13**:162.

- 428 [27] Litzius K, Leliaert J, Bassirian P, Rodrigues D, Kromin S, Lemesh I, Zazvorka J, Lee KJ,

- 429 Mulkers J, Kerber N, The role of temperature and drive current in skyrmion dynamics, Nat.

430 Electron.,2020; 3: 30-36.

- 431 [28] Zeissler K, Finizio S, Barton C, Huxtable AJ, Massey J, Raabe J, Sadovnikov AV, Nikitov

- 432 SA, Brearton R, Hesjedal T, Diameter-independent skyrmion Hall angle observed in chiral

- 433 magnetic multilayers, Nat. comm.,2020; **11**: 1-11.

- 434 [29] Büttner F, Lemesh I, Beach GS, Theory of isolated magnetic skyrmions: From

435 fundamentals to room temperature applications, Sci. rep., 2018;8: 1-12.

- [30] Legrand W, Ronceray N, Reyren N, Maccariello D, Cros V, Fert A, Modeling the shape

of axisymmetric skyrmions in magnetic multilayers, Phys. Rev. Appl.,2018;10: 064042.

- 438 [31] Maccariello D, Legrand W, Reyren N, Ajejas F, Bouzehouane K, Collin S, George JM,

- 439 Cros V, Fert A, Electrical Signature of Noncollinear Magnetic Textures in Synthetic

440 Antiferromagnets, Phys. Rev. Appl., 2020: 14: 051001.

- [32] Zhang X, Zhou Y, Ezawa M, Magnetic bilayer-skyrmions without skyrmion Hall effect,

Nat. comm., 2016; 7: 10293.

- 443 [33] Legrand W, Maccariello D, Ajejas F, Collin S, Vecchiola A, Bouzehouane K, Reyren N,

- 444 Cros V, Fert A, Room-temperature stabilization of antiferromagnetic skyrmions in synthetic 445 antiferromagnets, Nat. Mat.,2020;**19**: 34-42.

- [34] Zhang X, Ezawa M, Zhou Y, Thermally stable magnetic skyrmions in multilayer synthetic

antiferromagnetic racetracks, Phys. Rev. B., 2016; **94**: 064406.

- 448 [35] Juge R., Bairagi K., Rana K. G., Vogel J., Sall M., Mailly D., Pham V. T., Zhang Q.,

- 449 Sisodia N., Foerster M., Aballe L., Belmeguenai M., Roussigné Y., Auffret S., Buda-Prejbeanu

- 450 L. D., Gaudin G., Ravelosona D. and Boulle O., Helium Ions Put Magnetic Skyrmions on the

- 451 Track, Nano Letters, 2021, **21**, 7, 2989–2996.

- 452 [36] Ohara K., Zhang X., Chen Y., Wei Z., Ma Y., Xia J., Zhou Y. and Liu X., Confinement

- 453 and Protection of Skyrmions by Patterns of Modified Magnetic Properties, Nano Letters, 2021,

- 454 21(10), 4320–4326.

- 455 [37] Tomasello R, Puliafito V, Martinez E, Manchon A, Ricci M, Carpentieri M, Finocchio G,

- 456 Performance of synthetic antiferromagnetic racetrack memory: domain wall versus skyrmion,

457 J Phys D Appl Phys., 2017; 50: 325302.

- 458 [38] Al Azim Z., Chen M. C. and Roy K., Skyrmion Sensor-Based Low-Power Global 459 Interconnects, *in IEEE Transactions on Magnetics*, 2017, **53**, 1-6.

- [39] Yoo MW, Cros V, Kim JV, Current-driven skyrmion expulsion from magnetic nanostrips,

Phys. Rev. B., 2017; 95: 184423.

- [40] Song M, Moon KW, Yang S, Hwang C, Kim KJ, Guiding of dynamic skyrmions using

chiral magnetic domain wall, Appl. Phys. Express., 2020; 13: 063002.

- [41] Vansteenkiste A, Leliaert J, Dvornik M, Helsen M, Garcia-Sanchez F, Van Waeyenberge

B, The design and verification of MuMax3, AIP adv., 2014; 4 :107133.

- [42] Bindal N., Ian C. A. C., Lew W. S. and Kaushik B. K., Antiferromagnetic skyrmion

repulsion based artificial neuron device, Nanotechnology, 2021, 32(21), 215204.

- [43] Fattouhi M., Mak K. Y., Zhou Y., Zhang X., Liu X. and El Hafidi M., Logic gates based

on synthetic antiferromagnetic bilayer skyrmions, Physical Review Applied, 2021, 16(1),

014040.

- 471 [44] Maccariello D., Legrand W., Reyren N., Ajejas F., Bouzehouane K., Collin S., George J.-

- 472 M., Cros V. and Fert A., Electrical Signature of Noncollinear Magnetic Textures in Synthetic

- 473 Antiferromagnets, Physical Review Applied, 2020, **14**(5), 051001.

- 474 [45] Legrand W., Maccariello D., Ajejas F., Collin S., Vecchiola A., Bouzehouane K., Reyren

- N., Cros V. and Fert A., Room-temperature stabilization of antiferromagnetic skyrmions in

synthetic antiferromagnets, Nature Materials, 2020, **19**(1),34-42.

- [46] Liu E., Wu Y.-C., Couet S., Mertens S., Rao S., Kim W., Garello K., Crotti D., Van

Elshocht S. and De Boeck J., Synthetic-ferromagnet pinning layers enabling top-pinned

magnetic tunnel junctions for high-density embedded magnetic random-access memory,

- 480 Physical Review Applied, 2018, **10**(5), 054054.

- [47] Gilbert TL, A phenomenological theory of damping in ferromagnetic materials, IEEE trans.

Magn., 2004; 40: 3443-3449.

- [48] Landau L, Lifshitz E, On the theory of the dispersion of magnetic permeability in

ferromagnetic bodies, Perspectives in Theoretical Physics, Elsevier., 1992; 51-65.

- [49] Zhang X, Xia J, Zhou Y, Wang D, Liu X, Zhao W, Ezawa M, Control and manipulation

of a magnetic skyrmionium in nanostructures, Phys. Rev. B., 2016; **94**: 094420.

- [50] Zhang H, Zhu D, Kang W, Zhang Y, Zhao W, Stochastic computing implemented by

skyrmionic logic devices, Phys. Rev. Appl., 2020; 13: 054049.

- 489 [51] Liang J., Wang W., Du H., Hallal A., Garcia K., Chshiev M., Fert A. and Yang H., Very

- 490 large Dzyaloshinskii-Moriya interaction in two-dimensional Janus manganese dichalcogenides

- 491 and its application to realize skyrmion states, Physical Review B, 2020, 101(18), 184401.

- 492 [52] Jadaun P., Register L. F. and Banerjee S. K., The microscopic origin of DMI in magnetic

493 bilayers and prediction of giant DMI in new bilayers, npj Computational Materials, 2020,

494 6(1),88.

- 495 [53] Sampaio J, Cros V, Rohart S, Thiaville A, Fert A, Nucleation, stability and current-induced

496 motion of isolated magnetic skyrmions in nanostructures, Nat. nanotechnol., 2013; 8: 839.

- 497 [54] Veeramachaneni S. and Srinivas M. B., New improved 1-bit full adder cells, 2008

498 Canadian Conference on Electrical and Computer Engineering, 2008: 000735-000738.

- [55] Liu Z., Chen H., Wang J., Liu J., Wang K., Feng Z., Yan H., Wang X., Jiang C. and Coey

J., Electrical switching of the topological anomalous Hall effect in a non-collinear

- antiferromagnet above room temperature, Nature Electronics, 2018, **1**(3),172-177.

- 502 [56] Yan H., Feng Z., Shang S., Wang X., Hu Z., Wang J., Zhu Z., Wang H., Chen Z. and Hua

- 503 H., A piezoelectric, strain-controlled antiferromagnetic memory insensitive to magnetic fields,

- 504 Nature nanotechnology, 2019, **14**(2),131-136.

- 505 [57] Liu Z., Feng Z., Yan H., Wang X., Zhou X., Qin P., Guo H., Yu R. and Jiang C.,

- 506 Antiferromagnetic piezospintronics, Advanced Electronic Materials, 2019, 5(7), 1900176.