## SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

## INFRA-2010-2.3.1 – First Implementation Phase of the European High Performance Computing (HPC) service PRACE

## PRACE-1IP

# **PRACE First Implementation Project**

**Grant Agreement Number: RI-261557**

# D9.3.3 Report on prototypes evaluation

## **Final**

Version: 1.0

Author(s): Lennart Johnsson, Gilbert Netzer, SNIC/KTH

Date: 29.03.2013

## **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-26                                                                                              | 1557                          |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------|

|               | <b>Project Title: PRACE I</b>                                                                                      | First Implementation Project  |

|               | <b>Project Web Site:</b> <a href="https://doi.org/10.2016/j.jps.100.000">https://doi.org/10.2016/j.jps.100.000</a> | p://www.prace-project.eu      |

|               | Deliverable ID: D9                                                                                                 | 0.3.3                         |

|               | <b>Deliverable Nature:</b> Re                                                                                      | port                          |

|               | <b>Deliverable Level:</b>                                                                                          | Contractual Date of Delivery: |

|               | PU                                                                                                                 | 31 / March / 2013             |

|               |                                                                                                                    | Actual Date of Delivery:      |

|               |                                                                                                                    | 31 / March / 2013             |

|               | EC Project Officer: Led                                                                                            | onardo Flores Añover          |

<sup>\* -</sup> The dissemination level are indicated as follows: **PU** – Public, **PP** – Restricted to other participants (including the Commission Services), **RE** – Restricted to a group specified by the consortium (including the Commission Services). **CO** – Confidential, only for members of the consortium (including the Commission Services).

## **Document Control Sheet**

|          | Title: Report on protot | types evaluation |

|----------|-------------------------|------------------|

| Document | ID: D9.3.3              | -                |

|          | Version: 1.0            | Status: Final    |

|          | Available at:           |                  |

# **Document Status Sheet**

| Version | Date             | Status        | Comments                            |

|---------|------------------|---------------|-------------------------------------|

| 0.1     | 17/October/2012  | Draft         | Skeleton with initial structure.    |

| 0.2     | 5/February/2013  | Draft         | First compilation of contributions. |

| 0.3     | 12/February/2013 | Draft         | Result section for WP feedback.     |

| 0.4     | 10/March/2013    | Draft         | Final WP feedback round.            |

| 0.5     | 15/March/2013    | Draft         | Internal Review                     |

| 0.6     | 25/March/2013    | Draft         | For MB/TB approval.                 |

| 1.0     | 29/March/2013    | Final version |                                     |

## **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure |  |

|------------------|-------------------------------------|--|

|                  |                                     |  |

#### **Disclaimer**

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n° RI-261557. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2013 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-261557 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| Pr | oject a | and Deliverable Information Sheet                                         | i   |

|----|---------|---------------------------------------------------------------------------|-----|

| Do | cume    | nt Control Sheet                                                          | i   |

| Do | cume    | nt Status Sheet                                                           | ii  |

| Do | cume    | nt Keywords                                                               | iii |

|    |         | Contents                                                                  |     |

|    |         | igures                                                                    |     |

|    |         |                                                                           |     |

|    |         | ables                                                                     |     |

|    |         | ces and Applicable Documents                                              |     |

| Li | st of A | cronyms and Abbreviations                                                 | XX  |

| Ex | ecutiv  | e Summary                                                                 | 1   |

| 1  | Intro   | oduction                                                                  | 2   |

| 2  | Tech    | nology Background                                                         | 4   |

| 3  |         | otypes                                                                    |     |

| 3  | 3.1     | ••                                                                        |     |

|    | 3.1     | 3.1.1 An NVIDIA Tegra 2 mobile SoC based HPC cluster, BSC                 |     |

|    |         | 3.1.2 GPU-GPU communication over PCIe and IB, CaSToRC                     |     |

|    |         | 3.1.3 FPGA matrix computation acceleration, JKU                           |     |

|    |         | 3.1.4 On die integrated CPU and GPU, PSNC                                 |     |

|    |         | 3.1.5 DSP based node for HPC, SNIC                                        |     |

|    |         | 3.1.6 Shared memory through a cache-coherency add-in card (NUMA-CIC), UiO |     |

|    | 3.2     | I/O Prototypes                                                            |     |

|    | 3.2     | 3.2.1 Exascale I/O, CEA/CINES                                             |     |

|    |         | 3.2.2 Exascale Integrated I/O Subsystem, FZJ                              |     |

|    | 3.3     | Holistic Approach to Energy Efficiency, LRZ                               |     |

| 4  | Instr   | rumentation                                                               |     |

| 4  | 4.1     | Node architecture prototype measurement setups                            |     |

|    | 4.1     | 4.1.1 An NVIDIA Tegra 2 mobile SoC based HPC cluster, BSC                 |     |

|    |         | 4.1.2 GPU-GPU communication over PCIe and IB, CaSToRC                     |     |

|    |         | 4.1.3 FPGA matrix computation acceleration, JKU                           |     |

|    |         | 4.1.4 On die integrated CPU and GPU, PSNC                                 |     |

|    |         | 4.1.5 DSP based node for HPC, SNIC                                        |     |

|    |         | 4.1.6 Shared memory through a cache-coherency add-in card (NUMA-CIC), UiO |     |

|    | 4.2     | I/O Prototype instrumentation                                             |     |

|    |         | 4.2.1 Exascale I/O, CEA/CINES                                             |     |

|    |         | 4.2.2 Exascale integrated I/O subsytem, FZJ                               |     |

|    | 4.3     | Holistic approach to energy efficiency, LRZ                               |     |

| 5  | Benc    | hmarks for Measurements                                                   | 50  |

|    | 5.1     | Overview Matrix                                                           |     |

|    | 5.2     | Brief benchmark descriptions                                              |     |

|    |         | 5.2.1 STREAM                                                              |     |

|    |         | 5.2.2 Dense matrix multiplication                                         | 51  |

|    |         | 5.2.3 Sparse matrix-vector multiplication                                 | 51  |

|    |         | 5.2.4 FFT                                                                 | 52  |

|    |         | 5.2.5 Linpack                                                             | 52  |

|   |     | 5.2.6 <i>Hydro</i>                                                        | 52  |

|---|-----|---------------------------------------------------------------------------|-----|

|   |     | 5.2.7 QCD                                                                 | 53  |

|   |     | 5.2.8 <i>IOR</i>                                                          | 53  |

|   |     | 5.2.9 <i>SIONlib</i>                                                      | 54  |

|   |     | 5.2.1 HLRS Metadata Benchmark                                             | 54  |

|   |     | 5.2.2 Dhrystone                                                           | 55  |

|   |     | 5.2.3 <i>Mprime</i>                                                       | 55  |

| 6 | Mea | surement results                                                          | 56  |

|   | 6.1 | Node assessments                                                          | 57  |

|   |     | 6.1.1 STREAM                                                              | 57  |

|   |     | 6.1.2 Dense matrix multiplication                                         | 68  |

|   |     | 6.1.3 Sparse Matrix Vector Multiplication                                 | 74  |

|   |     | 6.1.4 FFT                                                                 | 75  |

|   |     | 6.1.5 <i>Linpack</i>                                                      | 76  |

|   |     | 6.1.6 <i>Hydro</i>                                                        | 84  |

|   |     | 6.1.7 <i>QCD</i>                                                          | 86  |

|   |     | 6.1.8 Dhrystone                                                           | 88  |

|   | 6.2 | I/O                                                                       | 89  |

|   |     | 6.2.1 IOR Benchmark Results                                               | 89  |

|   |     | 6.2.2 SIONlib Bencmark Results                                            | 93  |

|   |     | 6.2.3 <i>Hydro</i>                                                        | 95  |

|   |     | 6.2.4 Metadata benchmarks                                                 | 97  |

|   |     | 6.2.5 Scanning large file system issues                                   | 100 |

|   | 6.3 | Cooling                                                                   | 106 |

|   |     | 6.3.1 Holistic approach to energy efficiency, LRZ                         | 106 |

| 7 | Con | clusions                                                                  | 111 |

|   | 7.1 | Node Architectures                                                        | 111 |

|   | 7.2 | I/O                                                                       | 112 |

|   | 7.3 | Cooling                                                                   | 112 |

| 8 | Ann | ex                                                                        | 114 |

|   | 8.1 | Key to benchmark result tables                                            | 114 |

|   | 8.2 | Node Benchmark Results                                                    | 115 |

|   |     | 8.2.1 An NVIDIA Tegra 2 mobile SoC based HPC cluster, BSC                 | 115 |

|   |     | 8.2.2 GPU-GPU communication over PCIe and IB, CaSToRC                     | 119 |

|   |     | 8.2.3 DSP based node for HPC, SNIC                                        | 121 |

|   |     | 8.2.4 Holistic approach to energy efficiency, LRZ                         | 125 |

|   |     | 8.2.5 On die integrated CPU and GPU, PSNC                                 | 130 |

|   | 8.3 | Shared Memory Scaling Benchmark Results                                   | 138 |

|   |     | 8.3.1 Shared memory through a cache-coherency add-in card (NUMA-CIC), UiO |     |

|   | 8.4 | Distributed Memory Scaling Benchmark Results                              |     |

|   |     | 8.4.1 An NVIDIA Tegra 2 mobile SoC based HPC cluster, BSC                 |     |

|   |     | 8.4.2 GPU-GPU communication over PCIe and IB, CaSToRC                     |     |

|   |     | 8.4.3 Holistic approach to energy efficiency, LRZ                         |     |

|   |     | **                                                                        |     |

# **List of Figures**

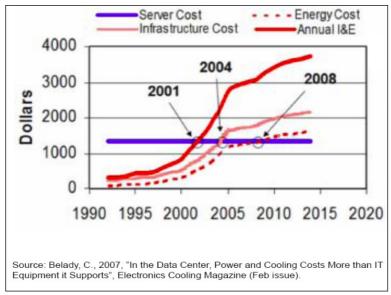

| Figure 1 Evolution of US power and cooling costs for standard x86 servers.                     |         |

|------------------------------------------------------------------------------------------------|---------|

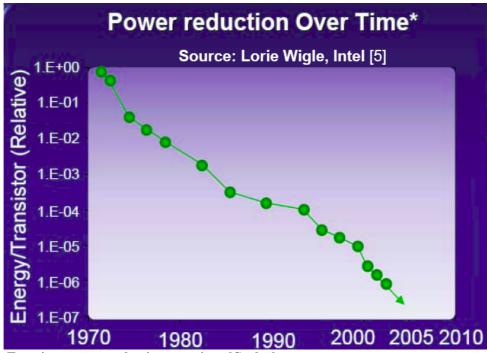

| Figure 2 Transistor power reduction over time. [Curley]                                        |         |

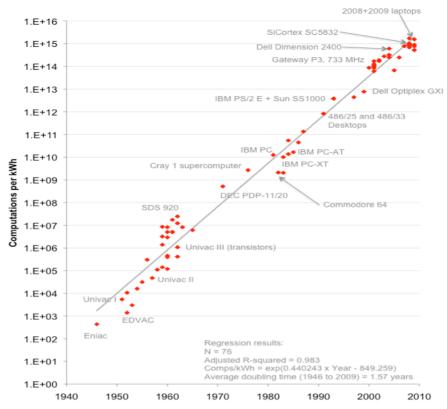

| Figure 3 Energy efficiency evolution of PCs. [Koomey-2009b]                                    | 5       |

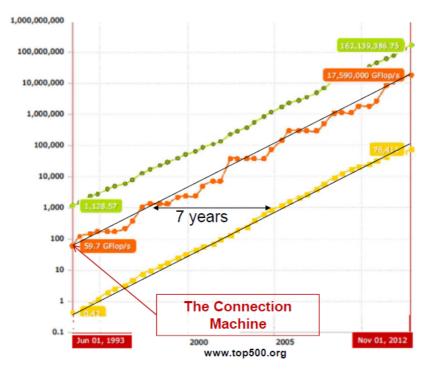

| Figure 4 Performance evolution of large HPC systems as measured by the Linpack (HPL) bence     | hmark.  |

|                                                                                                |         |

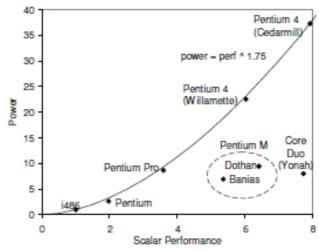

| Figure 5 Normalized power versus normalized scalar performance for multiple generations of     |         |

| microprocessors. [Intel-2006]                                                                  | 7       |

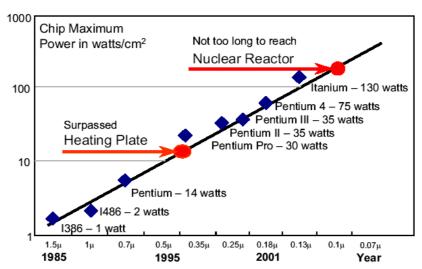

| Figure 6 Heat density of Intel microprocessors. Source: Shenkhar Borkar, Intel                 | 7       |

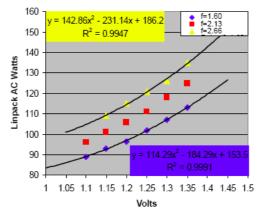

| Figure 7 Power requirements as a function of voltage and frequency. [Supermicro-2008]          | 8       |

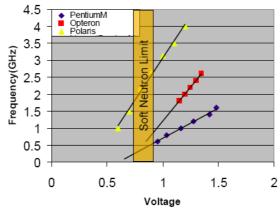

| Figure 8 Relationship between frequency and voltage. [Supermicro-2008]                         | 8       |

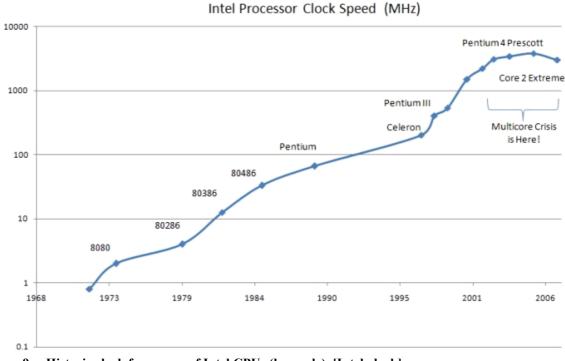

| Figure 9 Historic clock frequency of Intel CPUs (log scale). [Intel-clock]                     | 8       |

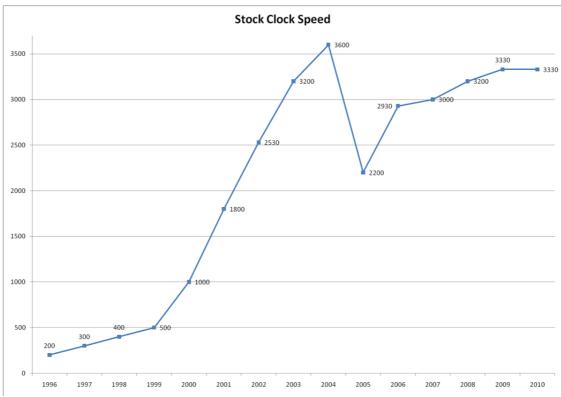

| Figure 10 Clock frequency of recent Intel CPUs without turbo boost. [ung-2010]                 | 9       |

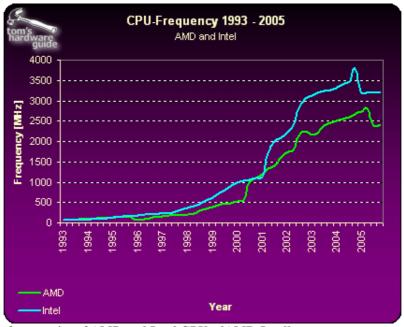

| Figure 11 Clock frequencies of AMD and Intel CPUs. [AMD-Intel]                                 | 9       |

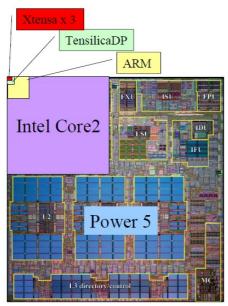

| Figure 12 Illustration of the large difference in size and power consumption of CPUs abou      | t 2005. |

| [Shalf-2007]                                                                                   | 10      |

| Figure 13 Hot water cooling and heat reuse [IBM-2009]                                          | 13      |

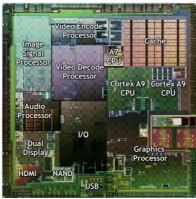

| Figure 14 NVIDIA Tegra 2 System on Chip (SoC).                                                 |         |

| Figure 15 Q3 compute node card                                                                 |         |

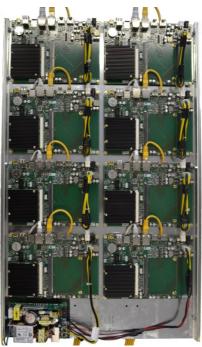

| Figure 17 19" rack with 16 compute containers.                                                 | 16      |

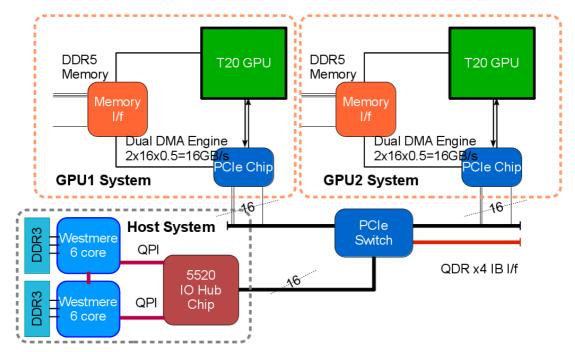

| Figure 19 IBM iDataplex dx360M3 server board and 2U chassis with two GPUs                      | 18      |

| Figure 20 Node configuration for the x86+GPU prototype                                         |         |

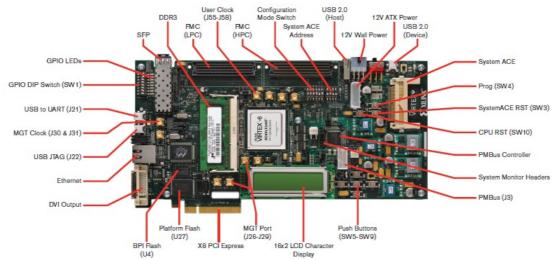

| Figure 21 Xilinx Vertex-6 ML605 evaluation module.                                             |         |

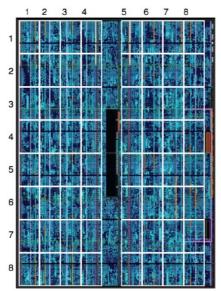

| Figure 22 Floorplan of a 8 × 8 stream matrix multiplication accelerator on a Xilinx Virtex-6   |         |

| Each box outlines a tile with a double-precision floating-point multiply-and-add unit, local m | emory,  |

| and communication network                                                                      |         |

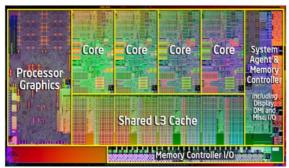

| Figure 23 Intel Sandy Bridge die and block diagram.                                            | 21      |

| Figure 25 The AMD Brazos E-350 motherboard.                                                    | 21      |

| Figure 26 AMD Llano A8-3870 die.                                                               | 22      |

| Figure 27 AMD Trinity A-10 5800k die.                                                          | 22      |

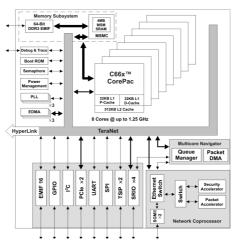

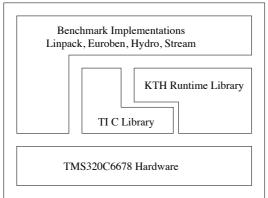

| Figure 28 Texas Instruments TMS320C6678 DSP block diagram.                                     | 23      |

| Figure 29 Texas Instruments TMS320C6678 DSP evaluation module                                  | 23      |

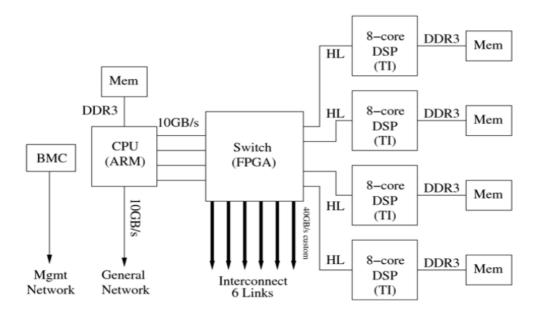

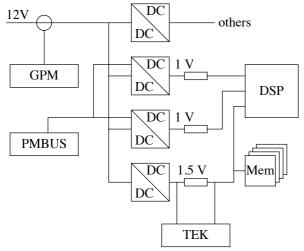

| Figure 30 Schematic of HPC node based on TI TMS320C6678 DSPs                                   | 24      |

| Figure 32 NumaConnect add-on HyperTransport card.                                              | 26      |

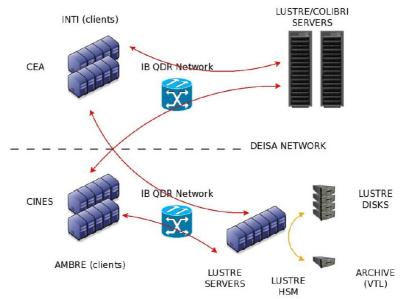

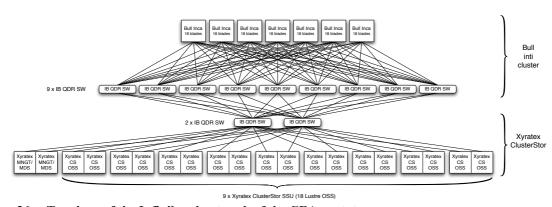

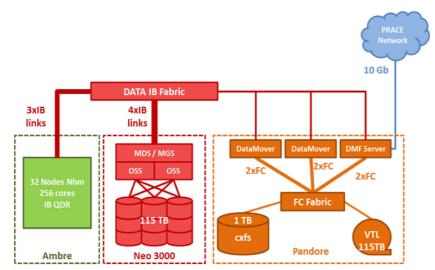

| Figure 33 The distributed file system CEA/CINES prototype.                                     | 27      |

| Figure 34 Xyratex racks and drawer.                                                            | 28      |

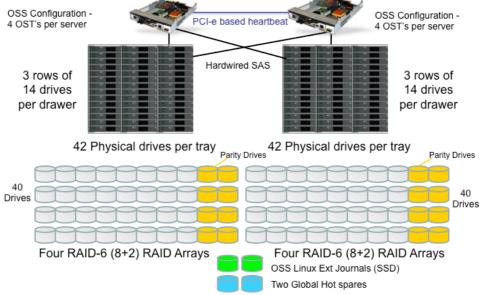

| Figure 35 Scalable Storage Unit (SSU) configuration.                                           | 28      |

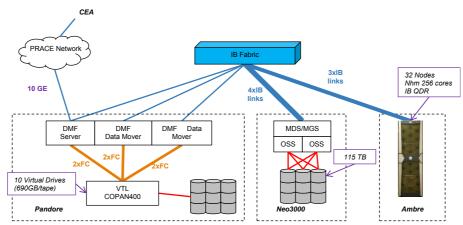

| Figure 37 The CINES storage system using MAID technology.                                      | 29      |

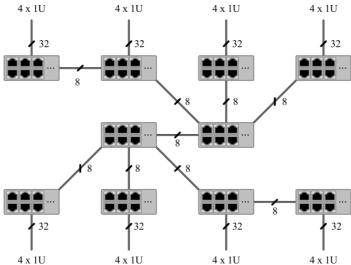

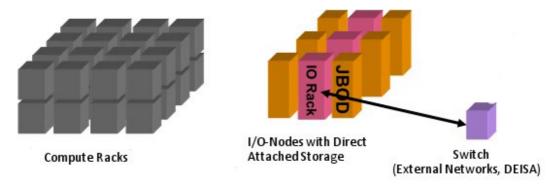

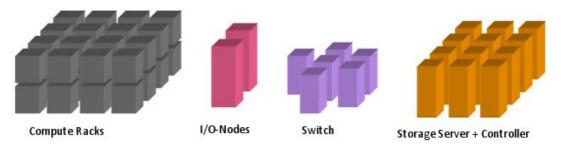

| Figure 38 Storage integrated into MPP/Cluster interconnection network.                         | 32      |

| Figure 39 Traditional cluster storage architecture.                                            | 32      |

| Figure 40 Schematic of the cluster I/O prototype                                               | 34      |

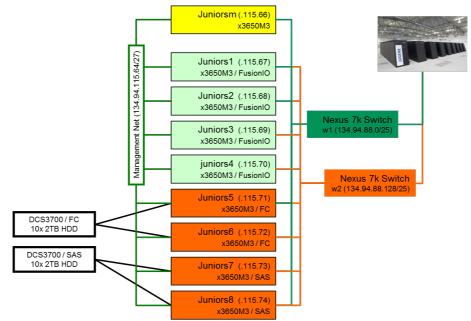

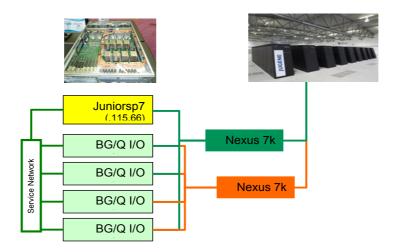

| Figure 42 CooLMUC prootype at the Leibniz Supercomputer Centre.                                | 35      |

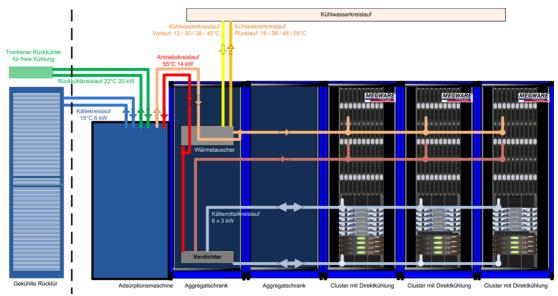

| Figure 43 CoolMUC compute node with copper pipes for direct liquid cooling.                    | 36      |

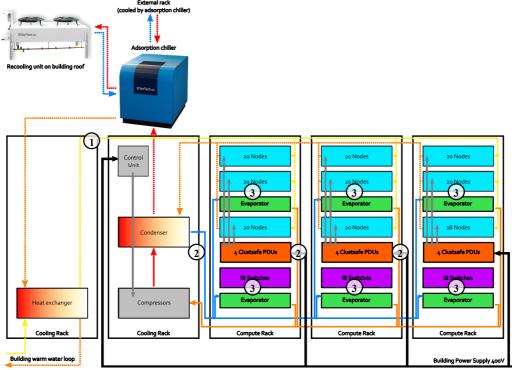

| Figure 44 CoolMUC cooling system schematic.                                                    | 37      |

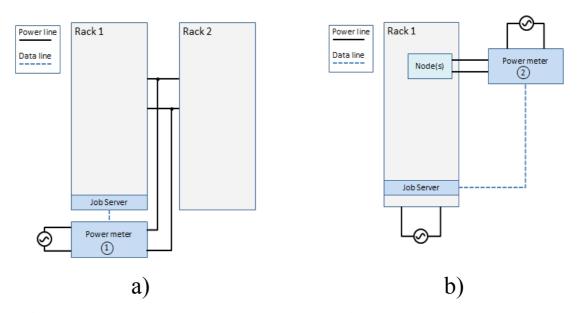

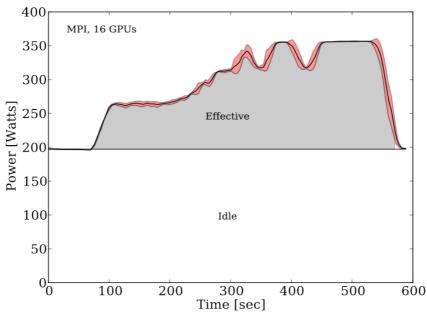

| Figure 45 Rack power a) and node power b) measurements of the Tegra 2 cluster                  | 39      |

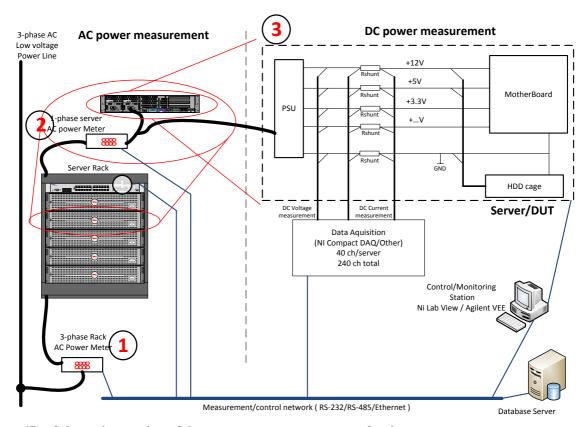

| Figure 47 Schematic overview of the power measurement system for the prototype                 | 41      |

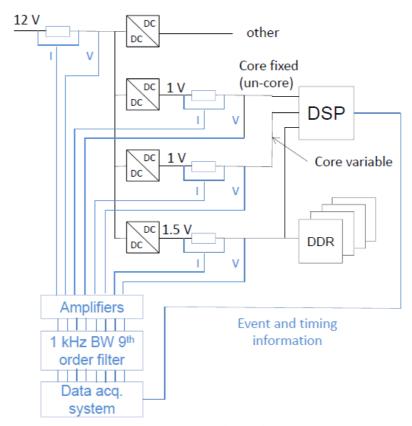

| Figure 48 The power measurement instrumentation of the DSP EVM prototype.                      |         |

| Figure 50 Older instrumentation of the DSP EVM using build power sensors and multimeters       | 43      |

| Figure 51 Schematic overview of the instrumentation of the x86 prototype.                      |         |

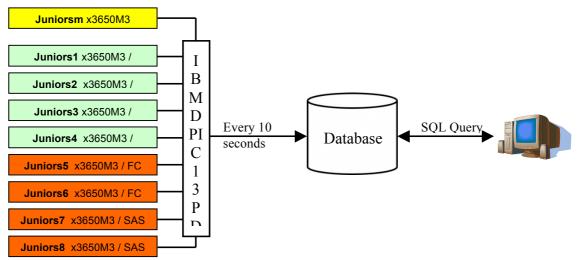

| Figure 52 Schematic overview of the instrumentation of the MPP prototype.                      | 47      |

| Figure 53 SQL table to store PDU power monitoring information.                                 | 47      |

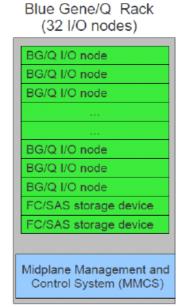

| Figure 54 SQL table holding the BG/Q power measurements.                                       | 47      |

| Figure 55 Schematic overview of the power distribution and cooling measurement system          | 48      |

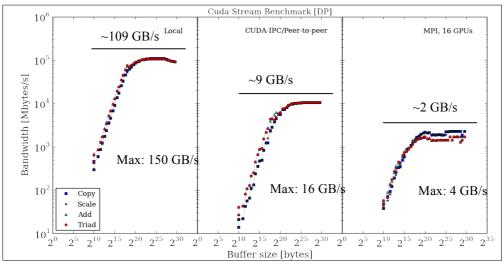

| Figure 57 STREAM performance results using NVIDIA's Unified Virtual Addressing technology for             |

|-----------------------------------------------------------------------------------------------------------|

| local GPU memory access (left), GPU-to-GPU memory access through the PCIe buses and switch o              |

| the same node (center), and GPU-to-GPU memory access via PCIe buses and host memories (right).5           |

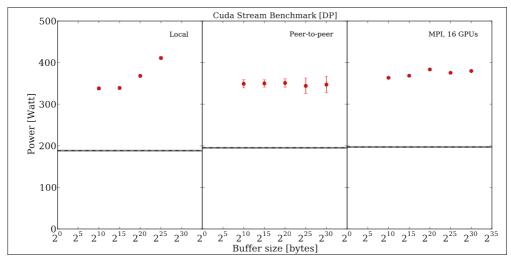

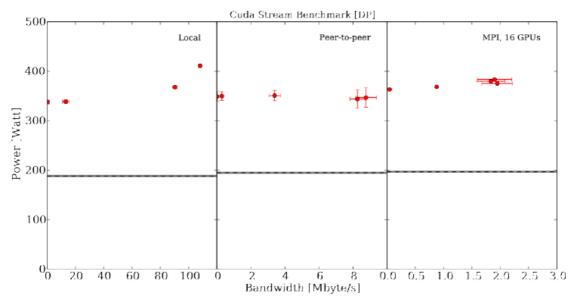

| Figure 58 Active power consumption for the local, intra-node and inter-node STREAM benchmarks a           |

| a function of array size for local GPU memory access (left), GPU-to-GPU memory access through th          |

| PCIe buses and switch on the same node (center), and GPU-to-GPU memory access via PCIe buse               |

| and host memories (right).                                                                                |

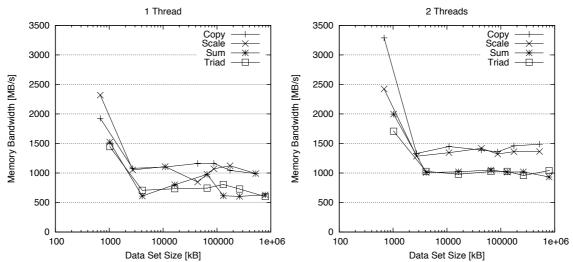

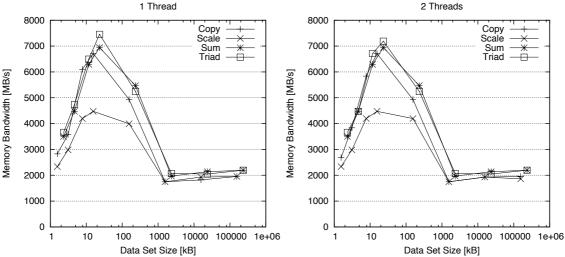

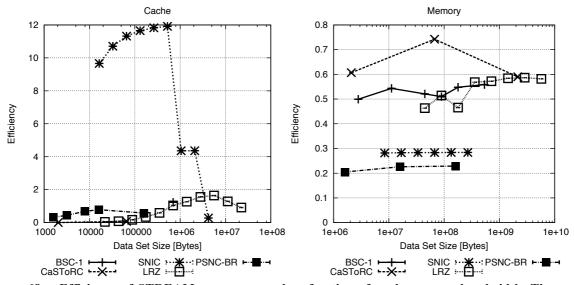

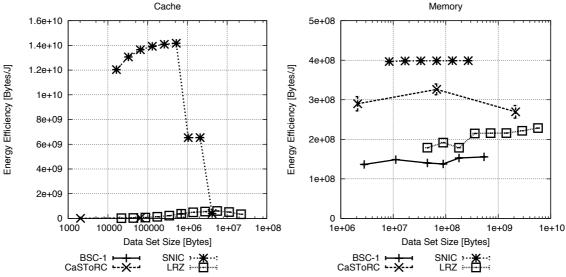

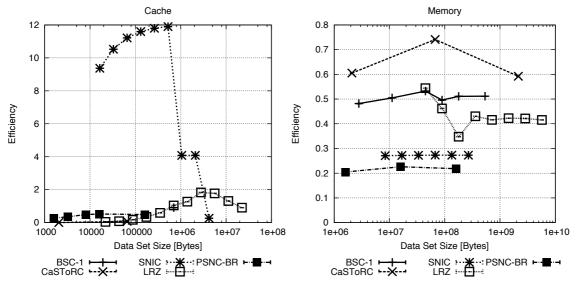

| Figure 60 AMD Brazos APU STREAM performance for 1 and 2 threads using OpenMP                              |

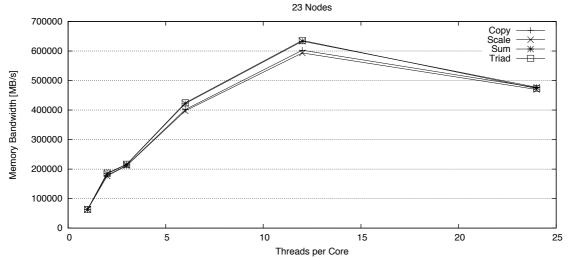

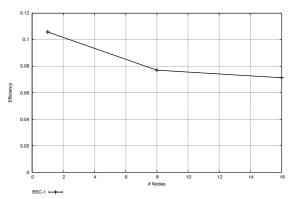

| Figure 62 Efficiency of the STREAM benchmark vs. number of threads per node for the NUMA-CIO              |

| prototype                                                                                                 |

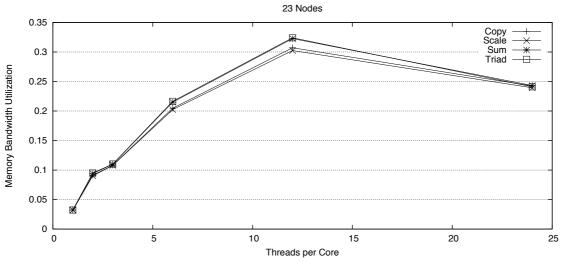

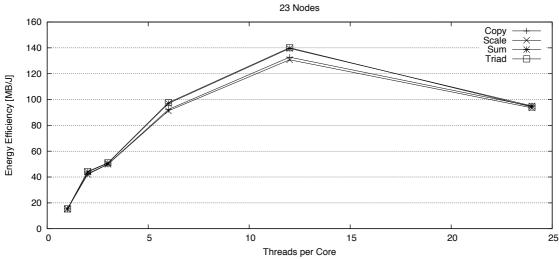

| Figure 63 Energy efficiency obtained by the STREAM benchmark for varying number of threads pe             |

| node for the NUMA-CIC prototype                                                                           |

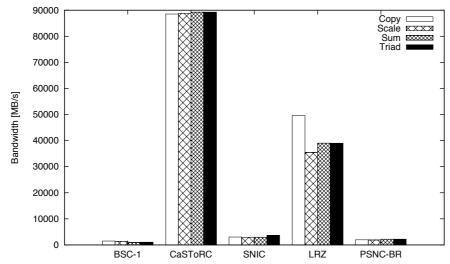

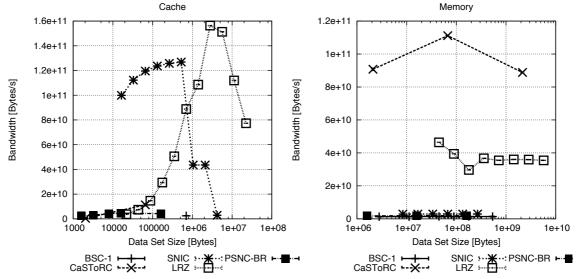

| Figure 64 Memory bandwidth obtained using the STREAM benchmark kernels shown for the larges               |

| vector sizes reported.                                                                                    |

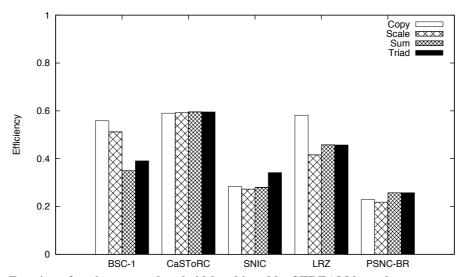

| Figure 65 Fraction of peak memory bandwidth achieved by STREAM kernels                                    |

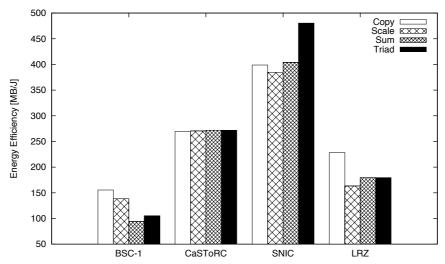

| Figure 66 Energy efficiency obtained by the STREAM benchmark kernels for the largest reporte              |

| vector sizes                                                                                              |

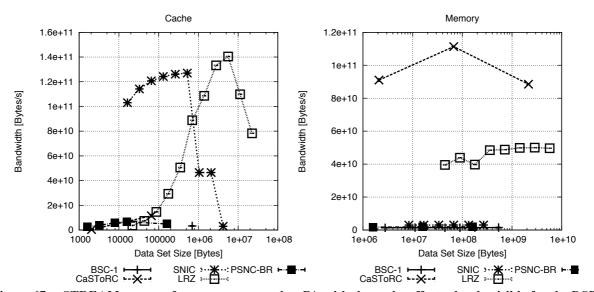

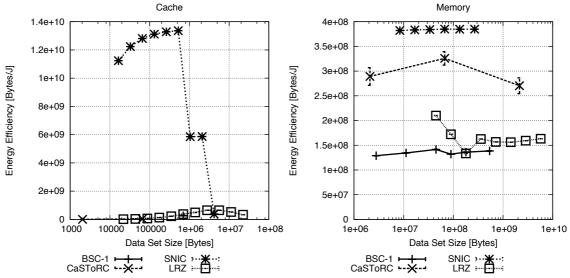

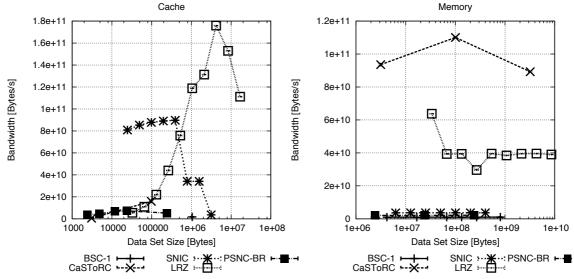

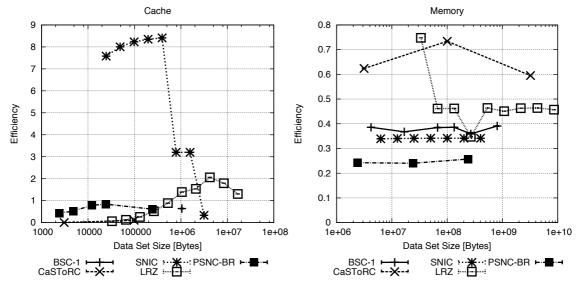

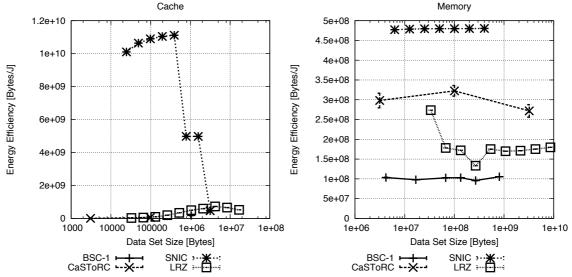

| Figure 67 STREAM <i>copy</i> performance measured as B/s with the cache effects clearly visible for th    |

|                                                                                                           |

| DSP (SNIC) and Magny-Cours (LRZ) prototypes and the significantly higher memory bandwidths of             |

| the x86+GPU and Magny-Cours prototypes.                                                                   |

| Figure 68 Efficiency of STREAM copy expressed as fraction of peak memory bandwidth. The cach              |

| memory bandwidth amplification is apparent.                                                               |

| Figure 69 STREAM <i>copy</i> energy efficiency measured as B/J.                                           |

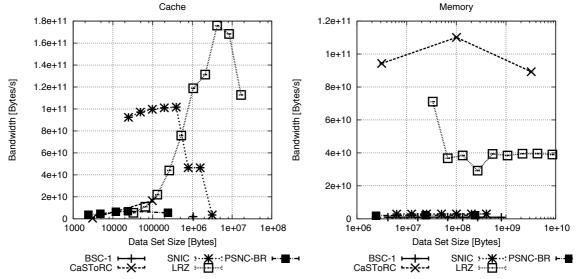

| Figure 70 STREAM scale performance measured as B/s, with the cache effects for the DSP (SNIC              |

| and Magny-Cours (LRZ) prototypes clearly visible                                                          |

| Figure 71 Efficiency of STREAM scale expressed as fraction of peak memory bandwidth. The cach             |

| memory bandwidth amplification is apparent.                                                               |

| Figure 72 STREAM <i>scale</i> energy efficiency measured as B/J                                           |

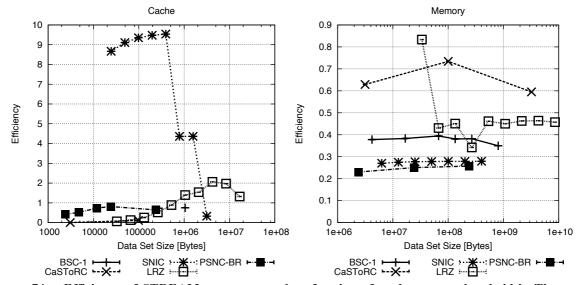

| Figure 73 STREAM sum performance measured as B/s, with the cache effects for the DSP (SNIC) an            |

| Magny-Cours (LRZ) prototypes clearly visible.                                                             |

| Figure 74 Efficiency of STREAM sum expressed as fraction of peak memory bandwidth. The cach               |

| memory bandwidth amplification is apparent.                                                               |

| Figure 75 STREAM sum energy efficiency measured as B/J.                                                   |

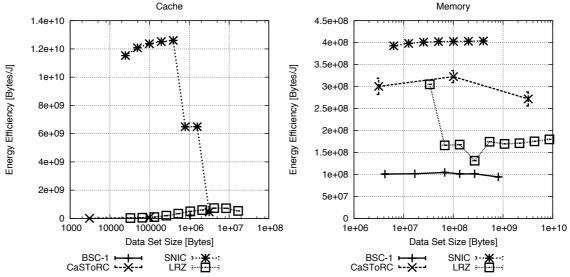

| Figure 76 STREAM triad performance measured as B/s, with the cache effects for the DSP (SNIC              |

| and Magny-Cours (LRZ) prototypes clearly visible                                                          |

| Figure 77 Efficiency of STREAM triad expressed as fraction of peak memory bandwidth. The cach             |

| memory bandwidth amplification is apparent.                                                               |

| Figure 78 STREAM <i>triad</i> energy efficiency measured as B/J.                                          |

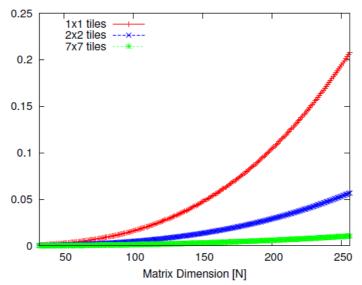

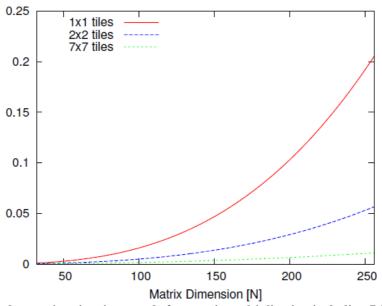

| Figure 79 Measured execution time in seconds for matrix multiplication including PCI                      |

| communication time on the Xilinx ML605 FPGA for 1, 4 and 49 tiles                                         |

| Figure 80 Predicted execution time in seconds for matrix multiplication including PCI                     |

| communication time on the Xilinx ML605 FPGA for 1, 4 and 49 tiles.                                        |

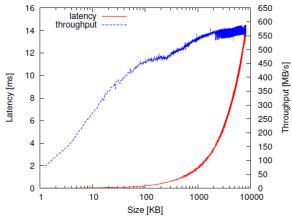

| Figure 81 PCIe Gen-1 x8 data transfer time in milliseconds as a function of transferred data set size. 70 |

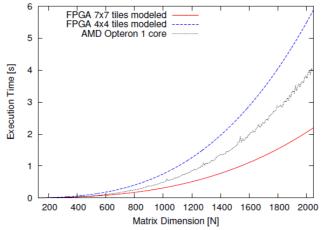

| Figure 82 Predicted execution time in seconds using the stream architecture FPGA design for the           |

| Xilinx ML605.                                                                                             |

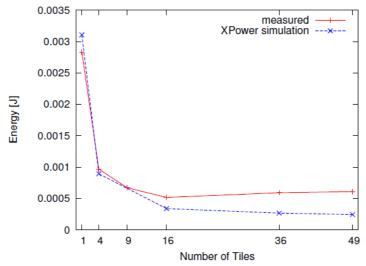

| Figure 83 Measured and predicted FPGA power consumption as a function of the number of tiles for          |

| 32 x 32 matrix multiplication                                                                             |

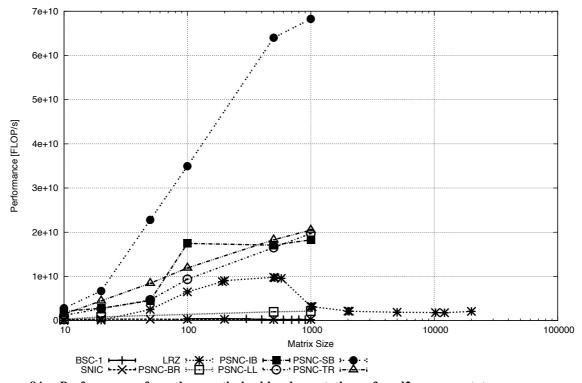

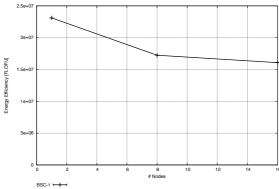

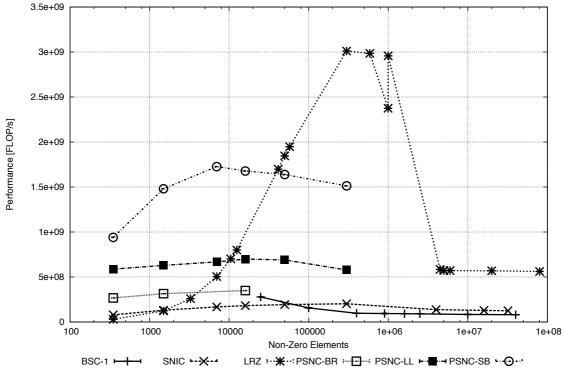

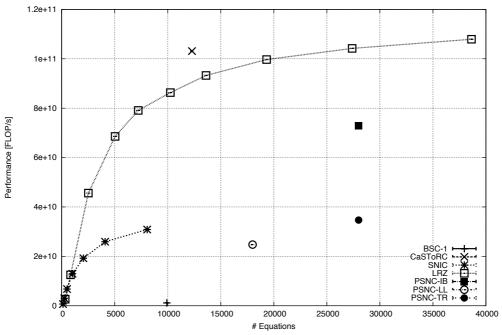

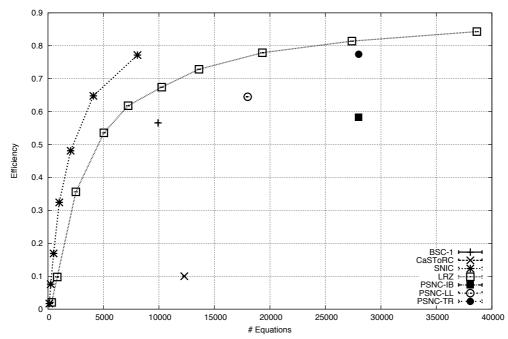

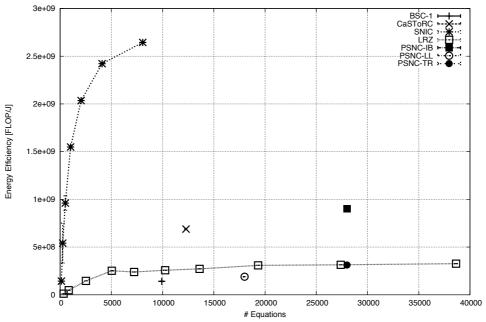

| Figure 84 Performance of mostly unoptimized implementations of mod2am on prototypes                       |

|                                                                                                           |

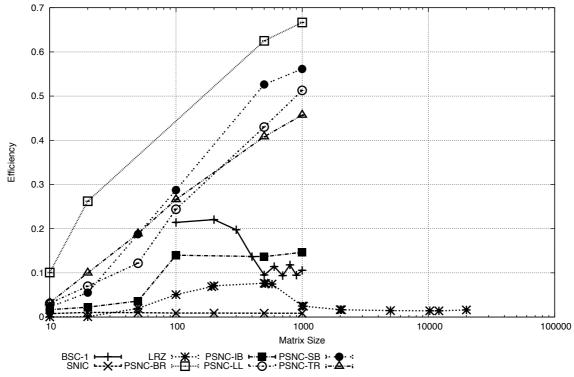

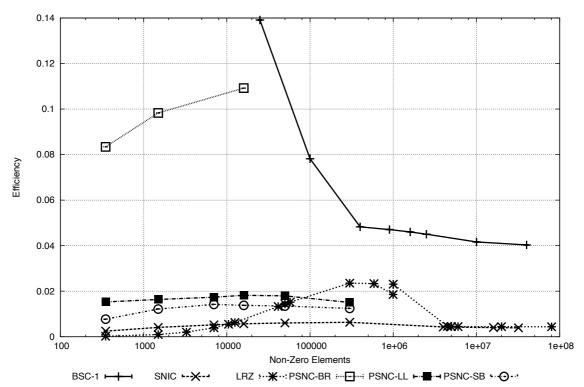

| Figure 85 The efficiencies of mostly unoptimized implementations of mod2am.                               |

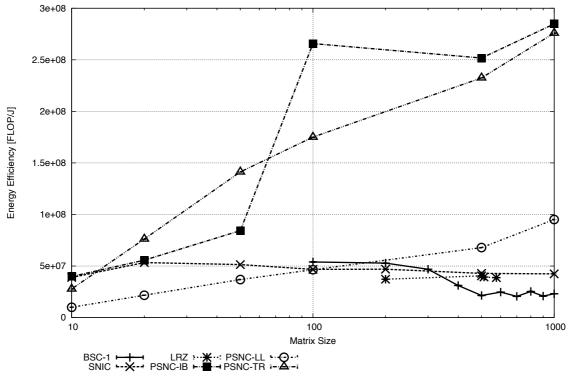

| Figure 86 The energy efficiencies of mostly un-optimized implementations of mod2am                        |

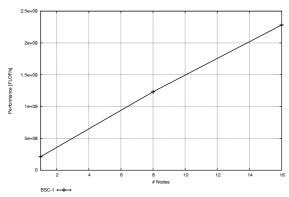

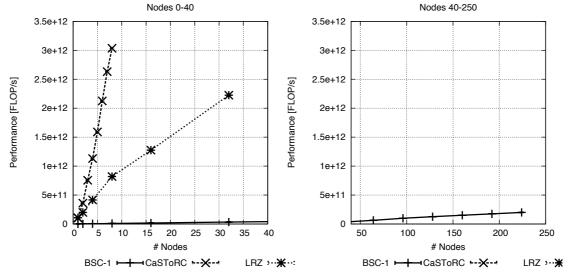

| Figure 87 Performance scaling across nodes for the Euroben mod2am kernel on the Tegra 2 prototype         |

| 7. 20 C 4 C 1 C 1 C 1 C 1 C 1 C 1 C 1 C 1 C 1                                                             |

| Figure 88 Computational efficiency scaling obtained for the Euroben mod2am kernel on the Tegra            |

| prototype                                                                                                 |

| Figure 89 Energy efficiency scaling for the Euroben mod2am kernel obtained by the Tegra                   |

| prototype 7-                                                                                              |

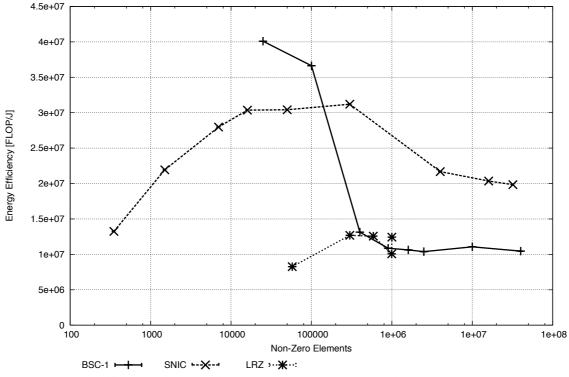

| Figure 90 Performance of mod2as on some of the prototypes.                                                      | 74      |

|-----------------------------------------------------------------------------------------------------------------|---------|

| Figure 91 Computational efficiency of mod2as on some of the prototypes                                          | 75      |

| Figure 92 Energy efficiency of the mod2as implementations on some of the prototypes                             |         |

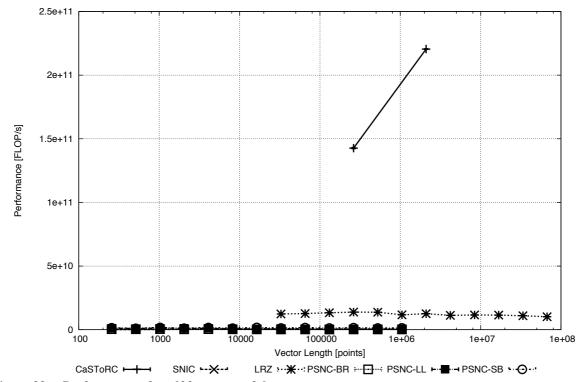

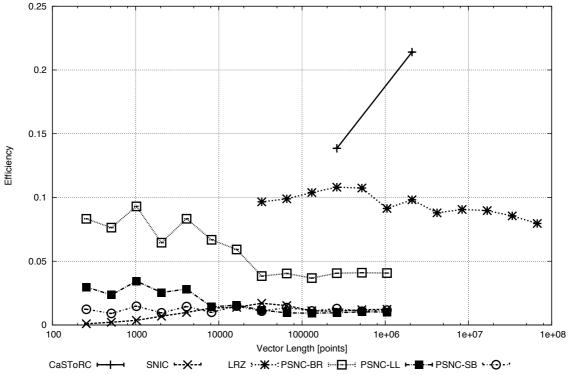

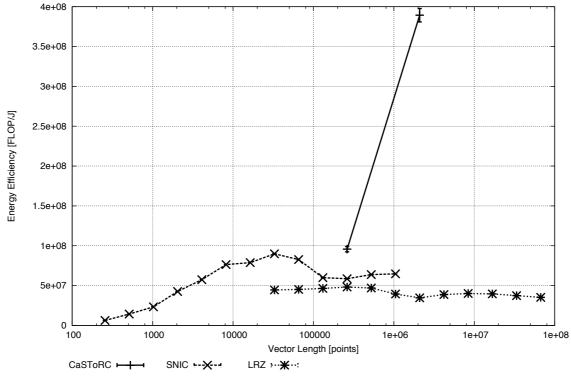

| Figure 93 Performance of mod2f on some of the prototypes.                                                       | 76      |

| Figure 94 Efficiency of mod2f on the prototypes                                                                 | 77      |

| Figure 95 Energy efficiency of mod2f on the prototypes                                                          |         |

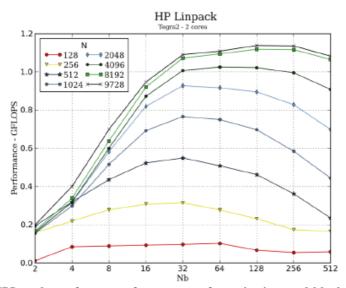

| Figure 96 Tegra 2 HPL node performance for a range of matrix sizes and block sizes. Node theo                   | retical |

| peak performance 2 GF/s at 1 GHz.                                                                               | 78      |

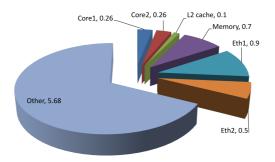

| Figure 97 Power consumption of various components of the Tegra 2 prototype node for HPL.                        | Total   |

| power consumption is 8.4 W.                                                                                     |         |

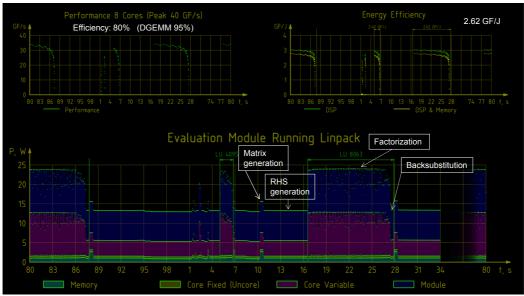

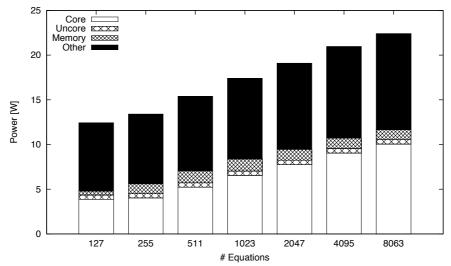

| Figure 98 Power consumption of the measured subsystems of the DSP node for different HPL r                      | uns at  |

| 1250 MHz clock frequency.                                                                                       |         |

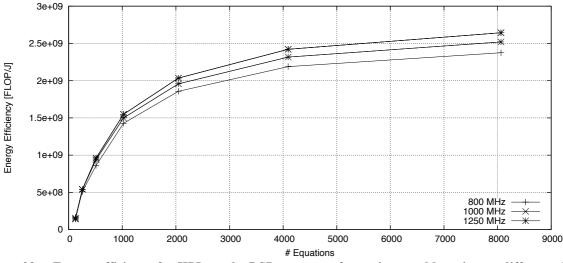

| Figure 99 Energy efficiency for HPL on the DSP prototype for various problem sizes at different                 |         |

| frequencies.                                                                                                    |         |

| Figure 100 HPL node performance on several prototypes.                                                          |         |

| Figure 101 HPL node efficiencies achieved on several prototypes.                                                |         |

| Figure 102 HPL node energy efficiencies achieved on several prototypes                                          |         |

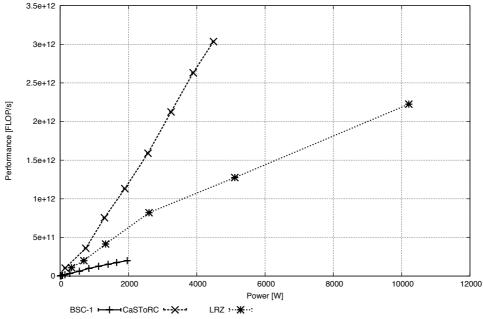

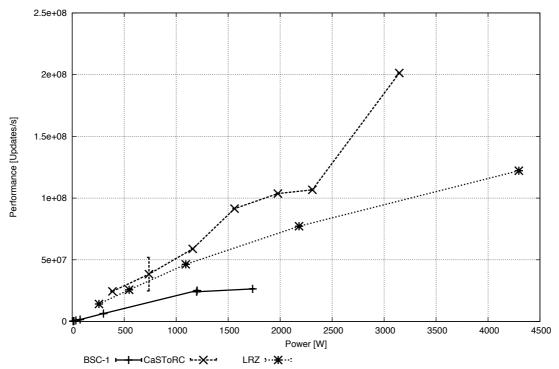

| Figure 103 Performance plotted against power for the HPL benchmark scaling across nodes                         |         |

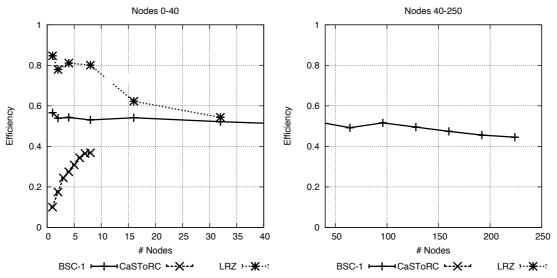

| Figure 105 Scalability of HPL efficiency on the Tegra 2, x86+GPU, and Magny-cours clusters                      |         |

| Figure 106 Scalability of the HPL energy efficiency on the Tegra 2, x86+GPU, and Magny                          |         |

| clusters.                                                                                                       |         |

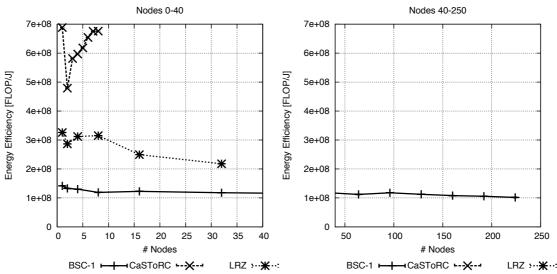

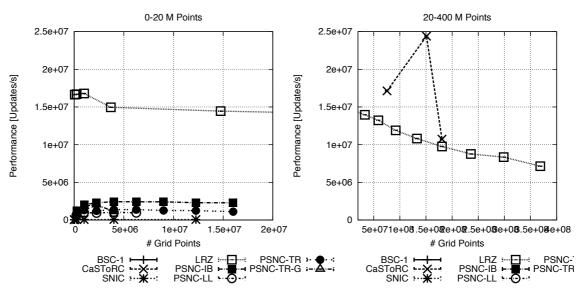

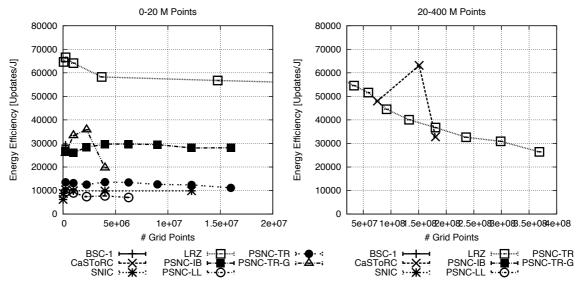

| Figure 107 Performance of the Hydro benchmark measured in terms of updates per grid-poi                         | _       |

| second for a range of grid points.                                                                              |         |

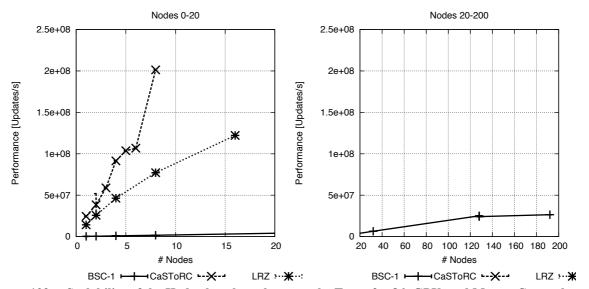

| Figure 109 Scalability of the Hydro benchmark across the Tegra 2, x86+GPU, and Magny-                           |         |

| cluster measured as grid point updates/sec.                                                                     |         |

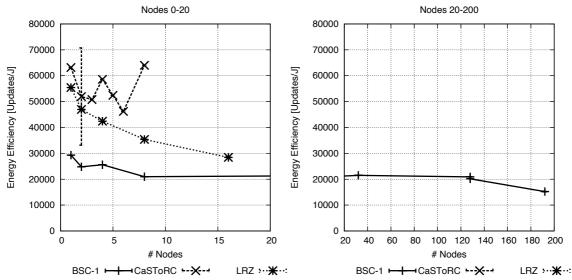

| Figure 110 Scalability of the energy efficiency of the Hydro benchmark across the Tegra 2, x86+                 | -       |

| and Magny-Cours nodes measured as grid-point updates/J.                                                         |         |

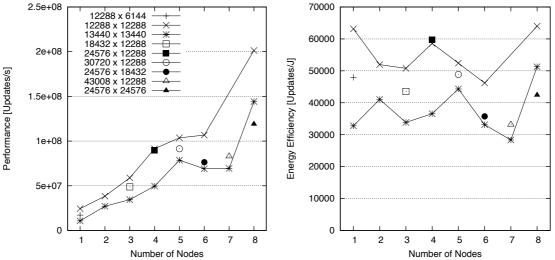

| Figure 111 Hydro Performance and energy scalability for different problem sizes on the x86 (CoSToPC) protesting |         |

| (CaSToRC) prototypeFigure 112 Performance of Hydro versus measures power for multiple node scaling runs         |         |

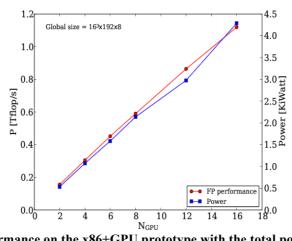

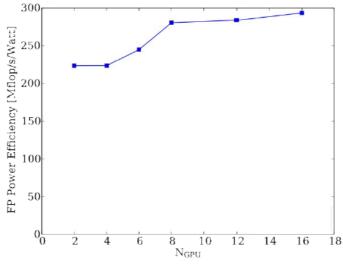

| Figure 113 QUDA performance on the x86+GPU prototype with the total power consumption                           |         |

| Figure 114 The energy efficiency of the QUDA code on the x86+GPU prototype based on total                       |         |

| consumption                                                                                                     |         |

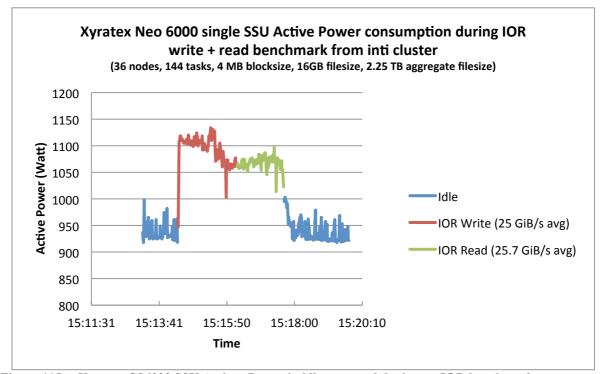

| Figure 115 Xyratex CS6000 SSU Activer Power in idle state and during an IOR benchmark                           |         |

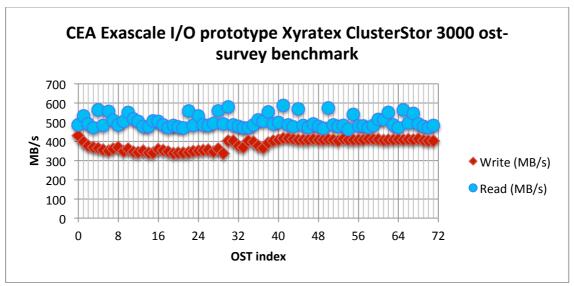

| Figure 116 ost-survey Lustre benchmark results with the CS3000 system at CEA                                    |         |

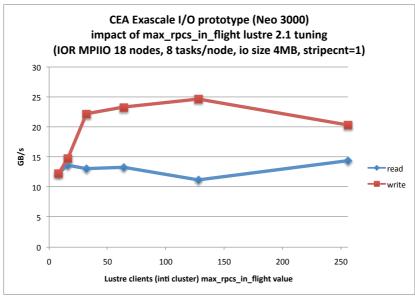

| Figure 117 Impact of max_rpcs_in_flight value on I/O performance                                                |         |

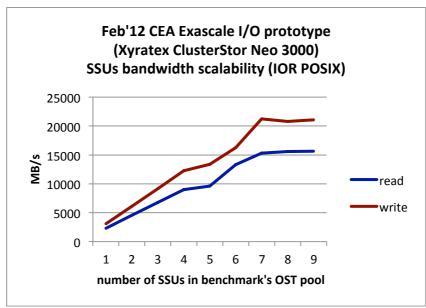

| Figure 118 CS3000 IOR POSIX benchmark.                                                                          |         |

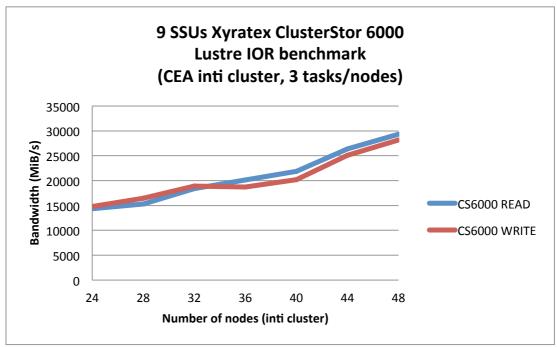

| Figure 119 CS6000 IOR POSIX benchmark.                                                                          |         |

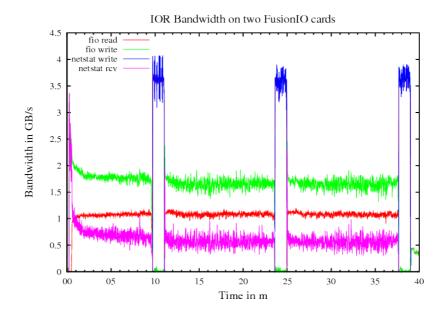

| Figure 120 GPFS bandwidth measurements for the IOR benchmark on two Fusion-io cards                             |         |

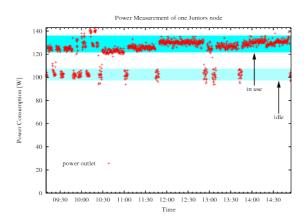

| Figure 121 Power consumption of one I/O node with two Fusion-io cards as read from PDU                          |         |

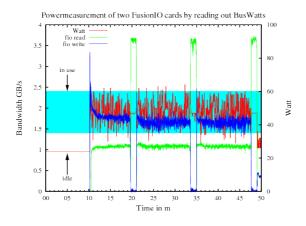

| Figure 122 Power consumption of two Fusion-io cards as read from the cards                                      |         |

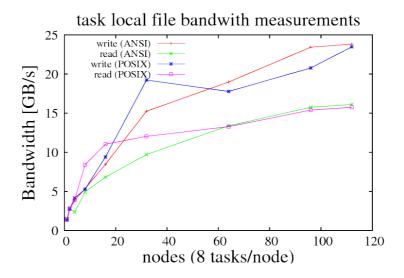

| Figure 123 SIONlib benchmark results for task local files.                                                      | 94      |

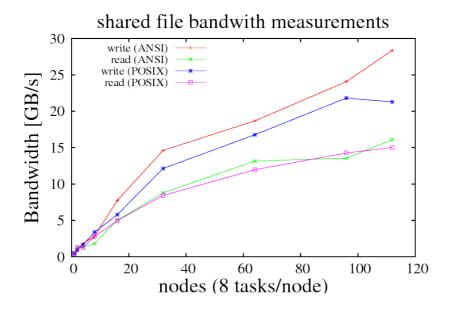

| Figure 124 SIONlib benchmark results for shared files.                                                          | 94      |

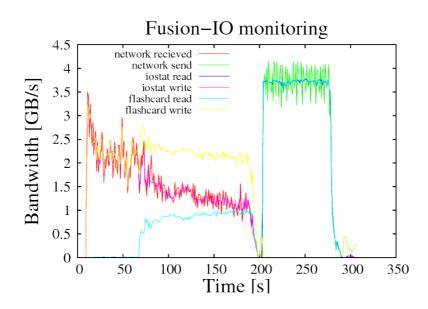

| Figure 125 Fusion-io card monitoring results for detailed performance analysis.                                 | 95      |

| Figure 126 Timing results for the Hydro benchmark on a cluster of four servers with four I/O                    |         |

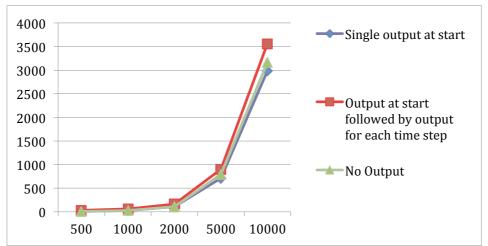

| each with two Fusion-io cards and 10 GbE interconnection.                                                       | 96      |

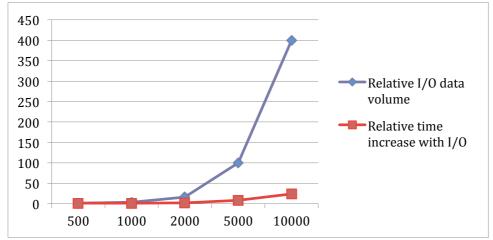

| Figure 127 Scalability of data volume and incremental time for I/O for the Hydro benchmarl                      |         |

| cluster of four servers with four I/O nodes each with two Fusion-io cards and 10 GbE interconnections           | ection. |

|                                                                                                                 |         |

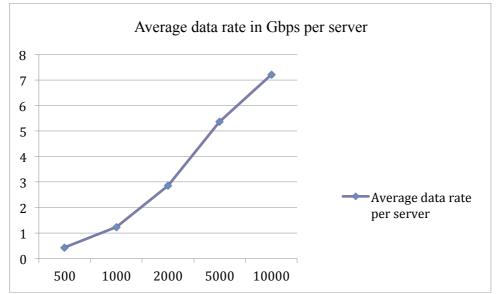

| Figure 128 Average data rate per server for I/O for the Hydro benchmark on a cluster of four s                  |         |

| with four I/O nodes each with two Fusion-io cards and 10 GbE interconnection                                    |         |

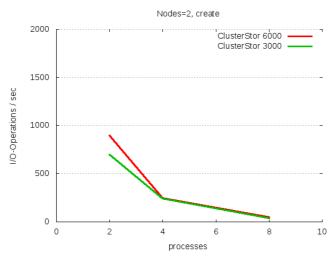

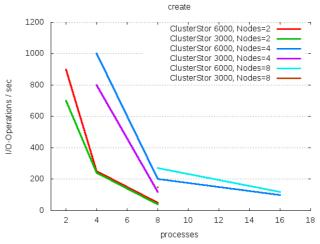

| Figure 129 I/O-Operations/sec per process, for <i>create</i> on two nodes.                                      |         |

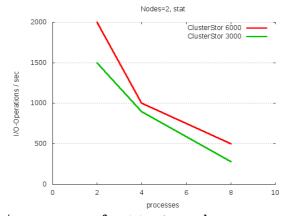

| Figure 130 I/O-Operations/sec per process, for <i>stat</i> on two nodes                                         |         |

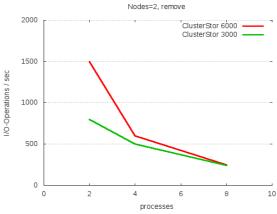

| Figure 131 I/O-Operations/sec per process, for <i>remove</i> on two nodes                                       |         |

| Figure 132 I/O-Operations/sec per process, for <i>create</i> on two, four and eight nodes                       |         |

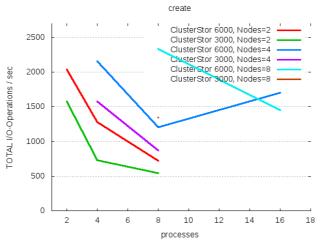

| Figure 133 Total I/O-Operations/sec, for <i>create</i> on two, four and eight nodes                             | 99      |

#### D9.3.3

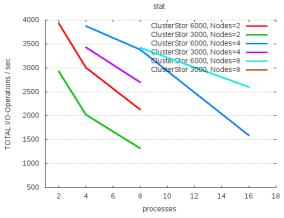

| Figure 134 Total I/O-Operations/sec, for <i>stat</i> on two, four and eight nodes        | 99    |

|------------------------------------------------------------------------------------------|-------|

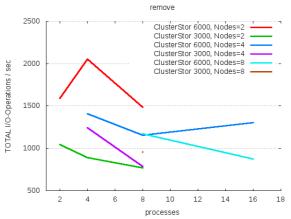

| Figure 135 Total I/O-Operations/sec, for remove on two, four and eight nodes             | 100   |

| Figure 136 Data management and back-up system for the CINES prototype                    | 101   |

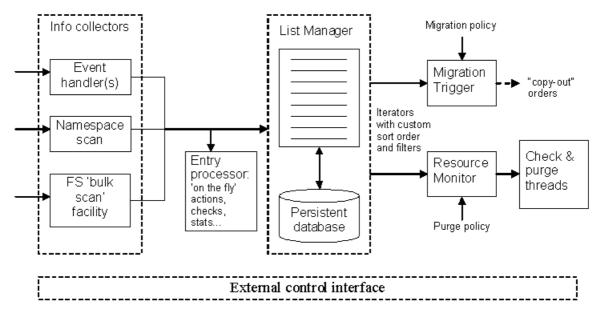

| Figure 137 The Robinhood Policy Engine architecture.                                     | 102   |

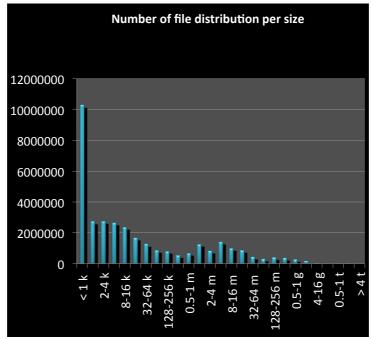

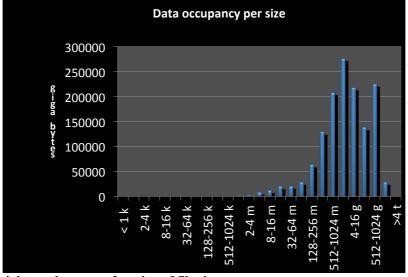

| Figure 138 Distribution of file sizes for the 34 million files in the CINES file system. | 104   |

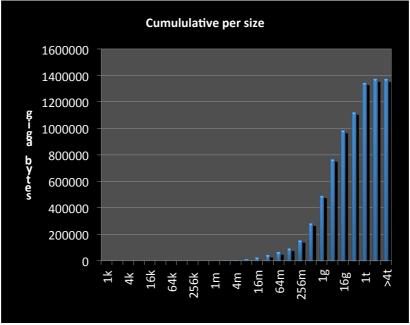

| Figure 139 Total data volume as a function of file size.                                 | 104   |

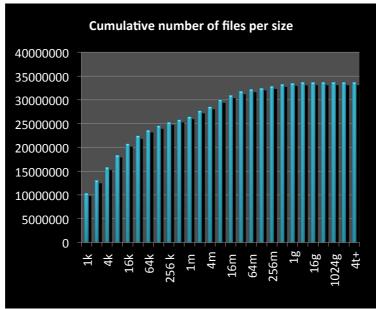

| Figure 140 Cumulative distribution of files in the CINES file system                     | 105   |

| Figure 141 Cumulative distribution of data volume in files as a function of size.        | 105   |

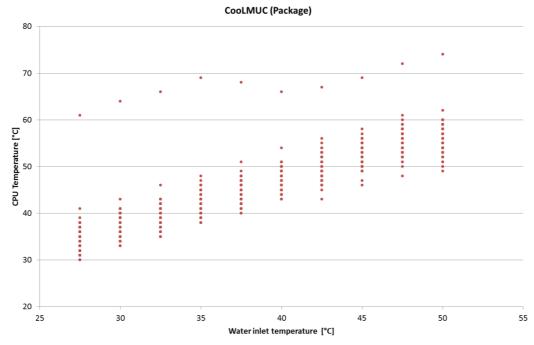

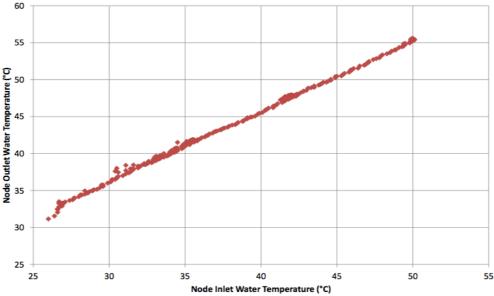

| Figure 142 CPU temperatures in relation to water inlet temperature.                      | 107   |

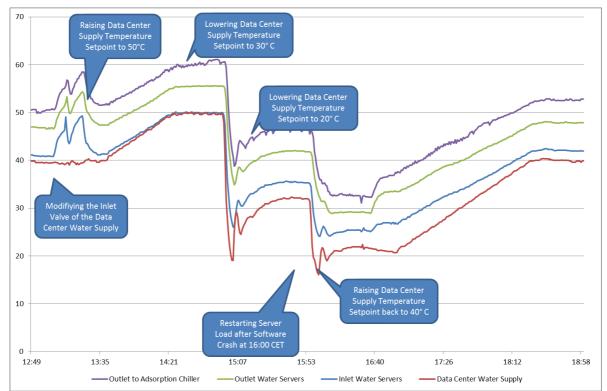

| Figure 143 Water inlet setpoint and water outlet temperature response curves.            | 107   |

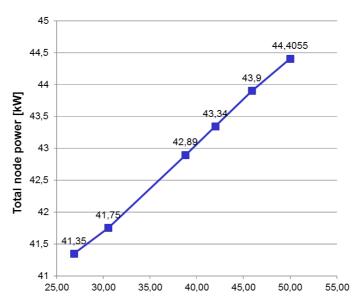

| Figure 144 Water inlet vs water outlet temperature under max CPU load                    | 108   |

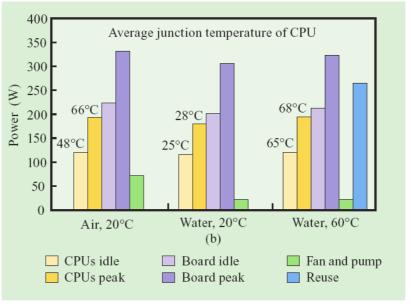

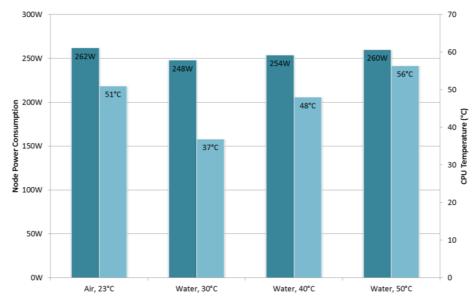

| Figure 145 Comparison of node power consumption and CPU temperature of air-cooled nodes  | s and |

| direct liquid cooled nodes at different inlet temperatures.                              | 109   |

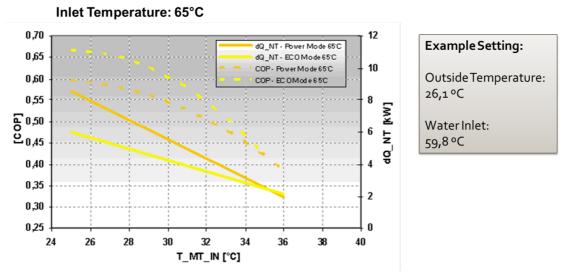

| Figure 147 SortTech Adsorption chiller efficiency curve for 65°C inlet temperature       | 110   |

| Figure 148 Potential applications for heat reuse                                         | 113   |

# **List of Tables**

| Table 1 Energy efficiency for Top500 systems in MF/J for the HPL benchmark                       | 6   |

|--------------------------------------------------------------------------------------------------|-----|

| Table 2 Energy per instruction (EPI) of Intel microprocessors. [Intel-2006]                      | 7   |

| Table 3 Summary of the nominal double precision floating-point performance                       | 12  |

| Table 4 Prototype processor and node characteristics.                                            | 14  |

| Table 6 Detailed prototype hardware description for the CEA and CINES sites                      | 30  |

| Table 7 Energy and performance data for flash based storage.                                     | 31  |

| Table 8 Some I/O device performance data.                                                        |     |

| Table 9 Integrated I/O system prototype hardware.                                                |     |

| Table 10 BSC NVIDIA Tegra 2 mobile SoC based node Prototype Characteristics                      | 38  |

| Table 11 On-chip and off-chip quantities measured by FPGA system monitor                         | 40  |

| Table 12 Instrumentation properties.                                                             |     |

| Table 13 Error budget for the DSP measurement system. The total errors are dependent on the se   | _   |

| channel in the table the worst case is specified.                                                |     |

| Table 14 Summary of the instrumentation.                                                         |     |

| Table 15 Properties of the Exascale integrated I/O subsytem instrumentation.                     |     |

| Table 16 CoolMUC internal sensor description.                                                    |     |

| Table 17 Summarizes what computational benchmarks were carried out on the different prototype    |     |

| Table 18 Summarizes what I/O benchmarks were carried out on the different prototypes             |     |

| Table 19 Parameter space used for the IOR benchmark                                              |     |

| Table 20 Suggested parameter space for the SIONlib benchmark.                                    |     |

| Table 21 Abbreviations for the prototypes used in the graphs and the report.                     |     |

| Table 22 STREAM <i>copy</i> performance and energy efficiency on the DSP prototype               |     |

| Table 23 STREAM <i>scale</i> performance and energy efficiency for the DSP prototype             |     |

| Table 24 Memory bandwidth and energy efficiency obtained by the STREAM benchmark kerne           |     |

| the largest reported vector sizes. PSNC power measurement data is excluded due to instrument     |     |

| problems, see also section 8.2.5                                                                 |     |

| Table 25 FPGA power estimates at 250 MHz clock frequency for 1 to 8 tiles.                       |     |

| Table 26 HPL parameters used for benchmarking of the GPU prototype                               |     |

| Table 27 Performance, efficiency and energy efficiency of the 8-core DSP prototype node.         |     |

| Table 28 Dhrystone performance, measured in Dhrystone MIPS (DMIPS), for the Tegra2 prot          |     |

| node in comparison with an i7 node.                                                              |     |

| Table 29 Active Power consumption of one Xyratex SSU measured at CEA.                            |     |

| Table 30 Performance per watt of Xyratex ClusterStor SSUs.                                       |     |

| Table 31 GPFS write and read performance using 8 Fusion-io cards on 4 nodes.                     |     |

| Table 33 Timing results for the Hydro benchmark on a cluster of four servers with four I/O nodes |     |

| with two Fusion-io cards and 10 GbE interconnection.                                             |     |

| Table 34 Performance of various file system <i>scan</i> approaches for Lustre.                   |     |

| Table 35 Available measurement quantities on CooLMUC                                             |     |

| Table 36 Performance and energy to solution results for the Euroben mod2am kernel. (BSC)         |     |

| Table 37 Performance and energy to solution results for the Euroben mod2as kernel. (BSC)         |     |

| Table 38 Performance and energy to solution results for the Hydro application benchmark. (BSC)   |     |

| Table 39 Performance and energy to solution results for the Linpack benchmark. (BSC)             |     |

| Table 40 Performance and energy to solution for the STREAM copy benchmark using 2 the            |     |

| (BSC)                                                                                            |     |

| Table 41 Performance and energy to solution for the STREAM scale benchmark using 2 th            |     |

| (BSC)                                                                                            |     |

| Table 42 Performance and energy to solution for the STREAM sum benchmark using 2 threads. (      |     |

| Table 42 Description and annual description for the CTDFAM description and assistance 2 days     |     |

| Table 43 Performance and energy to solution for the STREAM triad benchmark using 2 th            |     |

| (BSC)                                                                                            |     |

| Table 44 Performance and energy to solution for the STREAM copy benchmark using 1 thread. (      |     |

| Table 45 Performance and energy to solution for the STREAM scale benchmark using 1 thread. (     |     |

| Table 43 Performance and energy to solution for the STREAM scale benchmark using 1 thread. (     |     |

|                                                                                                  | 11/ |

| Table 46 Performance and energy to solution for the STREAM sum benchmark using 1 thread. (BSC)   |

|--------------------------------------------------------------------------------------------------|

| Table 47 Performance and energy to solution for the STREAM triad benchmark using 1 thread. (BSC) |

|                                                                                                  |

| Table 48 Performance and energy to solution for the Euroben mod2f benchmark. (CaSToRC) 119       |

| Table 49 Performance and energy to solution for the Hydro application benchmark. (CaSToRC) 119   |

| Table 50 Performance and energy to solution for the Linpack benchmark. (CaSToRC)                 |

| Table 52 Performance and energy to solution for the STREAM scale benchmark. (CaSToRC) 120        |

| Table 53 Performance and energy to solution for the STREAM sum benchmark. (CaSToRC) 120          |

| Table 55 Performance and energy to solution for the Euroben mod2am benchmark. (SNIC) 121         |

| Table 56 Performance and energy to solution for the Euroben mod2as benchmark. (SNIC)             |

| Table 57 Performance and energy to solution for the Euroben mod2f benchmark. (SNIC)              |

| Table 58 Performance and energy to solution for the Hydro benchmark. (SNIC)                      |

| Table 59 Performance and energy to solution for the Linpack benchmark. (SNIC)                    |

| Table 60 Performance and energy to solution for the STREAM copy benchmark. (SNIC)                |

| Table 61 Performance and energy to solution for the STREAM scale benchmark. (SNIC)               |

| Table 62 Performance and energy to solution for the STREAM sum benchmark. (SNIC)                 |

| Table 63 Performance and energy to solution for the STREAM triad benchmark. (SNIC)               |

| Table 64 Performance and energy to solution for the Euroben mod2am benchmark. (LRZ)              |

| Table 65 Performance and energy to solution for the Euroben mod2as benchmark. (LRZ)              |

| Table 66 Performance and energy to solution for the Euroben mod2f benchmark. (LRZ)               |

| Table 67 Performance and energy to solution for the Hydro benchmark. (LRZ)                       |

| Table 68 Performance and energy to solution for the Linpack benchmark. (LRZ)                     |

| Table 69 Performance and energy to solution for the STREAM copy benchmark. (LRZ)                 |

| Table 70 Performance and energy to solution for the STREAM scale benchmark. (LRZ)                |

| Table 71 Performance and energy to solution for the STREAM sum benchmark. (LRZ)                  |

| Table 72 Performance and energy to solution for the STREAM triad benchmark. (LRZ)                |

| Table 73 Performance for the STREAM copy benchmark on the AMD E-350 APU for 1 thread.            |

| (PSNC)                                                                                           |

| Table 75 Performance for the STREAM sum benchmark on the AMD E-350 APU for 1 thread.             |

| (PSNC)                                                                                           |

| Table 76 Performance for the STREAM triad benchmark on the AMD E-350 APU for 1 thread.           |

| (PSNC)                                                                                           |

| Table 77 Performance for the Euroben mod2am benchmark on the AMD E-350 APU. (PSNC) 131           |

| Table 78 Performance for the Euroben mod2as benchmark on the AMD E-350 APU. (PSNC) 131           |

| Table 80 Performance for the STREAM copy benchmark on the AMD E-350 APU using 2 threads.         |

| (PSNC)                                                                                           |

| Table 82 Performance for the STREAM sum benchmark on the AMD E-350 APU using 2 threads.          |

| (PSNC)                                                                                           |

| Table 83 Performance for the STREAM triad benchmark on the AMD E-350 APU using 2 threads.        |

| (PSNC)                                                                                           |

| Table 84 Performance and energy to solution for the Euroben mod2am benchmark on the AMD A8-      |

| 3870 APU. (PSNC)                                                                                 |

| Table 85 Performance for the Euroben mod2as benchmark on the AMD A8-3870 APU. (PSNC) 133         |

| Table 86 Performance of the Euroben mod2f benchmark on the AMD A8-3870 APU. (PSNC) 134           |

| Table 87 Performance and energy to solution of the Hydro benchmark on the AMD A8-3870 APU.       |

| (PSNC)                                                                                           |

| Table 88 Performance and energy to solution of the Linpack benchmark on the AMD A8-3870 APU.     |

| (PSNC)                                                                                           |

| Table 90 Performance and energy to solution for the Hydro benchmark on the AMD A10-5800k APU.    |

| (PSNC)                                                                                           |

| Table 91 Performance and energy to solution for the Hydro benchmark on the A10-5800k APU using   |

| the GPU. (PSNC)                                                                                  |

| Table 92 Performance and energy to solution for the Linpack benchmark on the AMD A10-5800k       |

| Table 97 Performance and energy to solution for the Linnack benchmark on the AMID ATILISMON      |

## **References and Applicable Documents**

[ACML] AMD Core Math Library, <a href="http://developer.amd.com/tools/cpu-">http://developer.amd.com/tools/cpu-</a>

development/amd-core-math-library-acml/

[Agarwal-1994] A High Performance Parallel Algorithm for 1-D FFT, Supercomputing

'94, Proceedings, p. 34-40, 14-18 Nov 1994

doi:10.1109/SUPERC.1994.344263,

http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=344263&isn

<u>umber=8021</u>

[AMD-2011] Practical Power Gating and Dynamic Voltage/Frequency Scaling,

S. Kosonocky, <a href="http://www.hotchips.org/wp-content/uploads/hc">http://www.hotchips.org/wp-content/uploads/hc</a> archives/hc23/HC23.17.1-

tutorial1/HC23.17.111.Practical PGandDV-Kosonocky-AMD.pdf

[AMD-Intel] The Mother of All CPU Charts 2005/2006, Nov 2005,

http://www.tomshardware.com/reviews/mother-cpu-charts-

2005,1175.html

[ATLAS] Automatically Tuned Linear Algebra Software (ATLAS),

http://www.netlib.org/atlas

[Belady-2007] In the Data Center, Power and Cooling Costs More Than the IT

Equipment It Supports, C. Belady. February 1, 2007, Electronics Cooling. <a href="http://www.electronics-cooling.com/2007/02/in-the-data-center-power-and-cooling-costs-more-than-the-it-equipment-it-supports">http://www.electronics-cooling.com/2007/02/in-the-data-center-power-and-cooling-costs-more-than-the-it-equipment-it-supports</a>

[BLAS] Basic Linear Algebra Subprograms, <a href="http://www.netlib.org/blas/">http://www.netlib.org/blas/</a>

[Brill-2008] Findings on Data Center Energy Consumption Growth May Already

Exceed EPA's Prediction Through 2010!, K. G. Brill, The Uptime Institute, 2008, <a href="http://uptimeinstitute.org/content/view/155/147">http://uptimeinstitute.org/content/view/155/147</a>

[Calxeda] http://www.calxeda.com

[Curley] Open Innovation 2.0 and 21st Century Industrial Research, M. Curley,

http://www.intel.com/content/dam/www/public/emea/eu/en/documents/

eric/day1-martin-curley.pdf

[Daily-2009] Weather supercomputer used to predict climate change is one of

Britain's worst polluters, Daily Mail, August 27, 2009,

http://www.dailymail.co.uk/sciencetech/article-1209430/Weather-supercomputer-used-predict-climate-change-Britains-worst-

polluters.html

[Dally-2008] Efficient Embedded Computing, W.J. Dally, J. Balfour, D. Black-

Shaffer, J. Chen, R. C. Harting, V. Parikh, J. Park, and D. Shef, IEEE

Computer, pp. 27-32, July, 2008

[DARPA-2008] ExaScale Computing Study: Technology Challenges in Achieving

Exascale Systems, DARPA, September 28, 2008,

http://users.ece.gatech.edu/mrichard/ExascaleComputingStudyReports/

exascale final report 100208.pdf

[Dhry] A synthetic computing benchmark program,

http://www.ct.se/dhrystone/index.html

[EPA-2007] Report to Congress on Server and Data Center Energy Efficiency, U.S.

Environmental Protection Agency, Energy Star Program. August 2,

2007, Public Law 109-431,

http://www.energystar.gov/ia/partners/prod\_development/downloads/E

PA Datacenter Report Congress Final1.pdf

[ESFRI-2006] European Roadmap for Research Infrastructures, Report 2006, The

European Strategy Forum for Research Infrastructures (ESFRI), ftp://ftp.cordis.europa.eu/pub/esfri/docs/esfri-roadmap-report-

26092006 en.pdf

[ESSL] Engineering Scientific Subroutine Library,

http://publib.boulder.ibm.com/epubs/pdf/a2322683.pdf

[EuroBen] EuroBen Benchmark Programs,

http://www.hpcresearch.nl/euroben/programs.php

[Eurostat-2013] Electricity Prices for Industrial Consumers, Eurostat,

http://epp.eurostat.ec.europa.eu/tgm/table.do?tab=table&plugin=0&lan

guage=en&pcode=ten00114

[Feng-2005] A Power Aware Run-Time System for High Performance Computing,

C. Hsu and W. Feng, <a href="http://public.lanl.gov/radiant/pubs/sss/sc2005.pdf">http://public.lanl.gov/radiant/pubs/sss/sc2005.pdf</a>

[FFTPACK] FFTPACK, http://www.netlib.org/fftpack/

[FFTW] FFTW, <a href="http://www.fftw.org/">http://www.fftw.org/</a>

[Frigo-1999] Cache Oblivious Algorithms, M. Frigo, C. E. Leiserson, H. Prokop, and

S. Ramachandran, in 40<sup>th</sup> Annual Symposium on Foundations of Computer Science, pp. 285-298, NewYork, USA, October 1999

[FZJ] SIONlib: Scalable I/O Library for Parallel Access to Task-Local Files,

http://www.fz-

juelich.de/ias/jsc/EN/Expertise/Support/Software/SIONlib/ node.html

[GF-2008] Towards Ultra-High Resolution Models of Climate and Weather, M.

Wehner, L. Oliker, J. Shalf,

http://crd-legacy.lbl.gov/~oliker/papers/IJHPCA08 Wehner.pdf

[Godunov] A Difference Scheme for Numerical Solution of Discontinuous

Solution of Hydrodynamic Equations, Godunov, S. K. (1959), Math.

Sbornik, 47, 271–306, translated US Joint Publ. Res. Service, JPRS 7226, 1969.

[Green500-2007] www.green500.org/lists/green200711

[Green500-2012] <a href="http://www.green500.org/">http://www.green500.org/</a>

[HPCC] HPC Challenge Benchmarks, <a href="http://icl.cs.utk.edu/hpcc/">http://icl.cs.utk.edu/hpcc/</a>

[Horowitz-2009] Scaling Power and the Future of CMOS, M Horowitz, 2009,

https://www.e3s-center.org/events/09/symposium/index.htm

[Hybrid] Hybrid MPI-OpenMP Programming, P.-Fr. Lavallée and Ph. Wautelet,

http://www.idris.fr/data/cours/hybride/choix\_doc.html

[Hydro] Hydro Benchmark, <a href="https://github.com/HydroBench/Hydro.git">https://github.com/HydroBench/Hydro.git</a>

[IBM-2009] High-Temperature Cooling: Towards a Zero-Emission Datacenter,

I. Meijer, T. Brunschwiler, S. Paredes and B. Michel, IBM, 1<sup>st</sup>

European Workshop on HPC Centre Infrastructures,

http://www.cscs.ch/events/event\_list/event\_detail/index.html?tx\_semin

ars pi1%5BshowUid%5D=7

[IBM-2010] Harnessing the Adaptive Energy Management Features of the

POWER7 chip, M. Floyd, B. Brock, M. Ware, K. Rajamani, A. Drake,

C. Lefurgy, and L. Pesantez, IBM, HotChips, August, 2010,

http://www.hotchips.org/uploads/archive22/HC22.23.130-1-Floyd-

IBM-POWER7-Power-Management.pdf

[IBM-2011] IBM Deep Computing XXL/SciComp Conference, Paris, May 11 2011,

L. Brochard <a href="http://spscicomp.org/wordpress/wp-">http://spscicomp.org/wordpress/wp-</a>

content/uploads/2011/05/brochard-Luigi Perf-and-Power-Trade-off.pdf

[Inefficient-2007] An In-Efficient Truth, Global Action Plan, Report, December 2007,

http://www.greenict.org.uk/reports-library/an-inefficient-truth

[Intel-2006] Energy per Instruction Trends in Intel® Microprocessors,

E. Grochowski, M. Annavaram, Technology@Intel Magazine, March 2006, http://support.intel.co.jp/pressroom/kits/core2duo/pdf/epi-trends-

final2.pdf

[Intel-2007] An 80-tile 1.28 Tflops Network-on-Chip in 65 nm CMOS, S. Vangal, J.

Howard, G. Ruhl, S.Dighe, H. Wilson, J. Tschanz, D. Finan, P. Iyer, A. Singh, T. Jacob, S. Jain, S. Venkataraman, Y. Hoskote, N. Borkar. February 11-15, 2007, pp. 98 – 99, IEEE Solid-States Circuits

Conference, San Francisco,

http://ieeexplore.ieee.org/xpl/freeabs all.jsp?arnumber=4242283

[Intel-2011] Power management architecture of the 2nd generation Intel® Core<sup>TM</sup>

microarchitecture, formerly codenamed Sandy Bridge, E. Rotem, A.

Naveh, D. Rajwan, A. Ananthakrishnan, E. Weissmann,

http://www.hotchips.org/wp-

content/uploads/hc\_archives/hc23/HC23.19.9-Desktop-

CPUs/HC23.19.921.SandyBridge Power 10-Rotem-Intel.pdf

[Intel-2012] Intel's Near Threshold Voltage Computing and Applications, D.

Kanter, September 18, 2012. http://www.realworldtech.com/near-

threshold-voltage/

[Intel-clock] Intel Processor Clock Speed (MHz),

http://smoothspan.files.wordpress.com/2007/09/clockspeeds.jpg

[IOR] IOR: I/O Performance Benchmark,

https://asc.llnl.gov/sequoia/benchmarks/IOR\_summary\_v1.0.pdf

[Jovanovic-2012] FPGA Accelerator for Floating-Point Marix Multiplication, Computers

& Digital techniques, vol. 6, no. 4, pp 249 – 256, July 2012,

http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber

=6337379

[Koomey-2009a] Assessing Trends over Time in Performance, Costs, and Energy Use

for Servers, J. G. Koomey, C. Belady, M. Patterson, A. Santos, K-D.

Lange. August 17, 2009, Intel,

http://www3.intel.com/assets/pdf/general/servertrendsreleasecomplete-

v25.pdf

[Koomey-2009b] Assessing in the Trends in the Electrical Efficiency of Computation

over Time, Intel, August 17, 2009. J.G. Koomey, S. Berard, M.

Sanchez, H. Wong.,

http://download.intel.com/pressroom/pdf/computertrendsrelease.pdf

[LINPACK] HPL - A Portable Implementation of the High-Performance Linpack

Benchmark for Distributed-Memory Computers. September, 2008. A.

Petitet, R. C. Whaley, J. Dongarra, A. Cleary.

http://www.netlib.org/benchmark/hpl/

[Marvell] http://www.marvell.com

[Mills-2009] SuperComputers: Super-Polluters? Data Center Journal vol. 7, May, p.

16–18 (2008) Evan Mills, William Tschudi, John Shalf, and Horst

Simon

[MKL] Intel Math Kernel Library, http://software.intel.com/en-us/intel-mkl

[Moore-1965] Cramming More Components onto Integrated Circuits, Electronics,

Vol. 38, no 8. April, 1965. G. E. Moore,

ftp://download.intel.com/research/silicon/moorespaper.pdf

[Mora-2010] Private Communication.

[Mora-2012] Understanding Bulldozer architecture through Linpack benchmark, J.

Mora, ISC 2012,

http://www.hpcadvisorycouncil.com/events/2012/European-

Workshop/Presentations/12 AMD.pdf

[MPI] MPI - The Message Passing Interface Standard,

http://www.mcs.anl.gov/research/projects/mpi/

[MPrime] Mersenne Prime, http://en.wikipedia.org/wiki/Prime95

[NEST] Neural Simulation technology, http://www.nest-

initiative.org/index.php/index.php

[NUMAscale] <a href="http://www.numascale.com">http://www.numascale.com</a>

[NVIDIA-2010] CUDA Accelerated Linpack on Clusters, E. Phillips, NVIDIA, GPU

Technology Conference, September, 2010,

http://www.nvidia.com/content/GTC-2010/pdfs/2057 GTC2010.pdf

(Also presented at SC10)

[NYT-2012a] Power, Pollution and the Internet, New York Times, J. Glanz, 2012-09-

22, http://www.nytimes.com/2012/09/23/technology/data-centers-

waste-vast-amounts-of-energy-belying-industry-

image.html?pagewanted=all& r=0

[NYT-2012b] Data Barns in a Farm Town, Gobbling Power and Flexing Muscle,

New York Times, J. Glanz, 2012-09-23,

http://www.nytimes.com/2012/09/24/technology/data-centers-in-rural-

washington-state-gobble-power.html?pagewanted=all

[OpenMP] OpenMP - Open Multi-Processing specifications,

http://openmp.org/wp/openmp-specifications/

[Pollack-1999] New Microarchitecture Challenges in the Coming Generations of

CMOS Process Technologies, Pollack, F., Proceedings of the 32nd Annual IEEE/ACM International Symposium on Microarchitecture,

Haifa, Israel.

[QCD-2013] Computational Challenges in QCD Thermodynamics, C. DeTar and F.

Karsch, February 6, 2013,

http://www.usqcd.org/documents/13thermo.pdf

[QUDA] QUDA: A Library for QCD on GPUs, http://lattice.github.com/quda/

[RAMSES] The RAMSES Code,

http://irfu.cea.fr/Sap/en/Phocea/Vie des labos/Ast/ast visu.php?id ast

=904

[Rose] Approximate Riemann solvers, parameter vectors and difference

schemes, P. L. Rose, (1981), J. Comput. Phys. 43 (2): 357–372, Pibooda 1081 ICoPh, 43, 357P, doi:10.1016/0021.0001(81)00128.5

Bibcode 1981JCoPh..43..357R, doi:10.1016/0021-9991(81)90128-5

[RPE] Robinhood Policy Engine, <a href="http://sourceforge.net/apps/trac/robinhood">http://sourceforge.net/apps/trac/robinhood</a>

[SeaMicro] http;//www.seamicro.com

[SGIMAID] http://www.sgi.com/products/storage/maid/

[Shalf-2007] About Memory Bandwidth, J. Shalf, June 13, 2007,

http://www.csm.ornl.gov/workshops/SOS11/presentations/j shalf.pdf

[Shalf-2010] Exascale Computing Technology Challenges, John Shalf, National

Energy Research Supercomputing Center, Lawrence Berkeley National Laboratory ScicomP / SP-XXL 16, San Francisco, May 12, 2010, <a href="http://www.spscicomp.org/ScicomP16/presentations/ExascaleChalleng">http://www.spscicomp.org/ScicomP16/presentations/ExascaleChalleng</a>

es.pdf

[SorTech] http://www.sortech.de/en/

[SPRASEPACK] Sparsepack,

http://people.sc.fsu.edu/~jburkardt/f\_src/sparsepak/sparsepak.html

[STREAM-1] The STREAM Benchmark: Computer Memory Bandwidth, J.

McCalpin, http://www.streambench.org/

[Strumpen-2004] Stream Algorithms and Architecture, V. Strumpen, H. Hoffman and A.

Agarwal, Journal of Instruction-Level Parallelism, vol. 6, September

2004 http://www.jilp.org/vol6/v6paper8.pdf

[Supermicro-2008] Private Communication.

[TI-2012] Multicore DSP+ARM KeyStone II System-on-Chip (SoC), November

2012, http://www.ti.com/lit/ds/symlink/66ak2h12.pdf

[Ung-2010] The History of a Dream: How the Ultimate PC Has Evolved In 15

Years, 2010, G. M. Ung and A. Castle,

http://www.maximumpc.com/article/home/history\_dream\_how\_ultimat

e pc has evolved 15 years

[UPC-1] UPC: Distributed Shared Memory Programming, Book of Wiley Inter-

Science (2005), W. Carlson et. al.

[UPC-2] Berkeley UPC, <a href="http://upc.lbl.gov">http://upc.lbl.gov</a>

[Wyoming-2010] NCAR's dirty little secret, January 16, 2010, Anthony Watts,

http://wattsupwiththat.com/2010/01/16/ncars-dirty-little-secret/

[Wyoming-2012] Wyoming experiences that "giant sucking sound" as new coal fired

climate supercomputer is turned on, October 16, 2012 by Anthony Watts, <a href="http://wattsupwiththat.com/2012/10/16/wyoming-experiences-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-sound-as-new-coal-fired-climate-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-sucking-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-super-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-supercomputer-is-that-giant-sup

turned-on/

[Xilinx-2012] Latest FPGAs Show Big Gains in Floating Point Performance, April

16, 2012 D. Strenski, C. Kulkarni, J. Cappello, and P. Sundararajan,

http://www.hpcwire.com/hpcwire/2012-04-

16/latest fpgas show big gains in floating point performance.html

[Xyratex] http://www.xyratex.com

## **List of Acronyms and Abbreviations**

ACM Association for Computing Machinery

ACML AMD Core Math Library

ACS Adsorption Chiller System

AMD Advanced Micro Devices

API Application Programming Interface

APP Accelerated Parallel Processing

ARM Formerly known as Advanced RISC Machine

ASIC Application-Specific Integrated Circuit

ATI Array Technologies Incorporated (AMD)

ATLAS Automatically Tuned Linear Algebra Software

BAdW Bayerischen Akademie der Wissenschaften (Germany)

BG Blue Gene

BLAS Basic Linear Algebra Subprograms

BSC Barcelona Supercomputing Center (Spain)

CaSToRC Computation-based Science and Technology Research Centre

ccNUMA cache coherent NUMA

CEA Commissariat à l'Energie Atomique (represented in PRACE by GENCI,

France)

CINECA Consorzio Interuniversitario, the largest Italian computing centre (Italy)

CINES Centre Informatique National de l'Enseignement Supérieur (represented

in PRACE by GENCI, France)

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

CRAC Computer Room Air-Conditioning

CS ClusterStor

CSC Finnish IT Centre for Science (Finland)

CSCS The Swiss National Supercomputing Centre (represented in PRACE by

ETHZ, Switzerland)

CUDA Compute Unified Device Architecture (NVIDIA)

DARPA Defense Advanced Research Projects Agency

DAS Direct Attached Storage

DDR Double Data Rate

DGEMM Double precision General Matrix Multiply

DIMM Dual Inline Memory Module

DMA Direct Memory Access

DMF Data Migration Facility (SGI)

DP Double Precision, usually 64-bit floating point numbers

DRAM Dynamic RAM

DSP Digital Signal Processor EC European Community

EDMA Enhanced DMA

EESI European Exascale Software Initiative

EP Efficient Performance, e.g., Nehalem-EP (Intel) EPA Environmental Protection Agency (United States)

EPCC Edinburg Parallel Computing Centre (represented in PRACE by

EPSRC, United Kingdom)

EPSRC The Engineering and Physical Sciences Research Council (United

Kingdom)

eQPACE extended QPACE, name of the FZJ WP8 prototype

ESFRI European Strategy Forum on Research Infrastructures; created

roadmap for pan-European Research Infrastructure.

ESM Embedded Server Module

ETHZ Eidgenössische Technische Hochschule Zuerich, ETH Zurich

(Switzerland)

EX Expandable, e.g., Nehalem-EX (Intel)

FC Fiber Channel

FDR Fourteen Data Rate

FFT Fast Fourier Transform

FFTW Fastest Fourier Transform in the West

FHPCA FPGA HPC Alliance FMA Fused Multiply Add FP Floating-Point

FPGA Field Programmable Gate Array

FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte Gbps Giga (=  $10^9$ ) bits per second, also Gbit/s, Gb/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GCS Gauss Centre for Supercomputing (Germany)

GDDR Graphic Double Data Rate memory

GEDI Generic Diskless Installer

GEM General Enclosure Management

GENCI Grand Equipement National de Calcul Intensif (France)

GF/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second. also GFlops/s

GHz Giga (= 10<sup>9</sup>) Hertz, frequency =10<sup>9</sup> periods or clock cycles per second

GbE Gigabit Ethernet, also GigE GNU GNU's not Unix, a free OS

GPFS General Parallel File System (IBM)

GPGPU General Purpose GPU GPU Graphic Processing Unit

HBA Host Bus Adapter

HCA Host Channel Adapter

HDD Hard Disk Drive HE High Efficiency

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hewlett-Packard

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPCC HPC Challenge benchmark, http://icl.cs.utk.edu/hpcc/

HPL High Performance LINPACK

HSM Hierarchical Storage Management

HT HyperTransport channel (AMD)

HTX HyperTransport Expansion

IB InfiniBand IBA IB Architecture

IBM Formerly known as International Business Machines

ICC Intel C Compiler IDMA Internal DMA

IDRIS Institut du Développement et des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International Exascale Project

I/O Input/Output

IOR Interleaved Or Random

IP Internet Protocol

IPC Inter-Process Communication

IPMI Intelligent Platform Management Interface

ISC International Supercomputing Conference; European equivalent to the

US based SC0x conference. Held annually in Germany.

JBOD Just a Bunch of Disks

JSC Jülich Supercomputing Centre (FZJ, Germany) kB Kilo (=  $2^{10} \sim 10^{3}$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC,

Sweden)

kW Kilo Watt

LINPACK Software library for Linear Algebra

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LMT Lustre Monitoring Tool

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

MAC Media Access Control

MAID Massive Array of Idle Disks

MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MDT MetaData Target

MFC Memory Flow Controller

MF/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second. also MFlops/s

MHz Mega (= 10<sup>6</sup>) Hertz, frequency =10<sup>6</sup> periods or clock cycles per second MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC

processor architecture developed by MIPS Technology

MKL Math Kernel Library (Intel)

Mop/s Mega (= 10<sup>6</sup>) operations per second (usually integer or logic operations)

MPI Message Passing Interface

MPICH MPI CHameleon

MPP Massively Parallel Processing (or Processor)

uSD Micro SD

MVAPICH MPICH over Verbs API

MW Mega Watt

NAS Network-Attached Storage

NCF Netherlands Computing Facilities (Netherlands)

NCPUM NumaConnect Pick-Up Module

NFS Network File System NI National Instruments

NIC Network Interface Controller

NSD Network Shared Disk (IBM/GPFS)

NUMA Non-Uniform Memory Access or Architecture

OpenCL Open Computing Language

OpenMP Open Multi-Processing

OpenMPI Open MPI

OS Operating System

OSS Object Storage Server

OST Object Storage Target

PCIe Peripheral Component Interconnect express, also PCI-Express

PDU Power Distribution Unit

POSIX Portable OS Interface for Unix

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

QCD Quantum Chromodynamics

QDR Quad Data Rate

QFED OpenFabrics Enterprise Distribution

QPACE QCD Parallel Computing on the Cell

RAID Redundant Array of Inexpensive Disks

RAM Random Access Memory RDMA Remote Data Memory Access

RI Research Infrastructure

RISC Reduce Instruction Set Computer RNG Random Number Generator

RPM Revolution per Minute SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SD Secure Digital

SDK Software Development Kit SFP Small Form-factor Pluggable

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SIMD Single Instruction Multiple Data

SLURM Simple Linux Utility for Resource Management

SoC System on Chip

SM Streaming Multiprocessor, also Subnet Manager

SMP Symmetric MultiProcessing

SNIC Swedish National Infrastructure for Computing (Sweden)

SP Single Precision, usually 32-bit floating point numbers

SRAM Static RAM

SRIO Serial Rapid I/O

SSD Solid State Disk or Drive

SSU Scalable Storage Unit (Xyratex)

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TCO Total Cost of Ownership. Includes the costs (personnel, power, cooling,

maintenance, ...) in addition to the purchase cost of a system.

TCP Transmission Control Protocol

TDP Thermal Design Power

TF/s Tera (= 1012) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TFlops/s

TI Texas Instruments

UiO Universitetet i Oslo (University of Oslo, Norway)

UPC Unified Parallel C

USB Universal Serial Bus

UV Ultra Violet (SGI)

UVA Unified Virtual Addressing (NVIDIA)

VTK Visualization Tool-Kit VTL Virtual Tape Library

W Watt

## **Executive Summary**

The objective of Work Package 9 task 3 is to assess and make recommendations to the PRACE RI for joint developments with industrial partners to develop highly energy efficient HPC components and systems, as well as power and cooling technologies. WP9 has carried out this task through evaluation of a number of prototypes targeting novel approaches to HPC server and system design with many prototypes having some degree of direct industry involvement or support.

Prototype efforts assessed the use of FPGAs for function acceleration, the use of CPUs for the mobile market and with a TDP about two orders of magnitude less than typical x86 CPUs for the HPC market, DSPs common for embedded systems and with a TDP about one order of magnitude less than x86 CPUs, the emerging heterogeneous CPUs integrating x86 and GPU cores, and traditional GPUs with a novel direct communication between GPUs via Infiniband between nodes. Two prototypes focused on novel approaches to scalability of I/O systems in support of Exascale systems and their energy efficiency. Technologies assessed included integration of I/O nodes into the MPP or cluster interconnect fabric, the use of flash technology, scalable disk systems and virtual tape libraries based on disk systems with spun down idle disks. Data management in file systems, in particular the management of large numbers of small files, was also addressed with the I/O-prototypes. One prototype evaluation assessed the issues and benefits of integrated cooling solutions for hot water cooling.

The findings of the evaluations of prototypes looking at HPC server architectures is that 1) an optimized FPGA implementation of matrix-multiplication can offer a 5-10 times higher energy efficiency than an x86 software solution, 2) an optimized implementation of matrix multiplication on the DSP can yield about half the energy efficiency gain of an FPGA implementation, 3) the first and second generation x86+GPU CPUs are not competitive in regards to energy efficiency even with standard x86 CPUs for the functions investigated, and 4) that good scalability can be achieved for clusters based on nodes using mobile CPUs though the floating-point capabilities of the current generation mobile CPUs is insufficient to be competitive in terms of energy efficiency.

Software optimization can make an order of magnitude or more difference in efficiency and energy efficiency for kernels frequently used for HPC benchmarking even for HPC established architectures, such as the x86. Further efforts are required to better understand the energy advantages of novel approaches to HPC server designs.

The evaluation of the I/O prototypes largely gave the expected outcomes, but did expose the dependence on good software implementations and the efficiency and scalability issues related to large file systems in which a large fraction of the files are small.

The integrated cooling with hot water prototype demonstrated that the technology is viable, but that further study is necessary to assess the economic benefits, and that those likely depend on the local situation. That could however change if technology would become available to convert heat into electricity in a cost competitive way.

#### 1 Introduction

The main objective of PRACE is to assure the availability of Leadership Class systems and associated software and services for the Computation and Data Treatment needs of European researchers as outlined in the 2006 ESFRI report [ESFRI-2006] to strengthen European competitiveness for the benefit of the society. The particular aspect of this broad objective addressed by Work Package 9 Task 3 in the First PRACE Implementation Phase project (PRACE-1IP) is energy efficiency of systems and their operation.

Large computing systems have become large consumers of electricity for operations and cooling to the point that the electricity demands may be the limiting factor for the size of the systems that can be installed, dominate the life-time cost of systems and their operation, or what is socially and environmentally acceptable. For this reason, in particular in regards to reaching the next major performance goal of large scale systems, Exascale systems, i.e., systems with a peak performance of 10<sup>18</sup> floating point operations per second and beyond, business as usual is generally not viewed as feasible. A business-as-usual approach has been estimated to lead to power requirements of about 200 MW or more for such a system. Innovations beyond the normal are necessary in every aspect: device technology, architecture, software, algorithms, cooling solutions, and operations. For cost and environmental reasons, solutions that enable energy recovery are also of great importance.