## SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

INFRA-2007-2.2.2.1 - Preparatory phase for 'Computer and Data Treatment' research infrastructures in the 2006 ESFRI Roadmap

## **PRACE**

# Partnership for Advanced Computing in Europe

**Grant Agreement Number: RI-211528**

# D6.5 Report on Porting and Optimisation of Applications

# Draft

Version: 1.0

Author(s): Sebastian von Alfthan, CSC

Giorgos Goumas, GRNET Olli-Pekka Lehto, CSC Pekka Manninen, CSC Mohammad Jowkar, BSC Harald Klimach, HLRS

Date: 26.10.2009

# **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-211          | 528                                  |

|---------------|---------------------------------|--------------------------------------|

|               | <b>Project Title: Partnersh</b> | nip for Advanced Computing in Europe |

|               | Project Web Site: http://       | ://www.prace-project.eu              |

|               | <b>Deliverable ID:</b> D6.5     |                                      |

|               | Deliverable Nature: Rep         | port                                 |

|               | <b>Deliverable Level:</b>       | Contractual Date of Delivery:        |

|               | PU                              | 31 / October / 2009                  |

|               |                                 | Actual Date of Delivery:             |

|               |                                 | 30 / October / 2009                  |

|               | EC Project Officer: Ma          | ria Ramalho-Natario                  |

# **Document Control Sheet**

|               | Title: Report on Porting a      | and Optimisation of Applications |

|---------------|---------------------------------|----------------------------------|

| Document      |                                 |                                  |

|               | <b>ID:</b> D6.5                 |                                  |

|               | Version: 1.0                    | Status: Final                    |

|               | Available at: http://www        | v.prace-project.eu               |

|               | <b>Software Tool:</b> Microsoft | Word 2007                        |

|               | File(s): D6.5.doc               |                                  |

|               | Written by:                     | Sebastian von Alfthan (CSC)      |

| Authorship    |                                 | Giorgos Goumas (GRNET)           |

| 1 tathor ship |                                 | Olli-Pekka Lehto (CSC)           |

|               |                                 | Pekka Manninen (CSC)             |

|               |                                 | Mohammad Jowkar (BSC)            |

|               |                                 | Harald Klimach (HLRS)            |

| Contributors: | Raúl de la Cruz (BSC)       |

|---------------|-----------------------------|

|               | Bertrand Cirou (CINES)      |

|               | Mauricio Araya Polo (BSC)   |

|               | Andrew Sunderland (STFC)    |

|               | Albert Farres (BSC)         |

|               | Xavier Saez (BSC)           |

|               | Orlando Riviera (LRZ)       |

|               | Jussi Enkovaara (CSC)       |

|               | Xu Guo (EPCC)               |

|               | Joachim Hein (EPCC)         |

|               | Martin Polak (GUP)          |

|               | Paschalis Korosoglu (GRNET) |

|               | John Donners (SARA)         |

|               | Fernando Nogueira (UC-LCA)  |

|               | Lukas Arnold (FZJ)          |

|               | Maciej Cytowski (PSNC/ICM)  |

|               | Carlo Cavazzoni (CINECA)    |

| Reviewed by:  | Florian Berberich (FZJ)     |

|               | Colin Glass (HLRS)          |

| Approved by:  | Technical Board             |

|               |                             |

# **Document Status Sheet**

| Version | Date              | Status        | Comments                                                                                   |

|---------|-------------------|---------------|--------------------------------------------------------------------------------------------|

| 0.1     | 02/February/2009  | Draft         | Initial version                                                                            |

| 0.2     | 15/September/2009 | Draft         | Complete document for internal WP6 internal review                                         |

| 0.3     | 04/October/2009   | Draft         | Integration of comments<br>from WP6 review, made<br>available to PRACE<br>internal review. |

| 1.0     | 26/October/2009   | Final version |                                                                                            |

## **Document Keywords and Abstract**

| Keywords: | PRACE, HPC, Porting, Optimisation, PABS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abstract: | This document reports the optimisation and porting of applications in the PRACE application benchmark suite (PABS) to the PRACE-WP7 prototype machines. Porting encompasses not only compiling functioning programs on target platforms, but also methods aimed at extracting maximum performance through informed choice of compilers, external libraries and platform parameters. Optimisation techniques are techniques for improving the performance of applications on a node-level. This includes techniques aimed at optimising usage of memory-hierarchy, computational parts of processors and algorithmic issues.  In this deliverable, we present porting and optimisation reports for each application. We also discuss the best practices extracted from the application reports, from knowledge gathered at the prototype sites and an analysis of synthetic kernels. |

## **Copyright notices**

© 2009 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-211528 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

# **Table of Contents**

| Pro | oject : | and Deliverable Information Sheet                                    | i    |

|-----|---------|----------------------------------------------------------------------|------|

| Do  | cume    | ent Control Sheet                                                    | i    |

| Do  | cume    | ent Status Sheet                                                     | ii   |

| Do  | cume    | ent Keywords and Abstract                                            | iii  |

| Ta  | ble of  | f Contents                                                           | iv   |

| Lis | t of F  | Figures                                                              | viii |

| Lis | st of T | Tables                                                               | ix   |

| Re  | feren   | ces and Applicable Documents                                         | xi   |

|     |         | Acronyms and Abbreviations                                           |      |

|     |         | ve Summary                                                           |      |

| 1   |         | roduction                                                            |      |

| 2   |         | thodology                                                            |      |

| 3   |         | rting                                                                |      |

|     | 3.1     | Hardware                                                             |      |

|     | 3.2     | Software environment                                                 |      |

|     |         | 3.2.1 Dense Systems                                                  |      |

|     |         | 3.2.2 Sparse Systems                                                 |      |

|     |         | 3.2.3 Fourier Transforms                                             |      |

|     |         | 3.2.4 Intrinsic Mathematical Operations                              | 7    |

|     |         | 3.2.5 Library support                                                | 7    |

|     | 3.3     | Compilers                                                            | 9    |

|     |         | 3.3.1 Optimisation flags                                             |      |

|     |         | 3.3.2 Iterative compilation                                          |      |

|     | 3.4     | Porting to Cray XT5 - Louhi                                          | 17   |

|     | 3.5     | Porting to IBM Blue Gene/P - Jugene                                  | 21   |

|     | 3.6     | Porting to IBM Power6 cluster - Huygens                              | 24   |

|     | 3.7     | Porting to NEC SX-9 / Nehalem cluster - Baku                         | 27   |

|     | 3.8     | Porting to Sun/Bull Nehalem cluster - JuRoPA                         | 27   |

|     | 3.9     | Porting to IBM Cell cluster - MariCel                                | 28   |

| 4   | Opt     | timisation                                                           | 29   |

|     | 4.1     | Memory hierarchy optimisation techniques                             | 30   |

|     |         | 4.1.1 <i>Blocking</i>                                                | 30   |

|     |         | 4.1.2 Loop permutation                                               | 31   |

|     |         | 4.1.3 Loop fusion                                                    | 31   |

|     |         | 4.1.4 Loop distribution                                              | 32   |

|     |         | 4.1.5 Prefetching                                                    | 32   |

|     |         | 4.1.6 Overlap of memory transfer and computations (double-buffering) |      |

|     |         | 4.1.7 Cache-line issues                                              |      |

|   | 4.2 | Computational optimisation techniques                          | 34 |

|---|-----|----------------------------------------------------------------|----|

|   |     | 4.2.1 SIMD instructions                                        |    |

|   |     | 4.2.2 Better instruction scheduling                            |    |

|   |     | 4.2.3 Loop unrolling                                           |    |

|   |     | 4.2.4 Software pipelining                                      |    |

|   |     | 4.2.5 Strength reduction                                       |    |

|   |     | 4.2.6 Inlining                                                 |    |

|   | 4.3 | Algorithmic optimisation                                       |    |

|   |     | 4.3.1 Precision issues                                         |    |

|   |     | 4.3.2 Data structures                                          |    |

|   | 4.4 | Optimisations for threaded applications on multicore platforms |    |

|   |     | 4.4.1 NUMA-aware data placement                                | 38 |

|   |     | 4.4.2 Shared Caches in multicore processors                    |    |

|   |     | 4.4.3 False-sharing and variable placement                     | 39 |

|   | 4.5 | Optimisation for NEC SX-9 vector processors                    | 40 |

|   | 4.6 | Optimisation for Cell processors                               | 41 |

|   |     | 4.6.1 Power Processor Element                                  |    |

|   |     | 4.6.2 Synergistic Processor Elements                           | 42 |

|   |     | 4.6.3 Inter-processor communication                            |    |

|   |     | 4.6.4 Multi-Buffering                                          | 44 |

|   |     | 4.6.5 Levels of Parallelism                                    | 44 |

|   |     | 4.6.6 PPE and SPE Workloads                                    | 45 |

|   |     | 4.6.7 Translation Look-Aside Buffer (TLB)                      |    |

|   |     | 4.6.8 Summary                                                  | 45 |

| 5 | Apı | plication reports                                              | 46 |

|   |     | Alya                                                           |    |

|   |     | 5.1.1 Application description                                  | 46 |

|   |     | 5.1.2 <i>Porting</i>                                           |    |

|   |     | 5.1.3 Optimisation techniques                                  |    |

|   |     | 5.1.4 Results of optimisation effort                           |    |

|   |     | 5.1.5 Conclusions                                              |    |

|   | 5.2 | AVBP                                                           |    |

|   |     | 5.2.1 Application description                                  |    |

|   |     | 5.2.2 Porting                                                  |    |

|   |     | 5.2.3 Optimisation techniques                                  |    |

|   |     | 5.2.4 Results of optimisation effort                           |    |

|   | 5.3 | BSIT                                                           |    |

|   |     | 5.3.1 <i>Porting</i>                                           |    |

|   |     | 5.3.2 Optimisation techniques                                  |    |

|   |     | 5.3.3 Results of optimisation effort                           |    |

|   |     |                                                                |    |

|      | 5.3.4 Cor        | nclusions                      | 53         |

|------|------------------|--------------------------------|------------|

| 5.4  | Code_Sa          | iturne                         | 53         |

|      | 5.4.1 <i>App</i> | olication description          | 53         |

|      | 5.4.2 <i>Por</i> | ting                           | 55         |

|      | 5.4.3 <i>Opt</i> | timisation techniques          | 56         |

|      | 5.4.4 <i>Cor</i> | nclusions                      | 60         |

| 5.5  | CP2K             |                                | 61         |

|      | 5.5.1 <i>App</i> | olication description          | 61         |

|      | 5.5.2 Por        | ting                           | 61         |

|      | 5.5.3 <i>Opt</i> | timisation techniques          | 62         |

|      | 5.5.4 Res        | ults of optimisation effort    | 63         |

|      | 5.5.5 Cor        | nclusions                      | 63         |

| 5.6  | CPMD             |                                | 63         |

|      | 5.6.1 <i>Por</i> | ting                           | 63         |

|      | 5.6.2 <i>Opt</i> | timisation                     | 65         |

|      | 5.6.3 Cor        | nclusions                      | 65         |

| 5.7  | EUTERI           | PE                             | 65         |

|      | 5.7.1 App        | olication description          | 65         |

|      | 5.7.2 Por        | ting                           | 66         |

|      | 5.7.3 Opt        | timisation techniques          | 67         |

| 5.8  | Gadget           |                                | 67         |

|      | 5.8.1 <i>App</i> | olication description          | 68         |

|      | 5.8.2 <i>Por</i> | ting                           | 68         |

|      | 5.8.3 Oth        | er optimisation techniques     | 71         |

|      | 5.8.4 Cor        | nclusions                      | 72         |

| 5.9  | GPAW             |                                | 72         |

|      | 5.9.1 <i>App</i> | olication description          | 72         |

|      | 5.9.2 <i>Por</i> | ting                           | 73         |

|      | 5.9.3 <i>Opt</i> | timisation techniques          | 75         |

|      | 5.9.4 <i>Cor</i> | nclusions                      | 75         |

| 5.10 | Gromacs          | s                              | 75         |

|      | 5.10.1           | Application description        | 75         |

|      | 5.10.2           | Porting                        | 76         |

|      | 5.10.3           | Optimisation techniques        | 77         |

|      | 5.10.4           | Conclusions                    | 77         |

| 5.11 | HELIUN           | И                              | 77         |

|      | 5.11.1           | Application description        | 77         |

|      | 5.11.2           | Porting                        | 77         |

|      | 5.11.3           | Optimisation techniques        | <i>7</i> 9 |

|      | 5.11.4           | Results of optimisation effort | 85         |

|      | 5.11.5           | Other optimisation techniques  | 87         |

| 5       | 5.11.6  | Conclusions                    | 88    |

|---------|---------|--------------------------------|-------|

|         |         |                                |       |

|         | 5.12.1  | Application description        |       |

| _       | 5.12.2  | Testcases                      |       |

|         | 5.12.3  | Porting                        |       |

| 5       | 5.12.4  | Optimisation                   |       |

| 5       | 5.12.5  | Conclusions                    |       |

| 5.13 N  | NEMO    |                                | 97    |

| 5       | 5.13.1  | Application description        | 97    |

| 5       | 5.13.2  | Porting                        | 97    |

| 5       | 5.13.3  | Results of optimisation effort | 98    |

| 5       | 5.13.4  | Conclusions                    | 99    |

| 5.14 N  | NS3D    |                                | 99    |

| 5       | 5.14.1  | Application description        | 99    |

| 5       | 5.14.2  | Porting                        | 100   |

| 5       | 5.14.3  | Optimisation techniques        | 101   |

| 5       | 5.14.4  | Results of optimisation effort | 105   |

| 5       | 5.14.5  | Other optimisation techniques  | 105   |

| 5       | 5.14.6  | Conclusions                    | 106   |

| 5.15 (  | Octopus |                                | . 107 |

| 5       | 5.15.1  | Application description        | 107   |

| 5       | 5.15.2  | Optimisation techniques        | 108   |

| 5       | 5.15.3  | Conclusions                    | 108   |

| 5.16 I  | PEPC    |                                | . 109 |

| 5       | 5.16.1  | Application description        | 109   |

| 5       | 5.16.2  | Porting                        | 110   |

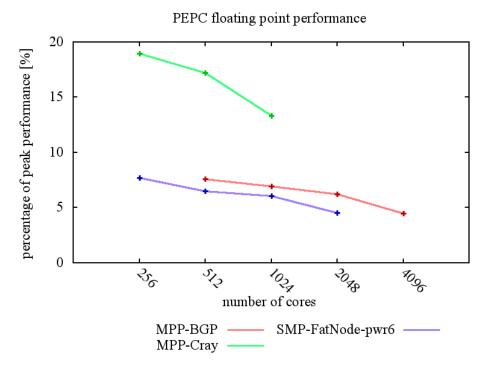

| 5       | 5.16.3  | Floating point performance     | 111   |

| 5       | 5.16.4  | Conclusions                    | 112   |

| 5.17    | QCD     |                                | . 112 |

| 5       | 5.17.1  | Application description        | 112   |

| 5       | 5.17.2  | Porting                        | 113   |

| 5       | 5.17.3  | Optimisation techniques        | 114   |

| 5       | 5.17.4  | Torus network topology         | 115   |

| 5       | 5.17.5  | Conclusions                    | 116   |

| 5.18 \$ | Siesta  |                                | . 116 |

| 5       | 5.18.1  | Application description        | 116   |

| 5       | 5.18.2  | Porting                        | 116   |

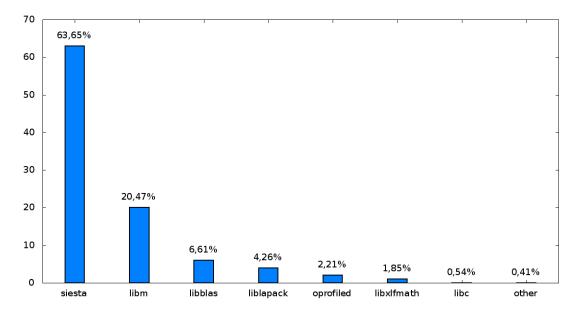

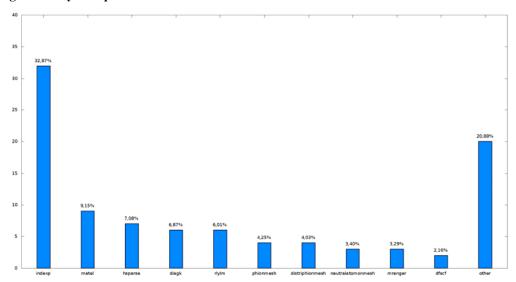

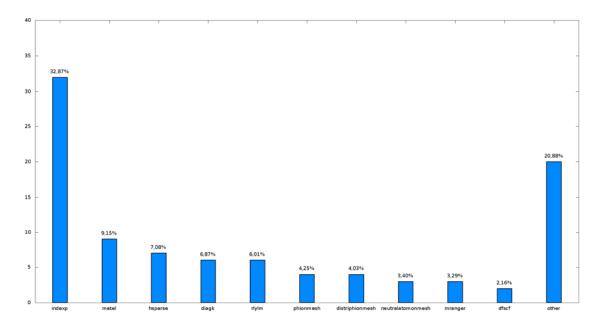

| 5       | 5.18.3  | Profiling                      | 117   |

| 5       | 5.18.4  | Optimisation techniques        | 119   |

| 5       | 5.18.5  | Results of optimisation effort | 120   |

| 5       | 5.18.6  | Conclusions                    | 121   |

| 5.19                   | 9 Quantun                | 1 ESPRESSO                                                                                                                                                                                                                                                        | 21       |

|------------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                        | 5.19.1                   | Application description                                                                                                                                                                                                                                           | 21       |

|                        | 5.19.2                   | Porting                                                                                                                                                                                                                                                           | 22       |

|                        | 5.19.3                   | Optimisation techniques                                                                                                                                                                                                                                           | 23       |

|                        | 5.19.4                   | Results of optimisation effort                                                                                                                                                                                                                                    | 25       |

|                        | 5.19.5                   | Conclusions 12                                                                                                                                                                                                                                                    | 26       |

| 6 Co                   | nclusions .              |                                                                                                                                                                                                                                                                   | 27       |

|                        |                          |                                                                                                                                                                                                                                                                   |          |

|                        |                          | List of Figures                                                                                                                                                                                                                                                   |          |

| Figure 4               | : Optimisa               | tion effort results, including the switch to a newer version                                                                                                                                                                                                      | 50       |

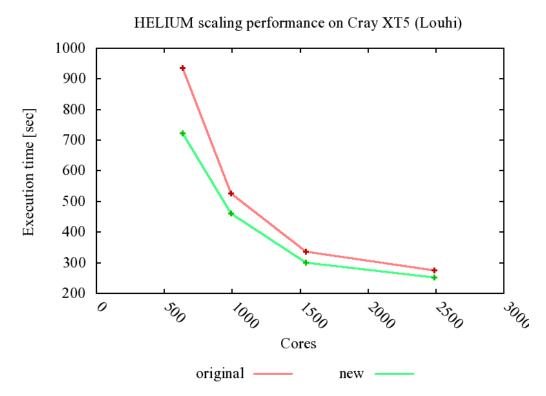

| Figure 5               | : HELIUM                 | 1 scaling performance on Cray XT5 (Louhi)                                                                                                                                                                                                                         | 36       |

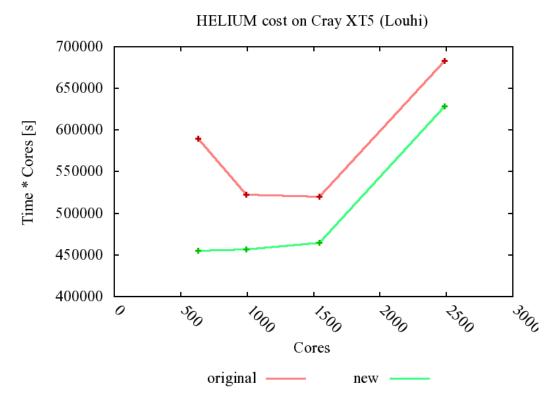

| Figure 6               | : HELIUM                 | 1 cost on Cray XT5 (Louhi)                                                                                                                                                                                                                                        | 36       |

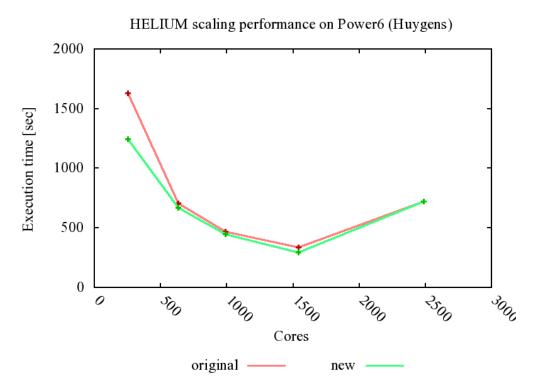

| Figure 7               | : HELIUM                 | 1 scaling performance on Power6 (Huygens)                                                                                                                                                                                                                         | 37       |

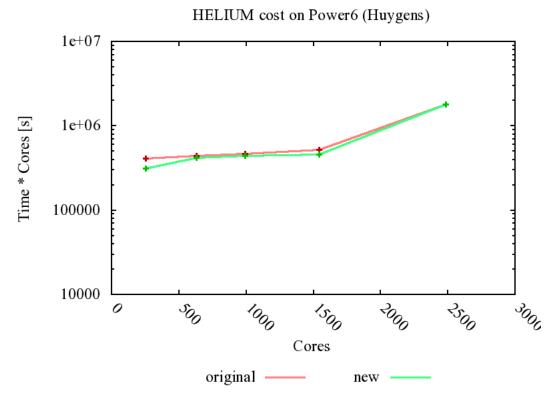

| Figure 8               | : HELIUM                 | 1 cost on Power6(Huygens)                                                                                                                                                                                                                                         | 37       |

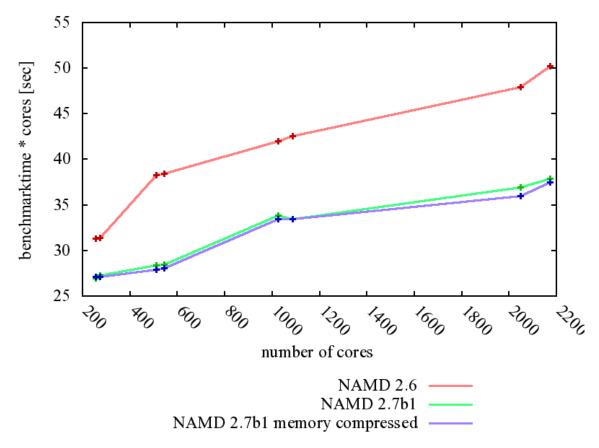

| we plot                | the NAM                  | nce of different versions of NAMD on the Cray XT5 prototype. On the vertical axis a measure for the total computational cost of a single NAMD step                                                                                                                | or       |

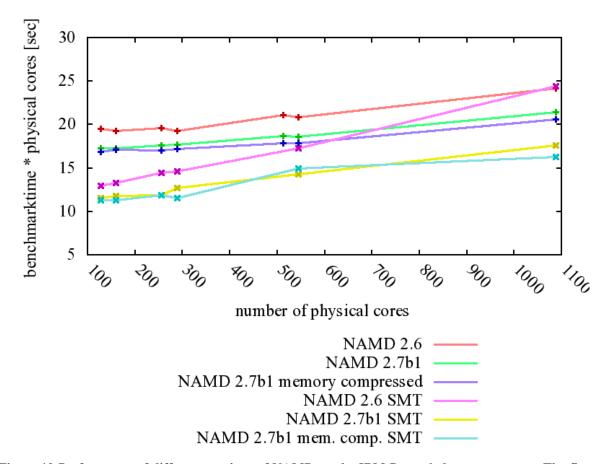

| figure al<br>multiplie | lso shows<br>ed by the 1 | nance of different versions of NAMD on the IBM Power6 cluster prototype. The effect of using SMT. On the vertical axis, we plot the NAMD benchmark tin number of physical processors used for simulation, which is a measure for the total of a single NAMD step. | ne<br>al |

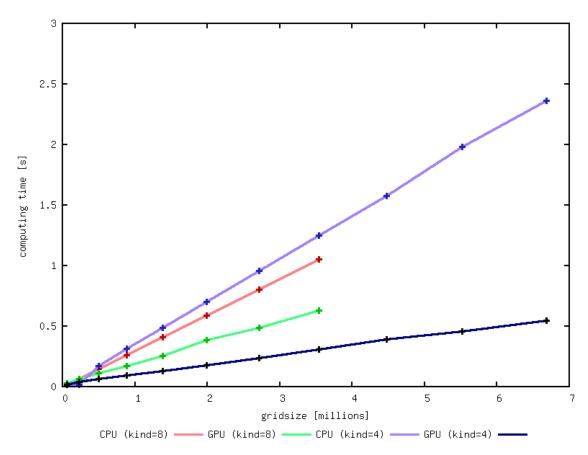

|                        |                          | ating time of merged subroutine ddt for CPU (Nehalem 2.8GHz) and hardwa Tesla S1070) as a function of grid size                                                                                                                                                   |          |

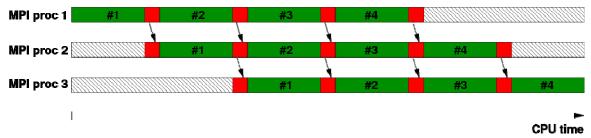

| domains                | . Green de               | tion of the pipelined Thomas algorithm solving four equation systems on three enotes the actual computation and red MPI communication. Grey areas corresponding                                                                                                   | nd       |

| Figure 1               | 3: Perform               | nance of PEPC-E on target architectures                                                                                                                                                                                                                           | 2        |

| Figure 1               | 4: Combin                | ed lattice QCD benchmark performance                                                                                                                                                                                                                              | 5        |

| Figure 1               | 5: System                | profile11                                                                                                                                                                                                                                                         | 8        |

| Figure 1               | 6: Siesta p              | rofile11                                                                                                                                                                                                                                                          | 8        |

| Figure 1               | 7: Lapack                | profile11                                                                                                                                                                                                                                                         | 9        |

## **List of Tables**

| Table 1: WP/ prototypes in PRACE                                                                                                                                                                           | . 1 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2: Available libraries on the PRACE prototypes                                                                                                                                                       | . 8 |

| Table 3: Libraries used by the PABS applications                                                                                                                                                           | . 9 |

| Table 4: Compiler support on the PRACE prototype systems.                                                                                                                                                  | 10  |

| Table 5: Output of the flagpruner algorithm on Cray XT5 when optimizing the flags for mod2am usin PGI 8.0.6. Speedup is in relation to the reference flag which is "-fast"                                 | _   |

| Table 6: Output of the flagpruner algorithm on Cray XT5 when optimizing the flags for mod2h usin PGI 8.0.6. Speedup is in relation to the reference flag which is "-fast"                                  | _   |

| Table 7: Optimal flags obtained using Opfla for the PGI compiler. The speedup is the increase performance when compiling using these flags, compared with compiling with "-fast"                           |     |

| Table 8: Speedup of each kernel compiled with the flags presented in Table 7                                                                                                                               | 13  |

| Table 9: Optimal flags obtained using Opfla for the PathScale compiler. The speedup is the increase performance when compiling using these flags, compared with compiling with "-03"                       |     |

| Table 10: Speedup of each kernel compiled with the flags presented in Table 9                                                                                                                              | 14  |

| Table 11: Optimal flags obtained using Opfla for the GNU compiler. The speedup is the increase performance when compiling using these flags, compared with compiling with "-03"                            |     |

| Table 12: Speedup when computing the speedup of each kernel compiled with the flags presented Table 11                                                                                                     |     |

| Table 13: Optimal flags obtained using Opfla for the Cray compiler. The speedup is the increase performance when compiling using these flags, compared with compiling with "-03"                           |     |

| Table 14: Optimal flags obtained using Opfla on Blue Gene/P with the IBM XLC 9.0 compiler. The speedup is the increase in performance when compiling using these flags, compared with compiling with "-O2" | ng  |

| Table 15: Optimal flags obtained using Opfla for the IBM XLC 9.0 compiler. The speedup is the increase in performance when compiling using these flags, compared with compiling with "-O2"                 |     |

| Table 16: Optimal cut-off for short- and long-message Alltoall algorithm as a function of the numb of MPI processes.                                                                                       |     |

| Table 17: PABS compiler flags in Cray XT5                                                                                                                                                                  | 19  |

| Table 18: PABS compiler flags for IBM Blue Gene/P - Jugene.                                                                                                                                                | 23  |

| Table 19: PABS compiler flags for IBM Power6 cluster - Huygens                                                                                                                                             | 26  |

| Table 20: Compiler flags for NEC SX-9 part of Baku                                                                                                                                                         | 27  |

| Table 21: Optimal compiler flags for the PRACE benchmark applications on the Cell prototype                                                                                                                | 28  |

| Table 22: Examples of strength reduction.                                                                                                                                                                  | 36  |

| Table 23: Compilation flag optimisation analysis on Cray XT5 with 32 processors, with fully occupie compute nodes                                                                                          |     |

| Table 24: Compilation flag test runs on Jugene with 1024 processes in VN mode                                                                                                                              | 59  |

| Table 25: Compilation flag analysis on IBM Power6 cluster- Huygens. The runs used 128 tasks, wi 32 tasks per node                                                                                          |     |

| Table 26: Compiler flags and execution times for Gadget on Huygens                                                                                                                                         | 70  |

| Table 27: Compiler flags and execution times for Gadget on Jugene71                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------|

| Table 28: HELIUM performance comparison using compiling options                                                                          |

| Table 29: Using compiling optimisation for HELIUM on Power6(Huygens)                                                                     |

| Table 30: Compiling flag optimisations on BG/P (Jugene)                                                                                  |

| Table 31: HELIUM performance comparison with and without the Test_MPI on Cray Xt5 (Louhi)84                                              |

| Table 32: HELIUM performance comparison with and without the Test_MPI on Power6 (Huygens) 84                                             |

| Table 33: Merging loops on Louhi reduce the execution time                                                                               |

| Table 34: The total cache misses on Louhi before and after merging loops                                                                 |

| Table 35: Merging loops and using temporary viables on Huygens reduce the execution time 85                                              |

| Table 36: The total cache misses on Huygens before and after merging loops and using temporary variables                                 |

| Table 37: NAMD performance with different compiler flags on Cray XT5                                                                     |

| Table 38: NAMD performance with different compiler flags on IBM Power6 cluster - Huygens 95                                              |

| Table 39: NAMD performance with different compiler flags on IBM Blue Gene/P96                                                            |

| Table 40: Comparison of the original FFT with the optimized one (50 Mio. grid points, 100 time steps, 16 MPI processes)                  |

| Table 41: Performance of the hopping matrix multiplication on a single core on the Altix 4700 [7]. 115                                   |

| Table 42: Speed of different versions of the distriphionmesh function: original, SPU version and SIMD optimized SPU version              |

| Table 43: Speedup obtained for routines in diagk.F                                                                                       |

| Table 44: Total speedup obtained for Siesta, using the VarCell Siesta internat test. Timings are measured using the Linux "time" command |

| Table 45: Speedup when replacing FFTW with the essl library on the Blue Gene/P system                                                    |

| Table 46: Speedup when inlining frequently called routines on the SX-9. Test case GRIR443. Number of cores 1024                          |

| Table 47: Speedup when inlining frequently called routines on IBM Blue Gene/P. Test case GRIR443. Number of cores 4096                   |

## **References and Applicable Documents**

- [1] NAMD2: Greater Scalability for Parallel Molecular Dynamics, L. Kalé, et al., Journal of Computational Physics 151, 283 (1999)

- [2] *Scalable Molecular Dynamics with NAMD*, J. Phillips, et al., Journal of Computational Chemistry **26**, 1781 (2005)

- [3] Charm++: Parallel Programming with Message-Driven Objects, L. Kalé, S.Krishnan, in: Parallel Programming using C++, by G.V. Wilson and P. Lu. MIT Press, 175 (1996)

- [4] Peter Coveney, Shunzhou Wan, private communication

- [5] http://www.ks.uiuc.edu/Research/namd/wiki/index.cgi?NamdMemoryR

eduction

- [6] Z. Sroczynski, *Improved performance of QCD code on ALICE*, Nucl. Phys. Proc. Suppl. 119 (2005) 1047-1049

- [7] Th. Streuer and H. Stüben, *Simulations of QCD in the Era of Sustained Tflop/s computing*, in C. Bischof, M. Brückner, P. Gibbon, G. Goubert, T. Lippert, B. Mohr, F. Peters (eds.), Parallel Computing: Architectures, Algorithms and Applications, IOS Press, Advances in Parallel Computing 15 (2008) 535--542,

## **List of Acronyms and Abbreviations**

AOS Array of Structures; a data layout

**BCO** Benchmark code owner. Person responsible for porting, optimizing,

petascaling and analysing a specific benchmark application.

**BLAS Basic Linear Algebra Subroutines**

**BLACS** Basic Linear Algebra Communication Subprograms

**BSC** Barcelona Supercomputer Center

**CPU** Central Processing Unit

CSC CSC — IT Center for Science Ltd (Finland)

**CSCS** Swiss National Supercomputing Center (Switzerland)

DFT **Density Functional Theory**

**EPCC** Edinburgh Parallel Computing Centre

Fat-node; describes a cluster with nodes with many processors and/or FN

large amount of memory

**FFT** Fast Fourier Transform

**GPGPU** General Purpose Graphic Processing Unit

**GUP** Institute of Graphics and Parallel Processing, Johannes Kepler

University Linz (Austria).

**HDF** Hierarchical Data Format.

**HLRS** High Performance Computing Center Stuttgart (Germany).

**HPC** High Performance Computing: Computing at a high performance level

at any given time; often-used synonym with Supercomputing.

Ю Input-Output

JuBE Jülich Benchmarking Environment

LAPACK Linear Algebra PACKage

LOC Lines of code

1 R7 Leibniz-Rechen Zentrum MD

Molecular Dynamics

**MPP** Massive parallel processing

MPI Message Passing Interface. A library for message-passing

programming.

Open Multi-Processing. An API for shared-memory parallel OpenMP

programming.

**PABS** PRACE Application Benchmark Suite

PETSc Portable, Extensible Toolkit for Scientific Computation

PRACE Partnership for Advanced Computing in Europe; Project Acronym.

PWR6 IBM Power 6 processor

**QCD Quantum Chromo Dynamics**

**RTM** Reverse time migration

SARA Computing and Networking Services Amsterdam (the SARA

Netherlands).

ScaLAPACK Scalable Linear Algebra PACKage

SMP Symmetric multiprocessing SMT Symmetric multi threading

SOA Structure of Arrays; a data layout SVN Subversion, a source code repository

TDDFT Time-Dependent Density Functional Theory

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the tier-0 systems; national or topical HPC centres would constitute tier-1.

Tier-1 Major national or topical HPC systems.

TN Thin-node; describes a cluster with nodes with one, or a few,

processors per node.

Wiki Web page or collection of web pages for creating collaborative web

sites.

XML eXtensible Markup Language

## **Executive Summary**

This document reports the work performed in task 6.5. The main objectives of the task were to discover best practices in porting applications to the PRACE WP7 prototype machines, and to study ways of optimizing the serial performance of the PRACE benchmark applications. The parallel performance of applications is studied in task 6.4 and reported in D6.4.

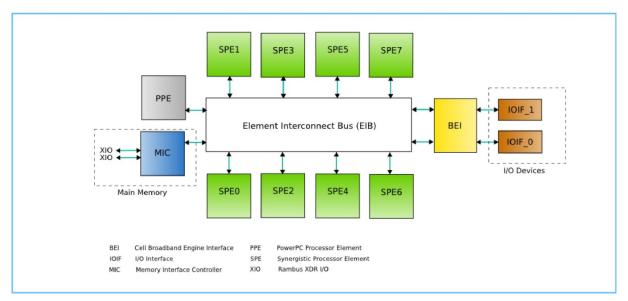

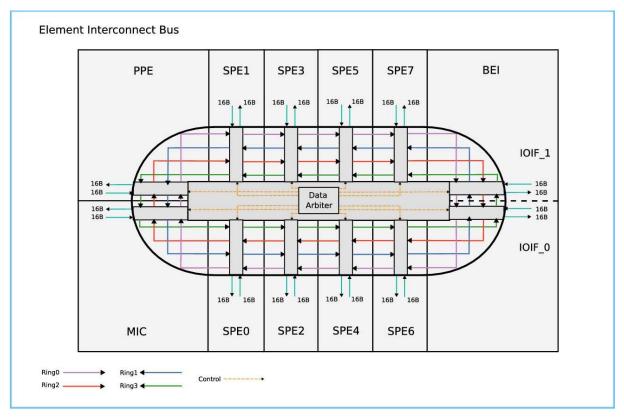

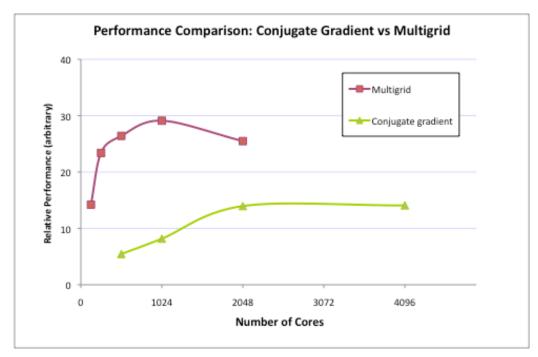

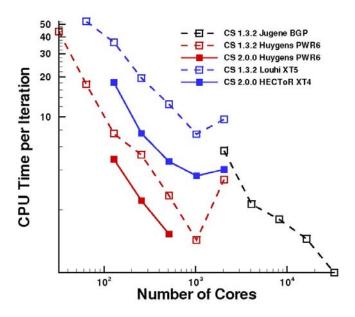

The PRACE WP7 prototype machines represent the current best-of-breed supercomputer architectures, comprising MPP machines, thin- and thick-node clusters, machines based on vector processors and finally machines based on Cell processors. The prototypes are listed in Table 1.

| Architecture                      | Туре                  | Name    | Site |

|-----------------------------------|-----------------------|---------|------|

| Cray XT5                          | MPP                   | Louhi   | CSC  |

| IBM Blue Gene/P                   | MPP                   | Jugene  | FZJ  |

| IBM Power6 cluster                | Fat-node (FN) cluster | Huygens | SARA |

| Nehalem cluster                   | Thin-node(TN) cluster | Juropa  | FZJ  |

| NEC SX-9 / Nehalem cluster hybrid | Vector /scalar hybrid | Baku    | HLRS |

| IBM Cell cluster                  | Cell cluster          | Maricel | BSC  |

**Table 1: WP7 prototypes in PRACE**

We have looked at the applications in the PRACE application benchmark suite (PABS). They represent the current, and future, computational workload expected on production petascale machines in Europe, and were identified in tasks 6.1 and 6.2. The first version of the suite was chosen based on a survey of the current usage of HPC applications. The final list of codes that emerged after taking into account the coverage of scientific areas, scalability, algorithms and user communities, is the following: Alya, AVBP, BSIT, Code\_Saturn, CP2K, CPMD, Elmer, EUTERPE, Gadget, GPAW, Gromacs, HELIUM, NAMD, NEMO, NS3D, Octopus, PEPC, SPECFEM3D, QCD, Quantum\_Espresso and WRF.

We report results for these applications, with the exception of Elmer, SPECFEM3D and WRF, which were added to the list in late 2009. Additionally we report results for Siesta, which was on the initial list, but not on the final one. Each application has been ported to an appropriate subset of prototypes, as described in report D6.3.2.

The application reports in Chapter 5 forms the main contribution of this report, detailing the issues and lessons learned for each application. From the reports we have extracted some information on porting and optimisation and present them in Chapters 3 and 4.

In the porting activities we have investigated not only adapting the applications to the prototypes, but also how to get optimal performance without resorting to source level modifications. We discuss porting issues caused by the hardware and software environment of the prototypes. We also look at the requirement for external libraries in the programs and present guidelines on how to leverage numerical libraries efficiently. Finally we discuss, in some depth, compilers and how to choose optimal compiler flags. We have systematically

studied optimal flags using four synthetic computational kernels, in order to discover compiler flags, which potentially enhance the performance of applications.

In the optimisation activities, we have focused on tuning the performance of the programs on the source code level. Here "optimisation" is defined as techniques, which improve the performance of the application on a node level. Here, a node is a shared memory compute element comprising one or more processors. We discuss general optimisation techniques, which are suitable for most platforms. These include techniques that improve the usage of the memory hierarchy, e.g., loop blocking and prefetching. We also look at ways of improving the computational throughput of applications, by using techniques such as SIMD instructions, and strength reduction. We also look at algorithmic optimisations, since in many cases they provide the greatest speedup to an application. Finally we also look at architecture-specific issues for x86 processors, SX-9 vector processors and Cell processors.

#### 1 Introduction

The Partnership for Advanced Computing in Europe (PRACE) has the overall objective to prepare for the creation of a persistent pan-European HPC service. PRACE is divided into a number of inter-linked work packages. WP6 focuses on software for petascale systems.

The primary goal of PRACE WP6 is to identify and understand the software libraries, tools, benchmarks and skills required by users, to ensure that their applications can use a Pflop/s system productively and efficiently. WP6 is the largest of the technical work packages and involves all of the PRACE partners.

In task 6.5 best practices in porting and optimizing leading HPC applications to PRACE prototype petascale systems (Table 1) are compiled, paving the way for the efficient exploitation of the upcoming Tier-0 systems. The applications under study are the benchmark applications in PABS, which is a benchmark suite being compiled in task 6.3.

The structure of the deliverable is as follows: Chapter 2 describes the methodology by which the work was carried out. In Chapter 3 we present the best practices for porting applications to the prototypes. Chapter 4 discusses optimisation techniques, while Chapter 5 presents application reports that detail the work done on each application.

## 2 Methodology

The work in this task has been structured around the process of porting and optimising the applications in the PRACE application benchmark suite. For each application a "benchmark code owner" (BCO) has been assigned, being responsible for the respective application. Each BCO has been in charge of an application-centred subproject, which ensures that the application is ported to a subset of prototypes, promising optimisation strategies are investigated and the results are reported. In many application subprojects not only the BCO, but also a number of contributors have been carrying out the work.

The role of the task leader has been to work with the BCOs to ensure that the work progresses smoothly. Additionally, porting and optimisation issues outside of the application centred framework have been looked at.

To organize the work, telephone conferences have been held every second week. The BCOs have attended these telephone conferences and reported on their progress. The work has been coordinated using a collaboration platform (Trac), combining a "Wiki" (collaborative webpublishing system) with a Subversion (SVN) version control server, maintained by CSC. This platform has proven to be very useful in a distributed project such as this, with close to twenty participating organizations.

This report has been compiled in the second year of the project, in 2009. Each BCO has filled in a report template in May 2009 and subsequently updated the report in August 2009. These reports are presented as a part of this report. We have also distilled the lessons learned of the application reports and have presented those results in this report. In addition to the application reports, the results are based on feedback from sites hosting the prototypes and studies on compiler flags for synthetic kernels.

## 3 Porting

In this document porting is defined as the process of adapting software to work on a new architecture. This includes processes required to compile a functioning binary and activities aimed at producing an optimal binary with respect to its usage of computational resource, e.g., wall clock time or memory requirement. The latter activities are called "optimal porting" in this document, to emphasize the focus on extracting maximal performance out of the target machine. Optimisations requiring source code changes are defined to be in the optimisation category and not in optimal porting.

In general, scientific applications are actively developed on a limited number of platforms. With some effort they are usually portable to other platforms, but the level of difficulty depends on how much the target architecture differs from the supported ones. For example, porting a program designed for general-purpose architectures to an accelerator-based supercomputer requires a significant rewrite in order to fully utilize the accelerators.

Porting of a scientific application to a new architecture involves several aspects, namely hardware, software environment, and compilers. In sections 3.1 to 3.3 we present some general remarks on porting issues. In sections 3.4 to 3.9 we report best practices regarding porting, on a per prototype basis. The information is based on knowledge from the prototype sites, experiences gained in porting the PRACE application benchmarks to the prototypes, as well as results obtained exploring optimal compiler flags for synthetic benchmark kernels.

#### 3.1 Hardware

The hardware in the prototypes range from fairly well understood x86 commodity clusters, to more exotic ones such as the IBM Cell based cluster (section 3.9). In general, applications are easier to port to the more common and widespread hardware platforms. Conversely, programs that have been tuned to an "exotic" architecture, can be challenging to port to more commonly used systems. This typically arises if the program has been programmed in a non-portable language or programming model. In such a case one needs to rewrite the code, which can be a significant effort. Some codes feature specially tuned assembler routines utilizing vector instructions (e.g. SSE2, Altivec), which are non-portable from one architecture to another. An example of this is Gromacs, as described in section 5.10.

Another issue is the memory configuration. In many MPP machines, such as the IBM Blue Gene/P, the amount of memory per core is small, posing problems for programs with high memory consumption.

In addition to compiling a fully functioning program, one must face challenges in extracting full performance from the machine. Cache-sizes, width of vector units and other issues affect the optimal way to utilize a processor. Also, the parallelization strategy can be well suited for one architecture, but not for another.

Finally, disk input/output (I/O) is in some case affected by endianness of the CPU. If one writes out data in a raw format there can be problems when reading the data on another machine, but external I/O libraries are in many cases able to handle this situation.

#### 3.2 Software environment

In clusters the operating system (OS) is normally Linux with complete support for all kernel features. This is not the case for MPP systems, such as Cray XT3/4/5 and IBM Blue Gene/P.

These are running lightweight operating systems on the nodes, giving applications maximum access to hardware. This yields low OS jitter, which enhances applications performance. On the flipside the porting requires cross compilation and the operating system does not support all features. On such platforms one can encounter cross compilation issues, as was the case for GPAW (section 5.9).

Most libraries for HPC are portable and often readily available as pre-compiled modules on the target machine. If the library is vendor specific, commercial, or in limited use in the HPC community, this might not be the case. In some cases the program is also dependent on a specific library version, which may not be available on the machine.

If a pre-compiled version of the library is not available one has to port it to the target machine. Thus, the single task of porting an application to an architecture can actually include more than one individual porting effort.

If the source code of the library on which the program relies is not available, one has to alter the program to use another library. If the library uses standardized interfaces this is trivial; examples of this are the BLAS (Basic Linear Algebra Subroutines) libraries. If the library uses non-standardized interfaces the task is non-trivial but still doable if another library providing similar features is available. For each library call one has to change the calling sequence to match the one of the new library.

Several different implementations of a library may be available on a system. The relative performance of these implementations can vary depending on the individual routine, size of input data, number of parallel processes and even the contents of the input data. It can thus be difficult to predict exactly which implementation is optimal for a certain application and input based on the results of other applications and inputs.

The following sections describe the most important library classes and their performance. The libraries are further described in the D6.6 report, chapter 6 (Assessment of Libraries for Petascale Systems).

#### 3.2.1 Dense Systems

Dense matrix operations are very common in HPC. The BLAS (Basic Linear Algebra Subroutines) and LAPACK (Linear Algebra Package) libraries arguably are the de facto standard for these operations. Also many higher-level libraries, such as ScaLAPACK (Scalable LAPACK) and sparse solvers leverage these libraries. Thus, for many applications they are often the most critical routines from a performance perspective. Each PRACE prototype features at least one, often several optimized implementations of these libraries. The relative performance of different implementations can vary depending on the operation and size of the input data. For example, on a Cray XT5, ACML can outperform Cray's libsci in matrix multiplication with small vector sizes, but not with large ones.

PBLAS and ScaLAPACK are the parallel counterparts for the BLAS and LAPACK libraries. The libraries use the BLACS (Basic Linear Algebra Communication Subprograms) library for parallelization. Usually BLACS is linked with MPI as the communication backend. Thus BLACS, as well as PBLAS and ScaLAPACK are specific to a certain MPI library implementation. This in turn means that optimized versions of these calls can usually only be found in the system vendors' own libraries (who also provide their own MPI implementation), such as Cray libsci and IBM PESSL. In addition to the operation type and problem size, the performance of these routines depends on the parallel decomposition of the problem, most importantly the block size and process topology.

#### 3.2.2 Sparse Systems

Sparse solvers are not standardized but the PETSc (Portable, Extensible Toolkit for Scientific Computation) framework is often used to provide a common interface for these libraries. Unlike dense matrices, the performance of sparse solvers is also affected by the sparsity pattern of the matrix (how the non-zero values are distributed). The optimal unrolling and prefetching parameters depend on this pattern and thus it is impossible to create general-purpose optimized kernels, which work on all types of patterns.

#### 3.2.3 Fourier Transforms

While no standard fast fourier transform (FFT) library interface exists, they generally have a similar interface and many perform operations in two stages: planning and execution phase. In the planning phase a "plan" is created based on the size of the input data. The plan is a description of the combination of codelets (code fragments) that is optimal for solving the FFT for that particular size. In the execution phase the FFT is executed according to the plan.

The plan can be executed any number of times with different input data sets, provided they are of the same size. The thoroughness of the planning stage can usually be adjusted. The fastest algorithms simply estimate the best combination based on the architecture, whereas the more thorough ones run and measure the execution times of different combinations. The most extensive algorithms may take several minutes to complete and might provide only marginal performance improvements. However, their use may be justified if the same plan is reused thousands of times in the course of execution. Some FFT implementations also provide facilities to store measured plans in a file. This can be useful for optimizing applications for specific problem sizes and for avoiding the overhead of executing a thorough planning stage.

To be more specific, we can note that FFTW is perhaps the most common cross-platform FFT library. There are actually two FFTW versions, FFTW2 and FFTW3, with incompatible interfaces. FFTW2 should not be used unless its MPI parallelization facilities are absolutely needed as it is in general slower than FFTW3. An MPI parallelized version of FFTW3 is being developed, but it is not ready for production use.

#### 3.2.4 Intrinsic Mathematical Operations

Many of the PRACE platforms feature libraries that can be used to replace a subset of the intrinsic math operations, such as exponential, sin etc., usually provided by the libm library. They tend to be relatively easy to use, often not requiring any changes to the application source code. Usually these functions omit normal error checking and exception handling and may degrade numerical accuracy. Thus it is recommended to carefully check the correctness of results when using them. Some libraries also provide array versions of intrinsic functions, which take arrays as input arguments and perform the specified function on each array member.

#### 3.2.5 Library support

In Table 2 we have listed which libraries are available on which prototypes, categorized by their type.

|                          |               | Louhi        | Jugene     | Huygens    | Maricel | Juropa | Baku       |

|--------------------------|---------------|--------------|------------|------------|---------|--------|------------|

|                          |               | libsci       | Goto       | ESSL       | SDK     | MKL    | MathKeisan |

|                          | BLAS          | ACML         | ESSL       | ATLAS      |         |        |            |

|                          | DLAS          | Cray IRT     |            |            |         |        |            |

|                          |               | MKL          |            |            |         |        |            |

| Dense                    |               | libsci       | netlib     | netlib     | SDK     | MKL    | MathKeisan |

| systems                  | LAPACK        | ACML         | Goto*      | ESSL       |         |        |            |

|                          | LATACK        | Cray IRT     | ESSL       |            |         |        |            |

|                          |               | MKL          |            |            |         |        |            |

|                          | PBLAS &       | libsci       | netlib     | netlib     |         |        | MathKeisan |

|                          | ScaLAPACK     | Cray IRT     | PESSL      | PESSL      |         |        |            |

|                          | Sequential    | SuperLU      | ESSL       |            |         | MKL    |            |

|                          | Sequentiai    | MKL          | HSL        |            |         |        |            |

| Sparse                   |               | PETsc        | PETsc      | MUMPS      |         |        |            |

| systems                  | Parallel      | (CASK)       | PESSL      |            |         |        |            |

| 5,5001115                |               | SuperLU_dist | MUMPS      |            |         |        |            |

|                          |               | Hypre        | Hypre      |            |         |        |            |

|                          |               | MUMPS        |            |            |         |        |            |

|                          |               | FFTW 2,3     | ESSL       | ESSL       | SDK     | MKL    | MathKeisan |

|                          | Sequential    | ACML         | FFTW 2,3   | FFTW 2,3   |         |        |            |

| Fourier                  | Sequential    | CRAFFT       |            |            |         |        |            |

| Transforms               |               | MKL          |            |            |         |        |            |

|                          | Parallel      | FFTW 2       | PESSL      | PESSL      |         |        | MathKeisan |

|                          | 1 11 11 11 11 |              | FFTW 2     | FFTW 2     |         |        |            |

| Random Num               | ber Generator | ACML         | ESSL/PESSL | ESSL/PESSL | SDK     |        |            |

| Kandom (Vamber Generator |               |              |            | SPRNG2     |         |        |            |

| Intrinsic math           |               | Cray FastMV  | MASS       | MASS       | MASS    | MKL    |            |

|                          |               | ACML-MV      |            |            | SDK     |        |            |

|                          |               | ParMETIS     | IMSL       | NAG        |         | MKL,   |            |

| Other                    |               |              | sundials   |            |         | NAG    |            |

|                          |               |              | ParMETIS   |            |         |        |            |

Table 2: Available libraries on the PRACE prototypes

In Table 3 we have listed the libraries that the applications require. It is evident that BLAS, LAPACK and FFTs are among the most widely used libraries.

| Code         | Libraries                                       |

|--------------|-------------------------------------------------|

| Alya         | Metis, Libspe2, pthread                         |

| AVBP         | Metis, HDF5                                     |

| BSIT         | Librt, Libnuma, Libspe2, pthread                |

| Code_Saturne | BLAS; optional: CGNS, Metis, HDF5, MED, SCOTCH  |

| CP2K         | BLAS, LAPACK, ScaLAPACK, FFT (ACML, FFTW, ESSL) |

| CPMD         | BLAS, LAPACK, FFT (FFTW)                        |

| EUTERPE      | BLAS, LAPACK, FFT (ESSL, FFTW), PETSc or WSMP   |

| Gadget       | FFT(FFTW 2), GSL                                |

| GPAW         | NumPy, BLAS, LAPACK, ScaLAPACK                  |

| Gromacs      | FFT(FFTW 3), BLAS, LAPACK                       |

| HELIUM           | ESSL                                                 |

|------------------|------------------------------------------------------|

| NAMD             | FFT(FFTW 2), TCL                                     |

| NEMO             | -                                                    |

| NS3D             | EAS3, (FFT)                                          |

| Octopus          | FFTW, BLAS, LAPACK, GSL                              |

| PEPC             | -                                                    |

| QCD              | -                                                    |

| Siesta           | BLAS, LAPACK, ScaLAPACK                              |

| Quantum ESPRESSO | BLAS, LAPACK, ScaLAPACK, FFT (FFTW, ACML, MKL, ESSL) |

Table 3: Libraries used by the PABS applications

### 3.3 Compilers

The foremost requirement for the compiler is that it has to be able to produce a correctly functioning binary. In some cases this requirement is not fulfilled for one of the reasons listed below.

- The source code of the application uses non-standard extensions of a specific compiler. To compile such a program with another compiler often requires extensive modifications to the source code and is thus often cumbersome and error prone.

- The compiler does not support the language features or version that the program uses, e.g., advanced Fortran 95 & 2003 features.

- The source code exposes a bug in the compiler.

There are several ways of attacking these problems. First, if the program supports a cross-platform compiler then one can use it on all supported platforms, e.g., the GNU compiler suite is supported on most platforms but they do not always provide the same performance as vendor provided compilers. In Table 4 we have listed the currently supported compilers on each prototype. Second, if the program only supports vendor or architecture specific compilers the problem has to be approached by solving the underlying incompatibility. The amount of work this entails can be significant. It can also be undesirable to do so in case one looses too much performance on the original platform.

| Prototype                            | GNU | PGI | Path-<br>Scale | Vendor provided<br>compiler        |

|--------------------------------------|-----|-----|----------------|------------------------------------|

| Cray XT5 - Louhi                     | X   | X   | X              | Cray Compiler<br>Environment (CCE) |

| IBM Blue Gene/P - Jugene             | X   |     |                | IBM XL                             |

| IBM Power6 cluster -Huygens          | X   |     |                | IBM XL                             |

| NEC SX-9 - BAKU                      |     |     |                | NEC compiler                       |

| Nehalem cluster - BAKU               | X   | X   |                | Intel compiler suite               |

| Sun/Bull Nehalem cluster -<br>JuRoPa | X   |     |                | Intel compiler suite               |

| IBM Cell cluster - MariCel           | X   |     |                | IBM XL (PPU & SPU versions)        |

Table 4: Compiler support on the PRACE prototype systems.

#### 3.3.1 Optimisation flags

After a fully working set of compilers has been identified the next stage is to identify an optimal set of flags for each compiler. After the optimal sets have been identified, one can pick the one providing the best performance.

Considering the large number of compiler flags it is clear that the number of possible combinations is extremely large, making an exhaustive trial of all combinations impossible. Thus, one cannot expect to find the optimal solution, only a very good suboptimal solution. There are essentially two ways of finding such a solution. The first is based on experience, intuition and knowledge, the second on automatic iterative compilation techniques.

Programmers typically have experience and knowledge of a set of compiler flags, which have produced good results for other programs. The compiler manual is also a good source for promising compiler flag candidates. Based on these, and knowledge of the algorithm and its implementation, one can produce a limited number of best guesses. From these candidates one then picks the best performing one. Assuming the optimisation flags are not interdependent, one can also follow a procedure where one adds flags one by one, accepting a flag only if it reduces the runtime. This is the strategy followed in porting the HELIUM code to the Cray XT5 architecture. As the flags are interdependent, this procedure is unlikely to produce the optimal result.

#### 3.3.2 Iterative compilation

In this project we have also studied iterative compilation techniques. The goal was to optimize the compiler flags for four synthetic benchmark kernels and to extract a set of compiler flags that is generally useful.

Iterative compilation techniques attempt to tune the compilation by iteratively compiling and running the program. Different algorithms can be used to evolve the compilation procedure during the optimisation. Noteworthy examples are the GCC compiler of the milepost project (www.milepost.eu), and the genetic algorithm (GA) implemented in the Pathscale compiler. Profile guided optimisation in which collected runtime statistics are used to guide the compiler can also be thought of as such a technique, requiring only two compilations.

Here we have developed a simple GPL licensed program named Opfla that implements a genetic algorithm to optimize compiler flags. It's written in Python and comprises 1100 lines of code. It's easy to adapt to new platforms and programs as all the relevant information for compiling and running programs are described in a set of XML files; we successfully ran it on the Cray XT5, IBM Blue Gene/P, IBM Power6 cluster, and the NEC SX-9 prototypes.

#### Algorithms

Opfla implements two algorithms. The first algorithm is a genetic algorithm that we use to find a sub-optimal set of compiler flags. In the algorithm one first calculates a reference time by compiling the program using a reference flag (usually "-02") and running the resulting binary. A reference result is extracted from the output to verify subsequent programs. In the next step one creates a population comprising 50 random compiler flag sets. The performance of these are measured, and using a stochastic criteria the best ones are allowed to produce the next population generation by combining the flag sets. The algorithm also introduces some random changes to simulate mutation, this is important to make sure phase space is explored as efficiently as possible. Once one has the new population it's iteratively refined using the proceeding step. We store all solutions and are able to pick the best one.

The second algorithm, flagpruner, is able to remove the least important flags from a set of compiler flags. This is important as GA in practice produces a flag set with tens of flags, but most of these are not important. In fact we find that most flags tend to have no impact on the produced binary, as verified by computing the MD5 sum of each binary. The algorithm iteratively removes the least important flag one after the other until all flags have been removed. The least important flag either has identical MD5 sum, or the least impact on performance.

The current version is mostly suitable for small test kernels as it requires of the order of hundreds to a few thousands compilation-execution cycles. The same compiler flags are also used for all files. To use this procedure for large-scale application tuning one would need to improve the optimisation algorithm to minimize the number of executions, and also enable it to tune optimisation flags on a per file, or per function, basis. Using identical compiler flags for all algorithms will always be a compromise. Additionally, the present scheme is unable to provide insert pragmas in the source code, which are useful for providing the compiler with in-depth information on how to compiler the code for optimal performance.

#### Test case and analysis procedure

The synthetic benchmark kernels that we studied were from the Euroben set of synthetic kernels: mod2m which performs a matrix multiplication, mod2as which performs a sparse matrix vector multiplication, mod2f which performs a 1D-FFT, and finally mod2h which produces random numbers. These kernels were written in C, hence no careful comparison of Fortran compilers was done. For more information on the Euroben kernels please see the PRACE report D6.3.2.

To give an example of the kind of information we can extract from these runs we take the output of the flagpruner algorithm on Cray XT5 for mod2am and mod2h using PGI 8.0.6 (Table 5 and Table 6). The kernels are quite different, and this is reflected in the optimal flags. For mod2am flags which optimize floating point performance and loop behaviour are important, while mod2h benefits from flags which tune inlining behaviour and unrolling. The relative importance of flags is also evident, as the most important ones are the last to be removed. It's also clear that some flags are dependent on each other in order to produce good performance, e.g., for mod2am "-Mvect=sse -Mipa=fast" gives good performance but having either flag separately looses all the speedup compared to the reference "-fast".

Finally we note that for both codes there is a small set of flags, which provides close to optimal performance. One does not need to aim for a large number of flags to get good performance. This is even more the case for large codes with a mix of different algorithms.

| Speedup | Flags                                                                       |

|---------|-----------------------------------------------------------------------------|

| 0.33    |                                                                             |

| 0.97    | -Mvect=sse                                                                  |

| 1.56    | -Mvect=sse -Mipa=fast                                                       |

| 1.60    | -Mvect=sse -Mipa=fast -Mnoprefetch                                          |

| 1.63    | -Mvect=sse -Mipa=fast -Mnoprefetch -Mvect=noaltcode                         |

| 1.67    | -Mvect=sse -Mipa=fast -Mnoprefetch -Mvect=noaltcode<br>-Mnozerotrip         |

| 1.70    | -Mvect=sse -Mipa=fast -Mnoprefetch -Mvect=noaltcode<br>-Mnozerotrip -Msmart |

Table 5: Output of the flagpruner algorithm on Cray XT5 when optimizing the flags for mod2am using PGI 8.0.6. Speedup is in relation to the reference flag, which is "-fast"

| Speedup | Flags                                                                                                   |

|---------|---------------------------------------------------------------------------------------------------------|

| 0.89    | -Minline=levels:11                                                                                      |

| 0.96    | -Minline=levels:11 -Munroll=n:16                                                                        |

| 1.07    | -Minline=levels:11 -Munroll=n:16 -Msmart                                                                |

| 1.15    | -Minline=levels:11 -Munroll=n:16 -Msmart -Mipa=fast                                                     |

| 1.19    | -Minline=levels:11 -Munroll=n:16 -Msmart -Mipa=fast -O4                                                 |

| 1.23    | -Minline=levels:11 -Munroll=n:16 -Msmart -Mipa=fast -O4 -alias=traditional                              |

| 1.25    | -Minline=levels:11 -Munroll=n:16 -Msmart -Mipa=fast<br>-O4 -alias=traditional -Mmovnt                   |

| 1.27    | -Minline=levels:11 -Munroll=n:16 -Msmart -Mipa=fast<br>-O4 -alias=traditional -Mmovnt -Msmartalloc=huge |

Table 6: Output of the flagpruner algorithm on Cray XT5 when optimizing the flags for mod2h using PGI 8.0.6. Speedup is in relation to the reference flag which is "-fast"

#### Cray XT5 - Louhi

On the Cray XT5 architecture there are four compilers which are relevant: The Portland Group's PGI Fortran/C/C++ Compiler, the PathScale Compiler Suite, the GNU compiler collection, and the Cray Compiler Environment (CCE). We have analyzed the flags of all of these compilers using the procedure described above.

For the PGI (8.0.6) compiler we used "-fast" as the reference. It provides in general good performance while still being fairly safe to use. Our experience is that it does break some programs. The results for the four synthetic kernels under study are presented in Table 7.

| Kernel | Optimal flags                                                                                                                       | Speedup |

|--------|-------------------------------------------------------------------------------------------------------------------------------------|---------|

| Mod2am | -Mnoprefetch -Mipa=fast -Msmart -Mvect=sse -<br>Mvect=noaltcode -Mnozerotrip                                                        | 1.70    |

| Mod2as | -Mipa=fast -Msmart -Mvect=sse -Mvect=noaltcode -<br>Munroll=c:4 -Mnomovnt                                                           | 1.28    |

| Mod2f  | -Mprefetch=plain -Minline=size:10 -Mipa=fast - Mvect=sse -Mvect=fuse -Mvect=uniform -Mnozerotrip -Munroll=c:8                       | 1.27    |

| Mod2h  | -04 -alias=traditional -Minline=levels:11 - Mipa=fast -Msmart -Msmartalloc=huge - Mvect=prefetch -Mnozerotrip -Munroll=n:16 -Mmovnt | 1.28    |