# A Cascaded H-Bridge Multilevel Inverter with Reduced Number of Switches

Ranjeeta Sugandhi, M.S.Aspalli

Abstract - This paper presents simulation of a 5-level cascaded H-bridge multilevel inverter, with reduce the number of power switching devices in the current flow direction. The propose topology consists of a five switches with double DC sources. The analysis is designing a new topology for a single-phase cascaded multilevel H-bridge inverter (CHBMLI), with a focus on the number of power switching devices in the current flow direction. Conduction and switching losses have to be reduced to achieve higher performance operation of power electronic devices. Multilevel inverters are designed to achieve the desired voltages of output from different DC sources. A analysis of the simulated power loss values is deals with based on how the power switch reduction led to the loss decreases.

Keywords - Conduction loss, Multilevel inverter, Power Converter, Switching loss.

### I. INTRODUCTION

Inverter is an electronic circuit converted direct current to alternating current. In a building, in aircraft systems, the inverters are used to turn the aircraft's DC power into AC for emergency backup power. The AC power is used mainly for electrical equipment such as lighting, radar, radio, generator and other equipment. The voltage source inverter produces an output voltage of 0,  $+V_{\text{dc}}$  and  $-V_{\text{dc}}$ . A multilevel inverter is an electronic control circuit which can use various lower level DC voltages as an input to obtain the desired alternating voltage at the output. The multilevel inverters attracted enormous interest from the power industries[1]. A multilevel inverter has many benefits over a traditional two-level inverter that uses modulation of the pulse width of high switching frequencies[2]. A waveform similar to sinusoidal at the output can be generated with an increase in the number of DC voltage sources on the input side. As a response, total harmonic distortion decreases, increasing the performance of the waveform quality.In comparison, the other main advantages of the multilevel inverter are lower switching rates, decreased dv/dt voltage switches[3], and greater electromagnetic interference[4]. Multilevel inverters have power conversion systems and capacitor voltage sources in operation. Due to the ability to synthesize output voltage waveforms with an improved harmonic spectrum and achieve higher voltages with a limited maximum operational level, they are suited for high-voltage applications. The different types of multilevel inverters include additional switches, diodes, capacitors, and voltage sources where the maximum harmonic distortion and electrical stress on the system is increased. There are three types of diode-clamped (neutralclamped), capacitor-clamped (flying capacitors) Cascaded H-Bridge Multilevel Inverter[5][6].

#### Revised Manuscript Received on October 13, 2020.

Ranjeeta Sugandhi, Department of Electrical and Electronics, PDA College of Engineering, Kalaburagi, India. Email:ranjeetasugandhi222@gmail.com

**Dr.M.S.Aspalli**, Department of Electrical and Electronics, PDA College of Engineering, Kalaburagi, India. Email: maspalli@gmail.com

Most of the study of inverters focused on operating with multilevel inverters. Compared to the standard 2-level inverter one, this topology has proved to be useful because it can minimize the harmonics of lower order as the number of output voltage staircases is increased. The cascaded fivelevel H-bridge inverters consist of modularity, control flexibility, durability, and allow less power semiconductor devices to produce a particular level[7]. As a result, the inverters losses and total costs decrease contributing to increased efficiency. New simple model of five stage inverter cascaded H-bridge is to maximize the number of output stages by using fewer electronic control units. The cascaded H-bridge multilevel inverter (CHBMLI) has been used for the application of renewable energy generation. Energy sources such as solar, wind, hydro, biomass, or a variation thereof can be adjusted to provide access to alternative renewable energy supplies[8]. These renewable energy sources have different electrical characteristics, such as DC or AC voltage, and when connected directly to a grid or load, it is difficult to use the generated power. As an interface for the power generated by the conditioning, a different power electronics converter is needed for the source of renewable energy. The cascaded multilevel Hbridge inverter primarily focuses on increasing the number of output voltage levels by using fewer switches.. The microcontroller can be used to generate the switching pulses to have the control on the operation of the inverter circuit.

## II. RELATED WORK

The Multilevel Inverter Cascaded H-bridge uses fewer switches. If the number of switches is reduced, the output always increases due to which losses in conductions and switches are reduced. In this multilevel inverter includes series connected modules which can generate only unidirectional positive voltage[9]. In order to get the bidirectional voltage an H-bridge is connected to the series connected modules. They have used a sinusoidal pulse width modulation technique (SPWM)[10]. Since the use of fewer amount of carriers controlling the circuit becomes less complicated, size and cost of installation also reduces. The multilevel inverter and its advantages. This paper explains the two different 7-level cascaded multilevel inverter topologies with a reduced number of switches compared to standard form which has 12 switches[11]. The topologies consist of circuits with the same 7-level output, with 9 switches and 7 switches. Therefore, with lesser switches, the gate drive circuitry requirement is minimized and very few switches will also be performed for specific time intervals. Multicarrier wave signals are used to implement the SPWM technique.

## A Cascaded H-Bridge Multilevel Inverter with Reduced Number of Switches

Level shifting triangular waves are used to produce sine PWM changing series in connection with sinusoidal reference. The number of triangular waves shifted to level depends on the number of output levels. Techniques that generating switching pulses are used in phase disposition (IPD), alternate phase disposition (APD), carrier overlap (CO) and variable frequency (VF) pulse width modulation (PWM) techniques. This inverter system has eight switches and triple DC sources per phase. This new inverter is suitable for low dc bus voltage, multilevel power inversion. The advantages of the new topology is to add only four active power switches in order to achieve operation at 5 levels[12].A modern low cost, useful multilevel cascaded inverter (MLI) configuration[13]. A multilevel inverter requires minimal switching equipment and isolated power supplies compared to the multilevel essential inverter. This solves the issue of neutral point fluctuations, current DC offset, issue of reverse diode recovery etc. As minimum number of switches and minimum standing voltage on switches, the maximum output voltage steps are produced. The suggested topology results in less switches, losses, and costs[14].

#### III. PROPOSED SYSTEM

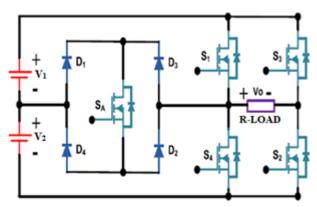

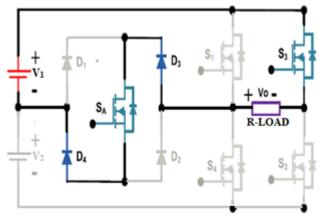

Fig.1: The proposed module of Cascaded H-Bridge multilevel inverter.

Table-I: Switching combinations of cascaded H-Bridge multilevel inverter.

| SL.NO. | Output voltages     | Switching states |                |                |                |       |

|--------|---------------------|------------------|----------------|----------------|----------------|-------|

|        |                     | S <sub>1</sub>   | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | $S_A$ |

| 1.     | V <sub>dc</sub>     | 1                | 1              | 0              | 0              | 0     |

| 2.     | V <sub>dc</sub> /2  | 0                | 1              | 0              | 0              | 1     |

| 3.     | 0                   | 0                | 1              | 0              | 1              | 0     |

|        | 0                   | 1                | 0              | 1              | 0              | 0     |

| 4.     | -V <sub>dc</sub> /2 | 0                | 0              | 1              | 0              | 1     |

| 5.     | -V <sub>dc</sub>    | 0                | 0              | 1              | 1              | 0     |

As seen in Fig.1, the hybridized H-bridge circuit topology used as part of the 5-level multilevel inverter design and implementation. The produced five-level cascaded MLI

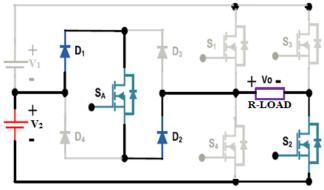

topology for output voltage is shown in Fig.1 The switching states showing the status of the basic MLI are seen in Table 1. The section presents how many sources, switches, and output voltage values are used. Operating Modes The five required output voltage levels are produced as follows. **Mode1:**In this mode of operation, the both switches  $S_1$  and  $S_2$  is in ON state. The other switches are OFF state. The output voltage produce  $V_o = V_{dc}$  Fig.2 shows the current paths at this stage.

Fig: 2. Generation of  $V_{dc}$  voltage level

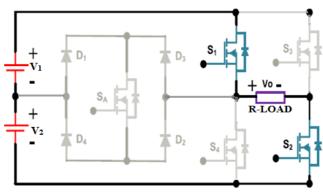

**Mode2:**In this mode of operation, the auxiliary switch,  $S_2$  and  $S_A$  is turned ON and the other controlled switches are turned OFF. The voltage applied to the load terminals is  $V_o = V_{dc}/2$  Fig.3. shows the current paths at this stage.

Fig 3. Generation of  $V_{dc}/2$  voltage level

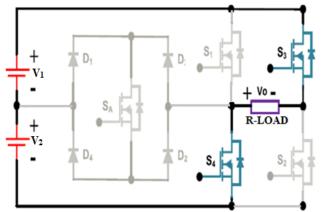

**Mode3:**In this mode of operation, the two main switches  $S_2$  and  $S_4$  are ON, short-circuiting the load. All other controlled switches are OFF the voltage applied to the load terminals is zero ( $V_o = 0$ ) is shown in Fig.4.

Fig 4. Generation of zero voltage level

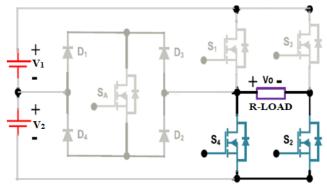

**Mode4:**In this modes of operation, the switch  $S_3$  and auxiliary switch,  $S_A$  both are in ON state and the other controlled switches are turned OFF and the voltage applied to the load terminals is  $V_{o} = -V_{dc}/2$ . Fig.5. shows the current paths at this stage.

Fig: 5. Generation of -V<sub>dc</sub>/2 voltage level

**Mode5:**In this modes of operation, When the both switches  $S_3$  and  $S_4$  are in ON state and the other controlled switches are OFF state the voltage applied to the load terminals is  $V_0 = -V_{dc}$  Fig.6. shows the current paths at this stage.

Fig 6. Generation of -V<sub>dc</sub> voltage level

#### IV. SIMULATION RESULTS

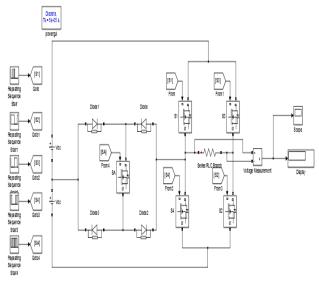

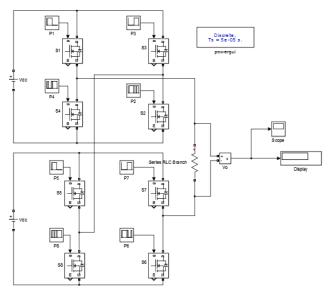

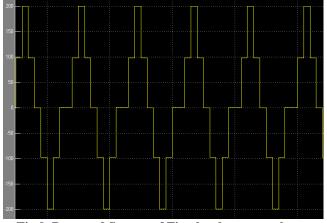

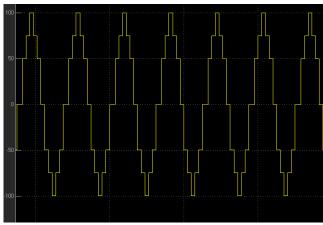

Simulation of a 5-level cascaded multilevel H-bridge inverter with reduced switch number. The proposed 5-level inverter is simulated using MATLAB/Simulink by using MOSFET developed in fig 7. We also used 5 switches in the proposed system to produce 5-level output along with 2 Voltage Source and 4 diodes. The multilevel inverter for the 7-level cascaded H-bridge is implemented using 8 MOSFETs modelled in fig. 8. The 5-level inverter phased output voltage waveform thus obtained is shown in Fig 9. and Fig. 10 also shows simulation of the 7-level output voltage waveform.

Fig 7. Proposed five-Level multilevel inverter in MATLAB

Fig 8. 7-Level Conventional Method in MATLAB

Fig 9. Proposed System of Five-level output voltage waveform

## A Cascaded H-Bridge Multilevel Inverter with Reduced Number of Switches

Fig 10. 7-Level output voltage waveform

#### V. CONCLUSIONS

This paper focused mainly to reducing switches and voltage sources. Inverters are static power electronics systems that change dc input voltage with the desired magnitude and frequency into an ac output voltage. The waveforms of ideal inverters with output voltage should be sinusoidal. Multilevel inverters are used to get improved waveforms with a low harmonic distortion. The topology used here is H-Bridge cascaded, and the modulation method is modulation of a sinusoidal pulse width. The voltage output level is at five. Simulation is performed in MATLAB and the waveforms are generated and the outcomes are evaluated using the program MATLAB / SIMULINK.

#### REFERENCES

- Ranjeeta Sugandhi, M.S.Aspalli, Sushma J Patil, "A Five-Level Cascaded H-Bridge Multilevel Inverter With Reduced Number of Switches," Information Technology and Electrical Engineering (ITEE), vol. 9, no.3, pp. 370-374, June 2020.

- Kahwa, H. Obara and Y. Fujimoto, "Design of 5-level Reduced Switches Count H-bridge Multilevel Inverter," in Proc. IEEE 15th Int. Workshop Adv. Motion Control(AMC), Tokyo, Japan, March 2018, pp.41-46.

- 3. E. Najafi and A. H. M. Yatim "Design and Implementation of a New Multilevel Inverter Topology," IEEE Trans. Power. Electron., vol. 59, no.11, pp. 4148-4154, Nov 2012.

- Z. Du, L. M. Tolbert, J. N. Chiasson and B. Ozpineci, "Fundamental frequency switching strategies of a seven-level hybrid cascaded Hbridge multilevel inverter," IEEE Trans. Power. Electron., vol. 24, no. 1, pp.25-33, January 2009.

- 5. J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol.49, no. 4, pp. 724-738, August 2002.

- 6. J. S. Lai and F. Z. Peng, "Multilevel converters—A new breed of power converters," IEEE Trans. Ind. Applicat., vol. 32, no. 3, pp. 509-517,May/June 1996.

- SreenivasuluMamila, Suresh Kumar Anisetty and M. Rama Pallavi "A New Cascaded H-Bridge Multilevel Inverter With Reduced Switch Count" 2017 International Conference on Smart Technology for Smart Nation (ICSTSN) 978-1-5386-0569-1\$31.00 ©2017 IEEE.

- J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A New Multilevel Converter Topology With Reduced Number of Power Electronic Components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp.655-667, Feb 2012

- P.Jamuna, Dr.C.Christober Asir Rajan, K.Gowri, V.Vijayasanthi, "Analysis of H-bridge based cascaded Multilevel Inverter," IEEE, Nov. 2016

- Rahul Nair, Mahalakshmi R, Dr. Sindhu ThampattyK.c. "Performance of Three Phase 11-level Inverter with reduced number of switches using different PWM Techniques" 2015 IEEE International Conference on Technological Advancements in Power & Energy 978-1-4799-8280-6/15/\$31.00 ©2015 IEEE.

- 11. T V V S Lakshmi , Noby George, Umashankar S and Kothari D P "Cascaded seven level inverter with reduced number of switches using level shifting PWM technique" 2013 International Conference on Power, Energy and Control (ICPEC) 978-1-4673-6030-2/13/\$31.00 ©2013 IEEE.

- 12. Y. Hu, Y. Xie, D. Fu and L. Cheng, "A New Single-Phase \_-Type 5-Level Inverter Using 3-Terminal Switch-Network," IEEE Trans. Ind. Electron.,vol. 63, no. 11, pp. 7165-7174, Nov. 2016.

- Venusonti, Sachin Jain, Vivek Agarwal "A New Low Cost and High Efficiency Cascaded Half-Bridge Multilevel Inverter with Reduced Number of Switches" 2014 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES) 978-1-4799-6373-7/14/\$31.00 ©2014 IEEE.

- Babaei, E., "A Cascade Multilevel Converter Topology With Reduced Number of Switches," Power Electronics, IEEE Transactions on , vol.23, no.6, pp.2657-2664, Nov. 2008.

- F. Z. Peng, "A generalized multilevel inverter topology with self voltage balancing," IEEE Trans. Ind. Applicat., vol. 37, no. 2, pp. 611-618, March/April 2001.

#### **AUTHORS PROFILE**

Ranjeeta Sugandhi received the B.E.degree in Electrical and Electronics Engineering in 2018 from Visvesvaraya Technological University, Belagavi,. Veerappa Nisty Engineering College, Shorapur.

**Dr.M.S.Aspalli** received the B.E. degree in Electrical Engineering in 1991, M.E. in Power Electronics in 1997 and Ph.D in 2014 from Gulbarga University, Gulbarga. He started his carrier as a lecturer in Electrical Department at P.D.A.College of Engineering, Gulbarga and now he is working there

as Professor and P.G.Coordinator for Post Graduate course in Power Electronics under the Department of Electrical and Electronics Engineering. His fields of interest are Power Electronics and Drives, Power Quality Issues, Electric Vehicles' and its control. He has published more than 60 papers in national and international journals and conferences and he has published a book titled "Microcontroller Based Controller for Three Phase Induction Motor" with (ISBN-978-620-0-5349-8) publishers: Lambert Academic publishing. He is life member of FIE, ISTE, IETE, ISLE and ISCA. He has attended and awarded the certificate for The AICTE-UKIERI Technical LeadershipProgram i.e UK-INDIA Education and Research Initiative Program which is jointly organized by Dudley College, UK and AICTE New Delhi. He has more than 20 years of experience and he has taught different subjects at UG and PG. At present he is guiding 03 research scholars.