# DesignandSimulation of High-Efficiency High Gain non Isolated Interleaved DC-DC Converter with Reduced Voltage Stress on the Devices

# Azra Fatima, M.S.Aspalli

Abstract: In this paper, a non-isolated two interleaved modified step up KY Converter is analyzed and designed, whose efficiency,the voltage conversion ratio is high. There are various types of non -isolated converters such as buck-boost, Cuk, SEPIC, ZETA converters, etc but the voltage gain of these converters is less compare to the proposed interleaved KY converters. The voltage gain, efficiency of the proposed converter is enhanced compared to the previous converters. The voltage stress on semi-conductor devices and the ripple in the input current is reduced because of this interleaving technique. Switches with low on-state resistance are used due to which the conduction losses are reduced. Steady-state analysis and the operating principle are studied in continuous conduction mode (CCM) at ideal conditions. Simulation is also carried out in MATLAB/Simulink for the proposed interleaved KY converter.

Keywords: dc-dc converter, High voltage gain, Interleaved KY converter, Voltage stress.

#### I. INTRODUCTION

As we all know that fossil fuels are being depleted day by day and they are also affecting the environment. So the renewable sources are being considered as an attractive feature by research scholars. Renewable resources like photovoltaic (PV), fuel cell, wind are commonly used but the output obtained by this is low dc voltage, to enhance this low dc voltage to higher value dc-dc converters are been used. In the case of PV there exist a shadow effect that cannot be neglected. In the present scenario, dc-dc converters are being widely used for various purposes, Such as battery power systems, uninterrupted power supply, etc. In SEPIC dc-dc converter efficiency-voltage gain is high where the output may be greater, equal, or less than the input voltage[1]. To have continuous input current for dc-dc convertor with low ripple double input source are used. Various conventional dc-dc converters have high voltage gain but due to their operating conditions and the parasitic element the voltage gain of the buck-boost, Cuk, SEPIC, ZETA converters have been restricted. Also, the stress on the semiconductor device is equal to the output voltage [2]. The voltage gain of the converters can also be increased by using a couple of inductors in a dc-dc converter. Thus a proper number of turns ratios must be chosen to increase the voltage gain[3]. But higher the turns ration reduces the efficiency and causes higher EMI noise and power loss which can be overcome by using non-isolated converters which indeed have lower size, cost, and losses[4].

#### Revised Manuscript Received on October 10, 2020.

#### \* Correspondence Author

**Azra Fatima:** M.Tech II year student of Power Electronics departmentat Poojya doddappa appa college of Engineering kalaburagi India. E-mail:a.fatima.elecengg@gmail.com.

**M.S.Aspalli:** Professor of Power Electronics department at Poojyadoddappa appa college of Engineering kalaburagi India. E-mail:maspalli@gmail.com The newly developed converter is proposed named as KY converters. In this converter, the voltage on the switches is less than the output voltage [5]. Also, the KY converters are very useful in supplying the power to the devices which will operate at low noise conditions they provide a very fast transient response which is similar to the buck converter [6]. The output current is non-pulsating of this KY converter. But still, the voltage gain of this converter can be enhanced [7]. In this paper a novel high step-up interleaved dc-dc converter is presented, This converter is proposed by interleaving two modified KY converters. The voltage conversion ratio of this converter is higher than the previously developed dc-dc converter like buck-boost, Cuk, SEPIC, ZETA convertors. The overall aim of this converter is to obtain high voltage gain, high efficiency, low voltage stress on the switches, and the other semiconductor devices. The low ripple in the input current and low switching and conduction losses.

#### II. PROPOSED INTERLEVED KY CONVERTER TOPOLOGY

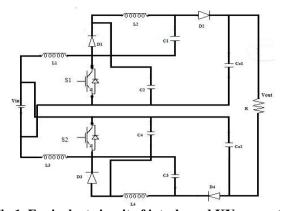

Fig1 represents a step up non-isolated interleaved dc-dc converter. In this paper, the voltage gain of the switches is less than the output voltage, and also the ripple at the output voltage is reduced and the output current is non-pulsating. As they have previously developed various converters but the voltage gain of the proposed converter is larger i.e M=1+3D/1-D (1)

The interleaved modified KY converter consists of two IGBTswitches, four inductors L1, L2, L3, L4 four diode D1, D2, D3, D4 four capacitors C1, C2, C3, C4 and two output capacitor  $C_01$ ,  $C_02$  and the load. This converter is operated in CCM. To ease the steady-state analysis few assumptions are made:

- 1. All the parasitic parameters of the semiconductor devices are neglected.

- 2. All the semiconductor devices are in ideal condition.

- 3. The voltage of the capacitors is assumed to be constant as the size of the capacitors is considered to be large enough.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication

# DesignandSimulation of High-Efficiency High Gain non Isolated Interleaved DC-DC Converter with Reduced Voltage Stress on the Devices

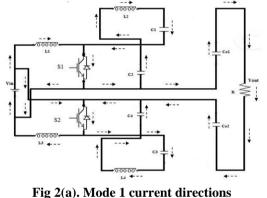

**Fig 1. Equivalent circuit of interleaved KY converter** The interleaved KY converter operates in two modes: A.Mode 1: The time interval for this mode is  $(t_0-t_1)$ .In this mode the switches  $S_1$ ,  $S_2$  are in on state and all the four diodes  $D_1-D_4$  are in off state. As the inductors are charged from the input source, the current through the inductors rises linearly. The capacitors  $C_1$  and  $C_3$  are charged and the capacitors  $C_2$ ,  $C_4$   $C_{01}$ ,  $C_{02}$  are discharged which were charged from the previous mode. The output capacitors also charge the load. Figure 2.(a) represents the current flow directions of mode 1. The voltage across the inductors are

| $V_{L1} = V_{in}$                                                                | (2)   |

|----------------------------------------------------------------------------------|-------|

| $V_{L2} = V_{C2} - V_{C1}$                                                       | (3)   |

| $V_{L3} = V_{in}$                                                                | (4)   |

| $\mathbf{V}_{\mathrm{L4}} = \mathbf{V}_{\mathrm{C4}} - \mathbf{V}_{\mathrm{C3}}$ | (5)   |

| D Made 2. The time internal for this mode                                        | :- (4 |

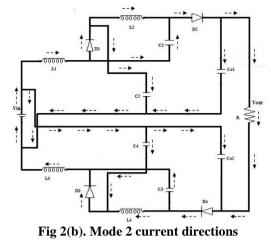

B.Mode 2: The time interval for this mode is  $(t_1-t_2)$ . In this mode, both the switches are in off state and all the four diodes are in on state. The current through the inductors decreases to its minimum value, now the capacitors  $C_1$  and  $C_3$  are discharged and the capacitors  $C_2$ ,  $C_4$ ,  $C_{01}$ ,  $C_{02}$ , Ro are charged through the diodes  $D_2$  and  $D_4$ . For the next timeperiod the switches  $S_1$  and  $S_2$  have turned on again which ends mode 2.Figure 2 (b) represents the current flow direction of mode 2. The voltage across the inductors are:

| $V_{L1} = V_{in} - V_{C2}$ | (6) |

|----------------------------|-----|

| $V_{L2} = -V_{C1}$         | (7) |

| VI VI VI                   | (0) |

$$V_{L3} - V_{in} - V_{C4}$$

(6)

$V_{L4} = -V_{C2}$  (9)

#### III. STEADY STATE ANALYSIS OF PROPOSED CONVERTER

To ease the analysis volt second balanced law of inductor is applied for the inductors  $L_1$ ,  $L_2$ ,  $L_3$ ,  $L_4$ :

$$V_{Li} = \int_{0}^{DT} (VLi) dt$$

(10)

$$V_{Li} = \int_{0}^{DTs} Vindt + \int_{DTs}^{Ts} (Vin - Vc2) dt$$

(11)

$$V_{L2} = \int_{0}^{DTs} (Vc2 - Vc1) dt + \int_{DTs}^{TS} (-Vc2) dt$$

(12)

$$V_{L3} = \int_{0}^{DTs} (Vin) dt + \int_{DTs}^{TS} (Vin - Vc4) dt$$

(13)

$$V_{L4} == \int_{0}^{DTs} (Vc4 - Vc3) dt + \int_{DTs}^{TS} (-Vc3) dt$$

(14)

# Fig 3.Key waveforms of interleaved ky converter in CCM

When KVL is applied in mode 1,the output voltage is  $Vo=V_{co1}-V_{in}+V_{co2}$  (15) Similarly in mode 2

| $V_{co1} = V_{c1} + V_{c2}$                                         | (16)        |     |

|---------------------------------------------------------------------|-------------|-----|

| $V_{co2} = V_{c3} + V_{c4}$                                         | (17)        |     |

| By equating equation 11,12,13 & 14                                  | to zero ,we | get |

| $\mathbf{V}_{c1} = \mathbf{V}_{c3} = \frac{D}{1-D} \mathbf{V}_{in}$ | (18)        |     |

| $\mathbf{V}_{c2} = \mathbf{V}_{c4} = \frac{1}{1-D} \mathbf{V}_{in}$ | (19)        |     |

| From The above equation 18 & 19                                     |             |     |

| $V_{col} = V_{co2} = \frac{D+1}{1-D} V_{in}$                        | (20)        |     |

Retrieval Number: 100.1/ijitee.L80221091220 DOI: 10.35940/ijitee.L8022.1091220

313 Blue Eyes Intelligence Engineering and Sciences Publication

Published By:

From equation 15 & 20 the voltage gain of the converter is  $M = \frac{Vo}{Vo} = \frac{Vco 1 - Vin + Vco 2}{(21)}$

Where

$$M = \frac{Vin}{1-D}$$

Design equations of the proposed converter Inductor

As we are analyzing in CCM, so the inductor values are obtained as

$I_L \ge \frac{\Delta Il}{2}$

$$\Delta I_{L1} = \Delta I_{L2} = \Delta I_{L3} = \Delta I_{L4} = \frac{0.2Volo}{Vin} = 1.5A$$

$$L_1 = L_2 = L_3 = L_4 = \frac{Vin * D}{\Delta IL * Fs} = 464 \mu H$$

# Capacitor

As from the voltage equations of the capacitor  $V_{C1}$ –Vc4 (18 & 19) the capacitor equations are obtained.Since the charges observed by all the capacitors is equal :

$$\Delta Q = \frac{Io * D}{\Delta Vc * Fs}$$

$$\Delta Vc = \frac{\Delta Q}{C}$$

Based on  $\Delta Vc$  the capacitor value here we use 1% but in the base, the paper may vary upto 5%

$C_{1} = C_{3} = \frac{0.72*0.68}{0.75*30*10^{3}} = 16 \mu F$   $C_{2} = C_{4} = \frac{0.72*0.68}{1.04*30*10^{3}} = 16 \mu F$   $C_{01} = C_{02} = \frac{0.72*0.68}{1.68*30*10^{3}} = 10 \mu F$

### IV. VOLTAGE STRESS

To select the proper ratings of the semiconductor devices the voltage stress of the converter is to be considered. Based on the operating principle of the proposed converter, the voltage stress on the switches and the diodes is :

$V_{ss}1=V_{ss}2=1/1$ -D  $V_{in}=29/1$ -0.72=103.5V  $V_{SD(1-4)=}$ -1/1-D  $V_{in}=-29/1$ -0.72=-103.5V

#### V. COMPARISON STUDY

The proposed converter is compared with some previously developed converters in terms of voltage gain, the voltage stress on power switches, efficiency, cost, and size. The voltage stress of the proposed converter is less than the other previously developed converters for different values of the duty cycle which indeed increases the converter efficiency and hence cost of the converter is reduced. Also, the voltage conversion ration and the voltage gain of the converter are more than the previously developed converters due to the interleaving technique of two modified step-up KY converter which is proposed in this project. The numbers of switches used here are less compared to previously developed converters.

Table 1:Comparsion of the proposed converter with present converters

| Proposed              | Reference                                                             | Reference                                                                                                                                                                                                  |

|-----------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Converter             | [1]                                                                   | [6]                                                                                                                                                                                                        |

| 1+3D/1-               | n+1+(n+1)D/1-                                                         | 2(KN+1)/1-                                                                                                                                                                                                 |

| D                     | D                                                                     | D                                                                                                                                                                                                          |

| 1/1-D V <sub>in</sub> | M+n+1/2n+1                                                            | M+1/2M                                                                                                                                                                                                     |

|                       |                                                                       |                                                                                                                                                                                                            |

|                       |                                                                       |                                                                                                                                                                                                            |

|                       |                                                                       |                                                                                                                                                                                                            |

| 2                     | 4                                                                     | 8                                                                                                                                                                                                          |

|                       |                                                                       |                                                                                                                                                                                                            |

| 2                     | 1                                                                     | 2                                                                                                                                                                                                          |

|                       |                                                                       |                                                                                                                                                                                                            |

| Small                 | complex                                                               | More                                                                                                                                                                                                       |

|                       |                                                                       | complex                                                                                                                                                                                                    |

| 96.6                  | 90.4                                                                  | 92.8                                                                                                                                                                                                       |

|                       | Converter<br>1+3D/1-<br>D<br>1/1-D V <sub>in</sub><br>2<br>2<br>Small | Converter         [1]           1+3D/1-         n+1+(n+1)D/1-           D         D           1/1-D V <sub>in</sub> M+n+1/2n+1           2         4           2         1           Small         complex |

# VI. SIMULATION RESULTS

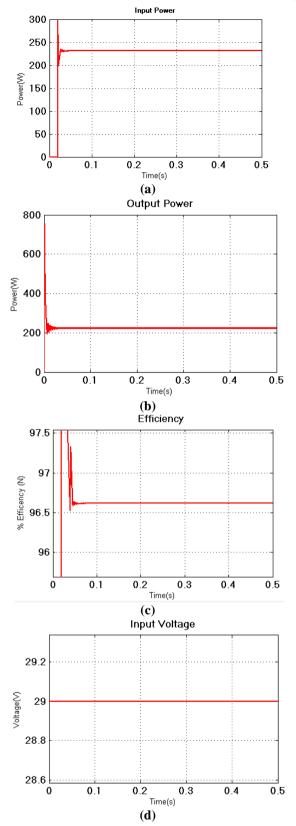

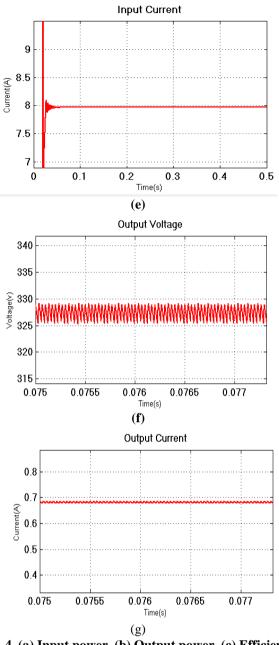

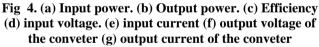

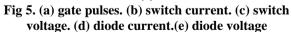

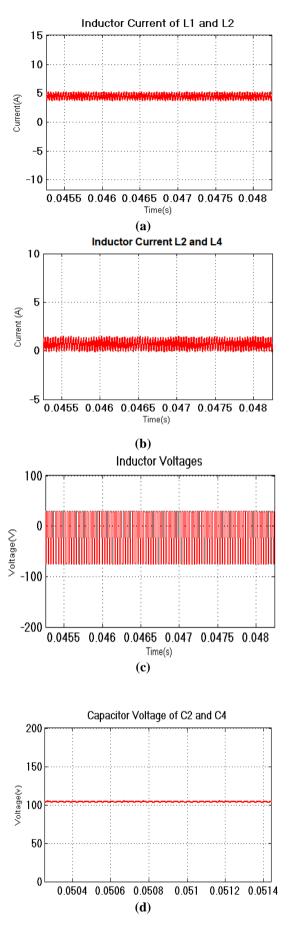

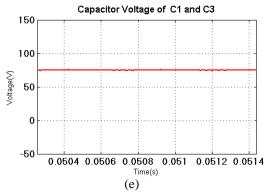

Simulation is carried out in Matlab/Simulink software. The parameter value used in this simulation is given in the below table 1. The graphical representation of voltage, current for different components of the proposed converter is shown in fig 4& 5. The switch voltage is less than the output voltage which reduces the stress on the switches, so the switches with low on-state resistance can be used. The efficiency of the proposed converter is 96.6% fig 4(c). The input power is 231W with an input voltage and current 29V and 9A represented in fig 4and the output power obtained is 225W the output voltage and current are represented in fig 4.The gate pulses are of 1V and the switch voltage V<sub>sw</sub> and current I<sub>sw</sub> is 100V and 9A represented in fig 5. The inductor voltage and current are represented in fig 6. The capacitor voltage V<sub>C4</sub> and V<sub>C2</sub> are represented in fig 7.

| ic ii. I al ameter values eseu in Simula |                               |  |

|------------------------------------------|-------------------------------|--|

| Specifications                           | Values                        |  |

| Input voltage                            | 29 V                          |  |

| Output voltage                           | 329 V                         |  |

| Output power                             | 225.5 Watt                    |  |

| Switching frequency                      | 30 kHz                        |  |

| Load Resistance                          | 480 Ω                         |  |

| Inductors                                | 464µH(4)                      |  |

| Capacitors                               | 22μF(2), 16μF(2),<br>100μF(2) |  |

# Table II: Parameter Values Used in Simulation

Fig 4: Simulation Diagram

# DesignandSimulation of High-Efficiency High Gain non Isolated Interleaved DC-DC Converter with Reduced Voltage Stress on the Devices

Published By: Blue Eyes Intelligence Engineering and Sciences Publication

316

Published By: Blue Eyes Intelligence Engineering and Sciences Publication

# DesignandSimulation of High-Efficiency High Gain non Isolated Interleaved DC-DC Converter with Reduced Voltage Stress on the Devices

Fig 6. (a) inductor current of  $L_1$  and  $L_3$ . (b) inductor current  $L_2$  and  $L_4$ . (c) voltage of inductors. (d) Capacitor voltage of C2 and C4. (e) Capacitor voltage of C1 and C3

#### VII. CONCLUSION

This paper proposes a new step-up non-isolated interleaved KY dc-dc converter. The proposed converter consist of two switches with low on-state resistances as the voltage stress on the switches is less. The modified interleaved KY converter has high voltage gain compared to the previously developed/conventional converters and due to low ripple in the input current, this is suitable for the PV system also. There can be further enhanced by using a PV array. The converter was operated in CCM and all the semiconductor devices were analyzed in steady-state The accuracy of the proposed converter is estimated in MATLAB/SIMULINK software. The voltage conversion ratio and the voltage gain of the converter are 11.34 for the duty cycle of 72%, which is more than that of input voltage due to the interleaving technique of two modified step-up KY converter. The voltage stress of the interleaved KY converter is less. The input voltage given to the converter is 29V and the boosted output voltage obtained is 329V. The interleaved KY converter output power obtained is 225W for an input power of 230W. The efficiency of the proposed converter is 96.6%. The gate pulses are of 1V which are obtained from the pulse generator given to the switch, diode voltage is 100V which is 3.25 times less than that of load voltage. The performance of the interleaved KY converter was studied.

#### REFERENCES

- H. Ardi, and A. Ajami, "Study on a high voltage gain SEPIC based DC-DC converter with a continuous input current for sustainable energy applications," *IEEE Transactions on Power Electronics*, vol. 33, no. 12. pp. 10403-10409,2018.

- S.H. Hosseini, F. Sedaghati, M. Sabahi, and G.B. Gharepetian, "Zero voltage switching analysis of modular isolated bidirectional DC-DC converter," *IEEE 27th Canadian Conference on Electrical and Computer Engineering (CCECE)*, Toronto, ON, Canada, May.2014.

- 3. M. Eskandarpour Azizkandi, F. Sedaghati, and H. Shayeghi, "Design of a new step-up DC-DC converter with high voltage gain for PV power application," *33rd International Power System Conference*, Tehran, Iran, October 2018.3

- M.R. Banaei, and H. Ajdar Faeghi Bonab, "High-efficiency transformerless buck-boost DC-DC converter," *International Journal of Circuit Theory and Applications*, vol. 45, no. 8, pp. 1129-1150, 2017.

- 5. K.I.Hwu,andY.T.Yau, "TwotypesofKYBuck–Boostconverters,"*IEEE Transactions on Industrial Electronics*, vol. 56, no. 8, 2009.

- R.Ismail, Neenu B "A High Voltage Gain Interleaved Boost Converter with Dual Coupled Inductor", International Journal of Engineering Research &Technology, Vol.4, ISSUE 09, SEPTEMBER 2015.

- 7. F . Sedaghati, M.Eskandarpour Azizkandi, S.HadiLatifi

Majareh,H.Shayeghi "A High-Efficiency Non-Isolated High-Gain Interleaved DC-DC Converter with Reduced Voltage Stress on Devices,"IEEE 10th International Power Electronics, Drive Systems and Technologies Conference (PEDSTC) 2019

#### **AUTHORS PROFILE**

Azra Fatima received a degree in Electrical and Electronics Engineering at Poojya Doddappa Appa College of Engineering Kalaburagi India, in 2018. I am Pursuing higher studies in the Power Electronics department Master of Technology at Poojya Doddappa Appa College of Engineering

Kalaburagi India 585102.

**Dr. M.S.Aspalli** received a B.E. degree in Electrical Engineering in 1991, M.E. in Power Electronics in 1997, and Ph.D. in 2014 from Gulbarga University, Gulbarga. He started his carrier as a lecturer in the Electrical Department at P.D.A.College of Engineering, Gulbarga and now he

is working there as Professor and P.G.Coordinator for Post Graduate course in Power Electronics under the Department of Electrical and Electronics Engineering. His fields of interest are Power Electronics and Drives, Power Quality Issues, Electric Vehicles' and its control. He has published more than 60 papers in national and international journals and conferences and he has published a book titled "Microcontroller Based Controller for Three Phase Induction Motor" with (ISBN-978-620-0-5349-8) publishers: Lambert Academic publishing. He is a life member of FIE, ISTE, IETE, ISLE, and ISCA. He has attended and awarded the certificate for The AICTE-UKIERI Technical LeadershipProgram i.e UK-INDIA Education and Research Initiative Program which is jointly organized by Dudley College, UK, and AICTE New Delhi. He has more than 20 years of experience and he has taught different subjects at UG and PG. at present, he is guiding 03 research scholars.

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication