# Vanumu Balaji, U. Subha, G Joga Rao

Abstract: Various types of new structures in multilevel inverters are evolving day by day. One among those is the reduced switch count type multilevel inverters. This inverter consists of low number of switches, gate driver components, and other switches like auxiliary switches. Depending on the value of the voltage sources we have symmetrical and asymmetrical multilevel inverters. In this paper, the seven level symmetrical inverter design is shown for seven levels in its output. The output voltage waveform is plotted and its FFT is performed and the THD values are shown. The inverter is simulated in SIMULINK software. Index Terms: Seven level MLI, inverter, and Modular Inverter.

Key Words: THD, FFT, Distortion factor.

#### I. INTRODUCTION

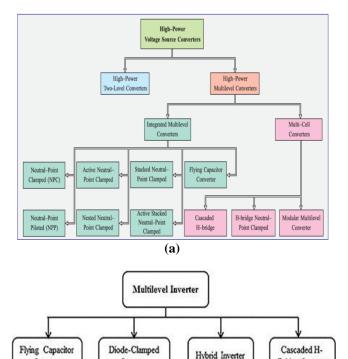

The voltage source converter plays vital role in the operation and control of HVDC systems. To provide smoother control, and effective power flows it is necessary to have voltage source converter in the HVDC systems. A voltage source converter converts the DC to AC or vice versa. The power conversion from one form to other is the most important requirement of HVDC systems[6]. There are several types in the voltage source converter. The basic types include conventional two level converters and multilevel converters. The classification of various voltage converters are shown in the next figure below.

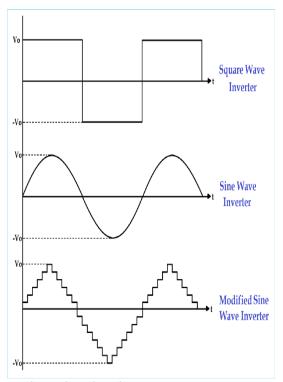

The other types of converters are current source converters (CSCs). Compared to CSCs, the topology and the operation of the VSCs are simple and cost effective. So, most of the applications like HVDC utilizes the voltage source converters only. The output voltage waveforms of various converters are shown in figure below.

It produces the square wave as output voltage waveform instead of a sinusoidal wave. SO, the quality of the output voltage produced by the conventional two levels VSC is very poor as shown in above figure. The topology of the single phase two level inverter is shown in the figure below.

The two levels VSC requires very less number of switches and other circuit components.

Manuscript received on May 29, 2021. Revised Manuscript received on July 26, 2021. Manuscript published on 30 July, 2021.

\* Correspondence Author

Mr. V Balaji\*, Pursuing MTech, Department of Power Electronics, Raghu Institute of Technology (Autonomous), Visakhapatnam (Andhra Pradesh), India.

Mrs. Uppili Subha, Assistant Professor, Department of EEE, Raghu Institute of Technology (Autonomous), Visakhaptanam (Andhra Pradesh), India.

**Dr. G Joga Rao,** Assistant Professor, Department of EEE, Raghu Institute of Technology (Autonomous), Visakhapatnam (Andhra Pradesh), India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<a href="http://creativecommons.org/licenses/by-nc-nd/4.0/">http://creativecommons.org/licenses/by-nc-nd/4.0/</a>)

It is free from auxiliary circuit components. So, the circuit is simple and the operation of the two level voltage source inverter is simple [5]. As the output voltage waveform is not pure sinusoidal waveform, now a day's multi level VSCs are utilized in the HVDC applications.

(b)

Figure 1 Classification of Multilevel Inverters.

The multi level VSCs produces approximate sinusoidal voltage as an output wave form as shown in the above figures. The main advantage of the MLVSC is, they produce good quality output voltage waveform compared to the square wave converters [4]. Various types in ML VSCs are

Diode clamped ML VSCs

Inverter

Inverter

- Capacitor Clamped ML VSCs

- Cascaded H-Bridge ML VSCs

Bridge Inverter

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication

© Copyright: All rights reserved.

Figure 2 various inverter output voltages.

The DC-MLI requires clamping diodes to produce the multilevel output voltage. The output voltage and the circuit topology of the single phase five level inverter are shown in the above figures. The circuit components in this type of VSCs are more compared to other. So these inverters require high cost compared to other [7]. Due to the increased number of elements, the losses increases and the control becomes complex.

The FC-MLI require relatively lesser number of diodes when compare with previous one. But, huge numbers of flying capacitors are required in this. Frequent failure of capacitors creates problem in this type of converters. The circuit topology and the output waveforms for this are shown in the figures below.

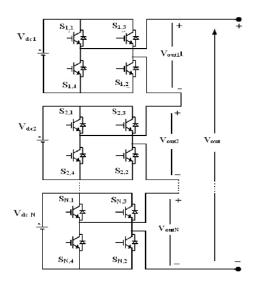

Out of all VSCs, these types of VSCs are simple and flexible. These VSCs are well suited for any applications. By connecting several numbers of H-bridges in series, it is possible to obtain the good quality output voltage waveform than any other type VSCs. It requires less number of circuit components compared to the other type of VSCs. The importance for these VSCs is high compared to the any other type of converters [3]. The circuit diagram and the output voltage wave form of single phase five level cascaded H-Bridge inverter are shown in figure below.

In this paper, the attention is shown towards the reduced switch count MLIs. The simulations are shown for the seven levels in output voltage waveform. The simulations are done in SIMPOWERSYSTEMS tool.

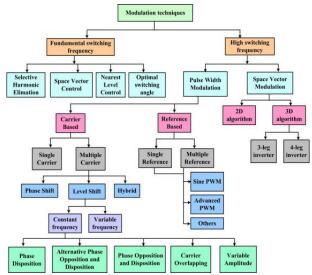

Figure 3 Classifications of Modulation Methods.

#### II. PROPOSED SEVEN LEVEL INVERTER

In this section the proposed topology of the inverter with other conventional topologies is shown. The circuit diagrams are presented and the switching tables are shown.

$$V_o = V_{01} + V_{o2} + V_{o3} + V_{on} \tag{1}$$

$$N_{Step} = 2n + 1 \tag{2}$$

$$V_{omax} = n \times V_{dc} \tag{3}$$

Figure 4 CHB MLI.

$$N_{\text{step}} = 2^{n+1} - 1 \ \text{if} V_j = 2^{j-1} V_{\text{dc}} \ \text{for} \ j = 1, 2, ... \, , n \eqno(4)$$

$$N_{\text{step}} = 3^n$$

if  $V_i = 3^{j-1}V_{dc}$  for  $j = 1, 2, ..., n$  (5)

$$V_{omax} = (2^n - 1)V_{dc} \text{ if } V_j = 2^{j-1}V_{dc} \text{ for } j = 1, 2, ..., n$$

(6)

$$V_{omax} = \left(\frac{3^{n}-1}{2}\right) V_{dc}$$

if  $V_{j} = 3^{j-1} V_{dc}$  for  $j = 1, 2, ..., n$  (7)

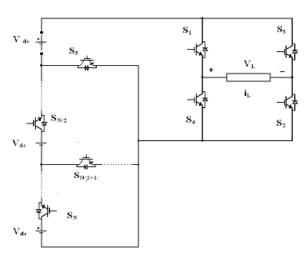

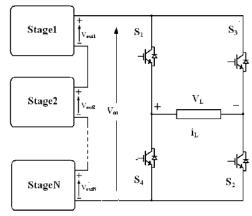

# 2.1 Proposed Topology

The circuit diagram of the proposed topology is shown in figure below. It requires less number of switches compare to the conventional circuits.

Figure 5 Proposed seven level topology.

Figure 6 n - Level Topology.

$$N_{Step} = 2n + 1 \tag{8}$$

$$V_{omax} = n \times V_{dc} \tag{9}$$

$$V_o = V_{vdc} + \frac{n-1}{2} V_{2vdc} + \frac{n-1}{2} V_{3vdc}$$

$$if \ n = odd \ number \qquad n = 3,5, \dots. \tag{10-a}$$

$$V_{o} = V_{vdc} + \frac{\rm n}{2} \, V_{2vdc} + \, \left( \frac{\rm n}{2} - 1 \right) V_{3vdc} \label{eq:volume}$$

$$if \ n = even \ number \tag{10-b}$$

$$N_{step} = 5n - 2$$

if  $n = odd$  number (11-a)

$$N_{step} = 5n - 3$$

if  $n = even$  number (11-b)

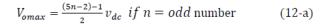

$$V_{\text{omax}} = \frac{(5n-3)-1}{2} v_{dc} \text{ if } n = even \text{ number}$$

(12-b)

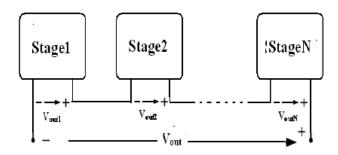

Figure 7 n - Stages.

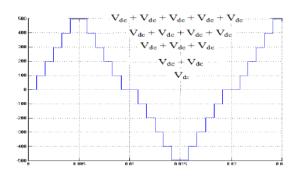

Figure 8 Typical output waveform.

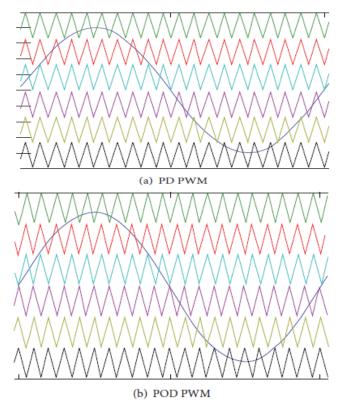

# III. MODULATION METHOD

In this section, the modulation method employed for the proposed MLI is presented along with the pulse generation waveforms.

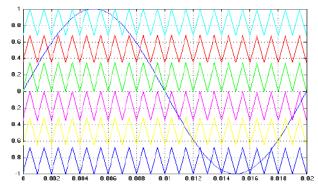

The conventional SPWM technique is employed in presented circuit. A triangular carrier wave is employed. Multiple numbers of carrier waves are used. A sinusoidal modulating signal is employed.

Following figure shows the pulse generation using SPWM modulation method.

Figure 9 Triangular carrier wave.

183

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication

© Copyright: All rights reserved.

Figure 10 various types in SPWM.

# IV. SIMULATION RESULTS

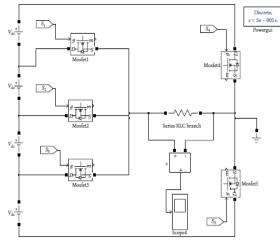

All the simulations result that is obtained using SIMULINK is presented in this section. All the simulation studies are carried out in SIMPOWERSYSTEMS tool. Following is the simulation circuit of the proposed inverter.

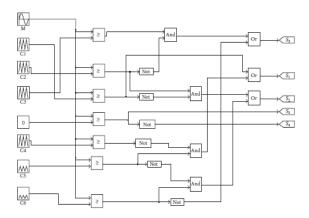

Figure 11 Simulation of MLI.

The proposed circuit consists of seven/eight main switches in the circuit. Following is the PWM pulses generation circuit simulated in MATLAB.

Figure 12 PWM pulse generation circuit.

|        |       |       |       |       |       | L/4               |

|--------|-------|-------|-------|-------|-------|-------------------|

| SL no. | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | Output<br>voltage |

| 1      | OFF   | OFF   | ON    | OFF   | ON    | +Vdc              |

| 2      | OFF   | ON    | OFF   | OFF   | ON    | +2Vdc             |

| 3      | ON    | OFF   | OFF   | OFF   | ON    | +3Vdc             |

| 4      | OFF   | OFF   | OFF   | OFF   | OFF   | 0                 |

| 5      | ON    | OFF   | OFF   | ON    | OFF   | -Vdc              |

| 6      | OFF   | ON    | OFF   | ON    | OFF   | -2Vdc             |

| 7      | OFF   | OFF   | ON    | ON    | OFF   | -3Vdc             |

|        |       |       |       |       |       |                   |

The above table is the switching states generation circuit for all the main switches.

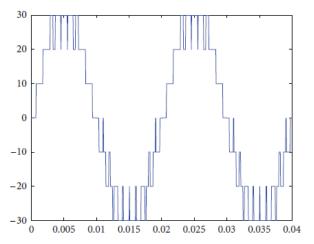

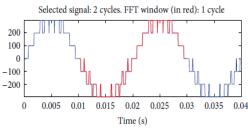

Figure 13 Output voltage and its FFT analysis.

Retrieval Number: 100.1/ijrte.B60320710221 DOI: 10.35940/ijrte.B6032.0710221 Journal Website: www.ijrte.org

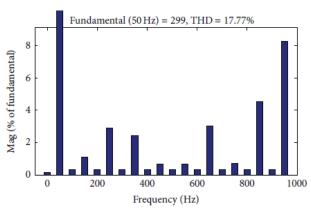

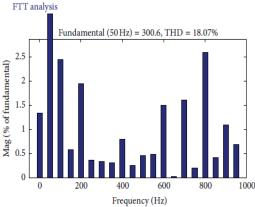

Figure 14 Output using APOD.

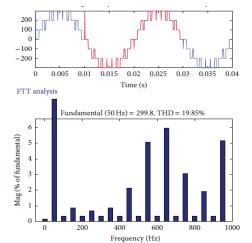

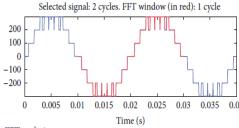

Figure 15 Using PD.

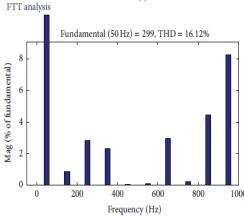

Figure 16 Using POD.

Retrieval Number: 100.1/ijrte.B60320710221 DOI: 10.35940/ijrte.B6032.0710221 Journal Website: www.ijrte.org From Figure 13 to Figure 15, it is clear that the output voltage of the proposed inverter is having low total harmonic distortion compared with other topologies which are similar to the presented or considered for the analysis in this paper. The THD value is limited in between 17% to 19% depending on the type of SPWM method employed for the generation of pulses for the main switches in the inverter. The lower order harmonics also well in control for the topology that is proposed in this work

# V. CONCLUSIONS

The performance of the proposed seven level symmetrical MLI with SPWM method is evaluated and the results are presented in this paper. Compared to the other so many existing topologies, the proposed topology requires very less number of switches, and gate driver components. Hence, in order to achieve good quality output voltage, it is suggested for the usage of the proposed topology with the SPWM modulation methods.

#### REFERENCES

- Chen, J., Liu, D., Ding, K., Wang, C., & Chen, Z. (2018, September). A single-phase double T-type seven-level inverter. In 2018 IEEE Energy Conversion Congress and Exposition (ECCE) (pp. 6344-6349). IEEE.

- Shaikh, R. R., & Rana, J. R. (2016, April). Single phase seven level inverter. In 2016 International Conference on Energy Efficient Technologies for Sustainability (ICEETS) (pp. 306-310). IEEE.

- Ali, A. I. M., Sayed, M. A., & Mohamed, A. A. (2021). Seven-Level Inverter with Reduced Switches for PV System Supporting Home-Grid and EV Charger. *Energies*, 14(9), 2718.

- Hsieh, C. H., Liang, T. J., Chen, S. M., & Tsai, S. W. (2016). Design and implementation of a novel multilevel DC–AC inverter. *IEEE Transactions on industry applications*, 52(3), 2436-2443.

- Weidong, J., Qunjing, W., & Xiaofeng, C. Q. S. (2009). SVPWM strategy for three-level inverter based on svpwm strategyfor twolevel inverter. *Transactions of China Electrotechnical Society*, 01.

- Venkataramanaiah, J., Suresh, Y., & Panda, A. K. (2017). Design and development of a novel 19-level inverter using an effective fundamental switching strategy. *IEEE Journal of Emerging and* Selected Topics in Power Electronics, 6(4), 1903-1911.

- Atkar, D., Udakhe, P. S., Chiriki, S., & Borghate, V. B. (2016, December). Control of seven level cascaded H-Bridge inverter by hybrid SPWM technique. In 2016 IEEE international conference on power electronics, drives and energy systems (PEDES) (pp. 1-6). IEEE.

- Meenakshi, M., Nagarajan, R., Banupriya, R., & Devi, M. D. (2017). Stepped Multicarrier SPWM Techniques for Seven-Level Cascaded Inverter. *International Journal of Emerging Technologies in Engineering Research (IJETER)*, 5(12), 43-49.

- Khan, S. A., Barzegarkhoo, R., Guo, Y., Siwakoti, Y., Khan, M. N. H., Lu, D. D. C., & Zhu, J. (2021). Topology, Modeling and Control Scheme for a New Seven-level Inverter with Reduced DC-Link Voltage. *IEEE Transactions on Energy Conversion*.

- Memon, M. A., Mekhilef, S., Mubin, M., & Aamir, M. (2018).

Selective harmonic elimination in inverters using bio-inspired intelligent algorithms for renewable energy conversion applications: A review. Renewable and Sustainable Energy Reviews, 82, 2235-2253.

# **AUTHORS PROFILE**

Mr. V Balaji, is pursuing MTech (Power electronics) in Raghu Institute of Technology (Autonomous) Visakhapatnam. He obtained B.Tech (Electrical and Electronics Engineering)

Published By:

Blue Eyes Intelligence Engineering

and Sciences Publication

© Copyright: All rights reserved.

Mrs. Uppili Subha, is working as an Assistant Professor in the department of EEE, Raghu Institute of Technology (Autonomous) Visakhaptanam. She Obtained B.Tech (Electrical Engineering) from Avanthi Institute of Engineering and Technology, Bhogapuram in 2010 and M.E(PED&C) from University Andhra in the vear 2015, Visakhapatnam. She has more than 9 Years teaching experience in various colleges and

published papers in various reputed international journals. She attended Various International Conferences and Faculty Development Programs. His area of interest includes power Electronics, Renewable Energy Technologies. She is a Life member of Indian Society for Technical Education (ISTE).

Dr. G Joga Rao, is working as an associate professor in the department of EEE, Raghu Institute of Technology (Autonomous) Visakhapatnam. He obtained B.Tech (Electrical Engineering) and MTech (Electrical Power Engineering) degree from J.N.T University, Hyderabad, in 2004 and 2007 respectively. He completed his doctoral program from

S.R University, India in 2017. He has more than 15 years of teaching experience in various colleges and published more than 50 publications in various reputed international journals. His area of interest includes Energy Systems, Power Electronics and Renewable Energy Technologies. He is a life member of the Indian Society for Technical Education and Institute of Engineers IE.

Retrieval Number: 100.1/ijrte.B60320710221 DOI: 10.35940/ijrte.B6032.0710221 Journal Website: www.ijrte.org

186

www.iirte.org