# Controlled Silicidation of Silicon Nanowires using Flash Lamp Annealing

Muhammad Bilal Khan,\*,†,‡,¶ Slawomir Prucnal,† Sayantan Ghosh,† Dipjyoti Deb,†,‡ René Hübner,† Darius Pohl, $\S$ ,¶ Lars Rebohle,† Thomas Mikolajick, $\P$ ,¶ Artur Erbe,†,¶ and Yordan M. Georgiev\*,†, $\bot$

†Institute of Ion Beam Physics and Materials Research, Helmholtz-Zentrum

Dresden-Rossendorf, Dresden, 01328, Germany

‡International Helmholtz Research School for Nanoelectronic Network, Helmholtz-Zentrum

Dresden-Rossendorf, Dresden, 01328, Germany

¶ Technische Universität Dresden, Center for Advancing Electronics Dresden (CfAED),

Dresden, 01069, Germany

§Dresden Center for Nanoanalysis (DCN), CfAED, Technische Universität Dresden, Dresden, 01069, Germany

||Namlab gGmbH, Nöthnitzer Strasse 64, Dresden, 01187, Germany ⊥On leave of absence from the Institute of Electronics at the Bulgarian Academy of Sciences, 72, Tsarigradsko chaussee blvd., Sofia 1784, Bulgaria

E-mail: m.khan@hzdr.de; y.georgiev@hzdr.de

#### Abstract

Among other new device concepts, nickel silicide (NiSi<sub>x</sub>)-based Schottky barrier nanowire transistors are projected to supplement down-scaling of the complementary metal-oxide-semiconductor (CMOS) technology as its physical limits are reached. Control over the NiSi<sub>x</sub> phase and its intrusions into the nanowire are essential for superior

performance and down-scaling of these devices. Several works have shown control over the phase, but control over the intrusion lengths has remained a challenge. To overcome this, we report a novel millisecond-range flash-lamp-annealing (FLA)-based silicidation process. Nanowires are fabricated on silicon-on-insulator substrates using a top-down approach. Subsequently, Ni silicidation experiments are carried out using FLA. It is demonstrated that this silicidation process gives unprecedented control over the silicide intrusions. Scanning electron microscopy and high-resolution transmission electron microscopy are performed for structural characterization of the silicide. FLA temperatures are estimated with the help of simulations.

#### Introduction

Today, silicides are mainly used in the contacts and as local interconnects in nanoelectronic and photonic devices. Furthermore, Ni-silicides have also been used in innovative devices, such as Schottky-barriers-based reconfigurable field-effect transistors (RFETs), <sup>1</sup> and are mostly formed by a high-temperature-induced interfacial reaction of Ni with Si. The Ni diffuses across the Si, forming single or multiple compounds.<sup>2</sup> This process is known as reaction phase formation.<sup>3,4</sup> The Ni-silicide phase can be controlled by the reaction conditions, 5 the Ni quantity and quality, 6,7 as well as the strain, 8,9 and the crystal orientation 10 of the Si nanowires. Various Ni-silicide phases exist. Their formation on thin-film and bulk Si substrates has been extensively studied.  $^{11-16}$  With the continuous downscaling of devices, the properties and formation of nickel silicides at nanoscale came under investigation. <sup>17–35</sup> Wu et al.  $^{36}$  were the first to report the transformation of Si NWs into a single crystalline low resistivity NiSi NWs. They transformed Ni covered regions of the NW into NiSi by annealing at 550 °C in a forming gas atmosphere. The first report on axial silicide growth into the nanowires and formation of abrupt Si-silicide Schottky junctions was given by Weber et al.  $^{37}$ In this case, annealing at 470 °C in Ar atmosphere led to axial diffusion of Ni into the Si NW. They demonstrated Schottky barrier based transistors using this process. A third variant was first reported by Kosloff et al.  $^{38}$ , where diffusion of Ni into Si nanopillars at 200-400  $^{\circ}$ C was used to form Si-NiSi core-shell nanowire.

In Schottky-barrier-FETs (SBFETs), the Schottky barrier height and interface quality depend on the phase of the silicide adjacent to the Si channel. <sup>1,39</sup> In this context, NiSi<sub>2</sub> is of special interest for SBFETs, as its Fermi level is near mid-gap in relation to the Si bandgap. Moreover, it has a small lattice mismatch with Si, enabling the formation of an atomically abrupt Si-NiSi<sub>2</sub> interface with good crystalline quality. <sup>1,40</sup> In planar thin-film reactions, Tu et al. <sup>41</sup> reported the formation of NiSi<sub>2</sub> above 750°C, while Tung et al. <sup>42</sup> demonstrated its formation at 450°C. In the case of Si nanowires, formation of NiSi<sub>2</sub> is reported at different temperatures, e.g. 550°C, <sup>8</sup> 450°C, <sup>10</sup> and 360°C <sup>43</sup>. Appenzeller et al. <sup>31</sup> had proposed the vol-

ume diffusion of Ni in Si nanowires as the rate-limiting factor, while Katsmann et al. 44 argued that the experimentally observed fast Ni diffusion at relatively low temperatures cannot be explained by volume diffusion. They proposed Ni surface diffusion to explain these fast diffusion rates. Chen et al. 45 and Dellas et al. 46 studied the dependence of Ni-silicide growth on the reaction temperature. Later, Tang et al. 47 proposed single silicide phase growth based on three distinct mechanisms, which are Ni diffusion through the Ni/Ni-silicide interface, diffusion of Ni across the already silicided segment of the nanowire, and conversion to a new silicide layer at the growth front. Even though researchers have extensively studied 3,7,48,49 the silicide growth kinetics and the Ni-silicide phase formation using various annealing techniques, such as rapid thermal annealing (RTA), vacuum furnace annealing, or in-situ transmission electron microscopy (TEM) annealing, 2 none of the works reported a reproducible process with controlled silicide lengths until now. Some works demonstrated the formation of short-channel devices. Tang et al.<sup>50</sup> presented a 17 nm-long Si channel with the help of in-situ TEM annealing at  $425^{\circ}$ C. Lu et al.  $^{51}$  demonstrated Si channel lengths down to  $2\,\mathrm{nm}$ with Ni-silicide/Si/Ni-silicide interfaces. However, they pointed out the variable growth rates of the Si/Ni-silicide interfaces as well. A reproducible silicidation process with homogeneous silicide intrusions (supporting information figure S1) is required for down-scaling and largescale integration of SBFETs. Scattering in silicide intrusions, as reported in our preceding work carried out using RTA, 35 could not be overcome using commonly utilized annealing approaches such as RTA. Here, we present an extension of our previous work 52 with a focus on the development of a controlled silicidation process using millisecond-range flash-lamp annealing (FLA). A brief introduction and comparison of different annealing techniques is presented in supporting information table S1. FLA offers sample surface treatment, rapid temperature ramp-up, and ramp-down properties unlike RTA.

#### Results and Discussion

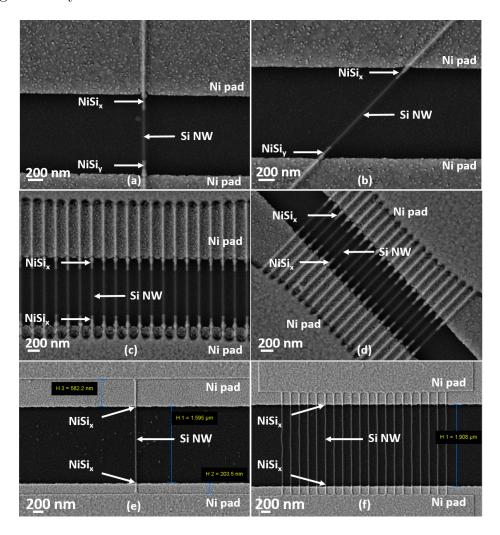

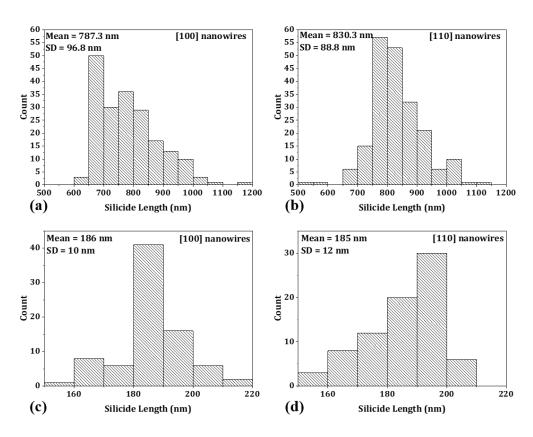

Various flash energy densities (70 Jcm<sup>-2</sup> - 90 Jcm<sup>-2</sup>) and pulse durations (3 ms to 20 ms) were used in a N<sub>2</sub> environment for the development of the silicidation process. Scanning electron microscopy (SEM) micrographs of samples obtained by a 90 Jcm<sup>-2</sup> flash energy density with 6 ms pulse duration process are presented in figure 1 (a-d). The silicide lengths are about 200 nm in both [110]- and [100]-orientated nanowires (figure 1 (a) and (b)). In the case of nanowire arrays (figure 1 (c) and (d)), a standard deviation (SD) of up to 6.5% is observed for the silicide intrusion lengths, which is significantly smaller compared to the values reported by an RTA-based process. <sup>35</sup> The width of the nanowires varies in these arrays due to the proximity effect in the electron beam lithography (EBL) process.<sup>53</sup> This effect causes exposure of the inner nanowires of the arrays with higher electron doses compared to the outer nanowires due to the back-scattered electrons coming from the adjacent nanowires. As a result, the width of the outer nanowires is a few nm smaller than that of the inner This width difference is large enough to affect the silicide lengths, as these lengths show an inverse dependence on the squared diameter of the nanowires.  $^{31}$  Figure 2 presents histograms highlighting the variation of the silicide intrusion lengths of the nanowire arrays annealed using FLA and RTA. After RTA, the SD of the silicides length is ca. 12.3%.

Next, processes with shorter pulse duration were explored, as they provide faster heating and cooling rates. <sup>54,55</sup> Symmetric silicide intrusions of 20 nm length were obtained after FLA at 70.4 Jcm<sup>-2</sup>, 3 ms (figure 1 (e) and (f)). Silicidation of the complete nanowire cross-section (nanowire height = 20 nm) was confirmed with scanning TEM (STEM) of the nanowire (supporting information figure S2) using a focused-ion-beam (FIB)-prepared TEM lamella. It is noted that the vertical (perpendicular to the sample surface) and axial (along the nanowires) intrusions of the silicide are of similar length in this case, indicating an equivalent vertical and axial silicidation rate. Using this FLA-based silicidation process, the position of the Schottky junctions can be precisely controlled, as the Ni contacts can be accurately placed with the lithography and lift-off processes. Unreacted Ni can be selectively etched

away using a wet chemical process, e.g., Piranha solution.<sup>34</sup> Moreover, the FLA-based process is free of unwanted effects such as breakage of silicide segments reported in other studies.<sup>5,43</sup> Thus, this state-of-the-art silicidation process can be used to fabricate scaled-down SBFETs with a high device yield.

Figure 1: Top-view SEM micrographs showing silicidation in (a) [110]- and (b) [100]-oriented nanowires. Homogeneous and symmetric silicide intrusions can be seen. (c) and (d) show silicided [110]- and [100]-oriented nanowire arrays, respectively. The annealing parameters were  $90\,\mathrm{Jcm^{-2}}$  flash energy density and  $6\,\mathrm{ms}$  pulse duration. (e) and (f) show silicidation in nanowires when FLA was performed at  $70.4\,\mathrm{Jcm^{-2}}$  flash energy density and  $3\,\mathrm{ms}$  pulse duration. All annealing processes were performed in  $N_2$  environment.

Figure 2: Histograms showing the distribution of the Ni-silicide lengths in the nanowires (a, b) RTA- (450 °C in a forming gas environment for 80 s) <sup>35</sup> and (c, d) FLA-based (6 ms, 90 Jcm<sup>-2</sup>) silicidation processes. The FLA-based process shows shorter silicide lengths compared to the RTA process. Both the silicidation length and the standard deviation (SD) of the silicide lengths are significantly reduced for the FLA process.

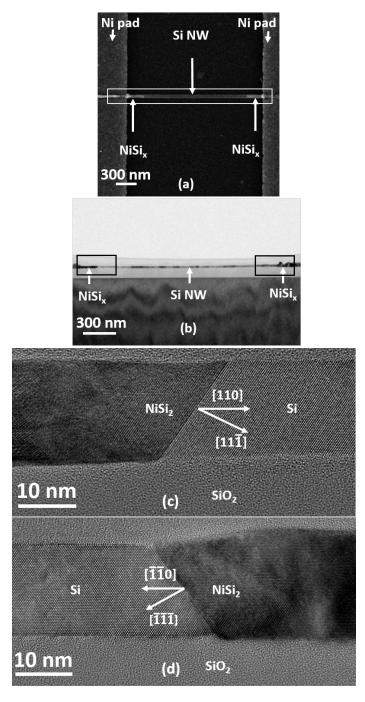

High-resolution transmission electron microscopy (HRTEM) was performed to study the Ni-silicide phase formation and the quality of the Schottky junctions. Therefore, a TEM lamella including a longitudinal section of a [110]-oriented nanowire was prepared (figure 3 (a) and (b)). Figure 3 (c) and (d) illustrate the formation of atomically sharp Si/Ni-silicide interfaces at both ends of the nanowire. Moreover, the interface is a shared, energetically most favorable (111) plane, in accordance with the simulation results reported in our previous work.<sup>35</sup> Furthermore, fast Fourier transformation reveals the formation of NiSi<sub>2</sub> having exactly the same orientation as the interfacing silicon. It was reported in <sup>51,56,57</sup> that Si/NiSi interfaces result in strained Si nanowire segments or dislocations to relax this strain. However, in our case, no dislocations are observed in the HRTEM micrographs. This is attributed to a lower lattice mismatch of the Si-NiSi<sub>2</sub> interface (0.4%) in comparison to that of the Si/NiSi interface (5.6%). <sup>16,57</sup>

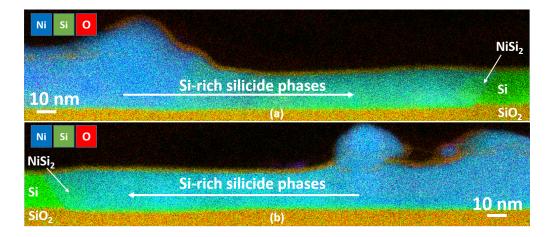

Energy-dispersive X-ray spectroscopy (EDXS) was applied to study the element distribution in the sectioned nanowire (figure 4). The measurements confirmed the formation of the Si-rich silicide NiSi<sub>2</sub> at the Si/Ni-silicide interface. Toward the Ni pads, i.e. away from the Si region, the concentration of Ni increases, and more Ni-rich phases are expected to form near the Ni reservoir. <sup>8,50</sup> Moreover, an expansion of the nanowire diameter in these regions is seen, as Ni-rich phases (e.g. Ni<sub>31</sub>Si<sub>12</sub>, Ni<sub>3</sub>Si<sub>2</sub>) have higher unit volume. <sup>16</sup> The thin oxide coating covering the nanowire is likely to be native SiO<sub>2</sub>. The formation of such SiO<sub>2</sub> layers has also been seen in previous studies of nanowire silicidation. <sup>58,59</sup>

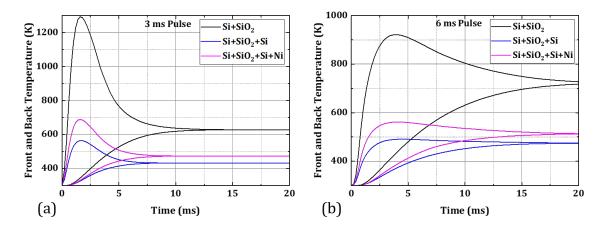

Temperature simulations were performed for both sets of FLA parameters used in this study, i.e. 6 ms at 3.6 kV flash voltage and 3 ms at 4.3 kV flash voltage, to estimate the temperature reached during the corresponding annealing processes. Under these conditions, the energy densities on the sample surface, as obtained from calibration, were 90 Jcm<sup>-2</sup> and 70.4 Jcm<sup>-2</sup>, respectively. The corresponding temperature profiles and extracted parameters are presented in figure 5 and table 1, respectively. The temperature reached its peak value quicker in the 3 ms process, as shorter pulses are expected to reach the peak temperature

Figure 3: (a) SEM micrograph of a silicidized [110]-oriented nanowire annealed in  $N_2$  environment at 90 Jcm<sup>-2</sup> flash energy density and 6 ms pulse duration. Subsequently, the nanowire was sectioned along its long axis, as indicated by the rectangular box. (b) Bright-field TEM micrograph of the nanowire section. (c, d) HRTEM of the nanowire section at the positions marked by the two rectangular boxes in panel (b). and showing the Si/Ni-silicide Schottky junctions formed in the nanowire.

Figure 4: (a, b) Element distributions between the Si/Ni-silicide interface region and the Ni pad at both ends of the nanowire depicted in figure 3. While NiSi<sub>2</sub> forms directly at the interface to silicon, the Ni concentration of the formed silicides increases toward the Ni-pad. Blue, green, and red color represent Ni, Si, and Oxygen content, respectively.

quicker. 55 The peak temperature of this process was also higher than that of the 6 ms process, while the equilibrium temperature (the point where the front- and back-side of the samples have an equal temperature) in the 6 ms process was higher due to the higher energy density of this process. The temperature ramp-down depends on various material properties and annealing parameters. 55 It has been shown that heat dissipation through heat convection by the annealing gas or thermal radiation does not have any significant effect on cooling in the range of ms. <sup>54</sup> Instead, the decrease in the surface temperature on a very short time scale is governed by heat conduction. However, the heat conduction coefficient of a material does not have a significant influence on the fast surface temperature decay, as a material with a higher coefficient will lead to a shallower heat gradient, resulting in a smaller difference between the peak and the equilibrium temperature of the surface. It is the pulse decay time that has a significant impact on the cooling rate. The shorter the pulse, the higher the temperature ramp-up and the cooling rate, as the shorter pulses have a faster decay. The temperature ramp-down, caused by thermal conduction within the layer stack, is largely dependent on the pulse duration. Therefore, a faster temperature ramp-down to equilibrium temperature was expected for the shorter 3 ms pulse. In contrast to this, the decay of the equilibrium temperature towards room temperature takes place on time scales of 100 ms and longer. Thus, longer silicide lengths were seen in the case of the higher equilibrium temperature, namely for the 6 ms process.

Figure 5: Temperature simulations of a (a) 6 ms,  $90\,\mathrm{Jcm^{-2}}$  and (b) 3 ms,  $70.4\,\mathrm{Jcm^{-2}}$  pulse for the three indicated material stacks. For each stack, the upper and lower curves are the temperature profiles of the front and the back-side of the sample, respectively. The temperature ramp-up and ramp-down are faster for a shorter pulse.

#### Summary

In summary, a novel FLA-based silicidation process was developed to overcome the problem of long and uneven distribution of Ni-silicide intrusions into the nanowires. We found that a 70.4 Jcm<sup>-2</sup>, 3 ms process leads to short, homogeneous, and symmetric silicide intrusions. The silicidation process is free of adverse effects, such as nanowire kinks and breakage. Temperature simulations of the FLA process reveal that the 70.4 Jcm<sup>-2</sup>, 3 ms process shows faster temperature ramp-up and ramp-down than the 90 Jcm<sup>-2</sup>, 6 ms process, giving better control over the silicide intrusions in the former case. HRTEM of a longitudinal nanowire section illustrates the formation of atomically abrupt NiSi<sub>2</sub>/Si/NiSi<sub>2</sub> interfaces, confirmed by element distribution analysis. Thus, the 70.4 Jcm<sup>-2</sup>, 3 ms FLA-based process can be used to form Schottky junctions at the desired positions with the help of lithography. Thereby,

the fabrication of scaled-down Schottky-barrier devices with high yield could be facilitated.

#### Experimental

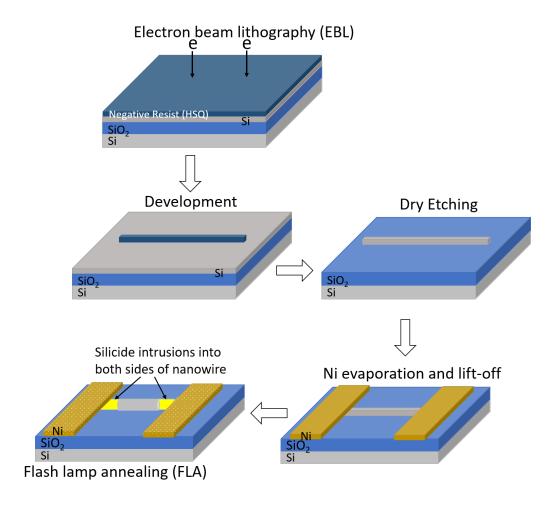

$1\times1$  cm<sup>2</sup> silicon-on-insulator (SOI) samples with (001) orientation were obtained by dicing a wafer consisting of a 20 nm-thick lightly p-doped silicon (Si) layer, a 102 nm buried oxide (BOx) layer, and a 775 µm Si carrier wafer. Single nanowires and nanowire arrays were fabricated on SOI substrates in [100]- and [110]-orientations. Nanowire fabrication is well known and widely used. Nanowires can be fabricated mainly by a bottom-up or a top-down approach. The bottom-up approach, e.g., vapor-liquid-solid (VLS) method, makes use of small units to assemble larger structures, while in the top-down fabrication approach, small structures are fabricated by subtracting material, e.g. by etching, from the bulk. Both of these approaches have distinct advantages and disadvantages to. <sup>60</sup> While the bottom-up approach can be used to grow a large number of smooth nanowires, top-down fabrication is a pre-requisite for large scale integration of devices. The top-down approach was followed in the present work considering the requirements of integrated circuits. First, the SOI substrates were cleaned in a piranha solution for 15 min, followed by successive cleaning in ultrasonic baths of acetone, isopropanol (IPA), and deionized (DI) water for 5 min each. Afterward, the samples were dehydrated by baking at 90°C for 3 min on a hotplate. A 6% hydrogen silsesquioxane (HSQ) solution, a negative tone resist, supplied by Dow Corning (X-1541), was diluted to a 2% concentration in methyl isobutyl ketone (MIBK) and spin-coated on the substrates at 2000 rpm for 30 s to produce a 40 nm-thick HSQ layer. Spin coating was followed by baking of the samples at 90°C for 3 min on the hotplate. Electron beam lithography (EBL) was carried out using a Raith e-Line Plus system at an acceleration voltage of 10 kV, 1200 µC cm<sup>-2</sup> dose, 30 µm aperture size, and 2 nm area beam step size. After the exposure, samples were developed with a high-contrast tetramethylammonium hydroxide (TMAH)-based development process. <sup>61</sup> The process steps were 15 s immersion in 25% TMAH, 30 s immersion in MF 319, 1 min rinse in DI water, and 30 s immersion in IPA. To anisotropically transfer the HSQ patterns into the device layer, SENTECH Inductively Coupled Plasma Reactive Ion Etching (ICP-RIE) SI 500 tool was used. The etching process parameters were 10 sccm  $SF_6$ , 20 sccm  $C_4F_8$  and 5 sccm  $O_2$  flow rates, 0.9 Pa chamber pressure, 400 W ICP power, and 12 W RF power. After etching of the silicon nanowires, the HSQ etch mask was removed by dipping the sample in a 1% hydrofluoric acid (HF) solution for 1 min. This was followed by the placement of Ni contacts at both ends of the nanowires using EBL, metal deposition (with Bestec e-beam evaporation tool), and lift-off. Subsequently, FLA experiments were performed for silicidation of the nanowires. Afterward, SEM (using the Raith e-Line Plus system) was performed to inspect the samples. A schematic of the complete fabrication flow is presented in figure 6.

Figure 6: Schematic of the fabrication process flow

Bright-field and high-resolution TEM imaging were performed on an image- $C_s$ -corrected Titan 80-300 microscope (FEI) operated at an accelerating voltage of 300 kV. High-angle annular dark-field scanning transmission electron microscopy (HAADF-STEM) imaging and spectrum imaging analysis based on energy-dispersive X-ray spectroscopy (EDXS) were done at 200 kV with a Talos F200X microscope equipped with an X-FEG electron source and a Super-X EDX detector system (FEI). Before (S)TEM analysis, the specimen, mounted in a high-visibility low-background holder, was placed for 8 seconds into a Model 1020 Plasma Cleaner (Fischione) to remove possible contamination. The preparation of the TEM specimens containing the longitudinal section of a nanowire was done by in-situ lift-out using a Zeiss Crossbeam NVision 40 system. To protect the sample surface of the layer stack, a carbon cap layer was deposited beginning with electron-beam-assisted and subsequently followed by Ga-focused-ion-beam- (FIB) assisted precursor decomposition. Afterward, the TEM lamella was prepared using a 30 keV Ga FIB with adapted currents. Its transfer to a 3-post copper lift-out grid (Omniprobe) was done with a Kleindiek micromanipulator. To minimize sidewall damage, Ga ions with only 5 keV energy were used for the final thinning of the TEM lamella to electron transparency.

To estimate the processing temperature at the front- and the back-side of the samples, one-dimensional temperature simulations were performed with COMSOL Multiphysics<sup>®</sup>. Each sample had the following three material stacks.

- (1) 20 nm Ni 20 nm Si 102 nm Si<br/>O $_2$  775 µm Si

- (2) 20 nm Si 102 nm  $\mathrm{SiO}_2$  775 µm Si

- (3) 102 nm  $\mathrm{SiO}_2$  775 µm Si

FLA parameters and reflectance coefficients of the materials (Ni, Si, and SiO<sub>2</sub>) were required for these simulations. The absorption profiles of these layer stacks were obtained by optical simulations using an in-house script, developed based on the transfer-matrix method. <sup>62</sup> The calculated reflectance coefficients for the three stacks were 0.64, 0.722, and 0.281, respectively

(table 1). The cross-sectional area of each Si nanowire was only a few nm<sup>2</sup>, while Ni and Si pads cover an area of a few  $\mu$ m<sup>2</sup>. Most of the sample at surface (1 cm<sup>2</sup> total area) consisted of SiO<sub>2</sub> (BOx) layer after fabrication of the nanowires. Therefore, the temperature of the third layer stack would have a major contribution to the overall surface temperature. Heat transfer from this stack was expected to influence the temperatures of the other two stacks as well.

Table 1: Parameters extracted from temperature simulations of the two FLA processes used in this work

|                                   |             | 3  ms, 4.3  kV Pulse            | 6  ms, 3.6  kV Pulse |                     |                       |                     |                       |

|-----------------------------------|-------------|---------------------------------|----------------------|---------------------|-----------------------|---------------------|-----------------------|

| Energy Density                    |             | 70.4                            | 90                   | 3 ms,               | 4.3 kV                | 6 ms,               | $3.6 \mathrm{\ kV}$   |

| $($ $\mathbf{J}\mathbf{cm}^{-2})$ |             |                                 |                      | Pulse               |                       | Pulse               |                       |

| Layer                             | Reflection  | Absorbed Energy                 |                      | $\mathbf{T}_{peak}$ | $\mathbf{T}_{equil.}$ | $\mathbf{T}_{peak}$ | $\mathbf{T}_{equil.}$ |

| Stack                             | Coefficient | ${\bf Density}({\bf Jcm}^{-2})$ |                      | (K)                 | $(\mathbf{K})$        | $(\mathbf{K})$      | $(\mathbf{K})$        |

| 1                                 | 0.64        | 25.3                            | 32.4                 | 685                 | 473                   | 561                 | 513                   |

| 2                                 | 0.722       | 19.6                            | 25                   | 563                 | 432                   | 490                 | 474                   |

| 3                                 | 0.281       | 50.6                            | 64.7                 | 1293                | 628                   | 921                 | 722                   |

### Acknowledgement

The authors are thankful to T. Schönherr and C. Neisser for their help in the fabrication processes and A. Kunz for preparing TEM specimen. They also acknowledge the funding by the Helmholtz Initiative and Networking Funds for support through the International Helmholtz Research School NanoNet via grant No. VH-KO-606 and by the European Union's Horizon 2020 Research and Innovation programme under grant No. 899282. Furthermore, the use of the HZDR's Ion Beam Center TEM facilities and the funding of TEM Talos by the German Federal Ministry of Education of Research (BMBF; grant No. 03SF0451) in the framework of HEMCP are acknowledged.

#### References

- (1) Heinzig, A.; Slesazeck, S.; Kreupl, F.; Mikolajick, T.; Weber, W. M. Reconfigurable silicon nanowire transistors. *Nano Letters* **2012**, *12*, 119–124.

- (2) Simon, M.; Mizuta, R.; Fan, Y.; Tahn, A.; Pohl, D.; Trommer, J.; Hofmann, S.; Mikolajick, T.; Weber, W. M. Lateral Extensions to Nanowires for Controlling Nickel Silicidation Kinetics: Improving Contact Uniformity of Nanoelectronic Devices. ACS Applied Nano Materials 2021, 4, 4371–4378.

- (3) d'Heurle, F. M.; Lavoie, C.; Gas, P.; Philibert, J. Diffusion Processes in Advanced Technological Materials; Elsevier, 2005; pp 283–332.

- (4) Laurila, T.; Molarius, J. Reactive phase formation in thin film metal/metal and metal/silicon diffusion couples. Critical Reviews in Solid State and Materials Sciences 2003, 28, 185–230.

- (5) Katsman, A.; Beregovsky, M.; Yaish, Y. E. Formation and evolution of nickel silicide in silicon nanowires. *IEEE Transactions on Electron Devices* **2014**, *61*, 3363–3371.

- (6) Dellas, N.; Schuh, C.; Mohney, S. E. Silicide formation in contacts to Si nanowires. Journal of Materials Science 2012, 47, 6189–6205.

- (7) Koyama, M.; Shigemori, N.; Ozawa, K.; Tachi, K.; Kakushima, K.; Nakatsuka, O.; Ohmori, K.; Tsutsui, K.; Nishiyama, A.; Sugii, N., et al. Si/Ni-Silicide Schottky junctions with atomically flat interfaces using NiSi 2 source. 2011 Proceedings of the European Solid-State Device Research Conference (ESSDERC). 2011; pp 231–234.

- (8) Lin, Y.-C.; Chen, Y.; Xu, D.; Huang, Y. Growth of nickel silicides in Si and Si/SiOx core/shell nanowires. *Nano Letters* **2010**, *10*, 4721–4726.

- (9) Chen, Y.; Lin, Y.-C.; Zhong, X.; Cheng, H.-C.; Duan, X.; Huang, Y. Kinetic manip-

- ulation of silicide phase formation in Si nanowire templates. *Nano Letters* **2013**, *13*, 3703–3708.

- (10) Dellas, N.; Liu, B.; Eichfeld, S.; Eichfeld, C.; Mayer, T.; Mohney, S. E. Orientation dependence of nickel silicide formation in contacts to silicon nanowires. *Journal of Applied Physics* 2009, 105, 094309.

- (11) Baglin, J. E. E.; Atwater, H. A.; Gupta, D.; D'Heurle, F. M. Radioactive Ni\* tracer study of the nickel silicide growth mechanism. *Thin Solid Films* **1982**, *93*, 255–264.

- (12) d Heurle, F.; Petersson, S.; Stolt, L.; Strizker, B. Diffusion in intermetallic compounds with the CaF2 structure: A marker study of the formation of NiSi2 thin films. *Journal of Applied Physics* **1982**, *53*, 5678–5681.

- (13) Julies, B. A.; Knoesen, D.; Pretorius, R.; Adams, D. A study of the NiSi to NiSi2 transition in the Ni Si binary system. *Thin Solid Films* **1999**, *347*, 201–207.

- (14) Iwai, H.; Ohguro, T.; Ohmi, S.-i. NiSi salicide technology for scaled CMOS. *Microelectronic Engineering* **2002**, *60*, 157–169.

- (15) Koyama, M.; Shigemori, N.; Ozawa, K.; Tachi, K.; Kakushima, K.; Nakatsuka, O.; Ohmori, K.; Tsutsui, K.; Nishiyama, A.; Sugii, N.; Yamada, K.; Iwai, H. Si/Ni-Silicide Schottky junctions with atomically flat interfaces using NiSi;inf¿2i/inf¿ source. Solid-State Device Research Conference (ESSDERC), 2011 Proceedings of the European. 2011; pp 231–234.

- (16) Chen, L. J. Silicide technology for integrated circuits; Iet, 2004; Vol. 5; pp 1–1.

- (17) Lin, J.-F.; Bird, J.; He, Z.; Bennett, P.; Smith, D. Signatures of quantum transport in self-assembled epitaxialnickel silicide nanowires. *Applied Physics Letters* **2004**, *85*, 281–283.

- (18) Tang, W.; Dayeh, S. A.; Picraux, S. T.; Huang, J. Y.; Tu, K.-N. Ultrashort Channel Silicon Nanowire Transistors with Nickel Silicide Source/Drain Contacts. *Nano Letters* 2012, 12, 3979–3985.

- (19) Beregovsky, M.; Katsman, A.; Hajaj, E. M.; Yaish, Y. E. Diffusion formation of nickel silicide contacts in SiNWs. *Solid-State Electronics* **2013**, *80*, 110–117.

- (20) Chen, Y.; Huang, Y. Phase control in solid state silicide nanowire formation. *physica status solidi c* **2013**, *10*, 1666–1669.

- (21) Yaish, Y. E.; Katsman, A.; Cohen, G. M.; Beregovsky, M. Kinetics of nickel silicide growth in silicon nanowires: From linear to square root growth. *Journal of Applied Physics* **2011**, *109*, 094303.

- (22) Ogata, K.; Sutter, E.; Zhu, X.; Hofmann, S. Ni-silicide growth kinetics in Si and Si/SiO 2 core/shell nanowires. *Nanotechnology* **2011**, *22*, 365305.

- (23) Katsman, A.; Beregovsky, M.; Yaish, Y. E. Evolution of nickel silicide intrusions in silicon nanowires during thermal cycling. *Journal of Applied Physics* **2013**, *113*, 084305.

- (24) Dellas, N. S.; Abraham, M.; Minassian, S.; Kendrick, C.; Mohney, S. E. Kinetics of reactions of Ni contact pads with Si nanowires. *Journal of Materials Research* 2011, 26, 2282–2285.

- (25) Lu, K.-C.; Tu, K. N.; Wu, W. W.; Chen, L. J.; Yoo, B.-Y.; Myung, N. V. Point contact reactions between Ni and Si nanowires and reactive epitaxial growth of axial nano-NiSi/Si. *Applied Physics Letters* **2007**, *90*, 253111.

- (26) Dellas, N. S.; Liu, B. Z.; Eichfeld, S. M.; Eichfeld, C. M.; Mayer, T. S.; Mohney, S. E. Orientation dependence of nickel silicide formation in contacts to silicon nanowires. *Journal of Applied Physics* 2009, 105, 094309.

- (27) Dellas, N. S.; Schuh, C. J.; Mohney, S. E. Silicide formation in contacts to Si nanowires.

\*Journal of Materials Science 2012, 47, 6189–6205.

- (28) Lin, Y.-C.; Chen, Y.; Xu, D.; Huang, Y. Growth of Nickel Silicides in Si and Si/SiOx Core/Shell Nanowires. *Nano Letters* **2010**, *10*, 4721–4726.

- (29) Katsman, A.; Beregovsky, M.; Yaish, Y. E. Formation and Evolution of Nickel Silicide in Silicon Nanowires. *IEEE Transactions on Electron Devices* **2014**, *61*, 3363–3371.

- (30) Chou, Y.-C.; Tang, W.; Chiou, C.-J.; Chen, K.; Minor, A. M.; Tu, K. N. Effect of Elastic Strain Fluctuation on Atomic Layer Growth of Epitaxial Silicide in Si Nanowires by Point Contact Reactions. *Nano Letters* **2015**, *15*, 4121–4128.

- (31) Appenzeller, J.; Knoch, J.; Tutuc, E.; Reuter, M.; Guha, S. Dual-gate silicon nanowire transistors with nickel silicide contacts. 2006 International Electron Devices Meeting. 2006; pp 1–4.

- (32) Habicht, S.; Feste, S.; Zhao, Q.-T.; Buca, D.; Mantl, S. Electrical characterization of Ω-gated uniaxial tensile strained Si nanowire-array metal-oxide-semiconductor field effect transistors with ¡100¿- and ¡110¿ channel orientations. Thin Solid Films 2012, 520, 3332–3336.

- (33) Habicht, S.; Zhao, Q. T.; Feste, S. F.; Knoll, L.; Trellenkamp, S.; Bourdelle, K. K.; Mantl, S. NiSi nano-contacts to strained and unstrained silicon nanowires. 2011 IEEE International Interconnect Technology Conference. 2010; pp 1–3.

- (34) Hashimoto, S.; Yokogawa, R.; Oba, S.; Asada, S.; Xu, T.; Tomita, M.; Ogura, A.; Matsukawa, T.; Masahara, M.; Watanabe, T. Enhanced nickelidation rate in silicon nanowires with interfacial lattice disorder. *Journal of Applied Physics* 2017, 122, 144305.

- (35) Khan, M. B.; Deb, D.; Kerbusch, J.; Fuchs, F.; Löffler, M.; Banerjee, S.; Mühle, U.; Weber, W. M.; Gemming, S.; Schuster, J., et al. Towards Reconfigurable Electronics: Silicidation of Top-Down Fabricated Silicon Nanowires. *Applied Sciences* **2019**, *9*, 3462.

- (36) Wu, Y.; Xiang, J.; Yang, C.; Lu, W.; Lieber, C. M. Single-crystal metallic nanowires and metal/semiconductor nanowire heterostructures. *Nature* **2004**, *430*, 61–65.

- (37) Weber, W. M.; Geelhaar, L.; Graham, A. P.; Unger, E.; Duesberg, G. S.; Liebau, M.; Pamler, W.; Chèze, C.; Riechert, H.; Lugli, P.; Kreupl, F. Silicon-Nanowire Transistors with Intruded Nickel-Silicide Contacts. *Nano Letters* **2006**, *6*, 2660–2666.

- (38) Kosloff, A.; Granot, E.; Barkay, Z.; Patolsky, F. Controlled Formation of Radial Core—Shell Si/Metal Silicide Crystalline Heterostructures. *Nano Letters* **2018**, *18*, 70–80.

- (39) Fuchs, F.; Bilal Khan, M.; Deb, D.; Pohl, D.; Schuster, J.; Weber, W. M.; Mühle, U.; Löffler, M.; Georgiev, Y. M.; Erbe, A., et al. Formation and crystallographic orientation of NiSi2–Si interfaces. *Journal of Applied Physics* 2020, 128, 085301.

- (40) Simon, M.; Liang, B.; Fischer, D.; Knaut, M.; Tahn, A.; Mikolajick, T.; Weber, W. M. Top-down fabricated reconfigurable FET with two symmetric and high-current on-states. *IEEE Electron Device Letters* **2020**, *41*, 1110–1113.

- (41) Tu, K.-N.; Alessandrini, E. I.; Chu, W.-K.; Krautle, H.; Mayer, J. W. Epitaxial growth of nickel silicide NiSi2 on silicon. *Japanese Journal of Applied Physics* **1974**, *13*, 669.

- (42) Tung, R.; Gibson, J.; Poate, J. Formation of Ultrathin Single-Crystal Silicide Films on Si: Surface and Interfacial Stabilization of Si-Ni Si 2 Epitaxial Structures. *Physical Review Letters* 1983, 50, 429.

- (43) Ogata, K.; Sutter, E.; Zhu, X.; Hofmann, S. Ni-silicide growth kinetics in Si and Si/SiO2 core/shell nanowires. *Nanotechnology* **2011**, *22*, 365305.

- (44) Katsman, A.; Yaish, Y.; Rabkin, E.; Beregovsky, M. Surface diffusion controlled formation of nickel silicides in silicon nanowires. *Journal of electronic materials* 2010, 39, 365–370.

- (45) Chen, Y.; Lin, Y.-C.; Huang, C.-W.; Wang, C.-W.; Chen, L.-J.; Wu, W.-W.; Huang, Y. Kinetic competition model and size-dependent phase selection in 1-D nanostructures.

Nano Letters 2012, 12, 3115–3120.

- (46) Dellas, N. S.; Abraham, M.; Minassian, S.; Kendrick, C.; Mohney, S. E. Kinetics of reactions of Ni contact pads with Si nanowires. *Journal of Materials Research* 2011, 26, 2282.

- (47) Tang, W.; Nguyen, B.-M.; Chen, R.; Dayeh, S. A. Solid-state reaction of nickel silicide and germanide contacts to semiconductor nanochannels. Semiconductor Science and Technology 2014, 29, 054004.

- (48) Ohring, M. A review of materials science. *Material Science of thin films: deposition and structure* **2002**, 2, 51–52.

- (49) Huang, Y.; Tu, K.-N. Silicon and Silicide Nanowires: Applications, Fabrication, and Properties; CRC Press, 2013; pp 1–1.

- (50) Tang, W.; Dayeh, S. A.; Picraux, S. T.; Huang, J. Y.; Tu, K.-N. Ultrashort channel silicon nanowire transistors with nickel silicide source/drain contacts. *Nano letters* 2012, 12, 3979–3985.

- (51) Lu, K.-C.; Wu, W.-W.; Wu, H.-W.; Tanner, C. M.; Chang, J. P.; Chen, L. J.; Tu, K.-N. In situ control of atomic-scale Si layer with huge strain in the nanoheterostructure NiSi/Si/NiSi through point contact reaction. *Nano Letters* 2007, 7, 2389–2394.

- (52) Khan, M.; Ghosh, S.; Prucnal, S.; Mauersberger, T.; Hübner, R.; Simon, M.; Mikola-

- jick, T.; Erbe, A.; Georgiev, Y. Towards Scalable Reconfigurable Field Effect Transistor using Flash Lamp Annealing. 2020 Device Research Conference (DRC). 2020; pp 1–2.

- (53) Ren, L.; Chen, B. Proximity effect in electron beam lithography. Proceedings. 7th International Conference on Solid-State and Integrated Circuits Technology, 2004. 2004; pp 579–582.

- (54) Rebohle, L.; Prucnal, S.; Skorupa, W. A review of thermal processing in the subsecond range: semiconductors and beyond. Semiconductor Science and Technology 2016, 31, 103001.

- (55) Rebohle, L.; Prucnal, S.; Reichel, D. Flash Lamp Annealing From Basics to Applications; Springer, 2019; pp 1–1.

- (56) Lu, K.-C.; Tu, K.-N.; Wu, W.-W.; Chen, L.; Yoo, B.-Y.; Myung, N. V. Point contact reactions between Ni and Si nanowires and reactive epitaxial growth of axial nano-Ni Si/Si. Applied Physics Letters 2007, 90, 253111.

- (57) Wu, W.-W.; Lu, K.-C.; Chen, K.-N.; Yeh, P.; Wang, C.; Lin, Y.; Huang, Y. Controlled large strain of Ni silicide/Si/Ni silicide nanowire heterostructures and their electron transport properties. *Applied Physics Letters* **2010**, *97*, 203110.

- (58) Weber, W. M. Silicon to Nickel Silicide Longitudinal Nanowire Heterostructures: Synthesis, Electrical Characterization and Novel Devices. Ph.D. thesis, Technische Universität München, 2008.

- (59) Bartur, M.; Nicolet, M.-A. Thermal oxidation of nickel disilicide. *Applied Physics Letters* **1982**, 40, 175–177.

- (60) Hobbs, R. G.; Petkov, N.; Holmes, J. D. Semiconductor nanowire fabrication by bottom-up and top-down paradigms. *Chemistry of Materials* **2012**, *24*, 1975–1991.

- (61) Henschel, W.; Georgiev, Y.; Kurz, H. Study of a high contrast process for hydrogen silsesquioxane as a negative tone electron beam resist. *Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures Processing, Measurement, and Phenomena* **2003**, *21*, 2018–2025.

- (62) Orfanidis, S. J. *Electromagnetic waves and antennas*; Rutgers University New Brunswick, NJ, 2002; pp 1–1.

## Graphical TOC Entry