# Hardware Implementation of Stockwell Transform and Smoothed Pseudo Wigner Ville Distribution Transform on FPGA using CORDIC Algorithm

#### B Murali Krishna, B.T. Krishna, K Babulu

Abstract: A comparison of linear and quadratic transform implementation on field programmable gate array (FPGA) is presented. Popular linear transform namely Stockwell Transform and Smoothed Pseudo Wigner Ville Distribution (SPWVD) transform from Quadratic transforms is considered for the implementation on FPGA. Both the transforms are coded in Verilog hardware description language (Verilog HDL). Complex calculations of transformation are performed by using CORDIC algorithm. From FPGA family, Spartan-6 is chosen as hardware device to implement. Synthetic chirp signal is taken as input to test the both designed transforms. Summary of hardware resource utilization on Spartan-6 for both the transforms is presented. Finally, it is observed that both the transforms S-Transform and SPWVD are computed with low elapsed time with respect to MATLAB simulation.

Keywords: Transforms, Chirp signal, FPGA and CORDIC.

#### I. INTRODUCTION

The advent of getting time indexes information and their mapped spectral components information together in time frequency plane, made time frequency distributions (TFDs) more popular recently. Time frequency distributions are majorly used for signal analysis applications [1]. Popular time frequency distributions are Stockwell transform [2] and Smoothed pseudo Wigner ville distribution (SPWVD) [3]. Both the transforms are effectively produces time frequency distribution (TFD) plane, when compared with other linear and quadratic transforms. The major problem associated with time frequency transforms are estimating complex calculation during signal analysis. This is due to some of the transforms produces poor resolution and cross term contents in TFD plane. Stockwell transform splices input signal into small parts by choosing guassian window as filter. By nature, Guassian window exhibits symmetric coefficients during computation, the computations generated will be repeated as half valued functions.

Manuscript received on December 18, 2021. Revised Manuscript received on December 23, 2021. Manuscript published on January 30, 2022. \* Correspondence Author

**B Murali Krishna**<sup>\*</sup>, Assistant Professor, Department of ECE, Sri Vasavi Engineering College, Green Pedatadepalli, Tadepalligudem (A.P), India. Email: murali.ece713@gmail.com

**B.T. Krishna**, Professor, Department of ECE, University College of Engineering Kakinada, Jawaharlal Nehru Technological University, Vizianagaram, (A.P), India.

**K Babulu**, Professor, Department of ECE, University College of Engineering Vizianagaram, Jawaharlal Nehru Technological University, Vizianagaram, (A.P), India.

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

Retrieval Number: 100.1/ijrte.E67050110522 DOI: 10.35940/ijrte.E6705.0110522 Journal Website: <u>www.ijrte.org</u>

Similarly, for SPWVD computation low pass filter (LPF) is used to slice the signal in to parts. When these transforms are used to analyze non stationary signals, the computation involves large floating values and produces significant rounding error. In addition to this, the limited on board memory allocation results in poor time frequency representation (TFR) [4]. From the literature survey, few methods are proposed earlier to implement these transforms on FPGA [5-11]. The proposed transforms are implemented on FPGA to overcome the disadvantages of DSPA [12]. The current paper is organized as, Section 2 gives the information about Stockwell transform and SPWVD functionality. Section 3 presents the design flow and hardware implementation of proposed transforms. Section 4 represents the simulation results and comparison of proposed designs with respect to earlier state of art methodologies. Finally, section 5 concludes the transform techniques implementation on FPGA.

#### II. BACKGROUND THEORY

#### A. Discrete Stockwell Transform (DST):

By the definition, Discrete Stockwell Transform for the sampled signal x(n) is defined as

$$DST\{x(x(n,m))\} = \sum_{n=-\infty}^{n=\infty} x(n)w(n - k,m)\exp(-j2\pi mk)$$

Eq (1)

Where discrete window filter function is Guassian function given as

$$w(n-k,m) = \frac{1}{\sigma(m)\sqrt{2\pi}} \exp\left(\frac{-(n-k)^2}{2\sigma m^2}\right) \qquad \text{Eq (2)}$$

Analytical computation of DST carried out using Eq (1). The computation is performed initially by multiplying input signal and guassian function. After the completion of multiplication process, Fourier transform is carried out for all the product terms to obtain DST. Discrete version of ST is considered in order to implement transform on FPGA. Guassian window preserves the phase content of signal during transformation and retrieval content is projected in to TFR plane. This advantage makes DST suitable for many real time applications [14].

# B. Discrete Smoothed Pseudo Wigner Ville Distribution (DSPWVD):

DSPWVD for the sampled signal x(n) is defined as  $DSPWVD\{x(n)\} = \sum_{n=-\infty}^{n=\infty} q(n-k) \sum_{n=-\infty}^{n=\infty} x(n+k)x^*(n-k)w(k)w^*(k)\exp(-j4\pi km)$  Eq (3)

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

# Hardware Implementation of Stockwell Transform and Smoothed Pseudo Wigner Ville Distribution Transform on FPGA using CORDIC Algorithm

### Where q(n - k) = Low Pass Filter (LPF)

DSPWVD is considered (discrete version) and its computation is performed by using Eq (3). Initially, signal is multiplied with its symmetric complex conjugative component and multiplication is performed. The product results in auto terms (signal and its conjugate component). If the signal consists of multiple frequency contents, then product produces auto terms as well as cross terms. LPF is used to suppress the cross terms that are presented in TFR plane [3]. As DSPWVD produces suppressed cross term TFD, makes suitable for many non-stationary signal analysis applications.

### **III. HARDWARE IMPLEMENTATION**

The non-stationary input signal representation is challenging task while computing transform techniques. Since, signal produces large floating values, these floating values are represented using CORDIC algorithm [13].

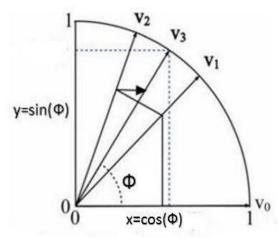

Fig. 1 CORDIC rotation

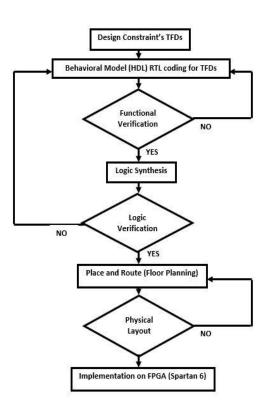

Fig.1 represents the CORDIC function and generation of trigonometric values with respect to rotational angle. All the floating values are generated by changing rotating angle. The signal floating values are generated using shifting and addition operation of CORDIC algorithm. For example, in order to get the product for two complex floating numbers, four registers are required to store all the imaginary and real components. But using CORDIC algorithm, two registers are sufficient to process the floating values (polar representation). So, the number of memory blocks used for computation are halved. Fig.2 indicated the algorithm design flow of proposed TFDs. Both DST and DSPWVD are designed using flow chart steps given in Fig.2.

Initially, consider the requirements for computation of DST and DSPWVD. Fixed guassian widow length for DST and fixed LPF limits are considered for DSPWVD. Verilog code is developed for both DST and DSPWVD. The developed designs are verified using behavioral model and cross checked with netlist generated from synthesis report. The process is repeated as feedback loop until netlist exactly matched with RTL schematics. RTL schematics are helpful in finding critical path and delay existence between different programmable logical blocks. Latency can be minimized by optimum critical path.

Fig.2 Design flow of TFD

Place and route steps are evaluated after the completion of logic verification. Suitable FPGA targeted device (Spartan-6) is chosen in order to dump the generated (.bit) files.

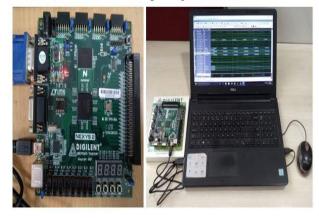

Fig.3 Experimental Set up

Fig.3 represents the real time experimental set up for designed transforms DST and DSPWVD. The interface between personal computer and Spartan board is established using bidirectional communication ports and ports are joined using RS232 cable as shown in Fig.3.

## IV. RESULTS AND DISCUSSIONS

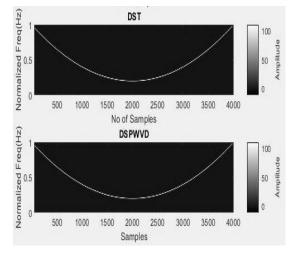

In this section, simulation results of DST and DSPWVD for the input chirp is presented. Fig.4 shows the time frequency representation of quad chirp signal. The samples of chirp signal are converted in to digital by using CORDIC rotation.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.E67050110522 DOI: 10.35940/ijrte.E6705.0110522 Journal Website: <u>www.ijrte.org</u>

Initially, chirp signal is sampled by using operating clock frequency to avoid aliasing effect during reconstructed signal representation in TFR plane. Fig.5 and Fig.6 represents the simulation results of DST and DSPWVD performed using Xilinx version 14.0. The values are represented in hexadecimal format to visualize the 32 bit register length. Specification of Spartan 6 board consists of 70 input and output pins which are useful to apply the input signal bits. The inbuilt CMOS oscillator operated at The simulated values obtained from 100MHz. Xilinx platform are cross verified using MATLAB server end. Port 4999 is used to interface the MATLAB and Xilinx server (HDLDaemon socket). As computation is performed on Xilinx platform with high operation frequency, the elapsed time for FPGA implementation is 2.32ms where as for MATLAB server it is 209ms. The obtained Xilinx simulated values are cross verified with simulated MATLAB waveforms for proper functionality.

Fig.4 TFDs of DST and DSPWVD

From Fig.4, it can be observed that both DST and DSPWVD performs equal TFR for the input chirp signal. The obtained TFD plane is smoothed frequency contents without any cross term effect [15].

| /u_STRANSFORM_PROCESS/u_FFT_COMPUTE_FUNC_PROCESS/dk     | 1'h0   |            |               |           |          |           |          | 2         |           |          |           |          |            |      |

|---------------------------------------------------------|--------|------------|---------------|-----------|----------|-----------|----------|-----------|-----------|----------|-----------|----------|------------|------|

| u_STRANSFORM_PROCESS/u_FFT_COMPUTE_FUNC_PROCESS/rd_data | 32'h0  | 32'h000287 | f8 32'h0      | 00287f8 3 | 2'h00028 | 7f8 32    | 32'h0002 | 87f8 32'h | 000287f8  | 32'h0002 | 87f8 32'h | 000287f8 | 32'hfffc6/ | 6cd  |

| u_STRANSFORM_PROCESS/u_FFT_COMPUTE_FUNC_PROCESS/tw_fact | 32'h0  | 32'h000004 | 00 32'h0      | 00003fb ( | 2'h00000 | 3ec 32'h0 | 00003d43 | 2'h00000  | 3b2 32'h0 | 0000387  | 32'h0000  | 353 32'h | 0000318    | 32'h |

| /u_STRANSFORM_PROCESS/u_FFT_COMPUTE_FUNC_PROCESS/out0   | 32'hff | 32'h002a31 | 06            |           |          |           | 32'h0048 | 3efa      |           |          |           |          |            | 6 8  |

| Now                                                     | 630 ns | 733500     | 1111<br>10 ns | 11111     | 1111     | 73350     | )20 ns   | 1111      | 1111      | 73350    | )40 ns    | 11111    | 1111       | TTTT |

|                                                         |        | 100000     | 14.119        |           |          | 10000     | 1000110  |           |           | 1000     | C 19/11/2 |          |            |      |

**Fig.5 DST Simulations for Input Chirp Signal**

| /u_PWV_DISTRIBUTION_PROCESS/dk      | 1'h0   |               |              |                |                |              |              |

|-------------------------------------|--------|---------------|--------------|----------------|----------------|--------------|--------------|

| /u_PWV_DISTRIBUTION_PROCESS/rd_data | 32'h   | (32'h005c0000 | 32'h005f0000 |                | 32'h004f0000   | 32'h00430000 | 32'h003c0000 |

| /u_PWV_DISTRIBUTION_PROCESS/out0    | 32'h   | (32'h000003c  | 32'h0000003d | , 32'h0000003e | , 32'h0000003f | 32'h00000040 | 32'h00000001 |

| /u_PWV_DISTRIBUTION_PROCESS/out1    | 32'h0  | (32'h0de714fc | 32h1554723c  | 32'h1cbd03f8   | 32h1a49d65c    | 32'h1a296cb4 | 32h1c8126b9  |

| Now                                 | 160 ns | 146           | 3010 ns      | 1463020 ns 1   | 1463030 ns     | 1463040 ns   | 463050 ns    |

## Fig.6 DSPWVD Simulations for Input Chirp Signal

Most of the earlier implementation are based on considering 16 bit register length, which results in large rounding error. In the proposed method, central mean rounding is implemented to overcome the disadvantage of errors. Round the value nearest mean value by taking threshold as mean difference. Table 1 represents the comparison for resource utilization of DST and DSPWVD with exiting methods.

**Table.1 Resource Comparison of TFDs**

| TFD               | IOB | LUTs | FFs | SLICES | CLK<br>(MHz) |  |

|-------------------|-----|------|-----|--------|--------------|--|

| DST<br>Proposed   | 126 | 642  | 132 | 526    | 48.1         |  |

| ST [5]            | 176 | 1568 | 182 | 882    | 67.2         |  |

| DST [6]           | 184 | 1392 | 152 | 987    | 67.2         |  |

| DST [7]           | 135 | 1554 | 186 | 745    | 98.1         |  |

| DSPWD<br>Proposed | 126 | 598  | 112 | 642    | 48.1         |  |

| SPWVD<br>[8]      | 134 | 1258 | 144 | 760    | 54.1         |  |

| SPWVD<br>[9]      | 221 | 1326 | 152 | 876    | 82.5         |  |

| SPWVD<br>[10]     | 246 | 1412 | 193 | 814    | 96.3         |  |

| DSPWD<br>[11]     | 221 | 1462 | 182 | 776    | 96.3         |  |

The proposed DST utilizes 642 look up tables, 132 flip flops and 526 slices at clock frequency of 48.1 MHz. Similarly, DSPWVD utilizes 598 look up tables, 112 flip flops and 642 slices at a clock frequency of 48.1 MHz.

From the results, the overall resource utility from the available board is 14% which is less when compared with compared methods.

#### **Table.2** Power consumption Comparison of TFDs

| Time Frequency<br>Transform | LATENCY | POWER<br>CONSUMPTION<br>(nano Joules) |  |  |  |  |

|-----------------------------|---------|---------------------------------------|--|--|--|--|

| DST<br>Proposed             | 241     | 348.2                                 |  |  |  |  |

| ST [5]                      | 352     | 764.3                                 |  |  |  |  |

| DST [6]                     | 387     | 1524.3                                |  |  |  |  |

| DST [7]                     | 456     | 1364.4                                |  |  |  |  |

| DSPWD<br>Proposed           | 262     | 296.7                                 |  |  |  |  |

| SPWVD[8]                    | 287     | 1021.2                                |  |  |  |  |

| SPWVD[9]                    | 266     | 775.5                                 |  |  |  |  |

| SPWVD[10]                   | 437     | 895.8                                 |  |  |  |  |

| DSPWD[11]                   | 561     | 1293.4                                |  |  |  |  |

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.

Retrieval Number: 100.1/ijrte.E67050110522 DOI: 10.35940/ijrte.E6705.0110522 Journal Website: <u>www.ijrte.org</u>

# Hardware Implementation of Stockwell Transform and Smoothed Pseudo Wigner Ville Distribution Transform on FPGA using CORDIC Algorithm

Table.2 represents the power consumption comparison of proposed DST and DSPWVD with respect to earlier methods. As number of memory blocks occupied by designed transforms are less, their corresponding power consumption is also less. DST consumed 348 nano joule power and DSPWVD consumed 296 nano joule with respective latency factors are 241, 262.

#### V. CONCLUSION

In this paper, linear time frequency transform (DST) and quadratic time frequency transform (DSPWVD) are developed using CORDIC algorithm. The developed algorithms are tested on hardware platform using FPGA family (SPARTAN-6). It is observed that, the developed transforms consumed less memory PLBs and LUTs when compared with earlier exiting methods. Due to consideration of higher length register for input signal representation, rounding error is minimized. The accurate representation of DST and DSPWVD signal values using CORDIC, avoids time consuming factor and results in low power consumption. Finally, it is concluded that proposed transforms can be utilized for analysis of many nonstationary signals at low power consumption rate with less amount of computation time.

#### REFERENCES

- 1. Cohen, Leon. "Time-frequency distributions-a review." *Proceedings* of the IEEE 77.7 (1989): 941-981.

- Stockwell, Robert Glenn, Lalu Mansinha, and R. P. Lowe. "Localization of the complex spectrum: the S transform." *IEEE transactions on signal processing* 44.4 (1996): 998-1001.

Yan, Yong-sheng, Carmen CY Poon, and Yuan-ting Zhang.

- Yan, Yong-sheng, Carmen CY Poon, and Yuan-ting Zhang. "Reduction of motion artifact in pulse oximetry by smoothed pseudo Wigner-Ville distribution." *Journal of NeuroEngineering and Rehabilitation* 2.1 (2005): 1-9.

- 4. Lee, Ming-Huan, et al. "Hardware implementation of EMD using DSP and FPGA for online signal processing." *IEEE Transactions on industrial electronics* 58.6 (2010): 2473-2481.

- Gilliland, Spenser, et al. "Performance evaluation of FPGA based embedded ARM processor for ultrasonic imaging." 2013 IEEE International Ultrasonics Symposium (IUS). IEEE, 2013.

- Petranovic, D., S. Stankovic, and L. J. Stankovic. "Special purpose hardware for time frequency analysis." *Electronics Letters* 33.6 (1997): 464-466.

- Biswal, Birendra, Pradipta Kishore Dash, and Milan Biswal. "Time frequency analysis and FPGA implementation of modified Stransform for de-noising." *Int. J. Signal Process. Image Process. Pattern Recognit* 4.2 (2011): 119-135.

- 8. Stankovic, LJubisa. "A method for time-frequency analysis." *IEEE Transactions on Signal Processing* 42.1 (1994): 225-229.

- Andria, Gregorio, and Mario Savino. "Interpolated smoothed pseudo Wigner-Ville distribution for accurate spectrum analysis." *IEEE* transactions on instrumentation and measurement 45.4 (1996): 818-823.

- Le, Thuyen, et al. "A flexible approach and VLSI architecture for computing discrete time-frequency distribution." 1998 IEEE Workshop on Signal Processing Systems. SIPS 98. Design and Implementation (Cat. No. 98TH8374). IEEE, 1998.

- Djebbari, Abdelghani, and F. Bereksi-Reguig. "Smoothed-pseudo Wigner–Ville distribution of normal and aortic stenosis heart sounds." *Journal of Mechanics in Medicine and Biology* 5.03 (2005): 415-428.

- Rodriguez-Andina, Juan J., Maria J. Moure, and Maria D. Valdes. "Features, design tools, and application domains of FPGAs." *IEEE Transactions on Industrial Electronics* 54.4 (2007): 1810-1823.

- 13. Volder, Jack. "The CORDIC computing technique." Papers presented at the the March 3-5, 1959, western joint computer conference. 1959.

- Institution of Engineers (India): Series B 95.4 (2014): 377-382. Krishna, B. T. "Electrocardiogram Signal and Linear Time-

Retrieval Number: 100.1/ijrte.E67050110522 DOI: 10.35940/ijrte.E6705.0110522 Journal Website: <u>www.ijrte.org</u> Frequency Transforms." Journal of The Institution of Engineers (India): Series B 95.4 (2014): 377-382.

- 15. Krishna, Battula Tirumala. "Fractional Fourier transform: a survey." *Proceedings of the international conference on advances in computing, communications and informatics*. 2012.

- Dorfleitner, Gregor, and Thomas Klein. "Rounding with multiplier methods: An efficient algorithm and applications in statistics." *Statistical Papers* 40.2 (1999): 143-157.

#### **AUTHORS PROFILES**

**B** Murali Krishna Research scholar in University College of Engineering JNTUK, Kakinada, India, and his current research area is VLSI signal processing and presently research on time frequency distributions.

**B. T. Krishna** got his Ph.D. degree in ECE from Andhra University, Vishakhapatnam, and Andhra Pradesh, India in 2010. He has been with the college school of Engineering working as Professor, JNTU Kakinada since 2012. His exploration advantages incorporate in signal processing, VLSI.

**K Babulu** got his Ph.D. degree in ECE from Andhra JNTUH, Andhra Pradesh, India. He has been with the college school of Engineering, JNTUV working as a professor in ECE department, Vizianagaram. His exploration advantages in embedded systems, VLSI.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP) © Copyright: All rights reserved.