# A Hybrid Self-Voltage Balanced Multilevel Inverter Topologies for Induction Motors

# Sanjeev Kumar, H.K. Verma, M.P.S. Chawla

Abstract: A hybrid structured asymmetric switching capacitor multilevel inverter (ASC-MLI) is suggested in this work. The notion behind presenting this topology is to reduce the device count and DC sources as compared with conventional MLI. The step by step operating mode of single phase ASC-MLI is presented and by doing slight modifications the same configuration is used in three phase utility application and electric drive. The proposed configurations utilize major benefits of self-voltage balancing capability of capacitor voltage, which is independent from different load type and modulations index. To generate the switching pulse for corresponding switches the multi-carrier based sinusoidal pulse width modulation (MCS-PWM) technique is used; in addition to this simulation result are obtained using MATLAB/Simulink 2016b software version. Simulation results of an induction motor drive connected as three phase load highlights good performance of 17-level MLI.

OPEN ACCESS

Keywords: Renewable energy system, Asymmetric switchcapacitor multilevel inverter (ASC-MLI), Multi-carrier sinusoidal pulse width modulation (MCS-PWM), Total harmonic distortions (THD).

### I. INTRODUCTION

As the need for electrical power grows across the world, it is expected that power electronics system (PES) will be used in 100 percent of all electrical energy industry, changing the face of the electrical engineering sector [1]. Dc-to-ac power conversion is most significant technology for setting up generation, transmission, distribution, and electrical power utilization at the ongoing scenario as the uses of renewable energy system (RES) increases rapidly. Multilevel Inverter (MLI) has been a key technology in variable frequency drives using various utility applications, active filters, locomotives, and RES. A highuninterruptible power supply improves capacity electromagnetic compatibility and ensures desirable output voltage quality. [2,3,4]. Its wide application makes it a mature technology, since traditional converters only generate two levels of output voltage,  $+V_{dc}$  and  $-V_{dc}$ , which

Manuscript received on October 22, 2021. Revised Manuscript received on October 28, 2021. Manuscript published on November 30, 2021.

\* Corresponding Author

Sanjeev Kumar\*, Department of Electrical Engineering, Shri G.S. Institute of Technology & Science, Indore (Madhya Pradesh) India. E-mail Id: sanjeev.kumar92ex@gmail.com,

**H.K. Verma**, Department of Electrical Engineering, Shri G.S. Institute of Technology & Science, Indore (Madhya Pradesh) India. E-mail Id: vermaharishgs@gmail.com,

**M.P.S. Chawla**, Department of Electrical Engineering, Shri G.S. Institute of Technology & Science, Indore (Madhya Pradesh) India. E-mail Id: mpschawla@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an <u>open access</u> article under the CC BY-NC-ND license (<u>http://creativecommons.org/licenses/by-nc-nd/4.0/</u>)

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u> contain a high amount of harmonic components and require the use of a filter to assure a sinusoidal waveform. However, due to switching losses and the necessity for high-rated components, traditional converters have some limitations when used at high voltage/power applications. [7]. The requirement of MLI are less switch loss, and reduced dv/dt stress are all advantages of MLI [5,6,9]. Several MLI circuit configurations are available which are capable of synthesizing multilevel waveforms. Three topologies, however have acquired the status of being 'classic or conventional' topology [8]. These topologies are Neutral Point Clamped (NPC) MLI, Flying Capacitor (FC) MLI & Cascaded H-bridge (CHB) MLI [10-16]. The downside with NPC MLI configuration is as the output voltage level increases, it requires additional clamping diodes and also alarms whenever there is an unequal voltage sharing among capacitor which are connected in series [10]. When using FCMLI, a high number of storage capacitors are required to increase the amount and quality of output voltage as the stages to get desired waveform [11-12]. In CHB MLI configuration, no flying capacitor & clamping diodes are used; the only limitations with this configuration is that it requires isolated dc source as the output voltage level increases. As a result, a large range of MLI topologies and control schemes have been suggested in recent decades to reduce switched device count (RSDC) by using varying ratings of unidirectional and bidirectional switches [13-17]. Few of them are discussed here briefly. In [13-15], the MLIs having symmetrical topology has taken over, as they have less diversity in DC voltage source which results in low cost, but major concern with them is their modularity. In [16] a new configuration is presented which further is improved in [17], the primary disadvantage of this setup is that the suggested algorithm cannot achieve all of the stages (additive and subtractive). According to existing literature, the majority of reported MLI topologies in recent years have been achieving high output voltage levels with minimal numbers of switches. However, there has been a lot of tradeoff in terms of modularity, bidirectional switch simplicity, DC source variety, voltage stress against switch durability, and losses. This paper focuses on ASC-MLI topology which uses hexagonal switch cell [HSC] [11]. Using eight controlled switches, the suggested architecture can create 17 levels of output voltage. It provides dependable operation with decreased voltage stress across the switches due to its modular construction. Because the design has an inherent capacity of balancing capacitor voltage, it decreases DC source diversifications.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.

### II. PROPOSED MLI TOPOLOGIES

### 2.1 Proposed topology – I:

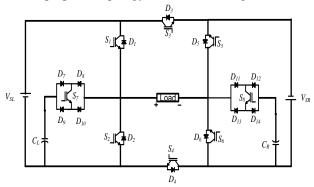

In the proposed work, a new configuration based on hybridized asymmetrical switched capacitor MLI is proposed, which is an extension of its basic unit [11]. The hybridized proposed topology is illustrated in fig 1, which is

switched-capacitor based multilevel inverter (SCMLI), and requires two unequal dc voltage source ( $V_{SL}$  &  $V_{SR}$ ), six bidirectional-conducting-unidirectional-blocking (BCUB) power switch, two bidirectional-conducting-bidirectional blocking (BCBB) power switches and two capacitor. Table 1 shows the generalized mathematical equation for asymmetrical operation and the DC value sources.

| Value of DC source                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Number of output level                                                      |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|--|--|

| $V_{SL1} = initial$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $4\mathbf{x}\left[\sum_{m=1}^{n}\frac{(V_{SLm}+V_{SRm})}{V_{SL1}}\right]+1$ |  |  |  |  |  |  |

| $V_{SR1} = 3xV_{SL1}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                             |  |  |  |  |  |  |

| $V_{SLn} = 4x \left[\sum_{m=1}^{n-1} (V_{SLm} + V_{Sm})\right]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $_{Rm}$ )] + V <sub>SL1</sub>                                               |  |  |  |  |  |  |

| $V_{SRn} = 2x[V_{SLn} + (\sum_{m=1}^{n-1} (V_{SLn} + (\sum_{m=1}^{n-1} (V_{$ | $V_{SLn} + V_{SRn}$ ))] + V <sub>SL1</sub>                                  |  |  |  |  |  |  |

### Fig. 1 Configuration of the proposed topology

To generate all possible levels (i.e. positive and negative) for the proposed configurations, the magnitude of voltage ( $V_{SL}$ :  $V_{SR}$ ) should be (2:6) obtained from table 1. As indicated in Table 2, states 1 to 8 of the proposed MLI's output voltage waveform have positive levels, state 9 has zero levels, and states 10 to 17 have negative levels. The '1' state condition represents the switch in the 'ON' state, whereas the '0' state condition represents the switch in the 'OFF' state.

| State | Output voltage level                                  | Switching scheme |       |                       |       |                       |                       |                       |                       |                                                                     |

|-------|-------------------------------------------------------|------------------|-------|-----------------------|-------|-----------------------|-----------------------|-----------------------|-----------------------|---------------------------------------------------------------------|

|       |                                                       | $S_1$            | $S_2$ | <b>S</b> <sub>3</sub> | $S_4$ | <b>S</b> <sub>5</sub> | <b>S</b> <sub>6</sub> | <b>S</b> <sub>7</sub> | <b>S</b> <sub>8</sub> | Conducting Diodes                                                   |

| 1     | $V_{SL} + V_{SR}$                                     | 1                | 0     | 0                     | 1     | 1                     | 0                     | 0                     | 0                     |                                                                     |

| 2     | $V_{CL} + V_{SR}$                                     | 0                | 0     | 0                     | 1     | 1                     | 0                     | 1                     | 0                     | $D_{7}, D_{10}$                                                     |

| 3     | V <sub>SR</sub>                                       | 0                | 0     | 0                     | 1     | 1                     | 0                     | 0                     | 0                     | $D_2$                                                               |

| 4     | $V_{SL} + V_{CR}$                                     | 1                | 0     | 0                     | 1     | 0                     | 0                     | 0                     | 1                     | D <sub>11</sub> , D <sub>14</sub>                                   |

| 5     | $V_{CL} + V_{CR}$                                     | 0                | 0     | 0                     | 1     | 0                     | 0                     | 1                     | 1                     | $D_7, D_{10}, D_{11}, D_{14}$                                       |

| 6     | V <sub>CR</sub>                                       | 0                | 0     | 0                     | 1     | 0                     | 0                     | 0                     | 1                     | D <sub>2</sub> ,D <sub>11</sub> ,D <sub>14</sub>                    |

| 7     | V <sub>SL</sub>                                       | 1                | 0     | 0                     | 1     | 0                     | 0                     | 0                     | 0                     | $D_6$                                                               |

| 8     | V <sub>CL</sub>                                       | 0                | 0     | 0                     | 1     | 0                     | 0                     | 1                     | 0                     | D <sub>7</sub> ,D <sub>6</sub> ,D <sub>10</sub>                     |

| 9     | 0V                                                    | 0                | 0     | 0                     | 1     | 0                     | 1                     | 0                     | 0                     | $D_2$                                                               |

| 10    | -(V <sub>SL</sub> -V <sub>CL</sub> )                  | 0                | 0     | 1                     | 0     | 0                     | 0                     | 1                     | 0                     | D <sub>5</sub> ,D <sub>8</sub> ,D <sub>9</sub>                      |

| 11    | -(V <sub>SL</sub> )                                   | 0                | 1     | 1                     | 0     | 0                     | 0                     | 0                     | 0                     | D <sub>5</sub>                                                      |

| 12    | -(V <sub>SR</sub> -V <sub>CR</sub> )                  | 0                | 0     | 1                     | 0     | 0                     | 0                     | 0                     | 1                     | $D_{1,}D_{11},D_{14}$                                               |

| 13    | -( $V_{SL}$ + $V_{SR}$ - $V_{CL}$ - $V_{CR}$ )        | 0                | 0     | 1                     | 0     | 0                     | 0                     | 1                     | 1                     | D <sub>8</sub> ,D <sub>9</sub> ,D <sub>12</sub> , D <sub>13</sub> , |

| 14    | -(V <sub>SL</sub> +V <sub>SR</sub> -V <sub>CR</sub> ) | 0                | 1     | 1                     | 0     | 0                     | 0                     | 0                     | 1                     | D <sub>12</sub> ,D <sub>13</sub>                                    |

| 15    | -(V <sub>SR</sub> )                                   | 0                | 0     | 1                     | 0     | 0                     | 1                     | 0                     | 0                     | D <sub>1</sub>                                                      |

| 16    | -(V <sub>SL</sub> +V <sub>SR</sub> -V <sub>CL</sub> ) | 0                | 0     | 1                     | 0     | 0                     | 1                     | 1                     | 0                     | D <sub>8</sub> ,D <sub>9</sub>                                      |

| 17    | -( $V_{SL}$ + $V_{SR}$ )                              | 0                | 1     | 1                     | 0     | 0                     | 1                     | 0                     | 0                     |                                                                     |

2

Table 2. Switching table for 17-Level Inverter Topology

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u>

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u>

3

Blue Eyes Intelligence Engineering

© Copyright: All rights reserved.

and Sciences Publication

no

, lenottemain

ww.iiese.or

# A Hybrid Self-Voltage Balanced Multilevel Inverter Topologies for Induction Motors

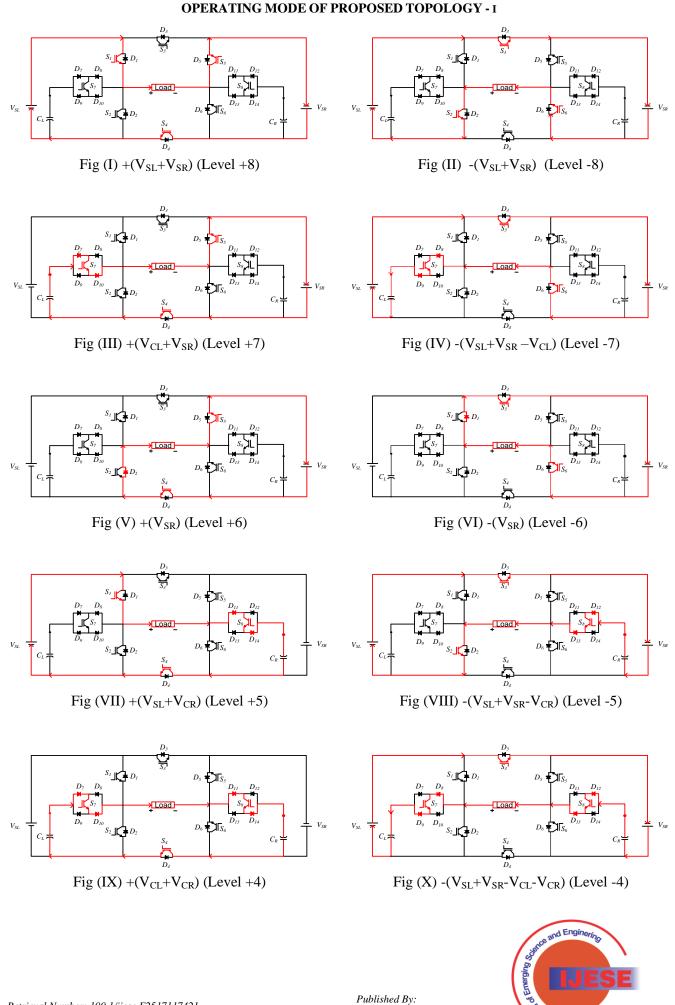

Fig (XVII) +(0 V) (Level 0)

# Fig. 2 shows sub figs. (I-XVII) which are the distinct mode of operations (i.e. current flow direction) for the proposed topology for 17-levels output.

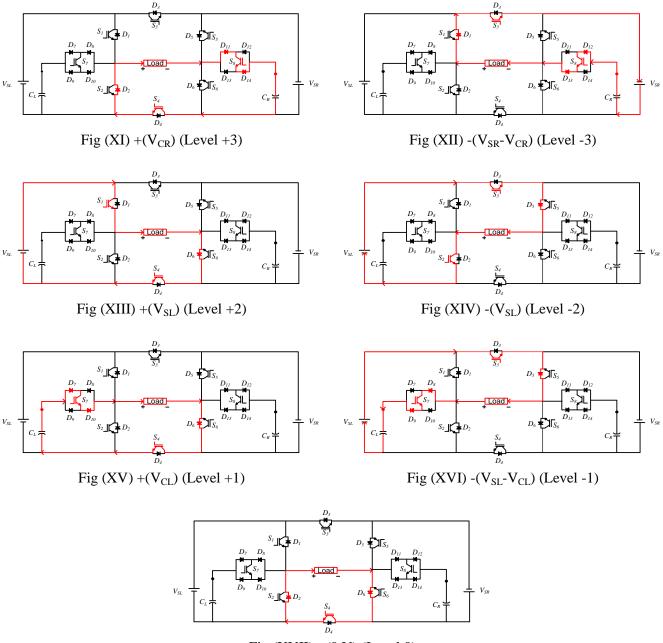

### 2.2 Proposed topology -II:

The topology I is used for the single phase operations, by doing slightly modifications it can be further developed to use in the three phase MLI applications. In the topology shown in fig. 3, three individual cells of topology I can be used and in their output, three phase load is connected.

Its switching signal is generated in such a manner that, by keeping their carrier signal same and making  $120^{0}$  phase shift in their reference signal.

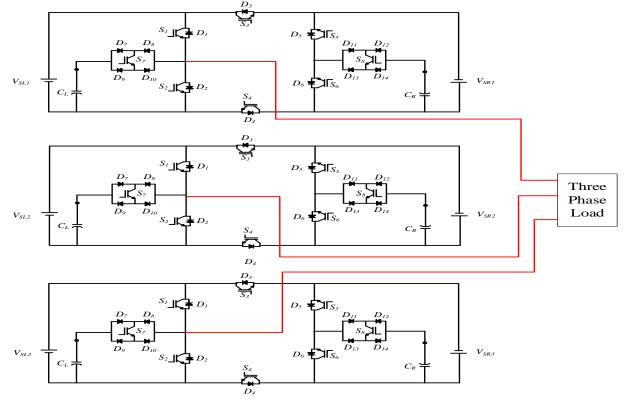

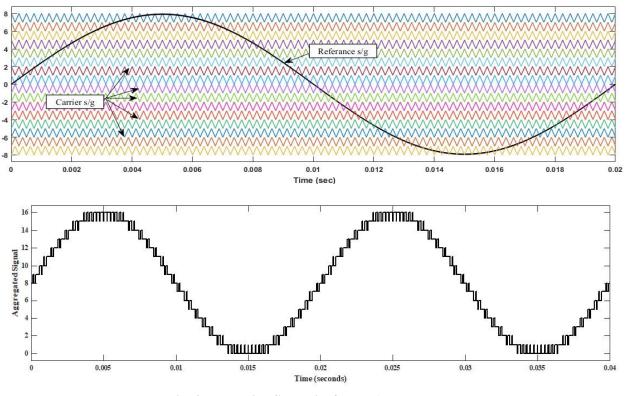

### III. MODULATING SCHEME

In both the topologies I & II, the operations of power switches are regulated by producing correct gate signals,

which is done using a suitable MCS-PWM approach (i.e. alternating phase opposition disposition (APOD) pulse shift technique). The switching frequency of the carrier signal is kept at 5 KHz, while the frequency of the reference signal is retained at 50 Hz. In the MCS-PWM approach, an appropriate logical operation is employed between the carrier and reference signal to create desired pulses, which are then supplied to the power switch's corresponding driver circuit, which amplifies the amplitude of the generated pulses to activate the respective switch. [17]. To create 'm' number of output levels, the MCS-PWM technique requires ('m-1') carrier signal. Figure 4 depicts the fundamental structure that is employed in the 17-level MLI modifying schemes.

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u> Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.

Fig. 3 Three phase connection of proposed topology II

# IV. SIMULATION RESULTS

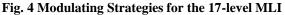

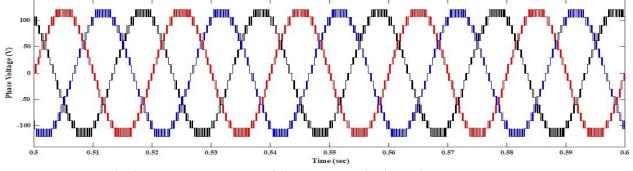

The simulation was carried out using MATLAB/Simulink to assess the performance of the proposed configuration. The simulation parameter for three phase MLI are as follows,  $V_{SL} = 30V$ ,  $V_{SR} = 90V$ , balancing capacitor  $C = 1200\mu$ F each, load resistance  $R = 80\Omega$ , load

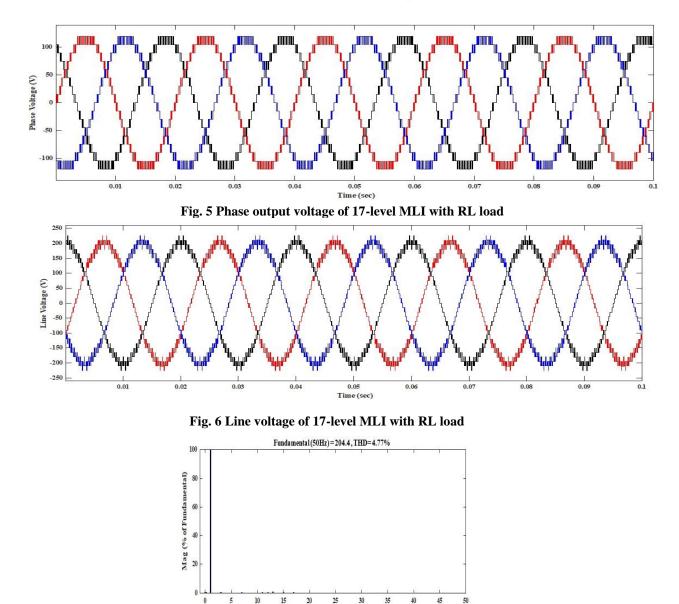

inductance L = 200 mH, modulating index (m) is 0.98 and switching frequency is 5 KHz. Their phase voltage and line voltage are shown in fig. 5 & 6 respectively and FFT analysis in MATLAB/Simulink 2016b is generally applied to determine total harmonic distortion as shown in fig. 7.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u>

Fig. 7 Harmonic component of output voltage spectrum

Harmonic orde

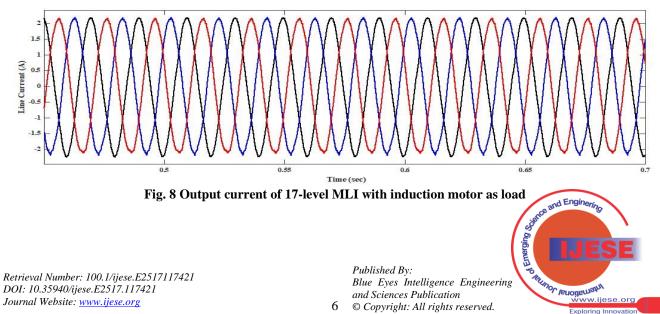

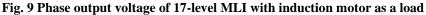

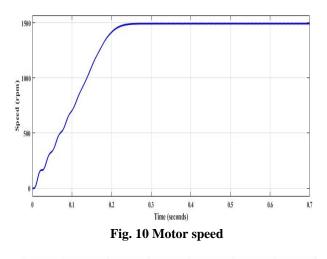

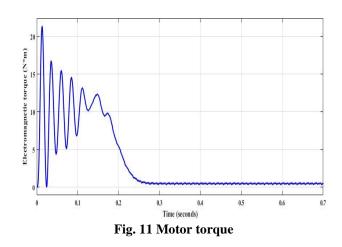

Further to analysis the performance characteristics of an Induction Motor Drive such as speed, torque and stator current along with its line voltage and phase current, an induction motor drive is connected as a three phase load in the proposed three phase multilevel inverter configurations. The corresponding results are displayed by using MATLAB/simulations software. The simulation results of three phase line current and phase voltages of an induction motor drive are depicted in Figures 8 and 9, respectively. Figures 10, 11, and 12 represent the simulation results of induction motor speed, torque and stator current respectively.

#### V. CONCLUSION

This work presents a new version of hybridized asymmetric switched-capacitor multilevel inverter (ASC-MLI) topology with reduced number of device counts. Proposed inverter uses switched capacitors which have inherent self-voltage balancing capabilities and suitable for low-voltage, high- current power and renewable energy applications. The PIV of all the power semiconductor switches are substantially lower than the operational voltage for all the modulation index ranges. Simulation results of the proposed configurations were successfully simulated and examine for 17-level invert which can produce all positive and negative levels with high quality of output voltage waveforms with minimum harmonics. Simulation results of an induction motor drive as a three phase load are also obtained to further validate a reasonable performance of 17-level inverter.

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u>

### REFERENCES

- 1. B.K. Bose, Global energy scenario and impact of power electronics in 21st century, IEEE Trans. Ind. Electron. 60 (7) (2013) 2638\_2651.

- Liu, C.-H., Hsu, Y.-Y.: 'Design of a self-tuning PI controller for a STATCOM using particle swarm optimization', *IEEE Trans. Ind. Electron.*, 2010, 57, (2), pp. 702–715.

- J.D. van Wyk, F.C. Lee, On a future for power electronics, IEEE J. Emerg. Sel. Top. Power Electron 1 (2) (2013) 59\_72.

- M.A.J. Sathik, S.H.E.A. Aleem, R. Kannan, A.F. Zobaa, A new switched DC-link capacitor- based multi-level converter (SDC2MLC), Electr. Power Compon. Syst. 45 (9) (2017) 1001\_1015

- Cheng, Y., Qian, C., Crow, M.L., *et al.*: 'A comparison of diodeclamped and cascaded multilevel converters for a STATCOM with energy storage', *IEEE Trans. Ind. Electron.*, 2006, 53, (5), pp. 1512– 1521.

- Rosas-Caro, J.C., Ramirez, J.M., Peng, F.Z., et al.: 'A DC–DC multilevel boost converter', IET Power Electron., 2010, 3, (1), pp. 129–137.

- Rabinovici, R., Baimel, D., Tomasik, J., et al.: 'Thirteen-level cascaded H-bridge inverter operated by generic phase shifted pulsewidth modulation', IET Power Electron., 2013, 6, (8), pp. 1516–1529.

- Shalchi Alishah, R., Nazarpour, D., Hosseini, S.H., et al.: 'Reduction of power electronic elements in multilevel converters using a new cascade structure', IEEE Trans. Ind. Electron., 2015, 62, (1), pp. 256– 269

- Shalchi Alishah, R., Nazarpour, D., Hosseini, S.H., et al.: 'Novel topologies for symmetric, asymmetric, and cascade switched-diode multilevel converter with minimum number of power electronic components', IEEE Trans. Ind. Electron., 2014, 61, (10), pp. 5300– 5310

- Bendre, A. and Venkataramanan, G. (2006), 'Neutral current ripple minimization in a three-level rectifier', IEEE transactions on industry applications 42(2), 582–590.

Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.

- S. P. Gautam, L. Kumar, and S. Gupta, —Hybrid topology of symmetrical multilevel inverter using less number of devices, *IET Power Electron.*, vol. 8, no. 11, pp. 2125–2135, 2015.

- Masaoud, A., Ping, H.W., Mekhilef, S., et al.: 'New three-phase multilevel inverter with reduced number of power electronic components', IEEE Trans. Power Electron., 2014, 29, (11), pp. 6018– 6029

- Najafi, E., Yatim, A.H.M.: 'Design and implementation of a new multilevel inverter topology', *IEEE Trans. Ind. Electron.*, 2012, 59, (11), pp. 4148–4154

- Gupta, K.K., Jain, S.: 'A novel multilevel inverter based on switched DC sources', *IEEE Trans. Ind. Electron.*, 2014, 61, (7), pp. 3269–3278

- Babaei, E., Gowgani, S.S.: 'Hybrid multilevel inverter using switched capacitor units', *IEEE Trans. Ind. Electron.*, 2014, **61**, (9), pp. 4614– 4621

- P. Lezana, C. Silva, R. Aceiton, Phase disposition PWM implementation for an hybrid multicell converter, IEEE Trans. Industrial Electron. 60 (5) (2013) 1936\_1942

- Jani Rushiraj and P.N. Kapil, "Analysis of Different Modulation techniques for multilevel inverters", in ISTIEEE international conference on power electronics, Intelligent control and energy system, 2016.

### **AUTHOR PROFILE**

**Sanjeev Kumar**, received B.E (Hons.) degree in electrical and electronic engineering from Lakshmi Narain College of Technology & Science (LNCTS), Bhopal (MP). He is now pursuing an M.E. in electrical engineering department with a Power Electronics specialty at Shri G S Institute of Technology and Science in Indore (MP). He is highly enthusiastic in power electronics innovation. Power

electronics, renewable energy, multilevel inverters, fault tolerances, power production analysis, hybrid energy systems, and smart grid are among his research interests.

**Dr. Harish Kumar Verma**, was born at Satna city, M.P. India on 01 July, 1963. He has completed Ph.D. in Power System under Elctrical Engineering department from SGSITS, Indore [M.P]. He has presented and published various research papers in National and International Journals and Conferences. His area of interest includes Image Processing, Speech Processing, Power System optimisations,

ANN, Fuzzy logic and Electrical Drives.

Assoc. Prof. M.P.S. Chawla, received the bachelor's degree (Hons.) in electrical engineering from Ujjain Engineering College (UEC), Ujjain, M.P, India in 1988, and the M.E. degree (Hons.) in Power Electronics from Shri Govindram Seksaria Institute of Technology and Science (SGSITS), Indore, M.P., India, in 1992. He worked as an Assistant Professor with Ujjain Engineering College,

for six months. He is currently an Associate Professor with the Electrical Engineering Department, SGSITS College, Indore, M.P., India. He had been selected as an Executive Editor in International Journal of "Robotics and Artificial Intelligence, Canada". His current interests include intelligence instrumentation, power electronic devices, signal processing, soft computing, higher order statistical techniques and control system. He is also the Professor-Incharge (head), library.

Retrieval Number: 100.1/ijese.E2517117421 DOI: 10.35940/ijese.E2517.117421 Journal Website: <u>www.ijese.org</u> Published By: Blue Eyes Intelligence Engineering and Sciences Publication © Copyright: All rights reserved.