# A Cost Effective Fault Diagnosis Technique for **Cascaded H-Bridge Multilevel Inverter**

### Pavan Mehta, Subhanarayan Sahoo

Abstract: Multilevel Inverters are universally accepted due to their wide range of applications and numerous advantages. In spite of this the reliability of the multilevel inverters are still questionable due to the repeatedly failures of power semiconductor switches. The industries need a cost effective and reliable solution of switch failures, which can be implemented without making major changes in the existing system. If the fault cannot be located within few seconds then fault may cause for multiple switch faults or malfunction of entire system. In this contrast, a cost effective solution to detect open circuit fault of a power semiconductor switch in five level cascaded H-Bridge multilevel inverter has been presented in this paper. The detection method is based on output pole voltage analysis of inverter. The principle of this technique can be implemented on existing system with little modifications. It requires only one voltage sensor per phase, which is already available with the main control system. The output of the multilevel inverter and fault detection results are validate through simulation results.

Keywords : Multilevel Inverter, Cascaded H-bridge (CHB), Fault diagnosis. Output Voltage Analysis.

### I. INTRODUCTION

Multilevel (ML) inverters have opened the doors for wide range of high and medium power applications in the last decade. This is because its remarkable advantages over traditional two level inverters: namely, high voltage blocking capacity, lower total harmonic distortion (THD), low switching losses, low electromagnetic interferences and better output voltage quality [1][2][3]. The structure of the multilevel inverter is such that the voltage across any power semiconductor device remains in ratio of the input DC supply [4]. So, the multilevel inverter power rating is higher even the switch rating is lower. The staircase output helps to reduce the harmonics and gives the better power quality at output side.

The ML inverter has three basic types of structures: Flying

Revised Manuscript Received on February 05, 2020. \* Correspondence Author Pavan Mehta\*, Electrical Engineering Department, Gujarat Technological University, Ahmedabad, India. Email: pvnmehta55@gmail.com Subhanarayan Sahoo, Electrical Engineering Department, Adani Institute of Infrastructure Engineering, Ahmedabad, India. Email: subhanarayan.sahoo@aiim.ac.in

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-nc-nd/4.0/)

Capacitor (FC) [6], Cascaded H-Bridge (CHB) [7] Neutral Point Clamped (NPC) [5]. The other topologies are also derived from these basic topologies, which has ability to overcome some of the disadvantages of basic structures are: Active Neutral Point Clamped (ANPC) [8][9], Hybrid multilevel inverter, Multilevel DC Link inverter (MLDCL) [10] and Modular Multilevel Converter (MMC) [11]. They can be chosen according to the different applications: grid connected inverters, PV connected inverters, motor drives, high voltage DC applications etc [12].

The multilevel structure will knit the output voltage waveform in staircase manner. This can be achieved by apply sequential switching of the power semiconductor device. However, due to the interaction between numbers of switches the chances of fault occurrence are higher. Specifically the switch fault can be categorized into two parts: Open circuit fault and Short circuit fault. The open circuit faults are common in semiconductor devices. It may occur due to gate driver failure or lift off the bond on power circuit for particular switching device due to thermal stresses [13]. Short circuit faults may be due to the thermal ageing because of over current passed through the switch. However, for the short circuit fault fuse based protections are generally provided at the starting of the converter and the circuit must be isolated from the source immediately [14]. In open circuit faults the multilevel inverter allows to operate the load under those faulty condition with reduced power quality. However the fault must be identified with in few seconds to avoid stress or failure of other devices and malfunction of the entire system.

This paper has presented a simple technique to diagnose an open circuit fault in a five level CHB ML inverter. The analysis of faulty and healthy conditions are differentiated. The fault diagnosis technique will sense the output pole voltage and the average factor will be calculated. This average factor is compared with the appropriate threshold value. The probable faulty switch will be identified with this comparison. The simulation results are presented to validate the technique.

### II. CASCADED H-BRIDGE MULTILEVEL **INVERTER**

### A. n-level structure of CHB ML Inverter

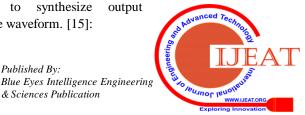

There are (n-1)\*2 power semiconductor switching devices and (n-1)/2 external DC sources are required in a single

phase to synthesize output voltage waveform. [15]:

& Sciences Publication

Published By:

Retrieval Number: B4547129219/2020©BEIESP DOI: 10.35940/ijeat.B4547.029320 Journal Website: www.ijeat.org

$$E_{cell_{xo}} = u \times E_{dc}$$

(1)

where,

$E_{cell_{xo}} = cell output voltage$

$E_{dc_v} = \text{cell input voltage}$

$$u =$$

Switching function (±1 or 0)

The equation of output phase voltage can be derived as following:

$$E_{oxi} = E_{cell_{xt}} + E_{cell_{xj}} \tag{2}$$

where,  $E_{oxi} = output phase voltage$

Fig. 1 5 Level CHB ML inverter

# A. 5 level CHB ML Inverter Switching with Fault and Without Fault:

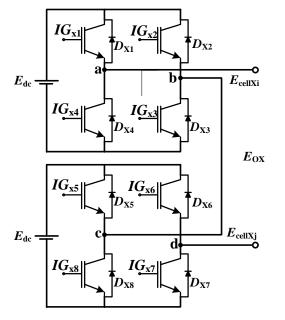

The fig. 2 indicates the path of the current. If there is no fault then for the production of  $+2E_{dc}$ , we need to follow the path indicating by the solid green line. In case of open circuit fault in  $IG_{xl}$  the current will follow the path of dotted red line. From the above operation of faulty and healthy condition, it is clear that the ML inverter will continue to deliver the load current but the power quality will be distorted[15].

Fig. 2 Direction of current on faulty and non-faulty condition

If we apply Kirchhoff's voltage law in the loop the path of the current will be as following:

*loop 1:* Follows the path with green line indicating non faulty condition:

$E_{x1} - IG_{x1} - a - d - IG_{x7} - E_{x2} - IG_{x5} - IG_{x4} - E_{x1}$ loop 2: Follows the path with red line indicating faulty condition:

$a - d - IG_{x7} - E_{x2} - IG_{x5} - IG_{x4} - a.$

# **B.** Cascaded H-Bridge Multilevel Inverter Operation With Fault

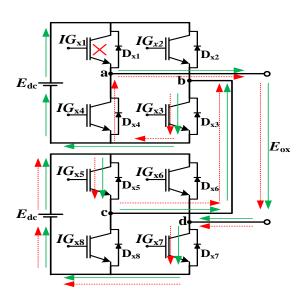

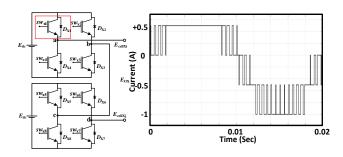

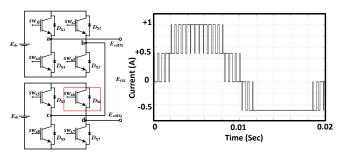

The switching state for Non Faulty and faulty conditions for  $IG_{x1}$  are given in Table I with the respective output voltage state. Fig. 3 to Fig. 5 indicates the output current waveforms for healthy and faulty conditions for  $IG_{x1}$  and  $IG_{x6}$  [15].

## Table I Switching Sequence during healthy and faulty condition

|            | Switching states of switches ( <i>IG<sub>x</sub></i> ) |                  |                  |                  |                  |    |                  |                  |                           |

|------------|--------------------------------------------------------|------------------|------------------|------------------|------------------|----|------------------|------------------|---------------------------|

| Condition  | IG <sub>x1</sub>                                       | IG <sub>x2</sub> | IG <sub>x3</sub> | IG <sub>x4</sub> | IG <sub>x5</sub> | IG | IG <sub>x7</sub> | IG <sub>x8</sub> | O/P                       |

| Non Faulty | I                                                      | 0                | I                | 0                | I                | 0  | I                | 0                | +2 <i>E</i> <sub>dc</sub> |

| Faulty     | 0                                                      | 0                | I                | 0                | I                | 0  | I                | 0                | +E <sub>dc</sub>          |

|            | U                                                      | Ŭ<br>            |                  | 0                |                  | 0  |                  | 0                | • <b>−</b> ac             |

### Fig. 3 Output current waveform at No fault condition

Retrieval Number: B4547129219/2020©BEIESP DOI: 10.35940/ijeat.B4547.029320 Journal Website: <u>www.ijeat.org</u> Published By: Blue Eyes Intelligence Engineering & Sciences Publication

Fig. 4 Output current waveform at  $IG_{XI}$  fault condition

Fig. 5 Output current waveform at  $IG_{X6}$  fault condition

### III. FAULT DIAGNOSIS TECHNIQUE

Fast and accurate fault diagnosis is prime condition for healthy operation of any converter. This fault diagnosis technique is based on the analysis of output voltage pattern. The average factor of output voltage will be taken according to following equation:

$$f(t) = \frac{1}{T} \int_{(t-T)}^{t} f(t) * dt$$

Where T = 1/f and f is fundamental frequency

This average factor is compared with a defined threshold value to ensure the faulty switch. The thresholds are given as below:

| Table III Mean | Value Factor | at different | switch faults |

|----------------|--------------|--------------|---------------|

|                |              |              |               |

|   | Mean Value Factor            | Threshol<br>d Set    | Possible Faulty<br>Switch |

|---|------------------------------|----------------------|---------------------------|

| 1 | 0                            | -                    | -                         |

| 2 | < -E <sub>DC</sub> /4        | - E <sub>DC</sub> /4 | $IG_{XI}$                 |

| 3 | $< +E_{DC}/4$                | $+ E_{DC}/4$         | $IG_{X6}$                 |

| 4 | $> -E_{DC}/4 \& < -E_{DC}/2$ | - E <sub>DC</sub> /2 | $IG_{X3}/IG_{X5}/IG_{X7}$ |

| 5 | >+ $E_{DC}/4 \& < +E_{DC}/2$ | $+ E_{DC}/2$         | $IG_{X2}/IG_{X4}/IG_{X6}$ |

#### IV. SIMULATION AND RESULTS DISCUSSION

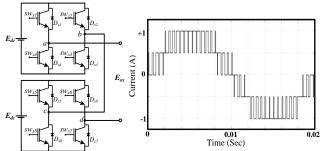

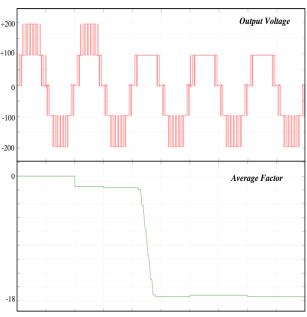

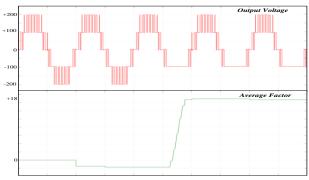

As thee fault occur in any of the switch of the cell, there will be a missing state in output voltage depending on the

faulty switch. If the open circuit fault occurs in  $IG_{XI}$ , then the top most level (+2E<sub>DC</sub>) from the output voltage waveform will be absent. Similarly if the fault occurs  $IG_{X6}$  then bottom most (-2E<sub>DC</sub>) level will be absent in the output voltage waveform.  $IG_{X3}$ ,  $IG_{X5}$  and  $IG_{X7}$  are responsible for +E<sub>DC</sub> voltage state and  $IG_{X2}$ ,  $IG_{X4}$  and  $IG_{X8}$  are responsible for -E<sub>DC</sub> voltage state. The simulated results of faulty switch and respective absent output voltage state is shown in fig. 6 and fig. 7.Table 3. Shows the simulation parameters:

| Simulation Component           | Remarks    |

|--------------------------------|------------|

| Power Semiconductor Device (8) | IGBT       |

| DC Source (2)                  | 100V       |

| R-L Load                       | 100Ω, 10mH |

| Control technique              | LS-PWM     |

**Table III Simulation Parameters**

The simulation results are also presented in tabular form in Table. 4. The threshold set and actual average factor value validates the simulation results. The defined threshold level is  $\langle -E_{DC}/4$  for IG<sub>X1</sub> and  $\langle +E_{DC}/4$  for IG<sub>X6</sub>. The same value is reflected in output -18V and +18V respectively. Similarly, it can be observed for the other switches.

**Table IV Simulation Results**

|    | itch<br>ult     | Threshold Set        | Mean Value Factor<br>Actual Value |  |  |

|----|-----------------|----------------------|-----------------------------------|--|--|

| 10 | 5 <sub>X1</sub> | <-E <sub>DC</sub> /4 | -18V                              |  |  |

| IC | 5 <sub>X6</sub> | <+E <sub>DC</sub> /4 | +18V                              |  |  |

Fig. 6 Fault Indication of IG<sub>X1</sub> by average factor

Published By: Blue Eyes Intelligence Engineering & Sciences Publication

#### A Cost Effective Fault Diagnosis Technique for Cascaded H-Bridge Multilevel Inverter

Fig. 7 Fault Indication of  $IG_{X6}$  by average factor

### V. CONCLUSION

The fault identification can be done using this technique without making any changes in the existing system. Due to this industries need not to change the entire system control. This technique only requires a voltage sensor per phase. The open circuit fault of a switch can be detected in one switching period. Moreover this technique can be implemented for n number of levels by voltage pattern analysis. This can be also implemented on any multilevel converters.

### REFERENCES

- H. Akagi, "Multilevel Converters: Fundamental Circuits and Systems," Proc. IEEE, vol. 105, no. 11, pp. 2048–2065, 2017.

- J. Rodríguez et al., "Multilevel Voltage-Source-Converter Topologies for.pdf," vol. 54, no. 6, pp. 2930–2945, 2007.

- P. Rodriguez, M. D. Bellar, R. S. Muñoz-Aguilar, S. Busquets-Monge, and F. Blaabjerg, "Multilevel-clamped multilevel converters (MLC 2)," IEEE Trans. Power Electron., vol. 27, no. 3, pp. 1055–1060, 2012.

- A. El-hosainy, H. A. Hamed, S. Member, and H. Z. Azazi, "A Review of Multilevel Inverter Topologies, Control Techniques, and Applications," no. December, pp. 19–21, 2017.

- J. Rodriguez, S. Member, S. Bernet, P. K. Steimer, and I. E. Lizama, "A Survey on Neutral-Point-Clamped Inverters," vol. 57, no. 7, pp. 2219–2230, 2010.

- S. Dargahi, M. Sabahi, S. Eskandari, E. Babaei, and V. Dargahi, "Flying-capacitor stacked multicell multilevel voltage source inverters: analysis and modelling," IET Power Electron., vol. 7, no. 12, pp. 2969–2987, 2014.

- F. Z. Z. Peng, J. W. W. McKeever, and D. J. J. Adams, "Cascade multilevel inverters for utility applications," Proc. IECON'97 23rd Int. Conf. Ind. Electron. Control. Instrum. (Cat. No.97CH36066), vol. 2, pp. 2–7, 1997.

- P. Mehta and M. Kumar, "Capacitor voltage balancing and THD analysis in ANPC multilevel inverter," 2018 IEEMA Eng. Infin. Conf., pp. 1–5, 2018.

- P. Mehta, A. Kunapara, and N. Karelia, "Improvement in Switching Strategy Used for Even Loss Distribution in ANPC Multilevel Inverter," Procedia Technol., 2015.

- G. J. Su, "Multilevel DC-link inverter," IEEE Trans. Ind. Appl., vol. 41, no. 3, pp. 848–854, 2005.

- A. António-Ferreira, C. Collados-Rodríguez, and O. Gomis-Bellmunt, "Modulation techniques applied to medium voltage modular multilevel converters for renewable energy integration: A review," Electr. Power Syst. Res., vol. 155, pp. 21–39, 2018.

- J. Rodríguez, J. S. Lai, and F. Z. Peng, "Multilevel inverters: A survey of topologies, controls, and applications," IEEE Trans. Ind. Electron., vol. 49, no. 4, pp. 724–738, 2002.

- R. Choupan, S. Golshannavaz, D. Nazarpour, and M. Barmala, "A new structure for multilevel inverters with fault-tolerant capability against open circuit faults," Electr. Power Syst. Res., vol. 168, no. May 2018, pp. 105–116, 2019.

- P. Lezana, R. Aguilera, and J. Rodríguez, "Fault Detection on Multicell Converter Based on Output Voltage Frequency Analysis," IEEE Trans. Ind. Electron., vol. 56, no. 6, pp. 2275–2283, 2009.

- P. Mehta, M. Kumar, and S. Sahoo, "Fault Diagnosis in Five-level CHB Inverter using Normalization Factor and THD Analysis," India Int. Conf. Power Electron. IICPE, vol. 2018-Decem, no. 1, pp. 1–5, 2019.

#### **AUTHORS PROFILE**

**Pavan Mehta** PhD. pursuing, Electrical Engineering, Gujarat Technological University, Ahmedabad, India. Currently he is working with Adani Institute of Infrastructure Engineering, Ahmedabad. He has published his research articles in reputed journals and conferences. Multilevel Inverter Drives Power Electronic Converters.

are areas of interest. He is student member of IEEE and Life Time member of ISTE.

**Dr. Subhanarayan Sahoo** Post-doctoral fellow from Institute for Plasma Research. PhD. From KIIT Univarsity, Odisha, India. Currently he is working as an Associate Professor in Adani Institute of Infrastructure Engineering, Ahmedabad. Dr. Sahoo has published more

than 20 research articles in reputed journals and conferences. He is member of IEEE, Life time member of ISTE. High Voltage, Electromagnetics and Power electronics are his research areas.

Retrieval Number: B4547129219/2020©BEIESP DOI: 10.35940/ijeat.B4547.029320 Journal Website: <u>www.ijeat.org</u> Published By: Blue Eyes Intelligence Engineering & Sciences Publication