# Multicarrier PWM Strategies for Hybrid Symmetrical Multilevel Inverter with Reduced Switch Count

# Ujwala Gajula, Gouthami Eragamreddy

Abstract: Multilevel inverters are widely used for high power and high voltage applications. The performance of multilevel inverters are superior to conventional two level inverters in terms of reduced total harmonic distortion, higher dc link voltages, lower electromagnetic interference and increased quality in the output voltage waveform. This paper presents a single phase hybrid eleven level multilevel inverter topology with reduced switch count to compensate the above mentioned disadvantages. This paper also presents various high switching frequency based multi carrier pulse width modulation strategies such as Phase Disposition PWM Strategy (PDPWM), Phase Opposition and Disposition PWM Strategy (PODPWM), Alternate Phase opposition Disposition PWM (APODPWM), Carrier Overlapping PWM (COPWM), Variable frequency carrier PWM (VFPWM), Third Harmonic Injection PWM (TFIPWM) applied to the proposed eleven level multilevel inverter and is analyzed for RL load. FFT analysis is carried out and total harmonic distortion, fundamental output voltage are calculated. Simulation is carried out in MATLAB/SMULINK.

Keywords: Multi Carrier Pulse Width Modulation, Total Harmonic Distortion, Hybrid Multilevel Inverter, High Switching Frequency PWM.

#### I. **INTRODUCTION**

In recent years, there has been a lot of increase in interest on the concept of multilevel power conversion. The theory of power conversion multilevel inverters has gained lot of advantages [1]-[3]. Recent researches have evolved in the introduction of novel inverter topologies and unique modulation techniques. However the mostly addressed multilevel inverter topologies are neutral-point clamped (NPC) inverter, the flying capacitor inverter, and the cascade inverter. Among these cascaded H Bridge configuration is more attractive because of its simplicity in design. Conventional H-Bridge inverters have applications in industrial side because of easy way of controlling and simple switching configuration. However the number of components and switching losses are quite high. "Although the above mentioned conventional MLI finds number of applications, all these topologies need more number of switches to produce higher voltages. So in the recent years the research focuses on reducing the number of components. Reducing the number of diodes used, voltage sources, switches and capacitors can improve the quality as well as reduce the switching losses, overall cost etc.," [5].

Revised Manuscript Received on June 15, 2020. \* Correspondence Author

Ujwala Gajula\*, Assistant Professor, EEE Department, G.N.I.T.S, India. E-mail: gjujwala@gmail.com

Gouthami Eragamreddy , Assistant Professor, EEE Department, G.N.I.T.S, India. E-mail: gouthami.erp@gmail.com

© The Authors. Published by Blue Eyes Intelligence Engineering and Sciences Publication (BEIESP). This is an open access article under the CC BY-NC-ND license (http://creativecommons.org/licenses/by-ncnd/4.0/)

In this paper a new symmetrical 11 level hybrid multilevel inverter topology is proposed with different PWM techniques to obtain more accurate waveform with minimal switching losses and lower harmonic distortion. This paper analyzes a comparative study carried out on different high switching frequency based carrier Pulse width modulation Techniques.

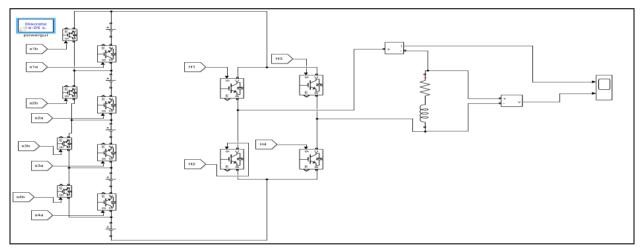

#### II. PROPOSED HYBRID INVERTER TOPOLOGY

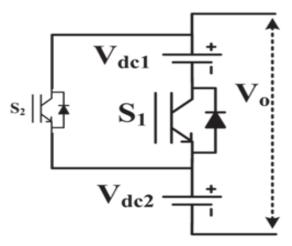

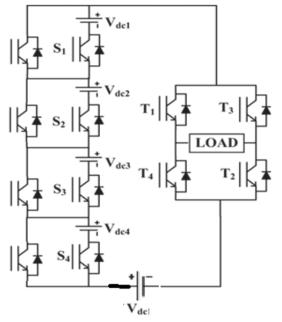

The proposed hybrid eleven level multilevel inverter mainly eliminates higher number of switches that are helpful in producing the output voltages when compared to the existing multilevel inverters. The fundamental structure of the proposed hybrid inverter topology is given in fig.1 (a). It consists of two isolated DC sources and six unidirectional switches  $(T_1, T_2, T_3, T_4, S_1 \text{ and } S_2)$ . The basic unit generates five level of output voltage  $(2V_{dc}, V_{dc}, 0, -V_{dc}, -2V_{dc})$ . The switching states are given in Table 1. Fig.1 (b) gives the proposed 11 level symmetrical novel inverter topology with reduced switch count.

Fig.1. a) Basic Structure

Retrieval Number: E9792069520/2020©BEIESP DOI: 10.35940/ijeat.E9792.069520 Journal Website: <u>www.ijeat.org</u>

Published By:

& Sciences Publication

© Copyright: All rights reserved.

# Multicarrier Pwm Strategies for Hybrid Symmetrical Multilevel Inverter with Reduced Switch Count

| Table1. Switching States for Dasic Unit |                                |                                                                       |                   |

|-----------------------------------------|--------------------------------|-----------------------------------------------------------------------|-------------------|

| S.No.                                   | Level of<br>Combined<br>Signal | Switches in<br>ON State                                               | Output<br>Voltage |

| 1                                       | 2                              | $S_1, T_1, T_2$                                                       | $+2V_{dc}$        |

| 2                                       | 1                              | $S_2, T_1, T_2$                                                       | $+ V_{dc}$        |

| 3                                       | 0                              | T <sub>1</sub> , T <sub>3</sub>                                       | 0                 |

| 4                                       | -1                             | S <sub>2</sub> , T <sub>3</sub> , T <sub>4</sub>                      | -V <sub>dc</sub>  |

| 5                                       | -2                             | <b>S</b> <sub>1</sub> , <b>T</b> <sub>3</sub> , <b>T</b> <sub>4</sub> | $-2V_{dc}$        |

Table1. Switching States for Basic Unit

Fig.1. b) proposed MLI Topology

In the propose hybrid Multilevel Inverter topology the number of switches  $(N_S)$  required to produce number of levels  $(N_L)$  is given by eq (1) & (2) and the maximum output voltage is given by eq (3).

$$Ns = 2n+2 ---- (1)$$

Where n is the number of DC sources used

$$N_L = 2Ns - 5$$

------ (2)

$V_{Max,O} = n Vdc$  ----- (3)

The switching states of the proposed hybrid multilevel inverter from the Simulink model Fig 8. are given in Table 2.

| Table 2. S | Switching | States of | f the Prop | osed MLI |

|------------|-----------|-----------|------------|----------|

|------------|-----------|-----------|------------|----------|

| S.No | Conducting Switches                                       | Output<br>Voltage |

|------|-----------------------------------------------------------|-------------------|

| 1    | $S_{4b}, S_{3b}, S_{2b}, S_{1b}, H_1, H_4$                | $+V_{dc}$         |

| 2    | $S_{1a}$ , $H_1$ , $H_4$ , $S_{4b}$ , $S_{3b}$ , $S_{2b}$ | $+2V_{dc}$        |

| 3  | $S_{2a}, S_{1b}, H_1, H_4, S_{4b}, S_{3b}$                                                         | +3V <sub>dc</sub> |

|----|----------------------------------------------------------------------------------------------------|-------------------|

| 4  | $S_{3a}, S_{2b}, S_{1b}, H_1, H_4, S_{4b}$                                                         | $+4V_{dc}$        |

| 5  | $S_{4a}, S_{3b}, S_{2b}, S_{1b}, H_1, H_4$                                                         | +5V <sub>dc</sub> |

| 6  | $H_1, H_4$                                                                                         | 0                 |

| 7  | $S_{4b}$ , $S_{3b}$ , $S_{2b}$ , $S_{1b}$ , $H_2$ , $H_3$                                          | -V <sub>dc</sub>  |

| 8  | $S_{1a}$ , $H_2$ , $H_3$ , $S_{4b}$ , $S_{3b}$ , $S_{2b}$                                          | -2V <sub>dc</sub> |

| 9  | $S_{2a}$ , $S_{1b}$ , $H_2$ , $H_3$ , $S_{4b}$ , $S_{3b}$                                          | -3V <sub>dc</sub> |

| 10 | S <sub>3a</sub> ,S <sub>2b</sub> ,S <sub>1b</sub> ,H <sub>2</sub> ,H <sub>3</sub> ,S <sub>4b</sub> | -4V <sub>dc</sub> |

| 11 | $S_{4a}$ , $S_{3b}$ , $S_{2b}$ , $S_{1b}$ , $H_2$ , $H_3$                                          | -5V <sub>dc</sub> |

### III. PULSE WIDTH MODULATION STRATEGIES

In the literature of MLI's various pulse width modulation strategies are proposed. A classification of these strategies is proposed in reference [4] and is updated in reference [6]. These strategies are classified based on the switching frequency as:

- 1. Low Switching Frequency PWM Techniques (selective harmonic elimination (SHE), space vector control, and nearest level control)

- High Switching Frequency PWM Techniques (Multicarrier PWM and space vector pulse-width modulation [SVPWM]).

Multi carrier based PWM methods depending on different carrier signals is selected for the proposed topology. Carrier PWM based methods have more than one carrier wave it can be either triangular wave or saw tooth wave. As far as the carrier signals are concerned there are multiple control parameters of freedom, which includes amplitude, offset between carriers, frequency and phase of each carrier. In this paper the following multicarrier based modulation strategies are proposed.

- Phase Disposition PWM (PDPWM)

- Phase Opposition and Disposition PWM (PODPWM)

- Alternate Phase opposition Disposition PWM (APODPWM)

- Carrier Overlapping PWM (COPWM)

- Variable frequency carrier PWM (VFPWM)

- Third Harmonic Injection PWM (TFIPWM)

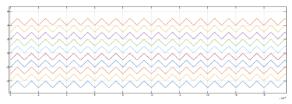

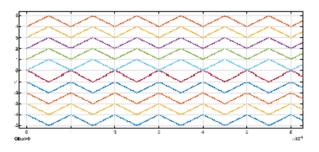

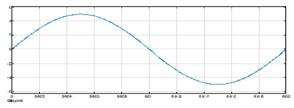

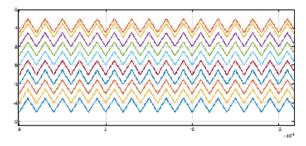

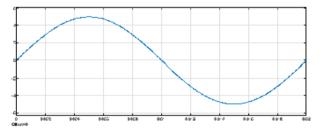

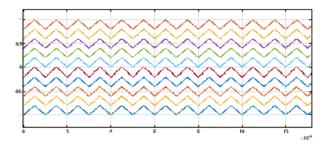

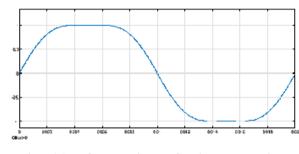

A. Phase Disposition PWM Strategy: In this method, the entire carrier signals above and below zero reference are in same phase. Carrier and reference wave arrangement is shown in fig. 2(a) & (b).

Published By: Blue Eyes Intelligence Engineering & Sciences Publication © Copyright: All rights reserved.

Fig.2 (a) Multi carrier signals for PD-PWM

Fig.2 (b) Reference signal of PD-PWM

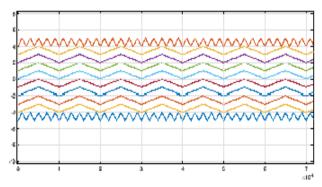

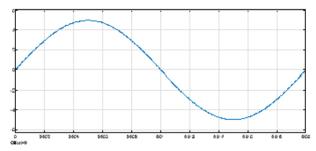

**Phase Opposition and Disposition PWM Strategy:** In this method, all the carriers have same amplitude and frequency. All the carriers above zero reference are in same phase and all the carriers below zero reference are in same phase but 180 degrees phase shifted with respect the above carriers. The arrangement is shown in fig. 3(a) & (b).

Fig.3 (a) Multi carrier signals for POD-PWM

Fig.3 (b) Reference signal of POD-PWM

**B.** Alternate Phase opposition Disposition PWM Strategy: In this method, all the carriers have same amplitude and frequency. All the alternate carriers are in same phase and the others are phase shifted by 180 degrees. The arrangement is shown in fig. 4(a) & (b).

Fig.4 (a) Multi carrier signals for APOD-PWM

Retrieval Number: E9792069520/2020©BEIESP DOI: 10.35940/ijeat.E9792.069520 Journal Website: <u>www.ijeat.org</u>

Fig.4 (b) Reference signal of APOD-PWM

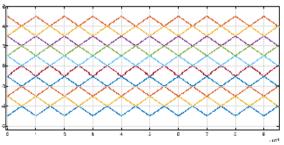

**C. Carrier Overlapping PWM Strategy:** In this method, the carriers are overlapped with each other as shown in fig. 5(a) & (b). The amount of overlapping decides the quality of the output waveform.

Fig.5 (a) Multi carrier signals for CO-PWM

Fig.5 (b) Reference signal of APOD-PWM

**D. Variable frequency carrier PWM Strategy:** In this method, the frequency of the carriers is not same. Some carriers have same frequency others have different frequency. The arrangement is shown in 6(a) & (b).

Fig.6 (a) Multi carrier signals for VF-PWM

Published By: Blue Eyes Intelligence Engineering & Sciences Publication © Copyright: All rights reserved.

# Multicarrier Pwm Strategies for Hybrid Symmetrical Multilevel Inverter with Reduced Switch Count

Fig.6 (b) Reference signal of VF-PWM

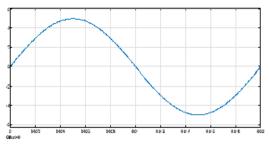

Third Harmonic Injection PWM Strategy: In this technique the effect of third harmonic is cancelled in the output voltage spectrum. The gain is increased by the addition of third harmonic component to the fundamental. The arrangement is shown in 7(a) & (b).

Fig.7 (a) Multi carrier signals for Third Harmonic Injection -PWM

Fig.7 (b) Reference signal of Third Harmonic Injection -PWM

# **IV. RESULTS AND SIMULATION**

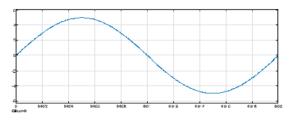

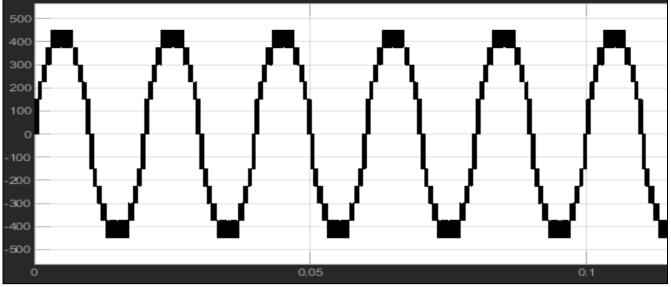

Fig.8 gives the simulation model of the proposed eleven level multilevel inverter topology and fig.9. Shows the eleven level output voltage generated.

Fig.8 Simulink Model of Eleven Level Hybrid Multilevel Inverter with Reduced Switch Count

Published By:

& Sciences Publication

Fig.9. Output Voltage of Eleven Level Hybrid Multilevel Inverter with Reduced Switch Count

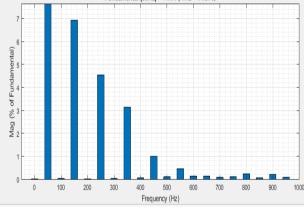

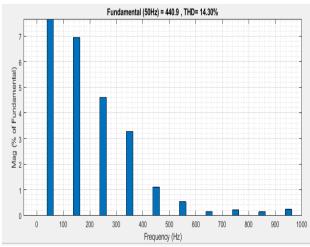

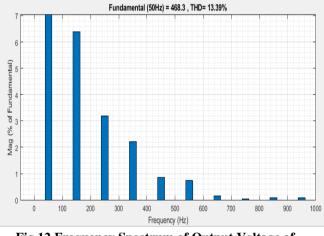

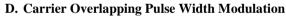

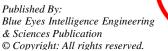

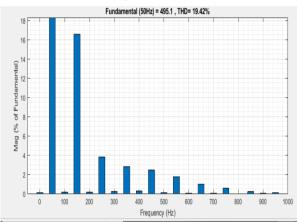

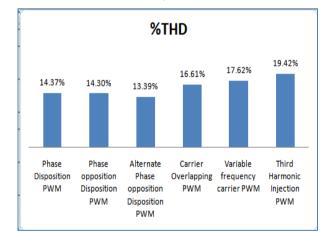

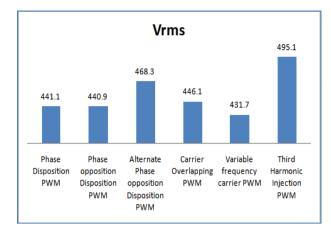

Fig.10, Fig.11, Fig.12, Fig.13, Fig.14 and Fig.15 shows the FFT analysis of PD, POD, APOD, CO and THI PWM. Table 3 gives the comparison between different pulse width modulation techniques versus % THD and Vrms.

Fig.10. Frequency Spectrum of Output Voltage of PD-PWM

B. Phase Opposition Disposition Pulse Width Modulation

Fig.11 Frequency Spectrum of Output Voltage of POD-PWM

Retrieval Number: E9792069520/2020©BEIESP DOI: 10.35940/ijeat.E9792.069520 Journal Website: <u>www.ijeat.org</u> C. Alternate Phase Opposition Disposition Pulse Width Modulation

Fig.12 Frequency Spectrum of Output Voltage of APOD-PWM

Fig.13 Frequency Spectrum of Output Voltage of CO-PWM

# Multicarrier Pwm Strategies for Hybrid Symmetrical Multilevel Inverter with Reduced Switch Count

# E. Variable frequency carrier Pulse Width Modulation

Fig.14 Frequency Spectrum of Output Voltage of VF-PWM

### F. Third Harmonic Injection Pulse Width Modulation

Fig.15 Frequency Spectrum of Output Voltage of Third Harmonic Injection –PWM

Fig.16 Graph of Different PWM Techniques versus % THD

## Fig.17 Graph of Different PWM Techniques versus Vrms

| Table 3: Comparison Table of different PWM |

|--------------------------------------------|

| Techniques versus THD & RMS Output Voltage |

| S.No | PWM Technique                                    | % THD  | Vrms   |

|------|--------------------------------------------------|--------|--------|

| 1.   | Phase Disposition<br>PWM                         | 14.37% | 441.1V |

| 2.   | Phase opposition<br>Disposition PWM              | 14.30% | 440.9V |

| 3.   | Alternate Phase<br>opposition Disposition<br>PWM | 13.39% | 468.3V |

| 4.   | Carrier Overlapping<br>PWM                       | 16.61% | 446.1V |

| 5.   | Variable frequency<br>carrier PWM                | 17.62% | 431.7V |

| 6.   | Third Harmonic<br>Injection PWM                  | 19.42% | 495.1V |

# V. CONCLUSION

The performance analysis of any power converter depends on the pulse width modulation technique employed and so the multilevel inverters. In this paper the results of single phase eleven level hybrid symmetrical multilevel inverter with reduced switch count with RL load is obtained through MATLAB/SIMULINK, various performance indices like total harmonic distortion and  $V_{rms}$  associated with power quality issues are measured, analyzed and tabulated. From the fig.16 and fig.17 it is observed that APOD PWM provides output with relatively lower distortion and Third Harmonic Injection PWM provides high fundamental output voltage achieving maximum DC utilization.

Retrieval Number: E9792069520/2020©BEIESP DOI: 10.35940/ijeat.E9792.069520 Journal Website: <u>www.ijeat.org</u> Published By: Blue Eyes Intelligence Engineering & Sciences Publication © Copyright: All rights reserved.

# REFERENCES

- L. M. Tolbert, F. Z. Peng, and T. G. Habetler, "Multilevel converters for large electric drives," IEEE Trans. Ind. Appl., vol. 35, no. 1, pp. 36–44, Jan./ Feb. 1999.

- Xiaoming Yuanand Ivo Barb, "Fundamentals of a New Diode Clamping Multilevel Inverter", IEEE Trans. on Power Electronics, Vol.15, No.4, July 2000.

- Jih-Sheng Lai, IEEE, and Fang Zheng Peng, "A New Breed of flying Capacitor Multilevel Converter" IEEE Transactions On Industry Applications, Vol. 32, No. 3, May/June 1996

- J. Rodriguez, J.S. Lai, F.Z. Peng, Multilevel inverters: a survey of topologies, controls, and applications, IEEE Trans. Industrial Electron. 49 (2002) 724-738.

- R. R. Karasani, V. B. Borghate, P. M. Meshram, H. M. Suryawanshi, and S. Sabyasachi, "A three-phase hybrid cascaded modular multilevel inverter for renewable energy environment," IEEE Trans. Power Electron., vol. 32, no. 2, pp. 1070–1087, Feb. 2017.

- L.G. Franquelo, J. Rodriguez, J.I. Leon, S. Kouro, R. Portillo, M.A.M. Prats, The age of multilevel converters arrives, Industrial Electron. Magaz. IEEE 2 (2) (2008) 28-39

#### **AUTHORS PROFILE**

Ujwala Gajula, working as Assistant Professor in G.Naryanamma Institute of Technology and Science (For Women), Shaikpet Hyderabad. She received her B-Tech in Electrical & Electronics Engineering from JNTUH in the year 2008 and M.Tech in Power Electronics & Electric Drives from JNTUH in the year 2010. Presently she is Pursuing Part time PhD in Annamalai university, Chidambaram. She is

member of IEI, IAENG and ISTE. Her areas of interest are Power Quality, Renewable Energy Sources.

Gouthami Eragamreddy, working as an Assistant Professor in G.Naryanamma Institute of Technology and Science (For Women), Shaikpet Hyderabad. She received her B. E in Electrical and Electronics Engineering from Anna University in 2005 and M.Tech Embedded systems in 2010 from JNTUH. Presently she is Pursuing Part time PhD in Visvesvaraya Technological University, Karnataka.

She is the Member of IEI, IAENG and ISTE. Her areas of interest are Electric Vehicles, Power Electronics, Embedded systems and IOT.