### PSP103.8 MOSFET MODEL: IMPROVEMENT OF THE CHARGE MODEL FOR SHORT CHANNEL TRANSISTORS

#### MOS-AK ESSDERC/ESSCIRC event

O. Rozeau\*, S. Martinie\*, G.D.J. Smit\*\*, A.J. Scholten\*\*, N. Derrier\*\*\*, A. Juge\*\*\*, P. Scheer\*\*\* and T. Poiroux\*

\*CEA-Leti (F), \*\*NXP (NL), \*\*\*STMicroelectronics (F)

September 6<sup>th</sup>, 2021

- Introduction to PSP

- Overview of recent PSP versions

- Parasitic charges included in PSP103.7 and before

- Inner fringe charge model

- Inversion charges of overlaps

- Conclusion

- PSP is a surface potential based model for deep-submicron bulk MOSFET

- Its development is supported by the CMC (Compact Model Coalition) : https://si2.org/cmc/

- In December 2005, PSP has been elected a new industrial standard model by the CMC. This

initial version was based on MM11 (from NXP Semiconductors) and SP (from Pennsylvania

State University and later at Arizona State University).

- PSP contains all relevant physical effects such as mobility degradation, velocity saturation, DIBL, gate leakage currents, lateral doping gradient effects, STI stress, etc.

- PSP meets numerical requirements for Digital, Analog-Mixed Signal, and RF circuit designs, in particular continuous derivation of currents and charges is insured.

- Since the first standard version, the developers have provided 16 releases.

• Since 2015, CEA-Leti is the main developer of PSP

#### Website address:

https://www.cea.fr/cea-tech/leti/pspsupport

#### Contains:

- Release information

- Model documentation for PSP and JUNCAP2

- Downloadable Verilog-A codes

• Since 2015, CEA-Leti is the main developer PSP: one release per year

| Date    | Release  | Major improvements/features                                                                                                                                       |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 08/2016 | PSP103.4 | Modeling of edge MOSFET to reproduce the subthreshold hump effect<br>Improved model of the subthreshold slope degradation induced by the<br>short channel effects |

| 04/2017 | PSP103.5 | New parameters for Coulomb scattering effect in mobility<br>Improvement of temperature dependence of the flatband voltage                                         |

| 12/2017 | PSP103.6 | New model of interface states for better accuracy of $g_m/I_d$                                                                                                    |

| 02/2019 | PSP103.7 | Improvement of gate leakage currents model<br>Possibility of charge model decoupling from IV for accurate CV of<br>short channel transistors in saturation        |

| 07/2020 | PSP103.8 | Model of Inner fringe charges<br>Inversion charge of overlaps                                                                                                     |

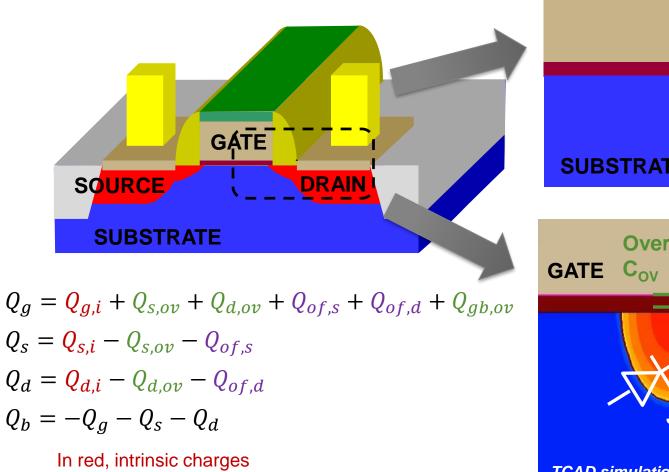

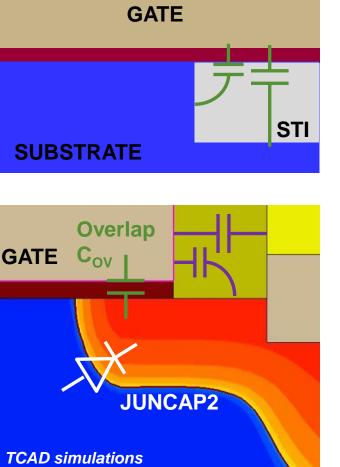

## PARASITIC CHARGES INCLUDED IN PSP103.7 AND BEFORE

• Parasitic capacitances: COV, CFR, CGBOV, junction capacitances

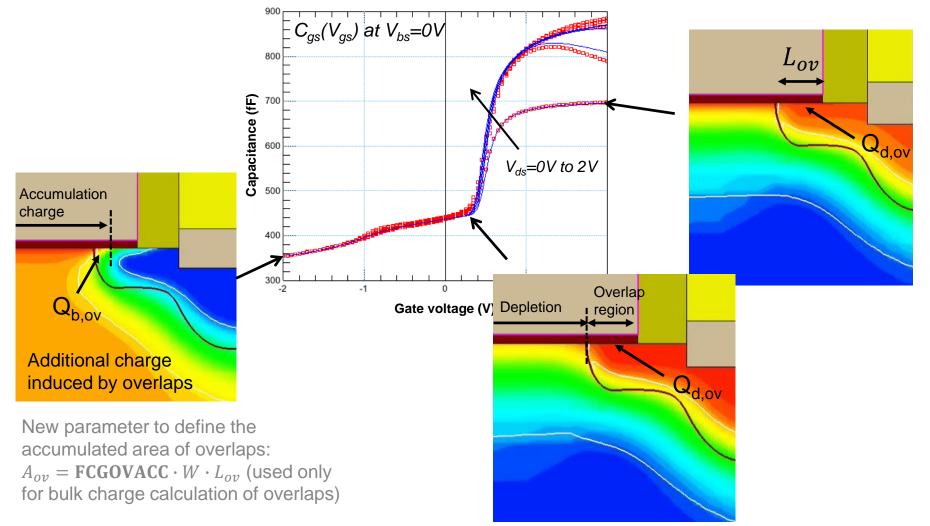

# Bias independent gate to substrate overlap charge $Q_{gb,ov}$

Bias independent outer fringe charges:  $Q_{of,s}$ , and  $Q_{of,d}$

Bias dependent gate to drain/source overlap charges  $Q_{s,ov}$  and  $Q_{d,ov}$ These charges model don't include the inversion regime

#### leti **PARASITIC CHARGES INCLUDED IN PSP103.7 AND BEFORE** Ceatech

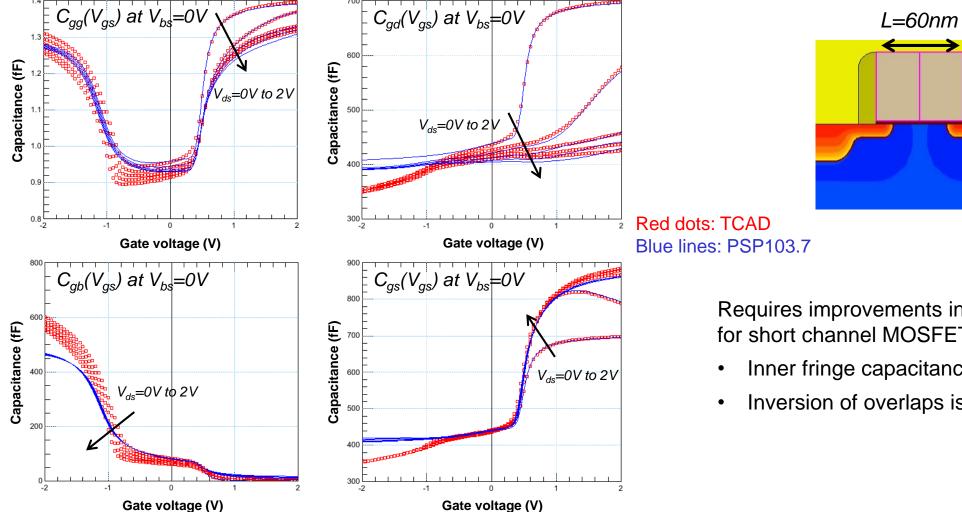

Analysis of PSP103.7 versus TCAD simulations: CV for short channel MOSFET

Requires improvements in accumulation regime for short channel MOSFET:

- Inner fringe capacitances are not modeled

- Inversion of overlaps is not modeled

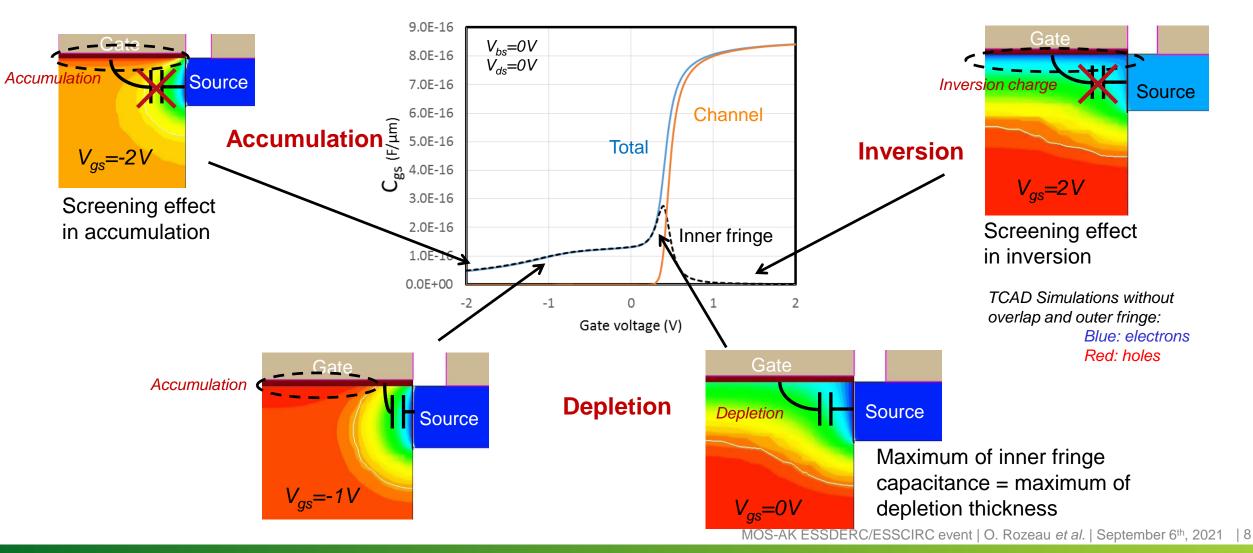

• Intrinsic MOSFET: inner fringe charges versus channel charge

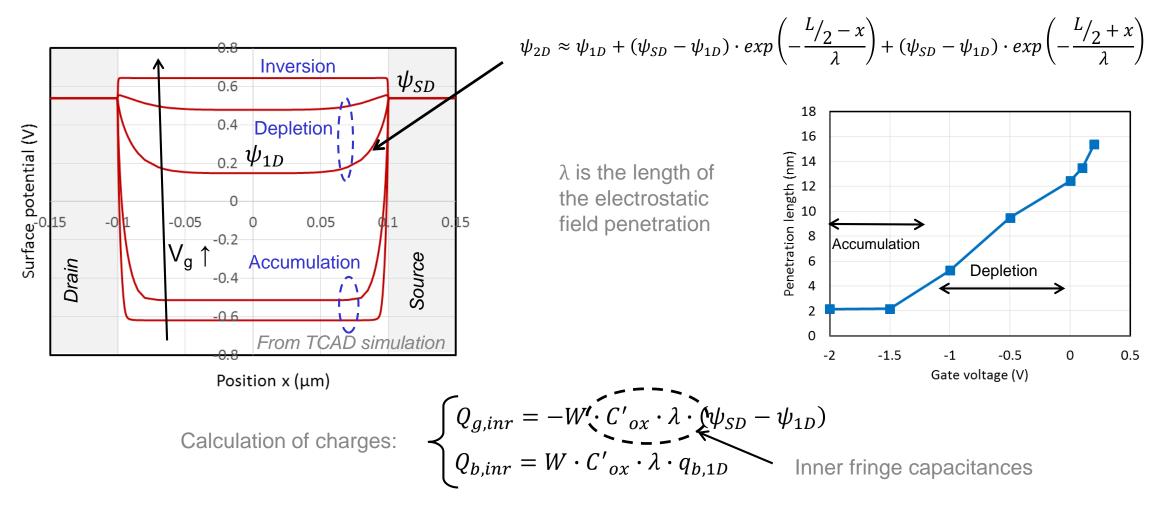

• Surface potential profile near to the drain and the source

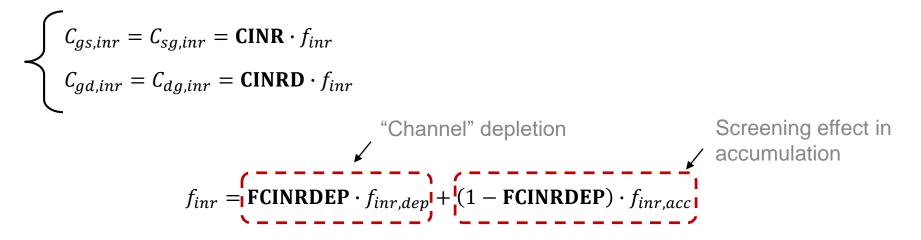

• Modeling method of inner fringe charge

Rigorous calculation of  $\lambda$  is very complex and depends on doping profiles, thicknesses, etc.

In depletion, we can write the inner fringe capacitance as:

Modeling method of inner fringe charge

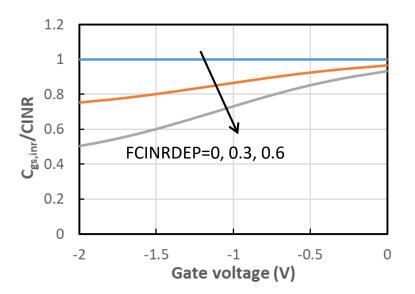

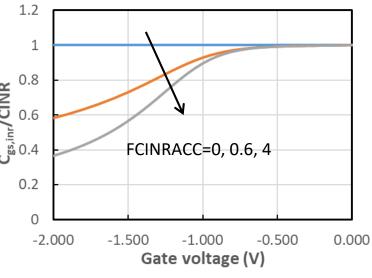

In accumulation, the decrease of inner fringe charges due to screening effect is done by:

$C_{gs,inr} = C_{sg,inr} = \mathbf{CINR} \cdot f_{inr,acc}$  $C_{ad.inr} = C_{dg,inr} = \mathbf{CINRD} \cdot f_{inr,acc}$

$f_{inr,acc} \text{ is a} \\ \text{mathematical} \\ \text{function to} \\ \text{reproduce the} \\ \text{behavior} \end{cases} \begin{cases} V_{\text{g,inr}} = V_{\text{GB,ac}}^* - \text{DVFBINR} + V_{\text{inr,max}} \\ V_{x1,\text{inr}} = MAXA(V_{\text{g,inr}}, V_{\text{inr,max}}, a_{\text{inr}}) \\ V_{x2,\text{inr}} = V_{x1,\text{inr}} \cdot (2 \cdot V_{x1,\text{inr}} - V_{\text{inr,max}} - V_{\text{g,inr}}) \\ V_{\text{g,inr,eff}} = \frac{V_{\text{g,inr}} \cdot V_{\text{inr,max}}}{V_{x1,\text{inr}}} \\ \text{Parameter for screening} \\ \text{effect in accumulation} \\ f_{\text{q,inr}} = \sqrt{1 - \text{FCINRACC}} \cdot V_{\text{g,inr,eff}} \\ f_{\text{inr,acc}} = \left(\frac{1}{2 \cdot f_{\text{q,inr}}} - 1\right) \cdot \frac{V_{x2,\text{inr}} + V_{\text{g,inr}} \cdot (V_{\text{inr,max}} - V_{x1,\text{inr}})}{V_{x2,\text{inr}}} \cdot \frac{V_{\text{inr,max}}}{V_{x1,\text{inr}}} + 1 \end{cases}$

• Modeling method of inner fringe charge

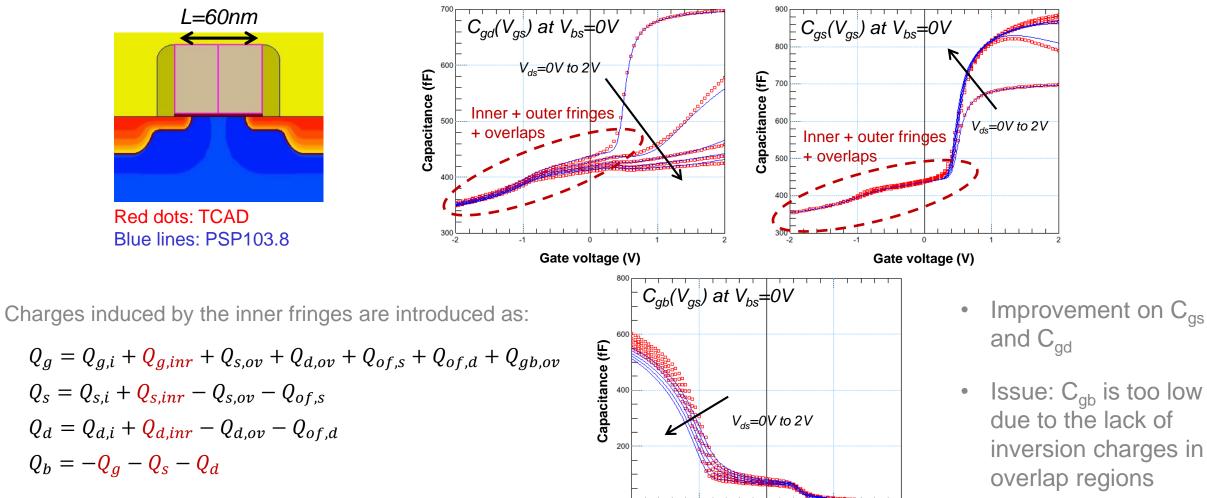

In general case, by combining both effects:

In PSP, the calculations of the inner fringe <u>charges</u> are based on these equations

• Parameter description of inner fringe charge model

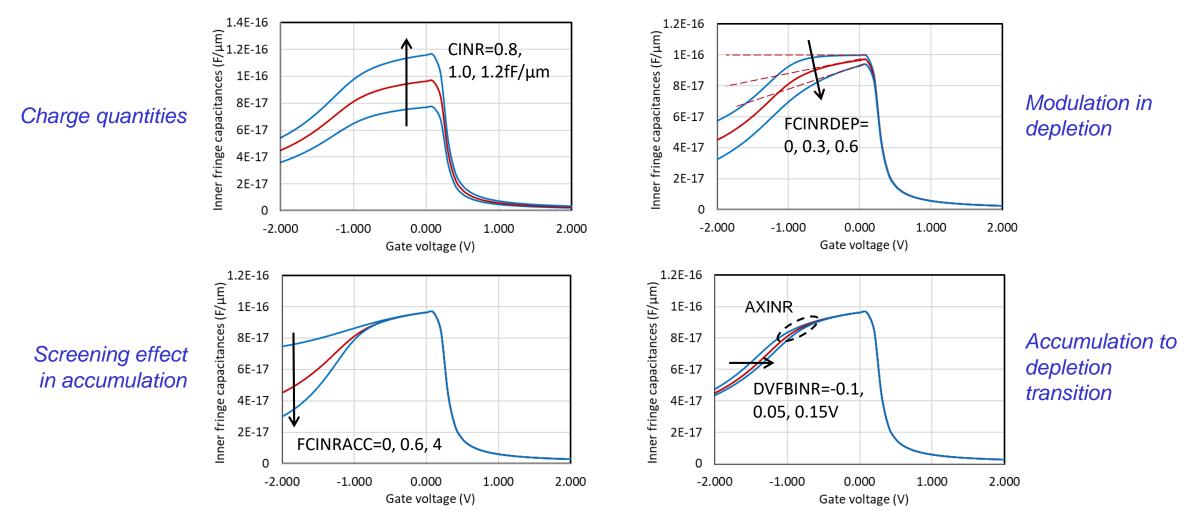

• Introduction and validation of inner fringe charge model

-1

0

• Analysis from TCAD simulations: partial inversion of overlaps

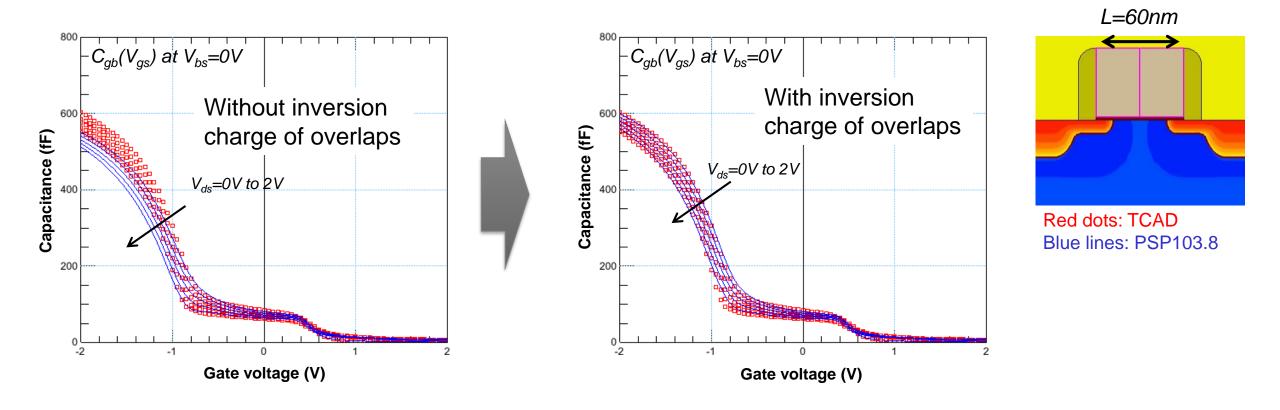

• Introduction of overlap charges in inversion (channel in accumulation)

Charges induced by the inversion of overlaps are added at the gate and the bulk

$$\begin{aligned} Q_g &= Q_{g,i} + Q_{g,inr} + Q_{s,ov} + Q_{d,ov} + Q_{of,s} + Q_{of,d} + Q_{gb,ov} + Q_{g,ov} + Q_{g,dov} \\ Q_s &= Q_{s,i} + Q_{s,inr} - Q_{s,ov} - Q_{of,s} \\ Q_d &= Q_{d,i} + Q_{d,inr} - Q_{d,ov} - Q_{of,d} \\ Q_b &= -Q_g - Q_s - Q_d \end{aligned}$$

The calculation of Lambert W-function

The calculation of these charges is based on the use of \_ambert W-function:

$$x_{\rm gb,eff,ov} = \ln \left( 1 + \exp \left( \text{CGOVACCG} \cdot \left( \frac{V_{\rm GB} - \boldsymbol{V}_{\rm FB}}{2 \cdot \phi_{\rm T}} + \boldsymbol{\Delta} \boldsymbol{x}_{\rm gb,ov} \right) \right) \right)$$

$$\begin{split} Q_{\rm g,ov} &= -2 \cdot \phi_{\rm T} \cdot \text{FCGOVACC} \cdot \text{CGOV} \cdot \frac{x_{\rm gb,eff,ov}}{\text{CGOVACCG}} \cdot \left(1 - \frac{\ln\left(1 + x_{\rm gb,eff,ov}\right)}{2 + x_{\rm gb,eff,ov}}\right) \\ x_{\rm gb,eff,dov} &= \ln\left(1 + \exp\left(\text{CGOVACCG} \cdot \left(\frac{V_{\rm GB} - \boldsymbol{V}_{\rm FB}}{2 \cdot \phi_{\rm T}} + \boldsymbol{\Delta} x_{\rm gb,dov}\right)\right)\right) \end{split}$$

$$Q_{\rm g,dov} = -2 \cdot \phi_{\rm T} \cdot \mathbf{FCGOVACC} \cdot \mathbf{CGOVD} \cdot \frac{x_{\rm gb,eff,dov}}{\mathbf{CGOVACCG}} \cdot \left(1 - \frac{\ln\left(1 + x_{\rm gb,eff,dov}\right)}{2 + x_{\rm gb,eff,dov}}\right)$$

• Improvement of gate-bulk capacitance for short channel transistors

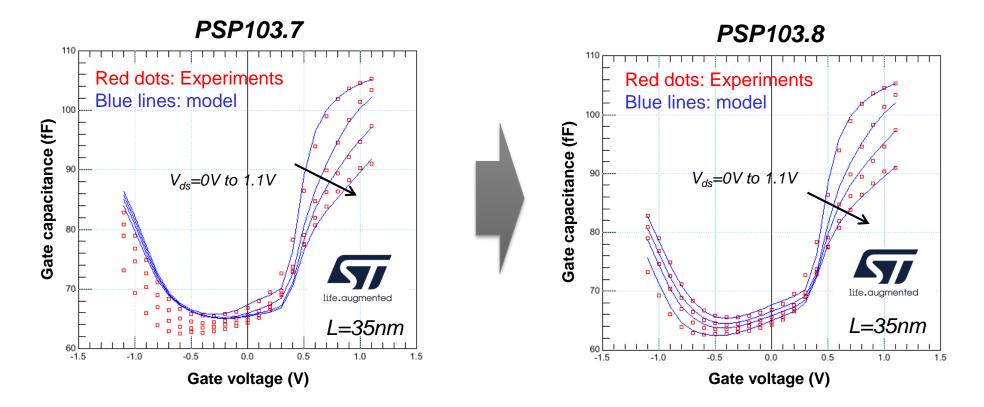

• Model validation using experimental data

Better description of CV characteristics in accumulation and depletion regimes for short channel MOSFET (here L=35nm)

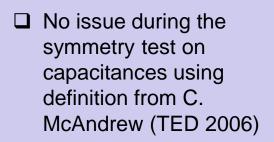

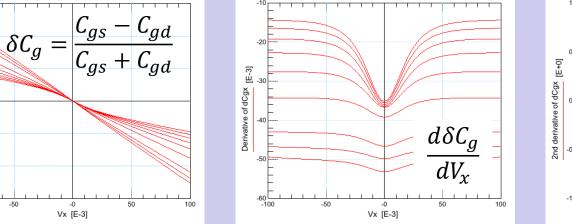

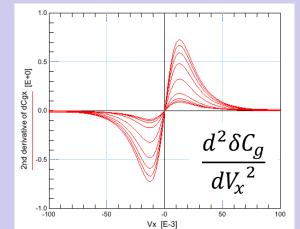

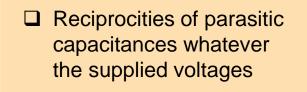

• Validations of Source-Drain symmetry and capacitance reciprocities

L=60nm  $V_{ds}=0V \text{ to } 2V$   $V_{bs}=0V$

$V_{as}$ =-2V to 0V

[E-3]

deltaCgx.s ! dCgx

- PSP103.8 is a significant release for the modeling of short channel CV in accumulation regime

- Where to find PSP releases

- Verilog-A versions of PSP are free downloadable at <u>https://www.cea.fr/cea-tech/leti/pspsupport</u>

- PSP can be used in most of commercial circuit simulators

- PSP103.8.0 has been released in July 2020

- PSP103.8.1, containing minor bug fixes and new parameters for temperature control, has been released in Avril 2021

CEA-Leti, technology research institute Commissariat à l'énergie atomique et aux énergies alternatives Minatec Campus | 17 avenue des Martyrs | 38054 Grenoble Cedex | France www.leti-cea.com