ublishing

i his is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/1.5134690

## Fan-out enabled spin wave majority gate

Abdulqader Mahmoud,<sup>1, a)</sup> Frederic Vanderveken,<sup>2</sup> Christoph Adelmann,<sup>2</sup> Florin Ciubotaru,<sup>2</sup> Said Hamdioui<sup>1</sup>, and Sorin Cotofana<sup>1</sup>

<sup>1)</sup>Delft University of Technology, Mekelweg 2, 2628 CD Delft, The Netherlands <sup>2)</sup>IMEC, Kapeldreef 75, B-3001 Leuven, Belgium

By its very nature, Spin Wave (SW) interference provides intrinsic support for Majority logic function evaluation. Due to this and the fact that the 3-input Majority (MAJ3) gate and the Inverter constitute a universal Boolean logic gate set, different MAJ3 gate implementations have been proposed. However, they cannot be directly utilized for the construction of larger SW logic circuits as they lack a key cascading mechanism, i.e., fan-out capability. In this paper, we introduce a novel ladder-shaped SW MAJ3 gate design able to provide a maximum fan-out of 2 (FO2). The proper gate functionality is validated by means of micromagnetic simulations, which also demonstrate that the amplitude mismatch between the two outputs is negligible proving that an FO2 is properly achieved. Additionally, we evaluate the gate area and compare it with SW state-of-the-art and 15nm CMOS counterparts working under the same conditions. Our results indicate that the proposed structure requires 12x less area than the 15 nm CMOS MAJ3 gate and that at the gate level the fan-out capability results in 16 % area savings, when compared with the state-of-the-art SW majority gate counterparts.

The rapid increase of available row data led to an abrupt downscaling of the CMOS technology in order to meet the continuously increasing application demand for high performance computation platforms<sup>1</sup>. However, CMOS scaling became more and more difficult due to various technological hurdles such as: (i) quantum mechanics related phenomena and physical limitations such as leakage<sup>2</sup>, (ii) high failure rate and short life time of devices<sup>3</sup>, and (iii) steep fabrication cost increase not justifiable by scaling economical benefits<sup>2</sup>. As a result, different emerging technologies are now explored as potential candidates for future partial/total CMOS replacement<sup>4,5</sup>. One of them relies on Spin Waves (SW) interference within magnetic waveguides<sup>4,5</sup>. Preliminary investigations suggest that SW based computing potentially enables ultra low power consumption at acceptable delay and has great scalability potential<sup>4,5</sup>. SW computing is based on wave interference, which can be either constructive or destructive depending on the interfering SWs phases. This principle is used to build SW logic gates. Spin wave interferometer, e.g., Mach-Zhender interferometer was used to investigate this phenomena $^{6-10}$ . To this end, different logic and Majority gate designs were introduced<sup>11-21</sup> they all, with the exception of <sup>16,17</sup>, make use of bent waveguides through which weak signals as SWs do not properly propagate and attenuate very fast.

As 3-input Majority gate (MAJ3) together with Inverter form a universal Boolean logic gate set, they provide the foundation for the potential implementation of complex SW circuits<sup>11</sup>. However, building larger circuits requires gates with fanout capability, which none of the previously mentioned designs posses. Thus, if a certain Majority gate has to provide its output to more than one gate input, it has to be replicated. For example, if a gate output has a fanout f > 1, all the gates on its cone of influence starting for the circuit primary inputs have to be replicated f times. Given that practical circuits include many such gates the lack of fanout capa-

<sup>a)</sup>Electronic mail: A.N.N.Mahmoud@tudelft.nl

bility results in substantial area and energy consumption overheads. The SW circuit fanout issue has been addressed and by magnonic splitters<sup>22–25</sup> or caustic beams<sup>22</sup> based solutions have been proposed. However, the presented designs require large frequency bands and are not scalable. If the magnetic field is applied in plane, the T-shape magnonic splitter<sup>23</sup> relies on SW mode (backward volume and surface) conversion. Given that the dispersion relation is magnetic field direction dependent, such an approach results in complex SW interference patterns, which precludes the utilization of T-shape magnonic splitters in the design of large SW circuits. The possibility to implement a magnonic splitter by voltage controlled reconfigurable nano-channels was discussed in<sup>24</sup>, however, no detailed analysis of the spin wave quality after splitting has been provided. Additionally, a nonlinear directional coupler that allows SW transmission from a waveguide to another was investigated<sup>25</sup> and demonstrated the SW power dependency of this phenomenon. However, this concept splits the SW energy and cannot provide SW replication, which is crucial for gate fanout achievement.

In view of the above, it can be concluded that SW based computing with potential ultra low energy consumption cannot become reality without gate intrinsic fanout capabilities. Here, we overcome this challenge and introduce a generic SW Majority gate structure that provides natural fanout support. Our structure is based on an area efficient 3-input Majority ladder-shaped SW gate structure that is able to provide a maximum fanout of 2. This concept has been validated by means of micromagnetic simulations with the Object Oriented Micromagnetic Framework (OOMMF).

Generally speaking, the proposed gate can operate with any SW type, however, each SW type has its proper dispersion relation, which plays a crucial role in the actual gate design. Magnetostatic Spin Waves (MSW) can be classified into three limiting cases: Magnetostatic Surface Spin Wave (MSSW), Backward Volume Magnetostatic Spin Wave (BVMSW), and Forward Volume Magnetostatic Spin Wave (FVMSW)<sup>26</sup>. Depending on the wave propagation direction, BVMSW and MSSW exhibit different dispersion relations. This complicates the circuit design because similar SW propagation in

ublishing

i his is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/1.5134690

both horizontal and vertical directions is required. For FVM-SWs, which propagate in a perpendicular plane to the static magnetization orientation, SW exhibit the same dispersion relation regardless of the wave vector orientation. In this view, we rely on them in the gate design introduced in the following lines.

Different SW excitation (and detection) methods exist, e.g., microstrip antennas<sup>27,28</sup>, magnetoelectric cells<sup>29–31</sup>, spin orbit torque<sup>32,33</sup>. A spin wave propagates through the waveguide with a wavelength  $\lambda$ , frequency f, amplitude A, and phase  $\phi$ . Information can be encoded in its amplitude, phase, or both of them. If multiple SWs coexist in a waveguide, the computation can be performed using wave interference. Two waves with the same  $\lambda$ , A, and f can interfere constructively or destructively depending on their relative phase difference: (i) inphase SWs interfere constructively and the resulting wave has doubled amplitude, (ii) out-of-phase SWs interfere destructively, and therefore cancel each other. If more than 2 equal  $\lambda$  and f SWs interfere, the result reflects a Majority decision, i.e., if more SW have  $\phi = \pi$  (logic "1") than  $\phi = 0$  (logic "0"), the resultant SW has  $\phi = \pi$ , and  $\phi = 0$  otherwise. This means that SW interference provides natural support for direct (no Boolean gates are required) Majority gate implementations. For example, a CMOS implementation of a 3-input Majority gate requires 18 transistors whereas a single magnetic waveguide is enough for the SW counterpart $^{11,16}$ . In the linear regime, it is possible to have simultaneous propagation of spin waves with different frequencies. The information can be encoded in the phase of the spin wave at each and every frequency, therefore, SW gates inherently enable parallel computation on shared hardware resources. Additionally, if the involved waves have different amplitude, they still constructively or destructively interfere depending on phase difference. However, this generates multiple SWs with different amplitude values, which could be beneficial for the realization of multi-valued logic gates. In the most general case, SWs with different amplitudes, phases, wavelengths, and frequencies can be excited and intricately interfere in the same waveguide. This provides promising alternative avenues towards novel, yet to be discovered, SW based computing paradigms and systems.

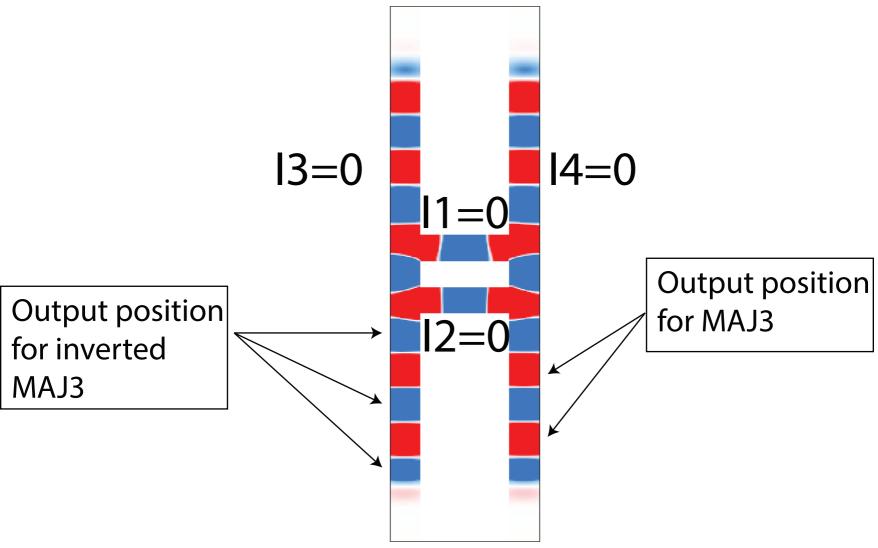

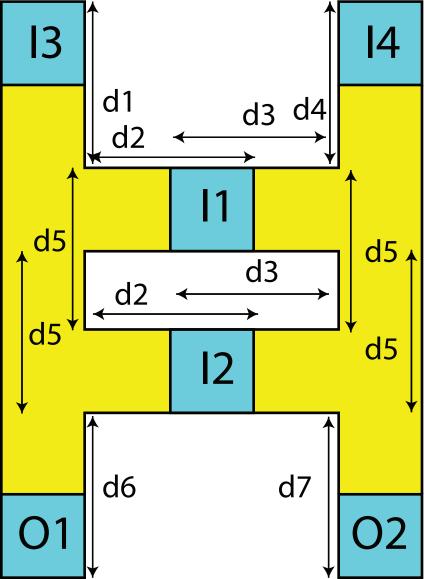

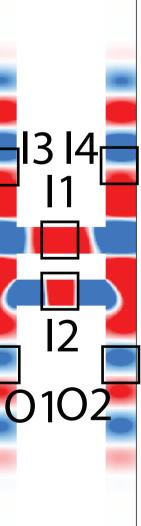

In this paper, we propose a 3-input Majority gate (MAJ3) that has a ladder-shape structure, as depicted in Figure 1. The inputs are excited at  $(I_1, I_2, I_3, I_4)$  and the outputs are read from  $(O_1, O_2)$ .

To obtain a proper interference pattern at the crosspoints, the waveguide width w has to be less than or equal to the wavelength  $\lambda$ . Also, the excited SWs should have the same amplitude A. In addition, all excited SWs are required to have the same frequency to achieve the desired interference pattern. We propose a generic device layout, its dimensions and some critical distances  $d_i$  (where i=1,2,...,7) are expressed in terms of spin wave wavelengths as indicated in Figure 1. For example, if  $\lambda$  wavelength SWs have to constructively interfere when they have the same phase and destructively otherwise,  $d_1, d_2, d_3, d_4$ , and  $d_5$  must be equal with  $n\lambda$  (n = 1, 2, 3, ...). If the opposite behaviour is targeted,  $d_1, d_2, d_3, d_4$  and  $d_5$  must be equal with  $\frac{n}{2}\lambda$  (n = 1, 3, 5, ...). Moreover, to obtain a proper

FIG. 1. 3-input Majority Gate with Fanout Capability.

fanout of 2, i.e., outputs with the same energy levels, the structure has to be symmetric, thus  $d_1$  to  $d_5$  must have the same value.

In contrast with CMOS gates, SW gates can provide both direct and inverted output by properly adjusting the output transducer position versus the output interference point. In this way the direct and inverted result can be read at a distance of  $n\lambda(n = 1, 2, 3, ...)$  and  $\frac{n}{2}\lambda(n = 1, 2, 3, ...)$  from the last interference, respectively. In our case, MAJ(a,b,c) and  $\overline{MAJ}(a,b,c)$  are obtained at  $d_6 = d_7 = n\lambda(n = 1, 2, 3, ...)$  and  $d_6 = d_7 = (\frac{n}{2}\lambda(n = 1, 3, 5, ...))$ , respectively, and both outputs exhibit the same energy because of the structure symmetry.

Intuitively speaking, the Majority gate operates as follows: (i) SWs with appropriate phases are initiated at  $I_1$ ,  $I_2$ ,  $I_3$ , and  $I_4$ to the targeted logic value (0 or 1). (ii) The excited SWs propagate (in both directions in the horizontal and vertical waveguides) and interfere when meeting each other. The resulting wave propagates toward the outputs  $O_1$  and  $O_2$ . Thanks to the symmetry of the device and the isotropic behavior of the spin waves in this configuration, the waves arriving at the gate outputs are identical, thus, the 3-input Majority gate exhibits a fanout of 2. It is worth-mentioning that  $I_3$  has effect on  $O_2$ as spin-wave signal excited at  $I_3$  propagates through  $I_1$  and  $I_2$ . Also,  $I_4$  has effect on  $O_1$  as spin-wave signal excited at  $I_4$ propagates through  $I_1$  and  $I_2$ . In addition, spin wave excited at  $I_1$  and  $I_2$  face edges while its propagation to the output, in contrast to  $I_3$  and  $I_4$ , which have straight path to the outputs. Therefore,  $I_3$  and  $I_4$  are excited at lower energy than  $I_1$  and  $I_2$ as will be discussed further later in this paper.

It is worth-mentioning that  $I_3$  has effect on  $O_2$  as the SW excited at  $I_3$  propagates through  $I_1$  and  $I_1$ . Similarly,  $I_4$  has effect on  $O_1$  spin-wave signal excited at  $I_4$  propagates through  $I_1$  and  $I_2$ . In addition, SWs excited at  $I_1$  and  $I_2$  face edges while they propagate towards the outputs while  $I_3$  and  $I_4$  generated SWs have straight path to  $O_1$  and  $O_2$ , respectively. Therefore,  $I_3$  and  $I_4$  are excited at lower energy than  $I_1$  and  $I_2$  as further discussed in the paper.

We validate the proposed majority gate by means of micromagnetic simulations while making use of  $Fe_{60}Co_{20}B_{20}$ waveguides, with a Perpendicular Magnetic Anisotropy (PMA) field greater than the magnetic saturation, which means that no external magnetic field is required for proper gate operation. We instantiated a MAJ3 gate for waveguide width w = 75 nm, and to simplify the interference pattern, we selected a larger wavelength than w, SW wavelength  $\lambda = 165$

TABLE I. MAJ3 Truth Table.

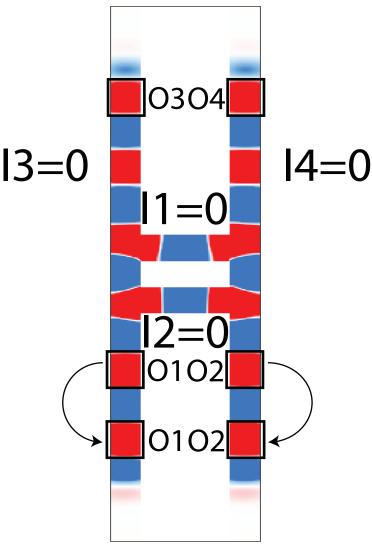

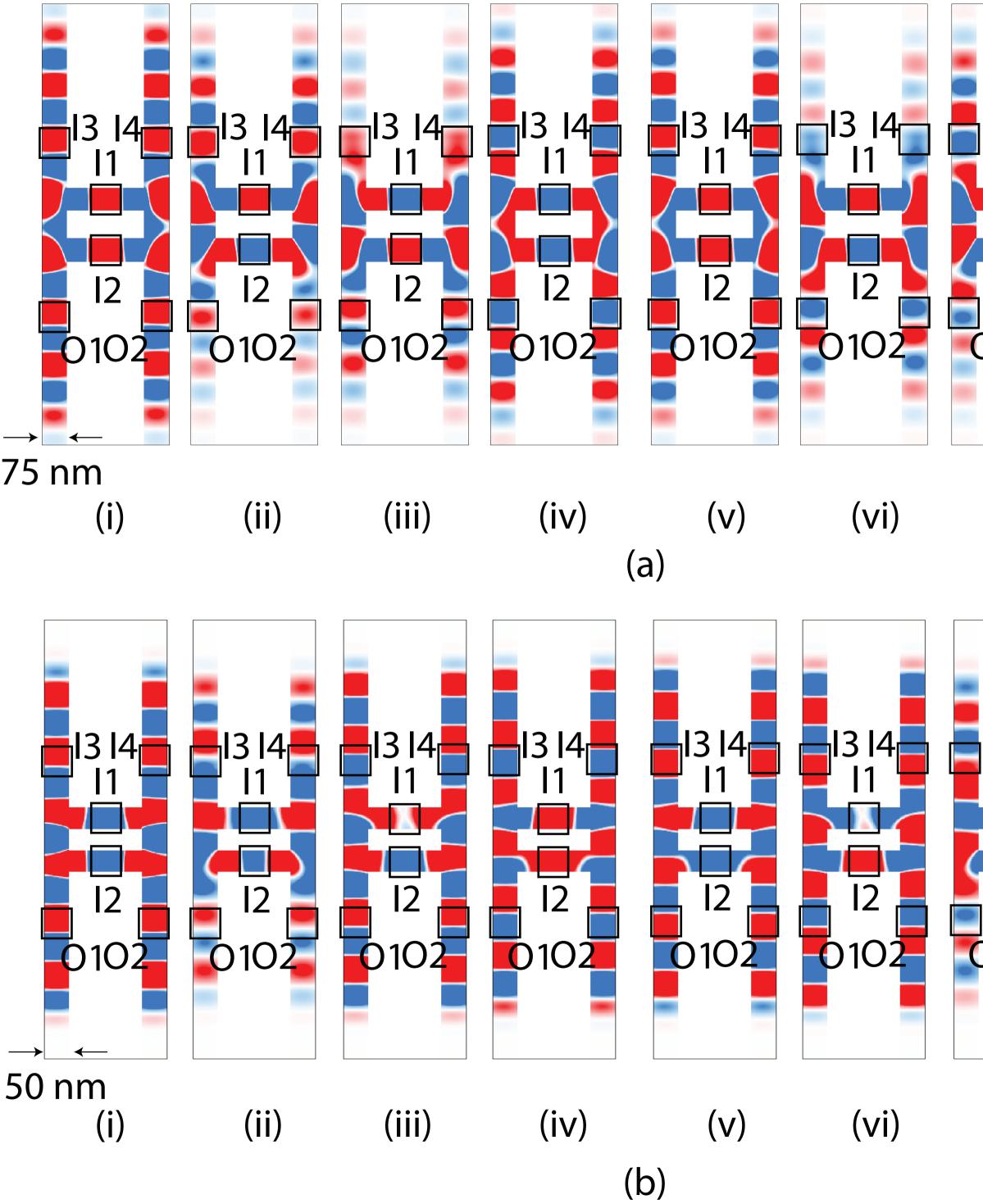

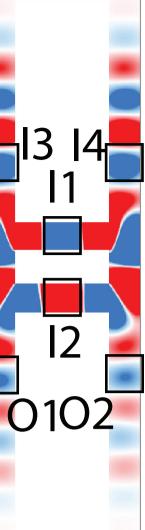

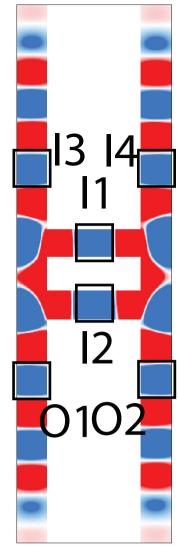

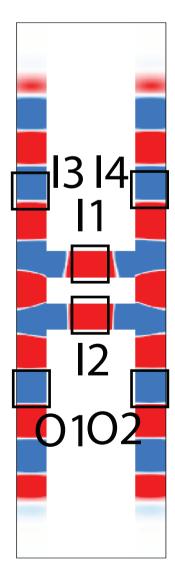

FIG. 2. Color coded snapshots of the magnetization state demonstrating all majority functions for two width of SW waveguide: (a) 75 nm and (b) 50 nm. Blue represents logic 1, which presents a phase of  $\pi$ , red presents logic 0 which presents phase 0, the input order is  $(I_3 I_2 I_1)$  and  $(I_4 I_2 I_1)$ , and i), ii), iii), iv), v), vi), vii), and viii) present the gate reaction to  $(0\ 0\ 0)$ ,  $(0\ 0\ 1)$ ,  $(0\ 1\ 0)$ ,  $(0\ 1\ 1)$ ,  $(1\ 0\ 0)$ ,  $(1\ 0\ 1)$ , (1 1 0), and (1 1 1) input patterns, respectively.

nm, which implies that  $d_1 = d_2 = d_3 = d_4 = d_5 = d_6 = d_7 =$ 165 nm. Further, we assume the following values of the relevant parameters<sup>34</sup>: magnetic saturation  $M_s = 1.1 \times 10^6 A/m$ , exchange stiffness  $A_{exch} = 18.5 \ pJ/m$ , damping constant  $\alpha =$ 0.004, perpendicular anisotropy constant  $k_{ani} = 8.3177 \times 10^5$  $J/m^3$ , and waveguide thickness t = 1 nm. We calculated the FVMSW dispersion relation for these parameters, and for  $\lambda = 165$  nm, and  $k = 2\pi/\lambda = 38$  rad/ $\mu$ m, the SW frequency is determined to be f = 6.5 GHz. To get some indication of the MAJ3 scaling implications, we also designed smaller structures, e.g., w = 50 nm, with  $\lambda = 110$  nm and f = 9 GHz. This makes the distances  $d_1 = d_2 = d_3 = d_4 = d_5 = d_6 = d_7 = 110$ nm.

The proposed design combines two Majority gates operating in parallel on the same input set as it can be observed in Table I.  $I_1$ ,  $I_2$ , and  $I_3$  constitute the first Majority gate with its output being detected at  $O_1$ , whereas  $I_1$ ,  $I_2$ , and  $I_4$  con-

FIG. 3. Inverted Outputs  $O'_1$  and  $O'_2$  and Non-inverted Outputs  $O_1$ and  $O_2$ .

stitute the second Majority gate with  $O_2$  as output. Figure 2 presents OOMMF simulation results for the proposed w = 75nm and w = 50 nm MAJ3 gates, under all possible input combinations. Note that in the Figure blue presents logic "1" (i.e., phase of  $\pi$ ), red presents logic "0" (i.e., phase 0), the input order is  $(I_3 I_2 I_1)$  and  $(I_4 I_2 I_1)$ , and i), ii), iii), iv), v), vi), vii), and viii) captures the gate reaction to  $(0\ 0\ 0)$ ,  $(0\ 0\ 1)$ ,  $(0\ 1\ 0)$ , (0 1 1), (1 0 0), (1 0 1), (1 1 0), and (1 1 1) input patterns, respectively. As it can be observed from Figure 2, the results are in agreement with the MAJ3 true table in Table I. If  $I_1 =$  $I_2 = I_3 = 0$  or the majority of the inputs are 0 then  $O_1 = O_2$ = 0 (red), whereas if the majority of the inputs are 1, then the outputs  $O_1$  and  $O_2$  are 1 (blue), as expected. In addition, it can be noticed in Figure 2 that the scaling doesn't affect the functionality of the Majority gate.

Figure 3 presents the possibility of having the inverted and non-inverted outputs by adjusting the reading position. As one can observe in Figure 3, the inverted output  $(O'_1 \text{ and } O'_2)$  of the Majority gates can be obtained by just shifting the reading position to a  $\frac{n}{2}\lambda$  position.

By post-processing the OOMMF simulations, we estimated the MAJ3 gate delay, i.e., the maximum time it takes for the inputs to propagate to the output, as 1.5 ns and 1 ns for the w = 75 nm and w = 50 nm structures, respectively. To investigate the waveguide width reduction influence on SW group velocity Vg, we calculated the group velocities from micromagnetic simulation and obtained  $Vg_{50nm} = 1.15 \ \mu$ m/ns and  $Vg_{75nm} = 1 \ \mu \text{m/ns}$  for w = 50 nm and w = 75 nm structures, respectively. We also note that SWs are traveling shorter distances for the smaller structure, e.g., distance  $I_3$  to  $O_1$  is 380 nm for w = 50 nm and 570 nm for w = 75 nm. This imply that the  $I_3$  to  $O_1$  propagation takes 330 ps for w = 50 nm and 570 ps w = 75 nm. Therefore, gate performance increase is a consequence of both shorter travelling distance and increased group velocity. Thus, the gate delay can be further reduced by scaling down w, but also by making use of other waveguide materials.

We note that if only one MAJ3 output is required the structure can be simplified: i) physically, by removing one of its vertical waveguides (arms) or ii) logically, by not providing

FIG. 4. FO4 MAJ3 Gate.

an input signal to  $I_4$ . Moreover, the gate fanout capabilities can be extended beyond 2 by vertically lengthening its arms. For example, if the outputs in Figure 2 and 3 are shifted downward to the end of the arms and two outputs are placed upward (at the upper-end of the arms), four outputs can be accommodated and if properly designed the gate can provide a fanout of 4 as indicated in Figure 4. However, the detailed design of such a structure constitutes future work and is out of the scope of the current paper.

To get inside on the quality of the achieved fanout, i.e., the similarity between the two SWs obtained at the gate outputs, we make use of Magnetization Spinning Angle (MSA) as metric. The input and output spinning angles are calculated as:

$$MSA = \arctan\left(\frac{\sqrt{(\overline{m_x})^2 + (\overline{m_y})^2}}{M_s}\right),\tag{1}$$

where  $\overline{m_x}$  and  $\overline{m_y}$  are the x and y component of the magnetization, respectively.

Table II presents the contribution percentage of each input to the outputs  $O_1$  and  $O_2$  when each of them is separately activated, for the 50 nm waveguide width design. The outputs MSAs in the Table are normalized value with respect to the activated input MSA. Thus, when only  $I_1$  is activated  $O_1$  and  $O_2$  MSAs are normalized by  $I_1$  MSA. The same holds true for the other 3 situations presented in the Table. As it can be noticed,  $I_3$ ,  $I_2$ ,  $I_1$ , and  $I_4$  contributions to  $O_1$  and  $O_2$  are quite different. Due to symmetry,  $I_1$  equally contributes to both gate outputs  $O_1$  and  $O_2$  and the same hold true for  $I_2$ also. However, due to its proximity  $I_2$  has a larger contribution to the outputs than  $I_1$  and as such their strengths have to be properly balanced. Input  $I_3$  SW is the strongest contributor to  $O_1$  as it has a direct path to  $O_1$ , while spin waves from  $I_2$  and  $I_1$  are facing edges, and reflect back and forth. Moreover,  $I_3$ mostly affects  $O_1$  and to a lower extend  $O_2$ , while  $I_4$  effect is stronger on  $O_2$  and weaker on  $O_1$ . Thus, as the inputs on the vertical and horizontal waveguides differently contribute to the outputs,  $I_3$  and  $I_4$  SWs must be excited at lower energy than  $I_1$  and  $I_2$  SWs to enable the correct gate behavior.

Table III presents the normalised (with respect to  $I_1$ ) MSA of the outputs when all inputs are activated together for the

TABLE II. Input Contribution Percentage on the Outputs - Separately Activated Inputs.

| Inputs | $O_1/I \%$ | $O_2/I \%$ |

|--------|------------|------------|

| $I_1$  | 54 %       | 54 %       |

| $I_2$  | 57 %       | 57 %       |

| $I_3$  | 96 %       | 35 %       |

| $I_4$  | 35 %       | 96 %       |

TABLE III. Normalized Outputs ( $O_1$  and  $O_2$ ) by  $I_1$  - Simultaneously Activated Inputs.

| Inputs |       | Inputs          | $O_1/I_1 \%$ | $O_2/I_1 \%$ |

|--------|-------|-----------------|--------------|--------------|

| $I_1$  | $I_2$ | $I_3$ AND $I_4$ |              |              |

| 0      | 0     | 0               | 1            | 1            |

| 0      | 0     | 1               | 0.28         | 0.28         |

| 0      | 1     | 0               | 0.37         | 0.37         |

| 0      | 1     | 1               | 0.45         | 0.45         |

| 1      | 0     | 0               | 0.45         | 0.45         |

| 1      | 0     | 1               | 0.37         | 0.37         |

| 1      | 1     | 0               | 0.28         | 0.28         |

| 1      | 1     | 1               | 1            | 1            |

same w = 50 nm design. As it can be noticed from Table III, the normalized  $O_1$  and  $O_2$  MSA is the same in all cases, which means that the proposed MAJ3 gate can successfully achieve a fanout of 2. One can also observe in the Table that different input combinations are producing different normalized MSA values. When all gate inputs have the same value  $(I_1 = I_2 = I_3)$ , the output MSA is reaching the highest value because of the constructive interference. When inputs have different values, the destructive interference diminishes the spin wave energy, which results in lower MSA values. Moreover, when the horizontal inputs  $(I_1 \text{ and } I_2)$  are different, the position of the asserted input affects the MSA output. For example, when  $(I_3 = 1, I_2 = 0, \text{ and } I_1 = 1)$  or  $(I_3 = 0, I_2 = 1 \text{ and } I_2 = 1)$  $I_1 = 0$ ) the the normalized output MSA is higher than when  $(I_3 = 1, I_2 = 1, \text{ and } I_1 = 0) \text{ or } (I_3 = 0, I_2 = 0, \text{ and } I_1 = 1) \text{ be-}$ cause  $I_2$  is located further than  $I_1$  and  $I_3$  from the interference location. As a result, when  $I_1$  and  $I_3$  have the same state, they interfere constructively and then destructively with  $I_2$ , which results in a larger magnetization angle.

An accurate evaluation of the proposed structure is not possible at this stage of development, especially for the energy and delay. That is mostly due to the missing excitation and detection cells figure of merit data. Thus, as the transducers are the dominant source for energy and delay, we chose to use the area as a metric to position our proposal versus existing state of the art.

In order to make a fair comparison with<sup>12</sup>, we scaled down the MAJ3 design for  $w = \lambda = 48$  nm and validate it by means of OOMMF simulations. In addition, the outputs are captured directly at the last interference point. The proposed scaled FO2 MAJ3 gate requires a real estate of 0.0576  $\mu m^2$ . As the gate in<sup>12</sup> cannot provide fanout, we have to consider two such gates working in parallel on the same input set to evaluate both gates in similar utilization conditions, which results in a required area of 0.0691  $\mu m^2$ , i.e., our proposal provides a 16 % area reduction at the gate level. We note, however, that at

his is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/1.5134690

the circuit level the area savings are significantly more substantial, as in order to deal with a fanout of 2 gate output Othe approach in<sup>12</sup> requires the replications of all the gates on O's cone of influence starting from the circuit primary inputs, and that for efficient logic synthesis of practical circuits gates with > 1 fanout are frequently necessary.

In order to compare with CMOS, we evaluated a 3-input Majority gate implemented in 15 nm technology with two NAND gates and one OR-AND-Invert (OAI) gate, at  $V_{dd} = 0.8$  V, 25°C, and an output load capacitance of 20 fF. Our evaluation indicate that the 15 nm CMOS MAJ3 area is 0.688  $\mu m^2$ , thus a 12x larger area than the proposed SW MAJ3 gate.

In summary, we presented a novel fanout of 2 area efficient 3-input spin wave Majority gate (MAJ3). We validated two instances of our proposal by means of OOMMF simulations and evaluated the fanout quality by making use of the Magnetization Spinning Angle (MSA) as metric. We calculated the normalized MSA values for the gate outputs and obtained negligible mismatch between them under all possible input combinations, i.e., a high quality fanout. We compared our proposal with MAJ3 SW, under the same material assumptions and utilization conditions, and 15nm CMOS state of the art counterparts in terms of area and demonstrated a 16 % and 12x less area, respectively. As a closing remark, we note that achieving > 1 fanout is an enabling factor for the realization of SW circuits, as it eliminates the otherwise required circuit replication associated with fanout nodes intrinsic to SW circuits produced by means of logic synthesis. Thus, the implications of our proposal at the circuit level are a lot more substantial than at the gate level, both in terms of area and energy consumption.

## ACKNOWLEDGMENTS

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/1.5134690

his is the author's peer reviewed, accepted manuscript. However,

"This work has received funding from the European Union's Horizon 2020 research and innovation program within the FET-OPEN project CHIRON under the grant agreement No. 801055."

## **Data Availability Statement**

The data that supports the findings of this study are available within the article.

- <sup>1</sup>N. D. Shah, E. W. Steyerberg, and D. M. Kent, "Big data and predictive analytics: Recalibrating expectations," JAMA (2018).

- <sup>2</sup>D. Mamaluy and X. Gao, "The fundamental downscaling limit of field effect transistors," Applied Physics Letters **106**, 193503 (2015).

- <sup>3</sup>N. Z. Haron and S. Hamdioui, "Why is cmos scaling coming to an end?" in *Design and Test Workshop, 2008. IDT 2008. 3rd International* (IEEE, 2008) pp. 98–103.

- <sup>4</sup>K. Bernstein, R. K. Cavin, W. Porod, A. Seabaugh, and J. Welser, "Device and architecture outlook for beyond cmos switches," Proceedings of the IEEE 98, 2169–2184 (2010).

- <sup>5</sup>D. E. Nikonov and I. A. Young, "Overview of beyond-cmos devices and a uniform methodology for their benchmarking," Proceedings of the IEEE **101**, 2498–2533 (2013).

- <sup>6</sup>Y. K. Fetisov and C. E. Patton, "Microwave bistability in a magnetostatic wave interferometer with external feedback," IEEE Transactions on Magnetics **35**, 1024–1036 (1999).

- <sup>7</sup>A. B. Ustinov and B. A. Kalinikos, "Nonlinear microwave spin wave interferometer," Technical Physics Letters 27, 403–405 (2001).

- <sup>8</sup>S. V. Vasiliev, V. V. Kruglyak, M. L. Sokolovskii, and A. N. Kuchko, "Spin wave interferometer employing a local nonuniformity of the effective magnetic field," Journal of Applied Physics **101**, 113919 (2007), https://doi.org/10.1063/1.2740339.

- <sup>9</sup>O. Rousseau, B. Rana, R. Anami, M. Yamada, K. Miura, S. Ogawa, and Y. Otani, "Realization of a micrometre-scale spin-wave interferometer," in *Scientific reports* (2015).

- <sup>10</sup>N. Kanazawa, T. Goto, K. Sekiguchi, A. B. Granovsky, C. A. Ross, H. Takagi, Y. Nakamura, and M. Inoue, "Demonstration of a robust magnonic spin wave interferometer," in *Scientific reports* (2016).

- <sup>11</sup>A. Khitun and K. L. Wang, "Non-volatile magnonic logic circuits engineering," Journal of Applied Physics **110**, 034306 (2011), https://doi.org/10.1063/1.3609062.

- <sup>12</sup>O. Zografos, B. Sorée, A. Vaysset, S. Cosemans, L. Amarù, P. Gaillardon, G. D. Micheli, R. Lauwereins, S. Sayan, P. Raghavan, I. P. Radu, and A. Thean, "Design and benchmarking of hybrid cmos-spin wave device circuits compared to 10nm cmos," in 2015 IEEE 15th International Conference on Nanotechnology (IEEE-NANO) (2015) pp. 686–689.

<sup>13</sup>S. Klingler, P. Pirro, T. Brächer, B. Leven, B. Hillebrands, and

- <sup>13</sup>S. Klingler, P. Pirro, T. Brächer, B. Leven, B. Hillebrands, and A. V. Chumak, "Design of a spin-wave majority gate employing mode selection," Applied Physics Letters **105**, 152410 (2014), https://doi.org/10.1063/1.4898042.

- <sup>14</sup>S. Klingler, P. Pirro, T. Brächer, B. Leven, B. Hillebrands, and A. V. Chumak, "Spin-wave logic devices based on isotropic forward volume magnetostatic waves," Applied Physics Letters **106**, 212406 (2015).

- <sup>15</sup>O. Zografos, S. Dutta, M. Manfrini, A. Vaysset, B. Sorée, A. Naeemi, P. Raghavan, R. Lauwereins, and I. P. Radu, "Non-volatile spin wave majority gate at the nanoscale," AIP Advances 7, 056020 (2017), https://doi.org/10.1063/1.4975693.

- <sup>16</sup>O. Zografos, L. Amarù, P. Gaillardon, P. Raghavan, and G. D. Micheli, "Majority logic synthesis for spin wave technology," in 2014 17th Euromicro Conference on Digital System Design (2014) pp. 691–694.

- <sup>17</sup>F. Ciubotaru, G. Talmelli, T. Devolder, O. Zografos, M. Heyns, C. Adelmann, and I. P. Radu, "First experimental demonstration of a scalable linear majority gate based on spin waves," in 2018 IEEE International Electron Devices Meeting (IEDM) (2018) pp. 36.1.1–36.1.4.

- <sup>18</sup>N. Kanazawa, T. Goto, K. Sekiguchi, A. B. Granovsky, C. A. Ross, H. Takagi, Y. Nakamura, H. Uchida, and M. Inoue, "The role of snell's law for a magnonic majority gate," in *Scientific Reports* (2017).

- <sup>19</sup>M. Balynskiy, H. Chiang, D. Gutierrez, A. Kozhevnikov, Y. Filimonov, and A. Khitun, "Reversible magnetic logic gates based on spin wave interference," Journal of Applied Physics **123**, 144501 (2018), https://doi.org/10.1063/1.5011772.

- <sup>20</sup>C. J. Tock and J. F. Gregg, "Phase modulation and amplitude modulation interconversion for magnonic circuits," Phys. Rev. Applied **11**, 044065 (2019).

- <sup>21</sup>A. B. Ustinov, E. Lähderanta, M. Inoue, and B. A. Kalinikos, "Nonlinear spin-wave logic gates," IEEE Magnetics Letters 10, 1–4 (2019).

- <sup>22</sup>F. Heussner, A. A. Serga, T. Brächer, B. Hillebrands, and P. Pirro, "A switchable spin-wave signal splitter for magnonic networks," Applied Physics Letters **111**, 122401 (2017), https://doi.org/10.1063/1.4987007.

- <sup>23</sup> A. V. Sadovnikov, C. S. Davies, S. V. Grishin, V. V. Kruglyak, D. V. Romanenko, Y. P. Sharaevskii, and S. A. Nikitov, "Magnonic beam splitter: The building block of parallel magnonic circuitry," Applied Physics Letters **106**, 192406 (2015), https://doi.org/10.1063/1.4921206.

- <sup>24</sup>B. Rana and Y. Otani, "Voltage-controlled reconfigurable spin-wave nanochannels and logic devices," Phys. Rev. Applied 9, 014033 (2018).

- <sup>25</sup>A. B. Ustinov and B. A. Kalinikos, "Power-dependent switching of microwave signals in a ferrite-film nonlinear directional coupler," Applied Physics Letters 89, 172511 (2006), https://doi.org/10.1063/1.2362576.

- <sup>26</sup>A. A. Serga, A. V. Chumak, and B. Hillebrands, "Yig magnonics," Journal of Physics D: Applied Physics **43**, 264002 (2010).

- <sup>27</sup>F. Ciubotaru, T. Devolder, M. Manfrini, C. Adelmann, and I. P. Radu, "All electrical propagating spin wave spectroscopy with broadband wavevector capability," Applied Physics Letters **109**, 012403 (2016), https://doi.org/10.1063/1.4955030.

- <sup>28</sup>A. V. Chumak, A. A. Serga, and B. Hillebrands, "Magnonic crystals for data processing," Journal of Physics D: Applied Physics **50**, 244001 (2017).

i his is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/1.5134690

- <sup>29</sup>S. Cherepov, P. Khalili Amiri, J. G. Alzate, K. Wong, M. Lewis, P. Upadhyaya, J. Nath, M. Bao, A. Bur, T. Wu, G. P. Carman, A. Khitun, and K. L. Wang, "Electric-field-induced spin wave generation using multiferroic magnetoelectric cells," Applied Physics Letters **104**, 082403 (2014), https://doi.org/10.1063/1.4865916.

- <sup>30</sup>C. Chen, A. Barra, A. Mal, G. Carman, and A. Sepulveda, "Voltage induced mechanical/spin wave propagation over long distances," Applied Physics Letters **110**, 072401 (2017), https://doi.org/10.1063/1.4975828.

- <sup>31</sup>R. Duflou, F. Ciubotaru, A. Vaysset, M. Heyns, B. Sorée, I. P. Radu, and C. Adelmann, "Micromagnetic simulations of magnetoelastic spin wave excitation in scaled magnetic waveguides," Applied Physics Letters **111**, 192411 (2017), https://doi.org/10.1063/1.5001077.

- <sup>32</sup>G. Talmelli, F. Ciubotaru, K. Garello, X. Sun, M. Heyns, I. P. Radu, C. Adelmann, and T. Devolder, "Spin-wave emission by spin-orbit-torque antennas," Phys. Rev. Applied **10**, 044060 (2018).

- <sup>33</sup>P. Gambardella and I. M. Miron, "Current-induced spin orbit torques," Philosophical Transactions of the Royal Society A: Mathematical, Physical and Engineering Sciences **369**, 3175–3197 (2011), https://royalsocietypublishing.org/doi/pdf/10.1098/rsta.2010.0336.

- <sup>34</sup>T. Devolder, J.-V. Kim, F. Garcia-Sanchez, J. Swerts, W. Kim, S. Couet, G. Kar, and A. Furnemont, "Time-resolved spin-torque switching in mgobased perpendicularly magnetized tunnel junctions," Phys. Rev. B **93**, 024420 (2016).

(vii)

(viii)

(viii)