# **Best Practice Guide**- Knights Landing

Vali Codreanu, SURFsara

Jorge Rodríguez, BSC

Ole Widar Saastad (Editor), University of Oslo

31-01-2017

# **Table of Contents**

|      | ntroduction                                                        |    |

|------|--------------------------------------------------------------------|----|

| 2. S | system Architecture / Configuration                                | 5  |

|      | 2.1. Processor Architecture / MCM Architecture                     |    |

|      | 2.1.1. Instruction Set Architecture                                | 7  |

|      | 2.2. Memory Architecture                                           |    |

|      | 2.2.1. Flat mode                                                   |    |

|      | 2.2.2. Cache mode                                                  |    |

|      | 2.2.3. Hybrid mode                                                 |    |

|      | 2.2.4. Optimal Settings                                            |    |

|      | 2.2.5. Example: Programming with the memkind library               |    |

|      | 2.3. Clustering modes                                              |    |

|      | 2.3.1. All to all mode                                             |    |

|      | 2.3.2. Quadrant mode                                               |    |

|      | 2.3.3. Sub NUMA mode                                               |    |

|      | 2.3.4. Performance using the different modes                       |    |

|      |                                                                    |    |

|      | 2.3.5. Example: Programming with sub-NUMA clusters                 |    |

|      | 2.3.6. BIOS settings for clustering, memory etc                    |    |

|      | 2.4. (Node) Interconnect                                           |    |

| 2 5  | 2.5. I/O Subsystem Architecture                                    |    |

| 3. P | Programming Environment / Basic Porting                            |    |

|      | 3.1. Default System settings                                       |    |

|      | 3.2. Available Compilers                                           |    |

|      | 3.2.1. Compiler Flags                                              |    |

|      | 3.3. Available (Vendor Optimized) Numerical Libraries              |    |

|      | 3.3.1. Math Kernel Library, MKL                                    |    |

|      | 3.3.2. Intel Performance Primitives, IPP                           |    |

|      | 3.3.3. Math library, libimf                                        |    |

|      | 3.3.4. Short vector math library, libsvml                          |    |

|      | 3.4. Available MPI Implementations                                 | 23 |

|      | 3.5. OpenMP                                                        | 24 |

|      | 3.5.1. Compiler Flags                                              | 24 |

| 4. E | Benchmark performance                                              | 24 |

|      | 4.1. STREAM benchmark                                              | 25 |

|      | 4.2. NAS kernel benchmark, NPB                                     | 26 |

|      | 4.2.1. Scaling and Speedup test                                    |    |

|      | 4.2.2. Performance                                                 |    |

|      | 4.3. HYDRO benchmark                                               |    |

|      | 4.3.1. Scaling and Speedup test                                    |    |

|      | 4.3.2. Performance                                                 |    |

| 5 A  | Application Performance                                            |    |

| 5. 1 | 5.1. ALYA                                                          |    |

|      | 5.1.1. Building and compiling                                      |    |

|      | 5.1.2. Scaling and speedup                                         |    |

|      | 5.1.3. Performance                                                 |    |

|      | 5.2. GROMACS                                                       |    |

|      |                                                                    |    |

|      | 5.2.1. Building and compiling                                      |    |

|      | 5.2.2. Scaling and speedup                                         |    |

|      | 5.2.3. Performance                                                 |    |

|      | 5.3. Bifrost (Stellar atmosphere simulation code)                  |    |

|      | 5.3.1. Building and compiling                                      |    |

|      | 5.3.2. Vectorization and scaling                                   |    |

|      | 5.3.3. Performance                                                 |    |

|      | 5.4. Dalton and LS-Dalton (molecular electronic structure program) |    |

|      | 5.4.1. Building and compiling                                      |    |

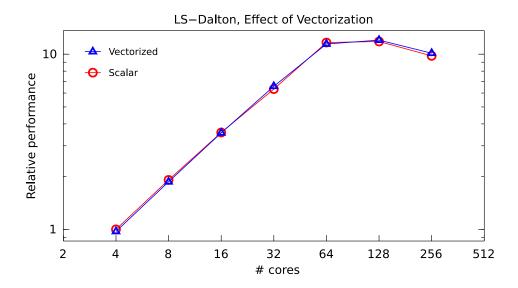

|      | 5.4.2. Effect of vectorization                                     | 39 |

# Best Practice Guide - Knights Landing

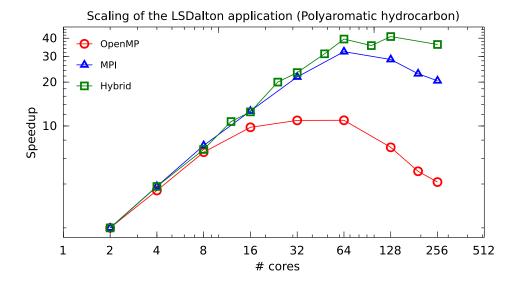

| 5.4.3. Scaling and speedup                                  |      |

|-------------------------------------------------------------|------|

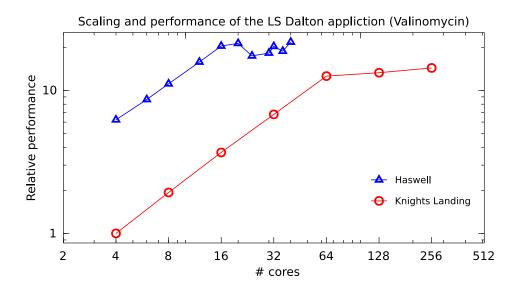

| 5.4.4. Performance                                          |      |

| 6. Performance Analysis                                     |      |

| 6.1. Performance Monitoring in the Knights Landing Tile     |      |

| 6.2. Available Performance Analysis Tools                   |      |

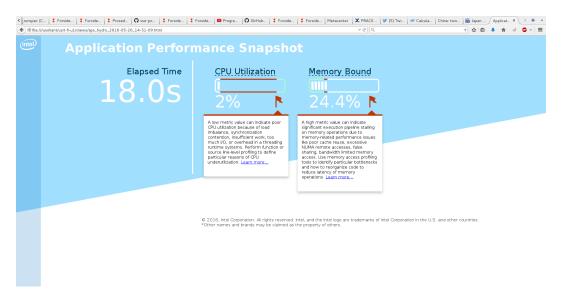

| 6.2.1. Intel Application Performance Snapshot               | 43   |

| 6.2.2. Allienea Performance Reports                         | 44   |

| 6.2.3. Intel Software Development Emulator                  | 46   |

| 6.3. Hints for Interpreting Results                         | 47   |

| 7. Tuning                                                   | 47   |

| 7.1. Guidelines for tuning                                  | 47   |

| 7.1.1. Top down                                             |      |

| 7.1.2. Bottom up                                            |      |

| 7.2. Intel tuning tools                                     |      |

| 7.2.1. Intel compiler                                       |      |

| 7.2.2. Intel MPI library                                    |      |

| 7.2.3. Intel XE-Advisor                                     |      |

| 7.2.4. Intel XE-Inspector                                   |      |

| 7.2.5. Intel VTune Amplifier                                |      |

| 7.2.6. Intel Trace Analyzer                                 |      |

| ·                                                           |      |

| 7.3. Single Core Optimization                               |      |

| 7.3.1. Vectorization                                        |      |

| 7.3.2. Compiler auto vectorization                          |      |

| 7.3.3. Interprocedural Optimization                         |      |

| 7.3.4. Intel Advisor tool                                   |      |

| 7.3.5. Intel VTune Amplifier tool                           |      |

| 7.4. Threaded performance tuning                            |      |

| 7.4.1. Shared memory / single node                          |      |

| 7.4.2. Core count and scaling                               |      |

| 7.4.3. False sharing                                        |      |

| 7.4.4. Intel XE-Inspector tool                              |      |

| 7.5. Advanced OpenMP Usage                                  |      |

| 7.5.1. SIMD vectorization                                   |      |

| 7.5.2. OpenMP Thread parallel                               |      |

| 7.5.3. Tuning / Environment Variables                       |      |

| 7.5.4. Usage of numactl                                     | 65   |

| 7.6. Advanced MPI Usage                                     |      |

| 7.6.1. Effect of multiple ranks per core                    | . 67 |

| 7.6.2. Intel Advisor tool                                   | 68   |

| 7.6.3. Intel VTune Amplifier tool                           | 68   |

| 7.6.4. Intel Trace Analyser tool                            | 69   |

| 7.6.5. Auto Tuning tool                                     | 72   |

| 7.6.6. Tuning / Environment Variables                       |      |

| 7.6.7. Mapping Tasks on Node Topology                       |      |

| 7.7. Hybrid Programming                                     |      |

| 7.7.1. Optimal Tasks / Threads Strategy                     |      |

| 7.7.2. Thread placement                                     |      |

| 7.7.3. Interoperability with MPI/OpenMP                     |      |

| 7.7.4. Performance issues, suggested settings               |      |

| 7.8. Memory Optimisation                                    |      |

| 7.8.1. Memory Affinity (MPI/OpenMP/Hybrid)                  |      |

| 7.8.2. Memory Allocation (malloc) Tuning                    |      |

| 7.8.2. Memory Anocation (manoc) running                     |      |

| 7.8.3. Using Huge Pages 7.9. Possible BIOS Parameter Tuning |      |

| · · · · · · · · · · · · · · · · · · ·                       |      |

| 7.9.1. Snoop filter settings                                |      |

| 99 9                                                        |      |

| 8.1. Available Debuggers                                    |      |

| 8.1.1. GNU based debuggers                                  | 81   |

# Best Practice Guide - Knights Landing

| 8.1.2. TotalView debugger | 82 |

|---------------------------|----|

| 8.2. Compiler Flags       |    |

| Further documentation     | 83 |

# 1. Introduction

This best practice guide provides information about Intel's MIC architecture and programming models for the Intel Xeon Phi co-processor in order to enable programmers to achieve good performance of their applications. The guide covers a wide range of topics from the description of the hardware of the Intel Xeon Phi co-processor through information about the basic programming models as well as information about porting programs up to tools and strategies how to analyze and improve the performance of applications.

The Knights Landing (KNL) processor differ from the usual Intel processor due to its very high core count and the hardware threading architecture. It represent an approach where a large number of simples cores are employed in large number as opposed to larger more sophisticated cores in smaller number. The idea is that a higher fraction of the transistors could be used for arithmetric operations. Over the decades the flops per transistor have declined. The KNL represent the second generation of this approach, the Knights Corner (KNC) being the first. There is also a best practice guide for the KNC [http://www.prace-ri.eu/best-practice-guide-intel-xeon-phi-html].

Figure 1. Knights Landing processor.

The KNL processor is a x86-64 compatible processor architecture and hence most of the content of the Best Practice Guide for the x86 architecture is still valid. It's a good idea to have the x86 guide handy as this guide cover the more KNL specific topics. The x86 BPG can be found at the PRACE web site [http://www.prace-ri.eu/Best-Practice-Guide-Generic-x86-HTML].

# 2. System Architecture / Configuration

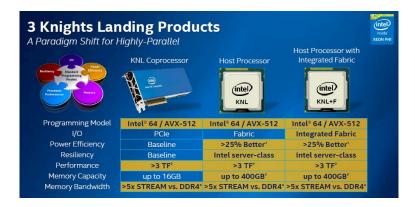

From a system point-of-view, the KNL platform comes in three configurations. The three options are outlined in Figure 2.

- The first, similar to the previous incarnation of the Xeon Phi architecture (Knights Corner), is a co-processor card. This card has access to 16GB of high-bandwidth memory (HBM) and PCIe access to the host memory.

- The second option is a standalone host processor. This option has the main advantage that it can boot and run a

full-fledged OS. Another advantage that it has both access to the HBM and to the much-larger system DDR4,

without being slowed by PCIe access. For communication with other KNL nodes, the system I/O fabric is used.

- The third option, and perhaps most appropriate for HPC is the standalone host processor that also has the Intel OmniPath communication fabric integrated on the package. It provides a 100Gb/s link across the KNL computing nodes, with arguably lower latencies than InfiniBand EDR.

Figure 2. Knights Landing variants.

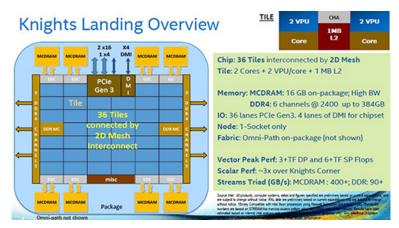

Thus, at a high level, the KNL system is composed of:

- The computing subsystem: composed of up to 36 compute tiles, connected in a 2D mesh fashion, each tile being composed of 2 cores.

- The memory subsystem: composed of 16GB of high-speed stacked memory accessed by 8 high-speed memory controllers, as well as up to 384GB of DDR4 accessed by 2 3-channel memory controllers.

- The I/O subsystem: composed of 36 PCIe lanes and an optional Omnipath controller.

One of the big paradigm shifts between the Knights Corner and Knights Landing capabilities is that the latter allows running a full-fledged operating system. This is because the KNL cores are fully Intel Xeon ISA-compatible through AVX2.

Another important detail is that the socketed KNL systems are single-socket systems. There is no QPI link connecting more KNL dies together. Hence, the performance per node is limited to the performance of a single KNL chip. In order to offer scalable performance, the communication fabric has to be very efficiently used, as large KNL installations will feature a very large number of nodes.

# 2.1. Processor Architecture / MCM Architecture

The Knights Landing processor architecture is composed of up to 72 Silvermont-based cores running at ~1.3-1.4 GHz. The cores are organized into tiles, each tile comprising two cores, and each core having two AVX-512 vector processing units. Each tile has 1MB of L2 cache, shared by the two cores, for a total of 36MB of L2 cache across the chip. The tiles are connected in a 2D mesh topology. The cores are 14nm versions of Silvermont, rather than 22nm P54C used in Knights Corner, with claims by Intel that the out-of-order performance is vastly improved, the KNL cores delivering up to 3 times the single-core performance of the Knights Corner cores. The architecture is depicted in Figure 3.

Each of the 72 cores is out-of-order and is multithreaded, supporting 4 SMT threads, similar to the Knights Corner. However, in order to reach peak performance for KNC, one needed to use at least 2 threads/core. In the case of KNL, it is claimed that peak performance can be achieved by using 1 thread/core for certain application. Another advantage of the KNL cores is that they are ISA-compatible with the regular Xeon cores, and can thus run any Xeon application without recompilation.

Figure 3. Knights Landing architecture.

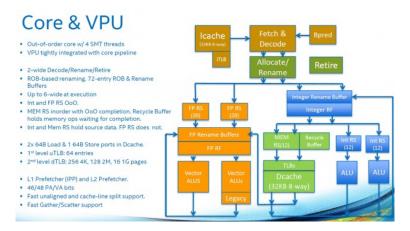

Going back to the core architecture, each KNL core features:

- 32KB Instruction and Data caches, 64 bytes cache line length.

- 2 AVX-512 units, each supporting up to 8DP/16SP operations per cycles. The units are tightly integrated with the core pipeline.

- L1/L2 prefetchers.

- Fast unaligned and cache-line split support. Fast Gather/Scatter support.

- Dynamic resource sharing between active threads.

- 4 SMT threads (HyperThreading).

Besides the two cores and the 1MB L2 cache, each tile includes a Cache/Home Agent (CHA) that sits on the 2D mesh interconnect and helps keep the 1 MB L2 caches from all tiles coherent.

Figure 4. Knights Landing core.

The KNL core microarchitecture has changed tremendously from the KNC one. The Silvermont-based core is modified to better accommodate HPC applications, and it offers 3x the single-thread performance of a KNC core. As can be seen in Figure 4, in order to achieve this Intel uses an out-of-order execution engine, and has increased the buffering structures that help with Instruction Level Parallelism. Each KNL core features 2-wide decode/rename/retire stages, 72 inflight μops/core out-of-order buffers, 72-entry ROB and rename buffers, up to 6-wide at execution. The branch prediction logic was also improved, less cycles being wasted due to branch misprediction.

#### 2.1.1. Instruction Set Architecture

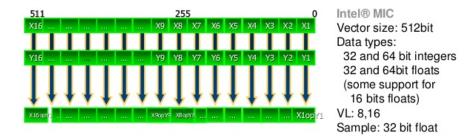

Being backward compatible with Intel Xeon products, KNL supports all previous ISA extensions: SSE, AVX, AVX2. On top of them, KNL adds support for the AVX-512 ISA, that will also be supported by upcoming CPU

architectures such as Intel Skylake. In this guide, we will cover more extensively the additions from AVX2 to AVX-512, and we advise the reader to check out the Haswell and generic x86 guides for descriptions of the previous ISA extensions.

Thus, the 512-bit vector functionality from KNL is comprised of:

- AVX512F: 512b vector extensions with mask support.

- AVX512PFI: Introduces new prefetch instructions

- AVX512ERI: Introduces new exponential and reciprocal instructions

- AVX512CDI: Introduces conflict detection instructions that help with vectorization

Intel AVX-512 Foundation instruction set is a natural extension to AVX and AVX2. It introduces the following architectural enhancements:

- Support for 512-bit wide vectors and SIMD register set. 512-bit register state is managed by the operating system using XSAVE/XRSTOR instructions previously introduced.

- Support for 16 new, 512-bit SIMD registers (for a total of 32 SIMD registers, ZMM0 through ZMM31) in 64-bit mode. The extra 16 registers state is managed by the operating system using XSAVE/XRSTOR/XSAVEOPT.

- Support for 8 new opmask registers (k0 through k7) used for conditional execution and efficient merging of

destination operands. These opmask registers are also managed by the operating system using the XSAVE/

XRSTOR/XSAVEOPT instructions.

- A new encoding prefix (referred to as EVEX) to support additional vector length encoding up to 512 bits. The

EVEX prefix builds upon the foundations of VEX prefix, to provide compact, efficient encoding for functionality available to VEX encoding plus the following enhanced vector capabilities:

- (1) opmasks

- (2) embedded broadcasts

- (3) instruction prefix-embedded rounding control

- (4) compressed address displacements.

#### 2.1.1.1. Masking

Most AVX-512 instructions may indicate one of 8 opmask registers (k0–k7). The k0 register is a hardcoded constant used to indicate unmasked operations. These registers are mostly used to control which values are written to the destination. A flag controls the opmask behavior, which can either be "zero" or "merge". "Zero" zeroes out everything not selected by the mask, while "merge" leaves everything not selected unmodified. The merge behavior is identical to the blend instructions.

#### 2.1.1.2. Embedded broadcasts

One addition to the EVEX encoding is a bit-field that encodes data broadcast for some instructions that load data from memory and perform some computational or data movement operation. An element from memory can be broadcasted (repeated) across all the elements of the effective source operand (up to 16 times for 32-bit data element, up to 8 times for 64-bit data element using 512-bit vector registers). This functionality reduces the overhead of reusing the same scalar operand for all the operations in a vector instruction. The broadcasting functionality is only enabled for elements of either 32 bits or 64 bits in size. Byte and word instructions do not support embedded broadcast.

#### 2.1.1.3. Embedded rounding control

In previous SIMD extensions rounding control was usually specified in MXCSR, with some instructions providing per-instruction rounding override via encoding fields within the imm8 operand. AVX-512 offers a more flexible

encoding attribute to override MXCSR-based rounding control for floating-pointing instruction with rounding semantic. This rounding attribute embedded in the EVEX prefix is called Static (per instruction) Rounding Mode or Rounding Mode override. This attribute allows programmers to statically apply a specific arithmetic-rounding mode irrespective of the value of RM bits in MXCSR. It is available only to register-to-register flavors of EVEX-encoded floating-point instructions with rounding semantic. Four rounding modes are supported by direct encoding within the EVEX prefix overriding MXCSR settings. This embedded rounding is implemented both because saving, modifying and restoring MXCSR is usually slow and cumbersome, and because being able to avoid suppressions and set the rounding-mode on a per instruction basis simplifies development of high performance math codes.

#### 2.1.1.4. Other AVX-512 extensions in KNL

Besides the foundation instructions, KNL features three additional extensions:

- AVX512PFI: Introduces instructions to:

- (1) Prefetch a cache line into the L2 cache with intent to write (RFO ring request). This reduces ring traffic in core-to-core data communication.

- (2) Prefetch vector of D/Qword indexes into the L1/L2 cache.

- (3) Prefetch vector of D/Qword indexes into the L1/L2 cache with intent to write. Reduce overhead of software prefetching: dedicate side engine to prefetch sparse structures while devoting the main CPU to pure raw flop.

- AVX512ERI: Introduces instructions to compute approximation of

- (1) exponential functions

- (2) reciprocal

- (3) reciprocal square root.

- AVX512CDI: Introduces conflict detection instructions that help with vectorization (a CDI example can be

found on page 28: http://www.alcf.anl.gov/files/Sewall\_ANL-ESPKnightsLanding.pdf). The VPCONFLICT

instruction detects elements with previous conflicts in a vector of indexes. It allows to generate a mask with

a subset of elements that are guaranteed to be conflict free, and afterwards the computation loop can be reexecuted with the remaining elements until all the indexes have been operated upon.

# 2.2. Memory Architecture

The memory subsystem: composed of 16GB of high-speed stacked memory accessed by 8 high-speed memory controllers, as well as up to 384GB of DDR4 accessed by 2 3-channel memory controllers. While raw floating point and integer performance is an important aspect of the Knights Landing design, the achievable memory bandwidth is perhaps of the same or even greater importance. It is expected that the KNL chip can get more than 400 GB/sec of bandwidth out of the 16 GB of MCDRAM and more than 90 GB/sec out of the regular DRAM attached to the chip running the STREAM Triad memory bandwidth benchmark.

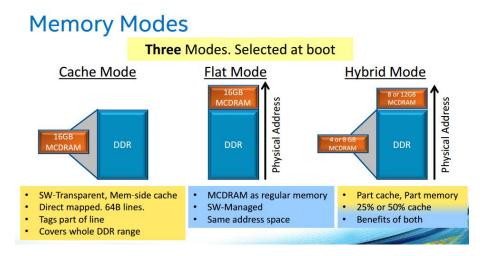

Figure 5. Different memory modes"

As can be seen in Figure 5, the KNL memory can work in three different modes. These are determined by the BIOS at POST time and thus require a reboot to switch between them.

#### 2.2.1. Flat mode

The first mode is called "Flat Mode". This mode allows the MCDRAM to have a physical addressable space. This in turn allows the programmer to migrate data structures in and out of the MCDRAM. This can be useful to keep large structures in DDR4 and smaller structures in MCDRAM. This mode offers the highest bandwidth and lowest latency. Another advantage is that the 16GB of MCDRAM are seen as addressable, hence increasing the total addressable memory in a KNL system. The downside of the flat mode is that software modifications are required in order to use both the DDR and the MCDRAM in the same application. The application has to maintain and keep track of what data goes where, increasing software design and maintenance costs. One consequence of the "Flat mode" is that the KNL system is seen as a two-node NUMA domain, similar to a dual-socket Xeon system. The memory is allocated by default in the DDR memory in order to keep non-critical data out of the MCDRAM. Applications that explicitly want to allocate data in MCDRAM have two ways to achieve this: (1) the "fast malloc" functions from the Memkind library: http://memkind.github.io/memkind/, and (2) the "FASTMEM" compiler annotation for Intel Fortran.

#### 2.2.2. Cache mode

The second mode is called "Cache Mode". When using this mode, the application code can remain unchanged. The OS will organize the data to use the MCDRAM similar to an L3 cache, caching data from the DDR4 level of memory. The obvious benefit is increased bandwidth, as after careful application design most memory request will hit in this huge 16GB L3 cache. The downside here is when the MCDRAM experiences cache misses, the missed requests have to be communicated back into the die and then another request is issued out into DDR for the relevant memory, leading to increased latency. This means that an MCDRAM cache miss is more expensive than a simple read out to DDR. Another downside of this mode is that all memory needs to be transferred, from DDR, to MCDRAM, and finally to the L2 cache, see Figure 6 with access for large vector sizes. Serving as a cache,the 16GB MCDRAM are not addressable, leading to less system-addressable memory.

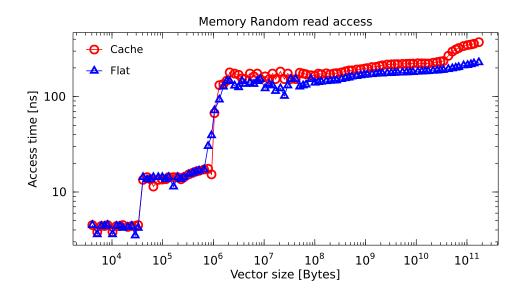

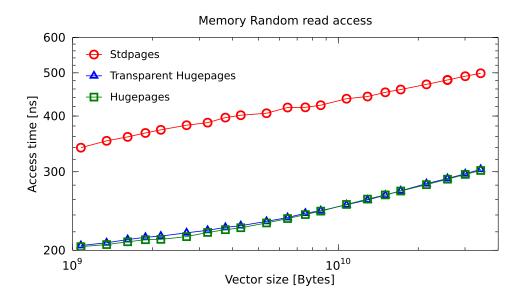

The figure below show the random access time when reading some random located data from memory using two different HBM layouts. As exptected the access time is lower in the Flat mode case as there is no cache memory management to pass through. The cache sizes are clearly visible. The jump at 16 GiB where the size of the High Bandwidth memory is exhausted is rather small, implying that the latency of the HBM is just slightly less of the DDR4 main memory. It is also evident that direct access to memory is faster than cached access for large data vectors. We see that for allocated vectors in excess of 16 GiB the random access time to memory increases when HBM is used as last level cache.

Figure 6. Random read memory access

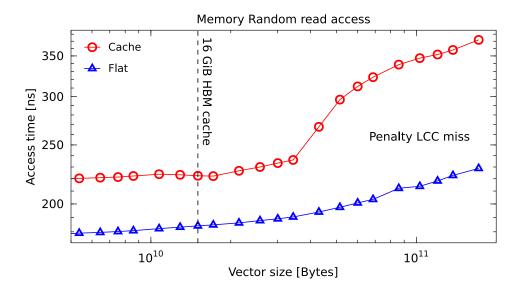

From the figure above we can observe that the cache coherency has a significant cost with respect to memory random access times. All memory transactions need to be handled by the cache coherency machinery and incure increased access times. In the figure below the random access times for larger vector sizes is shown. It is evident that the penalty for a cache miss in the Last Level Cache (the High Bandwidth Memory) can be quite significant when accessing memory randomly outside the cached part. In selected cases when the memory access pattern is random with unknown stride the Flat memory profile might yield better performance then using the HBM as a cache. The same is of course also true when the programmer is in full control over memory allocation. Some users are in full control using numactl and related tools other are unaware of such tools. Hence the system wide settings must be set to suite the users of the system. Administrators should be prepared to change the setting upon request.

Figure 7. Random read memory access for large vectors

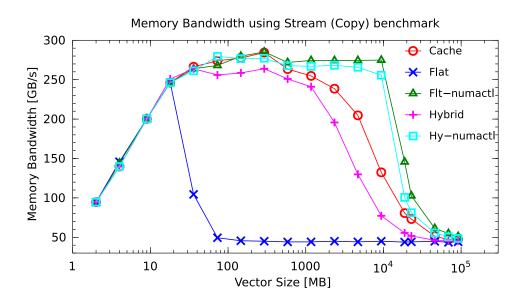

The figure below show the effect of High Bandwidth memory settings using the Stream memory bandwidth benchmark<sup>1</sup>. Here the benefit of the HBM is evident. Bypassing the cache coherency machinery seems to provide higher bandwidth for larger vector sizes, but require the users to be aware of the numa memory and allocate memory accordingly. It's also interesting to note that the DDR4 bandwidth is rather limited. This is a property of the chipset and motherboard. This system is a Ninja dvelopment system and one might expect HPC-compute nodes to have a better motherboard design.

Figure 8. Memory Bandwidth using the Stream benchamrk (Copy test)

<sup>&</sup>lt;sup>1</sup> Run without and with numactl, *numactl --preferred=1 ./stream.x* , where numanode 1 is HBM.

### 2.2.3. Hybrid mode

The third mode is called "Hybrid Mode". This mode allows the MCDRAM to be split in two, part of it to be used in "Cache Mode", and the other part in "Flat mode", using the High bandwidth Memkind library: http://memkind.github.io/memkind/. There is also an interposer library over Memkind available called AutoHBW which simplifies some of the commands at the expense of fine control. Under Memkind/AutoHBW, data structures aimed at MCDRAM have their own commands in order to be generated in MCDRAM.

### 2.2.4. Optimal Settings

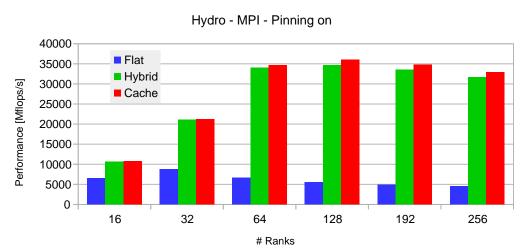

Of course, the best setting is application dependent. However, based on the characteristics of the application, there are three alternatives. If the whole application fits in the 16GB MCDRAM, it is advised to run the whole program in MCDRAM, by mapping it to the appropriate NUMA domain with numactl. This will give the highest possible bandwidth. If the application does not fit in MCDRAM, but the data can be easily split between critical/non-critical, the proper solution is to use the Memkind library and manually allocate the bandwidth-critical memory to MCDRAM. Finally, if the data cannot be easily split, or if it is desired that the codebase is left unmodified, the "Cache mode" should be employed. An example using the HYDRO benchmark in MPI implementation show the effect of High Bandwidth Memory settings.

Figure 9. Effect of High Bandwidth Memory settings

Effect of High Bandwidth Memory settings

Switching between these modes require change in the BIOS settings and a subsequent reboot. The command to alter the BIOS setting from command line is described in Section 2.3.6.

# 2.2.5. Example: Programming with the memkind library

An example with Fortran code can be found in Section 7.8.2.

# 2.3. Clustering modes

As noted before, in KNL each of its cores has an L1 cache, pairs of cores are organized into tiles with a slice of the L2 cache symmetrically shared between the two cores, and the L2 caches are connected to each other with a mesh. All caches are kept coherent by the mesh with the MESIF protocol. In the mesh, each vertical and horizontal link is a bidirectional ring. To maintain cache coherency, KNL has a distributed tag directory, organized as a set of per-tile tag directories (TDs), which identify the state and the location on the chip of any cache line. For any memory address, the hardware can identify with a hash function the TD responsible for that address. To manage

this complexity and set the optimal mode of operation for any given computational application, the programmer has access to cache clustering modes. The Knights Landing interconnecting mesh operates in one of three clustering modes: all-to-all, quadrant, and sub-NUMA. These modes are selected at boot-time, Intel providing no way to modify this setting without restarting the system.

#### 2.3.1. All to all mode

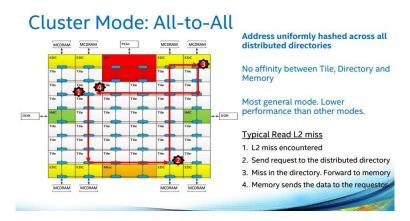

When using the all-to-all clustering mode, depicted in Figure 10 the memory addresses are uniformly distributed across all tag directories in the chip. This is the most general mode with the easiest programming model, but it will offer lower performance than the other modes.

Figure 10. All-to-all clustering mode.

#### 2.3.2. Quadrant mode

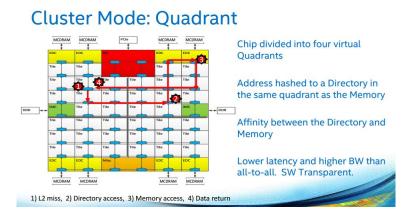

In quadrant/hemisphere modes, depicted in Figure 11, the Knights Landing chip is divided into two (hemispheres) or four parts (quadrants), and addresses are hashed to directories in the same hemisphere or quadrant, the quadrants being spatially local to the four groups of memory controllers. The operating system is not aware that this is going on underneath the covers, and it provides lower latency and higher bandwidth for the cores running in each hemisphere/quadrant. In the quadrant and hemisphere modes, the latency of L2 cache misses is reduced compared to the all-to-all mode.

Figure 11. Quadrant clustering mode.

#### 2.3.3. Sub NUMA mode

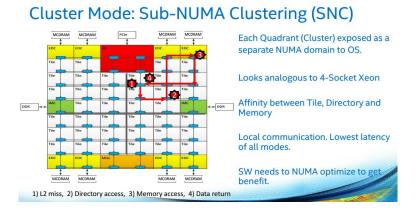

In the sub-NUMA cluster modes, depicted in Figure 12, the operating system exposes all four quadrants as virtual NUMA clusters. This makes a Knights Landing chip look like a four-socket Xeon server. This mode provides the lowest latency, provided that applications are NUMA-aware and hence thread and memory pinning are employed.

One important detail is that if cache traffic crosses the NUMA boundaries, using sub-NUMA clustering is less efficient than using the quadrant mode.

Figure 12. Sub-NUMA clustering mode.

# 2.3.4. Performance using the different modes

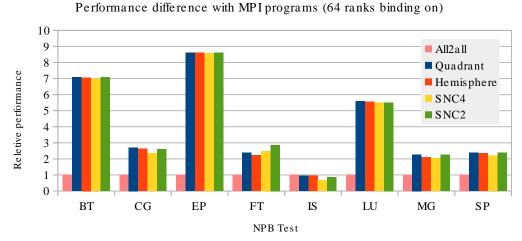

Performance varies with the different modes, the following figure give an example of the differences one might expect when running MPI applications. The suggested setting from Intel for daily work is Quadrant.

Figure 13. Example MPI Performance with different modes

Effect of different clustering modes

# 2.3.5. Example: Programming with sub-NUMA clusters

This is very much like programming a dual socket or four socket Intel system. Each of the sockets has its own local memory e.g. NUMA node. A four socket system will present four NUMA banks, when listed using the *numactl* - *H*. There a numerous example of NUMA programming available and programming a KNL set up with sub NUMA clusters are almost identical.

# 2.3.6. BIOS settings for clustering, memory etc

As with the memory modes switching betwene these core layout modes require BIOS setting changes and subsequent reboot. This can be done remote via a IPMI redirected serial console, a web based console or using a command line tool.

#### 2.3.6.1. CLI tools for BIOS settings

The tool *Syscfg* can be used to update the BIOS settings from the command line. It require the OpenIPMI tool to be installed as a prerequisite. The Syscfg tool can be found at Intel's web site [https://downloadcenter.intel.com/download/25439/Save-and-Restore-System-Configuration-utility-syscfg]. Once installed it provides a range of useful functions.

To save all the BIOS (and BMC) settings to a text file use the following command:

```

syscfg /s BIOSBMC.ini /b /f

```

From the saved file names of the relevant BIOS settings can be extracted and used as inputs to update the BIOS. After editing this config file the updated config file can be used to set the BIOS parameters.

```

syscfg /r BIOSBMC.ini /b /f

```

A power off is generally adviced. This is done in the normal way using IPMI.

To verify the settings the utility *hwloc* can be used. Just issue the command:

```

hwloc-dump-hwdata | egrep 'Cluster | Mode'

```

and the output should look something like:

```

Cluster mode: Quadrant Memory Mode: Cache

```

# 2.4. (Node) Interconnect

# 2.5. I/O Subsystem Architecture

From an I/O perspective, the three Knights Landing variants have different capabilities. The basic KNL chip has 36 PCIe 3.0 lanes available. When using the KNL co-processor, next to a Xeon host, one has the advantage that it can include more than one KNL chip inside a compute node. However, a major disadvantage when using the KNL cards is that only the 16GB MCDRAM are available as fast storage. The system memory needs to be accessed through PCIe, at a much lower rate. Perhaps the most interesting KNL variant from an I/O perspective is the KNL version that features two on-package integrated OmniPath fabric ports. This will drive data among KNL nodes at 100Gb/s.

# 3. Programming Environment / Basic Porting

# 3.1. Default System settings

The default settings are as suggested by Intel for every day general use, Chip layout set to "Quadrant" and High Bandwidth Memory to "Cache". This yield a system with a single memory image e.g. no NUMA and a rather large Last Level Cache LLC.

To change the settings please refer to sections in Section 2.3.6 and Section 7.9.

# 3.2. Available Compilers

A set of different compilers are available on the system. All support C, C++ and FORTRAN (90 and 2003) all with OpenMP threading support. For information about OpenMP support please refer to Section 3.5

#### **Compilers installed:**

• Intel compiler suite, icc, ifortran, icpc

• GNU compiler suite, gcc, gfortran, g++

# 3.2.1. Compiler Flags

We assume the users are familiar with the common flags for output, source code format, preprocessor etc. A nice overview of general compiler usage is found in the Best Practice Guide for x86 [http://www.prace-ri.eu/Best-Practice-Guide-Generic-x86-HTML]. The C compiler flags are also covered in this BPG.

Only the default flags will be listed and only for the FORTRAN compilers. Only Intel and GNU are covered as they make up the vast majority of usage. For C some flags may differ. For a discussion of the common flags for optimization please refer to Section 7.1

Only the default flags for the Intel FORTRAN compiler is given below. The C compiler will have a set of default compiler flags quite similar. As for the GNU gfortran and gcc the defaults are even more elaborate then Intel's and cannot be covered in detail here.

**Table 1. Default Intel FORTRAN compiler flags**

| Default flag                    | Description                                                                                                                                                                                                                                    |  |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -O2                             | Optimize for maximum speed                                                                                                                                                                                                                     |  |

| -f[no-]protect-parens           | enable/disable(DEFAULT) a reassociation optimization for REAL and COM-<br>PLEX expression evaluations by not honoring parenthesis.                                                                                                             |  |

| -f[no-]omit-frame-pointer       | er enable(DEFAULT)/disable use of EBP as general purpose registerfno-omit-frame-pointer replaces -fp                                                                                                                                           |  |

| -f[no-]exceptions               | enable(DEFAULT)/disable exception handling                                                                                                                                                                                                     |  |

| -[no-]ip                        | enable(DEFAULT)/disable single-file IP optimization within files                                                                                                                                                                               |  |

| -[no-]scalar-rep                | enable(DEFAULT)/disable scalar replacement (requires -O3)                                                                                                                                                                                      |  |

| -[no]pad                        | enable/disable(DEFAULT) changing variable and array memory layout                                                                                                                                                                              |  |

| -[no-]ansi-alias                | enable(DEFAULT)/disable use of ANSI aliasing rules optimizations; user asserts that the program adheres to these rules                                                                                                                         |  |

| -[no-]complex-<br>limited-range | enable/disable(DEFAULT) the use of the basic algebraic expansions of some complex arithmetic operations. This can allow for some performance improvement in programs which use a lot of complex arithmetic at the loss of some exponent range. |  |

| -[no-]ansi-alias                | enable(DEFAULT)/disable use of ANSI aliasing rules optimizations; user asserts that the program adheres to these rules                                                                                                                         |  |

| -[no-]complex-<br>limited-range | enable/disable(DEFAULT) the use of the basic algebraic expansions of some complex arithmetic operations. This can allow for some performance improvement in programs which use a lot of complex arithmetic at the loss of some exponent range. |  |

| -no-heap-arrays                 | temporary arrays are allocated on the stack (DEFAULT)                                                                                                                                                                                          |  |

| -[no-]vec                       | enables(DEFAULT)/disables vectorization                                                                                                                                                                                                        |  |

| -coarray                        | enable/disable(DEFAULT) coarray syntax for data parallel programming                                                                                                                                                                           |  |

| -q[no-]opt-matmul               | replace matrix multiplication with calls to intrinsics and threading libraries for improved performance (DEFAULT at -O3 -parallel)                                                                                                             |  |

| -[no-]simd                      | enables(DEFAULT)/disables vectorization using SIMD directive                                                                                                                                                                                   |  |

| -qno-opt-prefetch               | disable(DEFAULT) prefetch insertion. Equivalent to -qopt-prefetch=0                                                                                                                                                                            |  |

| -qopt-dynamic-align             | enable(DEFAULT) dynamic data alignment optimizations. Specify -qno-opt-dynamic-align to disable                                                                                                                                                |  |

| -[no-]prof-data-order           | enable/disable(DEFAULT) static data ordering with profiling                                                                                                                                                                                    |  |

| -pc80                           | set internal FPU precision to 64 bit significand (DEFAULT)                                                                                                                                                                                     |  |

| Default flag               | Description                                                                                                                                                                                                                                                                                           |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -auto-scalar               | make scalar local variables AUTOMATIC (DEFAULT)                                                                                                                                                                                                                                                       |

| -[no]zero                  | enable/disable(DEFAULT) implicit initialization to zero of local scalar variables of intrinsic type INTEGER, REAL, COMPLEX, or LOGICAL that are saved and not initialized                                                                                                                             |

| -init= <keyword></keyword> | enable/disable(DEFAULT) implicit initialization of local variables of intrinsic type INTEGER, REAL, COMPLEX, or LOGICAL that are saved and not initialized The <keyword> specifies the initial value keywords: zero (same as -zero), snan (valid only for floating point variables), arrays</keyword> |

| -Zp[n]                     | specify alignment constraint for structures (n=1,2,4,8,16 -Zp16 DEFAULT)                                                                                                                                                                                                                              |

| -fstack-security-check     | enable overflow security checksfno-stack-security-check disables (DEFAULT)                                                                                                                                                                                                                            |

| -fstack-protector          | enable stack overflow security checksfno-stack-protector disables (DEFAULT)                                                                                                                                                                                                                           |

| -fstack-protector-strong   | enable stack overflow security checks for routines with any bufferfno-stack-protector-strong disables (DEFAULT)                                                                                                                                                                                       |

| -fstack-protector-all      | enable stack overflow security checks including functionsfno-stack-protector-all disables (DEFAULT)                                                                                                                                                                                                   |

| -fpic, -fPIC               | generate position independent code (-fno-pic/-fno-PIC is DEFAULT)                                                                                                                                                                                                                                     |

| -fpie, -fPIE               | generate position independent code that will be linked into an executable (-fno-pie/-fno-PIE is DEFAULT)                                                                                                                                                                                              |

| [no-]global-hoist          | enable(DEFAULT)/disable external globals are load safe                                                                                                                                                                                                                                                |

| -f[no-]keep-static-consts  | enable/disable(DEFAULT) emission of static const variables even when not referenced                                                                                                                                                                                                                   |

| -mcmodel= <size></size>    | use a specific memory model to generate code and store data.                                                                                                                                                                                                                                          |

|                            | <ul> <li>small - Restricts code and data to the first 2GB of address space (DEFAULT)</li> <li>medium - Restricts code to the first 2GB; it places no memory restriction on data</li> <li>large - Places no memory restriction on code or data</li> </ul>                                              |

| -falign-functions=[2 16]   | align the start of functions on a 2 (DEFAULT) or 16 byte boundary                                                                                                                                                                                                                                     |

The performance impact of the different flags differ, and there are not really an optimal set of flags that suits all.

For the Intel compiler experience have shown that some flags are generally a good starting option. Intel have done a good job to ensure that the default flags are adapted to a range of applications. The vectorization is enabled per default, but we can force the compiler to generate code for our target architecture, in this case the KNL and the corresponding flag MIC-AVX512 (-xMIC-AVX512). The fused multiply add -fma is almost always yielding better performance. Another important flag is -O3, while not always yield better performance than -O2, it usually does. Aligning is another important flag to use, even though the penalty for a misaligned load is not as high as it use to be. With a 64 byte cache line the flag -align array64byte is useful. Inlining of functions can enable vectorization of some functions so -finline-functions might provide a higher degree of vectorization.

Flags like -ipo and loop unrolling are discussed in the tuning section as they they are more in the application tuning section.

A suggested set of flags for the Intel compilers are given in the table below.

Table 2. Suggested compiler flags for Intel compilers

| Compiler               | Suggested flags                                             |

|------------------------|-------------------------------------------------------------|

| Intel C compiler       | -O3 -xMIC-AVX512 -fma -align -finline-functions             |

| Intel C++ compiler     | -std=c11 -O3 -xMIC-AVX512 -fma -align -finline-functions    |

| Intel Fortran compiler | -O3 -xMIC-AVX512 -fma -align array64byte -finline-functions |

With a system with the High Bandwidth Memory set to cache the streaming stores should be disabled, *-qopt-streaming-stores=never*. The HBM is a memory side cache and cannot be bypassed. The cache line have to be loaded into the HBM cache in any case. See Figure 16 and associated text in Section 4.1 for a discussion about this.

Below is a table showing the most relevant default flags set by the GNU compilers.

Table 3. Default GNU Fortran compiler flags

| Default flag        | Description                                                                                                                                                                                                                                               |  |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| -O0                 | Reduce compilation time and make debugging produce the expected results.                                                                                                                                                                                  |  |

| -fno-inline         | Do not expand any functions inline apart from those marked with the "always_inline" attribute.                                                                                                                                                            |  |

| -mcmodel=small      | Generate code for the small code model. The program and its statically defined symbols must be within 4 GiB of each other. Pointers are 64 bits. Programs can be statically or dynamically linked.                                                        |  |

| -funderscoring      | By default, GNUFortran appends an underscore to external names.                                                                                                                                                                                           |  |

| -fno-protect-parens | By default the parentheses in expression are honored for all optimization levels such that the compiler does not do any re-association. Using -fno-protect-parens allows the compiler to reorder "REAL" and "COMPLEX" expressions to produce faster code. |  |

The GNU compiler set of default flags are not aggressively optimized for performance as is the default flags set by Intel. Some more investigation is generally needed with the GNU compilers.

A suggested set of flags for the GNU set of compilers are given in the table below.

Table 4. Suggested compiler flags for GNU compilers

| Compiler                                                                                                                     | Suggested flags                                                                                                        |  |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--|

| gcc compiler                                                                                                                 | -march=knl -O3 -mavx512f -mavx512pf -mavx512er -<br>mavx512cd -mfma -malign-data=cacheline -finline-functions          |  |

| g++ compiler                                                                                                                 | -std=c11 -march=knl -O3 -mavx512f -mavx512pf -mavx512er -<br>mavx512cd -mfma -malign-data=cacheline -finline-functions |  |

| gfortran compiler -O3 -march=knl -mavx512f -mavx512pf -mavx512er - mavx512cd -mfma -malign-data=cacheline -finline-functions |                                                                                                                        |  |

The flags setting the vector capabilities (-mavx512) let the compiler generate code for the 512 bits wide vector registers, it is assumed that any former instruction subset is included, e.g. that also SSE, AVX instructions are generated.

# 3.3. Available (Vendor Optimized) Numerical Libraries

The most common for Intel based systems are Intel Math Kernel Library, MKL and the Intel Performance Primitives. MKL contain a large range of high level functions of like Basic Linear Algebra, Fourier Transforms etc, while IPP contains a large number of of more low level functions like converting, scaling etc. For even lower level functions like scalar and vector versions of simple functions like square root, logarithmic and trigonometric there are libraries like libimf and libsyml.

# 3.3.1. Math Kernel Library, MKL

Intel MKL is installed with the compiler suite and are an integrated part of the compiler suite. The simplest way of enabling the MKL is to just issue the flag -mkl, this will link the default version of MKL, for a multicore system this will be the threaded version (-mkl=parallel). The actual link line is hidden and not presented when using

this shortcut. On a KNL system using a parallel MKL will effectively turn a pure MPI application into a hybrid application.

There are both a single threaded sequential version and a threaded multicore version. Most pure MPI jobs just require -mkl=sequential. To link with Intel MKL cluster components (sequential) that use Intel MPI use the cluster option. If ScaLapack routines are needed, use the -mkl=cluster option. The -mkl=cluster flag links to the sequential routines of the libraries, if the ScaLapack with threaded libraries are needed, you need to provide the correct combinations of the libraries to the link line. Please refer to the examples below or the Intel MKL link line advisor (see 3.3.1.2).

The sequential and cluster version are mostly used with none hybrid MPI programs. The parallel version can be controlled using the environment variable OMP\_NUM\_THREADS.

In some cases the user want to control the amount of High Bandwidth Memory that MKL allocate. Setting *MKL\_FAST\_MEMORY\_LIMIT=0* will prevent MKL from allocating memory in the High Bandwidth Memory.

Table 5. Invoking different versions of MKL

| MKL Version                   | Link flag             |

|-------------------------------|-----------------------|

| Single thread, sequential     | -mkl=sequential       |

| Single thread MPI, Sequential | -mkl=cluster          |

| Multi threaded                | -mkl=parallel or -mkl |

MKL contains a range of functions and other libraries. Several of the common widely used libraries and functions have been incorporated into MKL. Intel provide a large set of documentations etc about MKL, see Intel MKL documentation [https://software.intel.com/en-us/articles/intel-math-kernel-library-documentation].

#### **Libraries contained in MKL:**

- BLAS, BLAS95 and Sparse BLAS

- FFT and FFTW (wrapper)

- LAPACK

- Direct and Iterative Sparse Solvers, including PARADISO

- ScaLAPACK with BLACS

- Vector Math

- Vector Statistics Functions

A large fraction of the common functions that are needed for development are part of the MKL, Basic linear algebra (BLAS 1,2,3), FFT and the wrappers for FFTW. Software often require the FFTW package, with the wrappers there is no need to install FFTW which is outperformed by MKL in most cases.

#### 3.3.1.1. MKL examples

MKL is very simple to use, the functions have simple names and the parameter lists are well documented. An example of calling a matrix multiplications is show below:

```

write(*,*)"MKL dgemm

call dgemm('n', 'n', N, N, N, alpha, a, N, b, N, beta, c,N)

```

or with fftw syntax:

# Best Practice Guide - Knights Landing

```

call dfftw_plan_dft_r2c_2d(plan,M,N,in,out,FFTW_ESTIMATE)

call dfftw_execute_dft_r2c(plan, in, out)

```

The calling syntax is just as for dgemm from reference Netlib BLAS implementation and the widely used FFTW. The same apply to the other functions, calling and parameter list is kept as close to the reference implementation as practically possible.

The usage and linking sequence of some of the libraries can be somewhat tricky. Please consult the Intel compiler and MKL documentation for details. An example from building the application VASP is given below (list of object files object contracted to \*.o):

```

mpiifort -mkl -lstdc++ -o vasp *.o -Llib -ldmy\

-lmkl_scalapack_lp64 -lmkl_blacs_intelmpi_lp64 -lfftw3xf_intel_lp64

or even simpler for a fftw example:

```

```

ifort fftw-2d.f90 -o fftw-2d.f90.x -mkl

```

#### 3.3.1.2. Intel MKL link line advisor

Since the link line can be a bit complicated Intel has produced a nice tool to help making the correct link line, Intel MKL linking advisor [https://software.intel.com/en-us/articles/intel-mkl-link-line-advisor].

### 3.3.2. Intel Performance Primitives, IPP

Performance primitives library contain functions that do simple operations on scalars, vectors and smaller matrices. It is best suited for image and signal processing, data compression and cryptography.

Intel IPP offers thousands of optimized functions covering frequently used fundamental algorithms including those for creating digital media, enterprise data, embedded, communications, and scientific/technical applications.

The library contains a huge number for functions with a range of data types. Please refer to the documentation for a detailed description. Intel provide online documentation for IPP [https://software.intel.com/en-us/intel-ipp].

Examples provided with the library includes a high performance compress, gzip and bzip program. Another example of usage is shown below:

```

#include "ipp.h"

#include "ippcore.h"

#include "ipps.h"

#include <stdio.h>

#include <math.h>

#include <stdint.h>

void libinfo(void) {

const IppLibraryVersion* lib = ippsGetLibVersion();

printf("%s %s %d.%d.%d.%d\n",

lib->Name, lib->Version,

lib->major,

lib->minor, lib->majorBuild, lib->build);

#define N 207374182

main() {

int16 t x[N];

declspec(align(64)) float a[N],b[N],c[N];

```

```

float sum;

int i,j;

double t0,t;

extern double mysecond();

libinfo();

printf("Vector sizes int-vec %ld float vec %ld\n",(long)N*2, (long)N*4);

for (j=0; j<N; j++) x[j]=1;

t0=mysecond();

ippsConvert_16s32f(x, a, N);

t=mysecond()-t0;

printf("Convert time ipp %lf sec.\n",t);

t0=mysecond();

ippsCopy_32f(a, b, N);

ippsAdd_32f_I(b, c , N);

ippsMul_32f_I(b, c, N);

ippsAddProduct_32f(a, b, c, N);

ippsSqrt_32f(c, c, N);

ippsSum_32f(c, N, &sum, 1);

for (j=0; j<10; j++) printf("%d: %f\n",j,c[j]);

printf("IPP: Sum %10.0f time %1f sec Flops %1d %1f Gflops/sn",

sum, t, (long)N*2, ((double)N*10/t)/1e9);

```

### 3.3.3. Math library, libimf

Intel Math Libraries, in addition to libm. {a,so}, the math library provided with gcc and Linux.

Both of these libraries are linked in by default because certain math functions supported by the GNU math library are not available in the Intel Math Library. This linking arrangement allows the GNU users to have all functions available when using ifort, with Intel optimized versions available when supported.

This is why libm always shows up when using the Intel compilers, even when you linked with libimf (even before libm) when you check the library dependencies using ldd.

Performance of the libimf is generally better that using libm from gcc. The functions is optimized for use with Intel processors and seems to be well optimized. An example of performance gain can be found at Intel's web site, optimizing-without-breaking-a-sweat [https://software.intel.com/en-us/articles/optimizing-without-breaking-a-sweat], where they claim very high gains when making heavy use of the *pow* function. The simple test below:

```

for(j=0; j<N; j++) c[j]=pow(a[j],b[j]);</pre>

```

show a speedup of 3x when compiled with gcc 5.2.0 and linked -limf instead of the more common -lm.

# 3.3.4. Short vector math library, libsvml

The short vector math library functions take advantage of the vector unit of the processor and provide an easy access to well optimized routines that map nicely on the vector units.

The svml is linked by default and the functions are not easily available directly from source code. They are, however accessible through intrinsics. Intel provide a nice overview of the intrinsic functions available [https://software.intel.com/en-us/node/524288]. Usage of intrinsics can yield quite good performance gain. In addition intrinsics are compatible with newer versions of processors as the compilers and libraries and updated while the

names stay the same. Usage of inline assembly might not be forward compatible. Intel strongly suggest using intrinsics instead of inline assembly.

A simple example of intrinsic usage is show below:

```

for(j=0; j<N; j+=8){

__m512d vecA = _mm512_load_pd(&a[j]);

__m512d vecB = _mm512_load_pd(&b[j]);

__m512d vecC = _mm512_pow_pd(vecA,vecB);

_mm512_store_pd(&c[j],vecC);

}</pre>

```

The performance can be quite good compared to the serial code below.

```

for(j=0; j<N; j++) c[j]=pow(a[j],b[j]);</pre>

```

Mostly due to the difference in calls to *svml\_d\_pow8* vector function and the libimf serial *pow* function. However, at high optimization the compiler will recognize the simple expression above and vectorize it and performance gain will be lesser. The usage of these intrinsics is at its best when the compiler totally fails to vectorize the code.

If you want to play with this there is a blog entry by Kyle Hegeman [http://kylehegeman.com/blog/2013/12/27/using-intrinsics/] that will be helpful.

# 3.4. Available MPI Implementations

There are two different MPI implementations installed.

#### **MPIs installed:**

- · Intel compiler MPI

- OpenMPI

The two has quite common syntax during compiling and simple runs. The mpirun have a range of options, which is quite different. Please consult the help files and documentation for details about these options. For most runs the queue system will set up the run in a sensible way.

**Table 6. Implementations of MPI**

| MPI library | MPI CC | MPI CXX | MPI F90  |

|-------------|--------|---------|----------|

| Intel MPI   | mpiicc | mpiicpc | mpiifort |

| OpenMPI     | mpicc  | mpicxx  | mpifort  |

OpenMPI is built with a specific compiler suite so the mpicc, mpicxx and mpifort wrappers will invoke the compilers used during the build. This can be overrun with environment variables, but FORTRAN modules (expressions like "use mpi") might not work as expected.

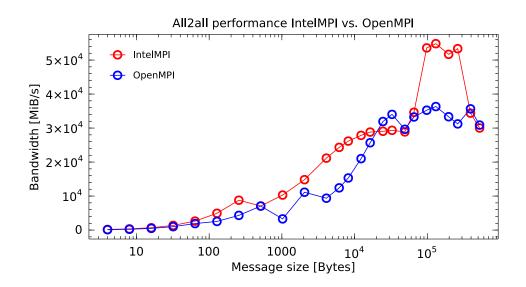

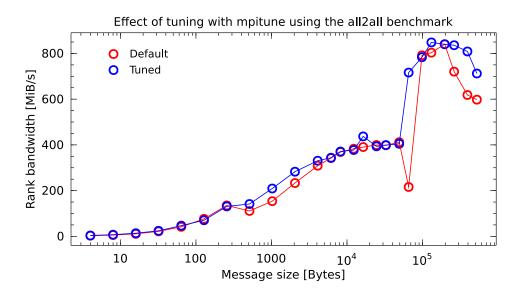

The two common MPI implementations Intel MPI and OpenMP are both fully supported with Knights Landing. Both perform good with some minor differences which is evident in the figure below. The all2all test is just one of a large range of MPI functions, but as this guide is not a benchmark report we show just an example that they both perform on KNL.

Figure 14. Comparing two MPI implementations

# 3.5. OpenMP

OpenMP is are supported with all the above compilers, Intel, GNU.

Table 7. Versions of OpenMP supported

| Compiler suite | Compiler version | Version supported |

|----------------|------------------|-------------------|

| Intel          | 2017.beta        | OpenMP 4.0        |

| GNU            | 6.1.0            | OpenMP 4.0        |

# 3.5.1. Compiler Flags

Table 8. OpenMP enabling flags

| Compiler | Flag to enable OpenMP |

|----------|-----------------------|

| Intel    | -qopenmp              |

| GNU      | -fopenmp              |

A common set of flags with the Intel Fortran compiler ifort is:

-O3 -xMIC-AVX512 -qopenmp -align array64byte -fma -ftz -finline-functions

and for the C/C++ icc and icpc

-O3 -xMIC-AVX512 -qopenmp -align -fma -ftz -finline-functions.

# 4. Benchmark performance

Benchmark performance is used to show the different performance aspect of a processor.

### 4.1. STREAM benchmark

Stream is a well known benchmark for measuring memory bandwidth written by John D. Calpin of TACC. TACC also happen to host the large supercomputer system called "Stampede" which is an accelerated system using a large array of Intel Xeon Phis.

The system is set up in quadrant mode and High Bandwidth Memory is used as a last level cache.

Stream can be built in several ways, it turned out that static allocation of the three vectors of which to operate on provided the best results. The source code illustrate how the data is allocated:

```

#ifndef USE_MALLOC

static double a[N+OFFSET], b[N+OFFSET],c[N+OFFSET];

#else

static volatile double *a, *b, *c;

#endif

#ifdef USE_MALLOC

a = malloc(sizeof(double)*(N+OFFSET));

b = malloc(sizeof(double)*(N+OFFSET));

c = malloc(sizeof(double)*(N+OFFSET));

#endif

```

The C version of benchmark was compiled using Intel icc with the following flags used: -O3 -xMIC-AVX512 - fomit-frame-pointer -qopenmp -fma.

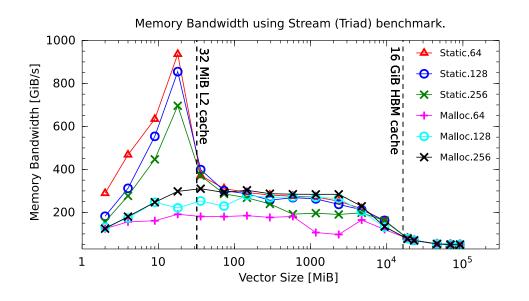

The figure below show the difference between using malloc and static allocation, when running the Stream benchmark with a range of threads, ranging 64 to 256, e.g. 1 to 4 threads per core. In order to use all Level 2 cache in all cores the threads have been scattered over most possible cores using the environment variable *KMP\_AFFINITY* set to *scatter*.

It's evident that L2 cache has a very high bandwidth as does the Last Level Cache (High Bandwidth Memory). All subsequent runs using stream were done using static allocation.

Figure 15. Memory bandwidth using Static allocation versus Malloc allocation

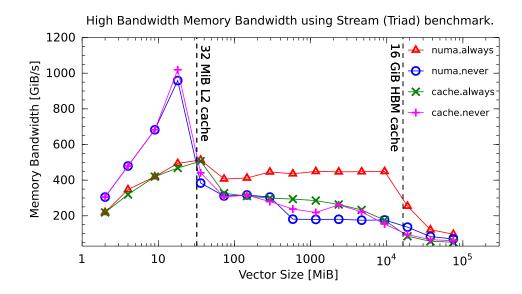

When running memory bandwidth benchmarks like stream the option to bypass the cache by using store instruction (-qopt-streaming-stores=always that store directly into memory can have an impact on performance. The figure below show the impact of using streaming store instructions that effectively bypass the cache. For small vector sizes there is a penalty when bypassing the cache. MCDRAM as cache is strictly inclusive. Every cache line has to be allocated in MCDRAM cache which basically mean that even in the case of nontemporal stores. The system need to do an extra read to MCDRAM thus wasting bandwidth for unnecessary reads (essentially like a regular store from the point-of-view of MCDRAM). Hence the bandwidth difference between the NT stores to flat MCDRAM and MCDRAM as cache. Since, from the point-of-view of the CPU, streaming stores are more complicated and require more complex micro ops to function, they really do not give that much benefit as their main benefit is negated by the inclusivity of the MCDRAM cache. It can look like the last level cache (the High Bandwidth Memory) is not bypassed by the streaming store instructions.

The figure below show the obtained bandwidth numbers when using the stream benchmark with 64 scattered threads. In the NUMA cases the HBM memory is set as a separate NUMA bank and numactl is used to preferably allocate from this bank.

numactl --preferred=1 ./stream.large.x

The benchmark is compiled using streaming stores always or never (-qopt-streaming-stores=always or never).

Figure 16. High Bandwidth Memory bandwidth NUMA vs. Cache / streaming store instructions or not

From the figure above it's beneficial to not use streaming stores for small size accesses, obvious for the cases where the chunk fit in the L2 cache. However in the case of flat memory and chunks larger than the L2 cache it's yielding significantly higher bandwidth numbers.

# 4.2. NAS kernel benchmark, NPB

The NAS benchmarks are well known. They are mostly known as MPI benchmarks, but they have been rewritten to OpenMP version and other parallel implementations.

As the KNL is a general processor it can run both OpenMP threaded shared memory code or distributed memory code like MPI. Hence both implementations have been tested. Most attention to the threaded version as this is more interesting with a cache coherent shared memory system.

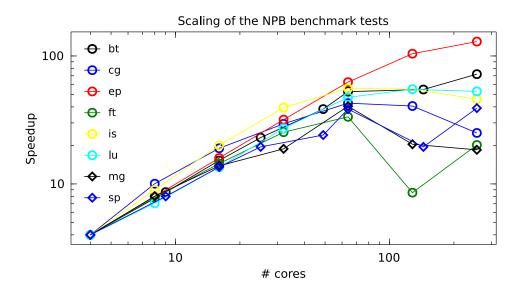

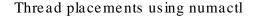

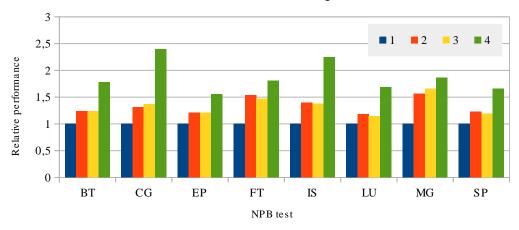

For this kind of benchmarks based on real application all optimization comes into play, prefetch, placement and affinity, threads per core etc. The effect of different placements is shown in figure below where the three models compact, scatter and balanced are shown. The best result for each test is compared, the actual number of cores might change as behavior changes with most parameters. The performance difference effect of placement is significant and care must always be taken to select optimal affinity. Which placement model yield best performance is not obvious. For small selected problems where all data for two or more threads can be kept in the L2 cache a compact model might be the best option. However, if those threads are competing for the execution units the core might be starved for execution units. The scheduler can fill the vector unit a thread, this is an improvement from Knights Corner where two threads were needed. In addition memory bandwidth are often a limiting factor. One core has a certain bandwidth and by spreading the threads onto many cores the total aggregated bandwidth is far larger than from a smaller set of cores.

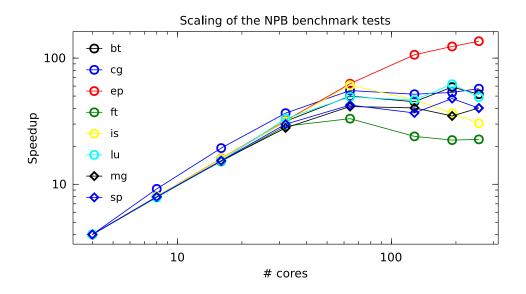

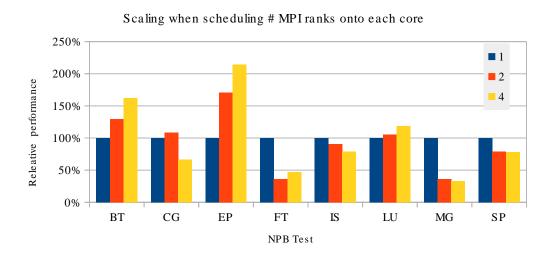

### 4.2.1. Scaling and Speedup test

The scaling of performance increase as a function of applying more mores are always a good technique to start assessing the performance of an application or a benchmark. The figures below show the performance speedup when increasing the core count. Perfect scaling up to four cores have been assumed.

Figure 17. Scaling test using MPI version of NPB

Figure 18. Scaling test using OpenMP version of NPB

From the figure we see that applying more physical cores and hence more execution/vector units increase performance nicely. The behavior start to change when more than one MPI rank or OpenMP thread per physical core is scheduled. Some benchmarks cores benefit others not. The NPB benchmarks are well selected to represent different kind of application kernels. From the figure it is clear that for most applications using up to 64 cores are ok, but thorough testing is required if using more than one rank per core.

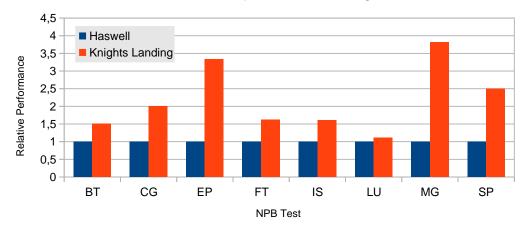

#### 4.2.2. Performance

The NPB set of benchmarks is a nice set of tests to assess the processor and system performance and compare with other processors and systems. The figure below show the performance obtained from a single systems with Dual Haswell<sup>2</sup> processors and the KNL system. Optimal core count is used in each case. The figure below thus compare compute node versus compute node, even though the Haswell node is a dual socket node. It is usually better to compare compute node versus compute node then processor versus processor.

<sup>&</sup>lt;sup>2</sup>Supermicro, SYS-6028TR-HTFR, E5-2660v3 2.6GHz, 64GiB, 8GB DDR4-2133 1Rx4 LP ECC RAM.

Figure 19. Performance Dual socket Haswell node versus KNL node

#### NPB Haswell vs. Knights Landing

NPB MPI version, max performance on a single node

The figure show that a single socket KNL node outperform a dual socket Haswell node. Again we see the different NPB kernels show exercises different type of computation and communication.

### 4.3. HYDRO benchmark

HYDRO is a much used benchmark in the PRACE community, it is extracted from a real code (RAMSES, which is a computational Fluid Dynamics code). Being widely used it has been ported to a number of platforms. The code exist in many versions, FORTRAN 90, C, CUDA, OpenCL as well as serial, OpenMP and MPI versions of these. Some versions have been instrumented with performance counters to calculate the performance in Mflops/s.

The instrumented version is a FORTRAN 90 versions and this version in both OpenMP and MPI versions have been used for evaluation. The OpenMP implementations exhibit far inferior performance than the MPI versions. Hence performance testing and comparison is only done using the MPI version.

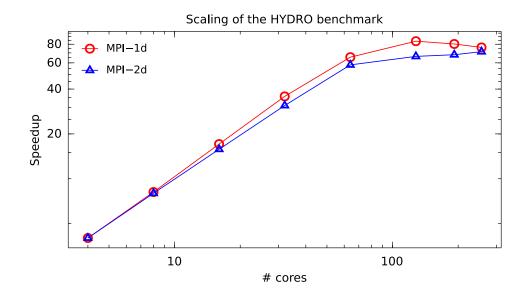

# 4.3.1. Scaling and Speedup test

Assessing the increased speedup with increasing core count is important with any benchmark or application. In some fortunate cases like well used benchmarks there are both MPI and OpenMP implementations.

Figure 20. Scaling test using MPI versions of HYDRO

From the figure above we see that adding more executions units e.g. more physical cores improves performance linearly. Issuing more than one rank per core onto the already busy executing units will not deliver any more performance. The 1-dimensional and 2-dimensional implementations exhibit just minor performance differences, both in terms of absolute Mflops/s numbers and in scaling.

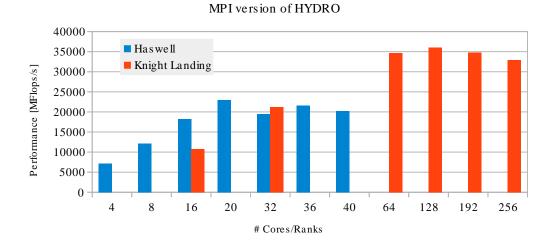

#### 4.3.2. Performance

The HYDRO benchmark being a kernel of a real scientific applications is a nice example to compare compute nodes based on Haswell by KNL based ones. The following performance evaluations is done using two single compute nodes one dual socket Haswell based compute node<sup>3</sup> and one single socket KNL node. The figure below show the performance recorded for the two compute nodes.

<sup>&</sup>lt;sup>3</sup>Supermicro, SYS-6028TR-HTFR, E5-2660v3 2.6GHz, 64GiB, 8GB DDR4-2133 1Rx4 LP ECC RAM.

Figure 21. Performance of a Dual socket Haswell node versus a KNL node

HYDRO benchmark - Has well node vs. Knights Landing node

Using the MPI version of HYDRO which scales to a higher core count the Knights Landing processor can utilize all the cores and outperform a dual socket Haswell based system.

# 5. Application Performance

A range of different application has been tested. Both threaded single node applications and application based on Message Passing Interface (MPI) and threading model OpenMP.

# 5.1. ALYA

ALYA is a Computational Mechanics code capable of solving different physics, each one with its own modelization characteristics, in a coupled way. Among the problems it solves are: convection-diffusion reactions, incompressible flows, compressible flows, turbulence, bi-phasic flows and free surface, excitable media, acoustics, thermal flow, quantum mechanics (DFT) and solid mechanics (large strain).

ALYA is part of the Unified European Applications Benchmark Suite (UEABS), the codes can be found here [http://www.prace-ri.eu/ueabs/].

# 5.1.1. Building and compiling

The ALYA version used was downloaded from SURFSARA web drive [https://surfdrive.surf.nl/files/index.php/s/cbo1up9bZCP1iTT?path=%2FAlya] in October 2016.

The building of ALYA was straightforward, changing the configure files for the makefiles to use Intel MPI and compilers was well documented. Building of third libraries could be done with GNU or Intel compilers. Both versions link with the Intel build. Compilation flags suggested in this guide were used, see table below.

Table 9. Compiler and library versions

| Compiler / Library | Versions and information                                                                                      |  |

|--------------------|---------------------------------------------------------------------------------------------------------------|--|

| C/Fortran          | Intel 2017 (2017.0.098)                                                                                       |  |

| MPI                | Intel MPI Version 2017 Build 20160721                                                                         |  |

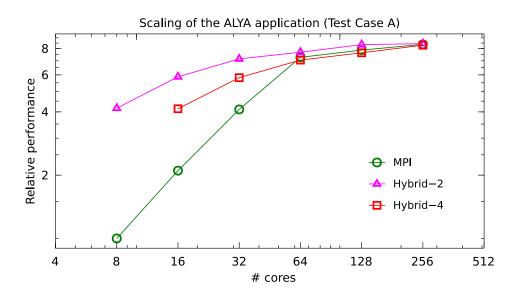

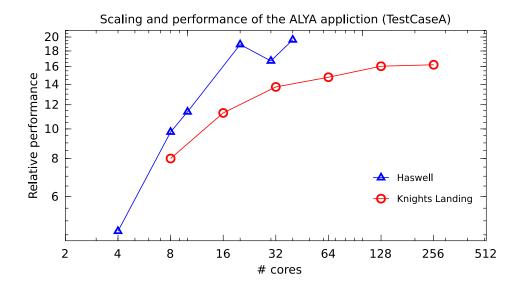

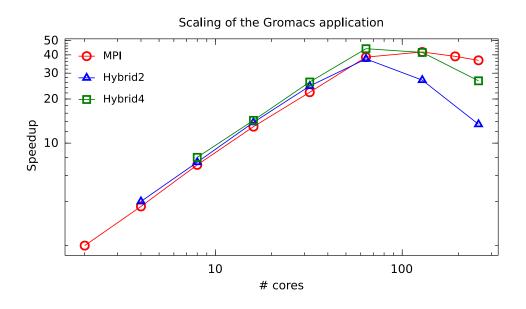

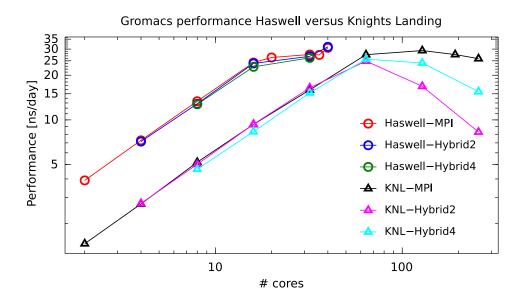

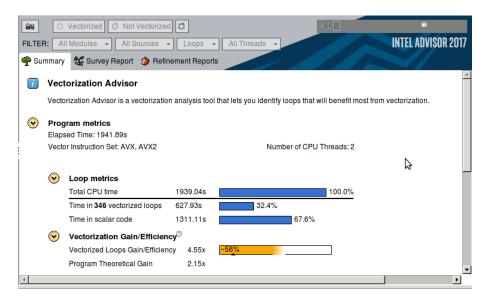

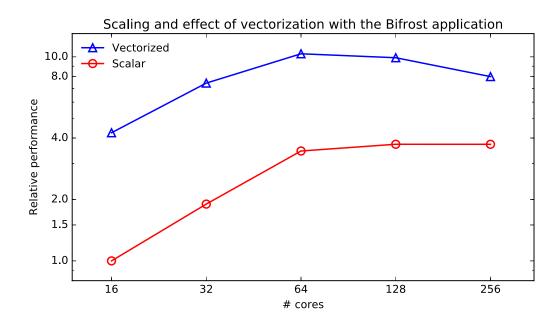

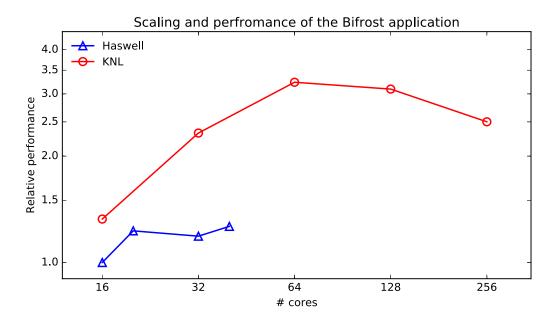

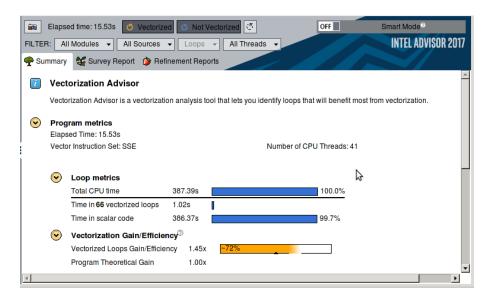

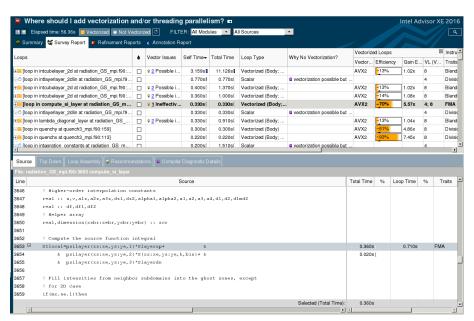

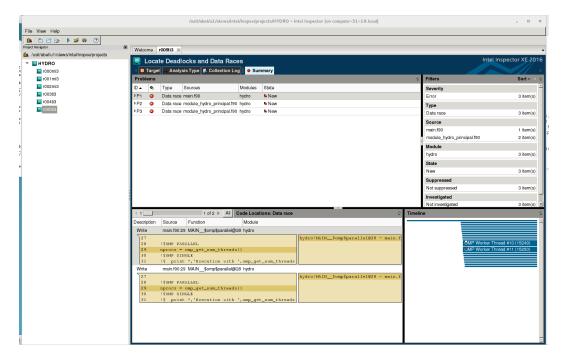

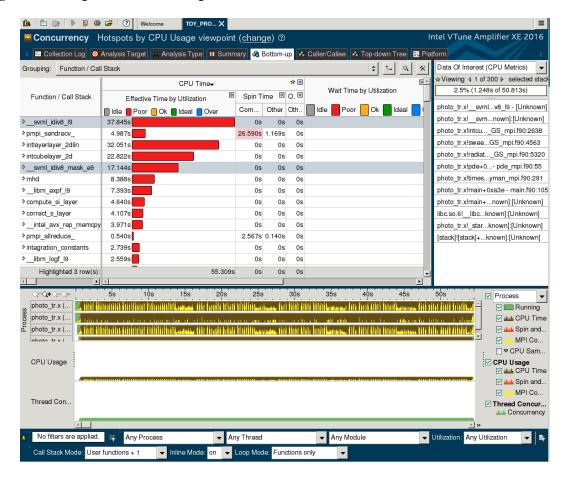

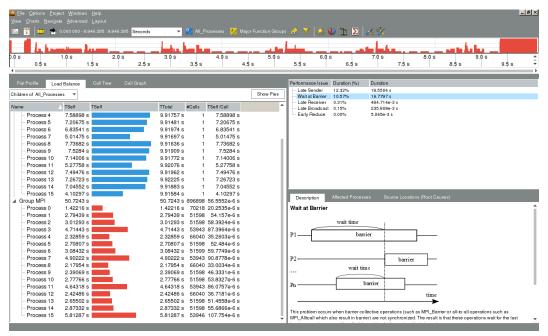

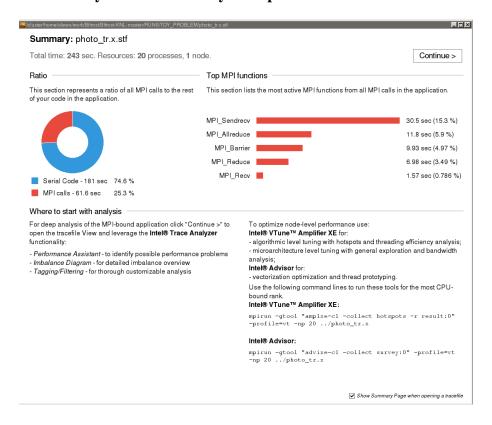

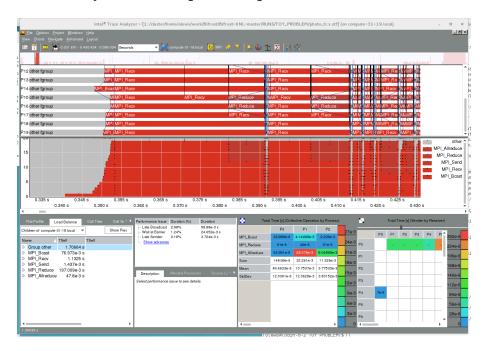

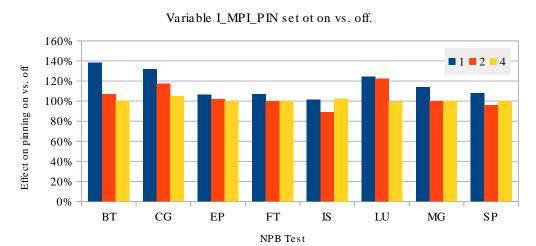

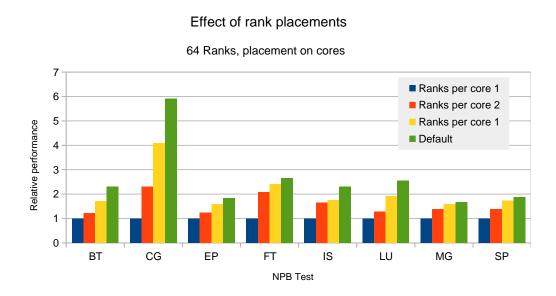

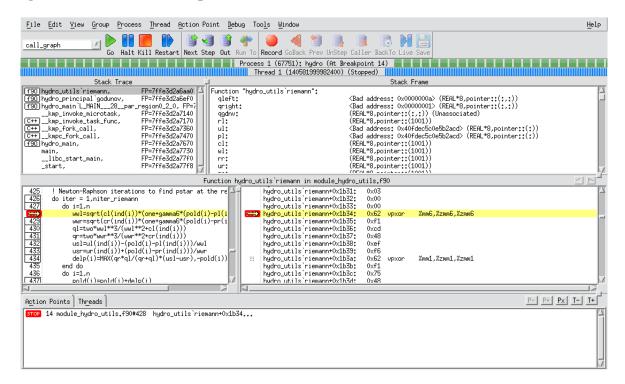

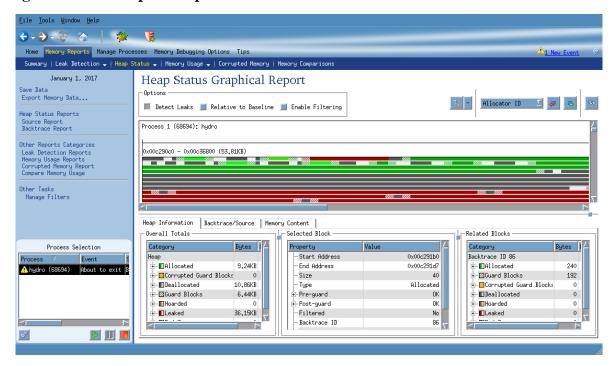

| Compiler flags     | -O3 -xMIC-AVX512 -align array64byte -fma -ftz -fomit-frame-pointer -finline-functions -qopenmp (hybrid model) |  |