# An Ultrashort Electric Field Pulse Generator using Avalanche Breakdown Transistors and the Open Circuit Transmission Line Technique for Nanosecond Electroporation

Ilan Wyn Davies\*+ and Christopher Paul Hancock\*+

\*School of Computer Science and Electronic Engineering, Bangor University, Bangor, United Kingdom. +Creo Medical Group PLC. Chepstow, United Kingdom.

*Abstract*— An ultrashort electric field pulse generator based on relatively slow charging and ultrafast discharging of a co-axial transmission line in conjunction with a stack of low-cost avalanche breakdown transistors which operate as a fast switching element has been designed and built. This low-cost circuit design produces well defined ultrashort electric field pulses with symmetrical rise and fall times of less than 2 ns. The pulse duration is determined by the length of the open-circuit transmission line. Initial results indicate that the circuit is capable of generating well defined nanosecond electroporation pulses to support nanosecond-pulse-based applications in biology, medicine and/or in a cost-effective manner.

Index Terms— Ultrashort Electric-Field Pulse, Transmission Lines, Avalanche Breakdown Transistors, Circuit Design & Applications.

## I. INTRODUCTION

In recent years there have been numerous developments of the application of ultrashort electric field pulse generators within the research field, with over 500 citations since 2017 on Google Scholar [1]. One growing application of these electric fields is electroporation of biological cells [2]. Ultrashort electric field pulses generated by avalanche breakdown transistors (ABTs) have been used in applications such as: laser technologies, high speed photography, ultrawideband radar and wireless communication systems [3]-[5].

Classical electroporation is the application of controlled pulsed electric fields in the milli-to-microsecond time frame to cells and tissue masses. Nanosecond electroporation is a further development of the classical electroporation where the pulsed electric filed are ultrashort, i.e. in the nanosecond (ns) regime [6]-[7]. Literature suggests ultrashort electric field pulse or nanosecond electroporation has additional potentials for cell manipulation and control of cell physiology; Effects include increased plasma membrane permeabilization, calcium (Ca<sup>++</sup>) release, ion channels activation and apoptosis induction [6]-[7].

In this article, a novel circuit design for the generation of ultrashort electric field pulses with minimal ringing and a 'flat-top' profile with steep symmetrical rise and fall times of less than 2 ns is presented. The circuit consists of an opencircuit co-axial transmission line (CTL) technique in conjunction with a stack of low-cost ABTs which operate as a fast switching element.

This design topology embedded an adjustable ultrashort, high amplitude electric field pulse generator to be implemented, where pulse width, field amplitude.

# II. THEORY OF OPERATION

# A. Open Circuit Co-axial Transmission Line Technique

Pulse generation is possible by using an open circuit CTL as a low-cost high Q storage element consisting of distributed series inductors and shunt capacitors with minimal series resistance and shunt conductance. Discharging an openended delay line through a fast switching element, provides a means of producing 'flat-top' rectangular pulse with steep rise and fall times of less than 2 ns in a simple and affordable manner [8]-[11].

The CTL with a characteristic impedance Z0, and a length, l, and dielectric constant,  $\varepsilon_r$ , is charged to a voltage level,  $V_{cc}$ , through a high impedance resistor  $R_c$ . The line has an associated delay time, T (1). Where c is the speed of light (2.99x108 m/s).

$$T = \frac{l\sqrt{\varepsilon_r}}{c} \tag{1}$$

The charged CTL is discharged through a load resistance,  $R_L$ , by closing a switching element. The switching element determines the rise time of the ultrashort electric field pulse [8]-[11].

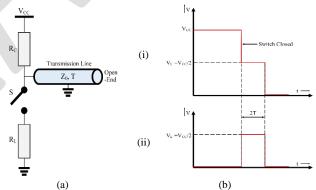

Fig. 1: Principle of a discharge line generator. (a) Basic circuit design (b) voltage waveforms at the transmission line (i) and load (ii)

$$V_L = \left(\frac{R_L}{R_L + Z_0}\right) V_{cc} \quad \therefore V_{Lmax} = \frac{V_{cc}}{2}, if \ R_L = Z_0 \qquad (2)$$

If the characteristic impedance,  $Z_0$ , of the CTL is the same as the load impedance,  $R_L$ , then the maximum amplitude of the pulse at the load,  $V_{Lmax}$ , is half the CTL voltage level ( $V_{cc}/2$ ) and the pulse width is 2T. The principle of generating an ultrashort electric field pulse using an open circuit CTL technique is illustrated in Fig. 1 [8]-[11]. Essentially, the relationship between  $Z_0$  and  $R_L$  imitates a potential divider as their relationship determines the pulse amplitude at the load  $V_L$  (2).

# B. Avalanche Breakdown Transistors (ABTs)

ABTs is an active switching element as that provide reliable and repeatable highspeed switching of high voltages with rise times as low as 300 ps, which can be achieved in practice if microwave component layout techniques are considered when the circuit are implemented [8]-[11].

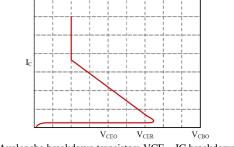

ABTs utilize the negative-resistance characteristics region of bipolar junction transistors, which result from operation in the common-emitter breakdown region ( $V_{CE} - I_C$  breakdown curve, Fig. 2), where  $V_{CE}$  is the voltage across the collector and emitter and  $I_C$  is the current flowing into the collector. The transistors avalanche region lies between collector-emitter ( $V_{CEO}$ ) and collector-base ( $V_{CBO}$ ) voltage with  $I_B=0$  and  $I_E=0$ . [1]-[2],[9].

Fig. 2: Avalanche breakdown transistors VCE - IC breakdown curve

Avalanche breakdown occurs when a reverse bias is applied to a semiconductor (collector-emitter) junction of a transistor resulting in an electric field across the junction. If the electric field/reverse bias is large enough minority carriers (electrons in an npn transistor) are accelerated through the space charge region of the base and collector junction which excite additonal carriers through impact ionization, as the minority carriers collides with the atoms in the crystal lattice[1]-[2],[9].

As the minority carriers collide with theses atoms it creates new electrons and holes that will accelerate (by the electric field) and create more electron-hole pairs. This effect causes an avalanche-type collector current rise. This is called an avalanche multiplication effect in the transistor, which can be described by the multiplication factor, M (3) [1]-[2],[9]. Where M is the multiplication factor, V is the applied voltage,  $V_B$  is the avalanche breakdown voltage (V<sub>CBO</sub>) and m, the empirical determined constant.

$$M = \frac{1}{1 - \left(\frac{V}{V_B}\right)^m} \tag{3}$$

# **III.** CIRCUIT DESIGN AND IMPLEMENTATION

#### A. Single Avalanche Breakdown Transistor Circuit Design

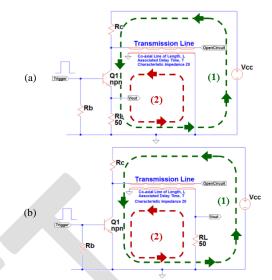

The circuit diagram of the implementation of a single ABT in conjunction with an open-ended CTL and the two current loops within the circuit are illustrated in Fig 3. The circuit function is based on the discharge of the CTL across an ABT.

An extremely small current flows in loop (1), in Fig 3, and energy is stored in the CTL. A positive trigger on the base of the transistors will suddenly switch the transistor 'on'. The energy stored in the CTL will simultaneously be released as a high current along loop (2), producing a positive pulse on  $R_L$  in Fig.3a or a negative pulse on  $R_L$  in Fig.3b. The rise-time of the pulse at  $R_L$  is < 2ns, and is determined by the avalanching time of the ABT. The pulse fall-time depends on the CTL.

Fig. 3: Circuit simulation model for generating a positive (a) or negative (b) ultra-short pulses with avalanche breakdown transistors and a charged open circuited co-axial transmission line.

# B. Stacking Multiple Avalanche Breakdown Transistor

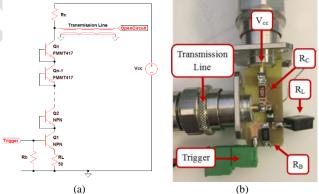

A single ABT circuit can be configured to have a bistable operation, where the maximum pulse amplitude at the output is limited to half the value of the ABTs collector-emitter breakdown voltage (BV<sub>CES</sub>). Staking multiple ABTs in series results in a proportionally higher pulse amplitude at the load (Fig. 4), where supply voltage  $V_{cc}$ /n is dropped across each of the ABTs in the series chain. Therefore, the pulse amplitude that can be generated depends on the number of ABTs stacked (n). The number of ABTs required to generate a specific pulse amplitude, VLmax, can be calculated (4), assuming  $Z_0 = R_L$ .

Fig. 4: (a) Circuit diagram for staking avalanche breakdown transistors with a transmission line for generating a higher pulse amplitude. (b) Example of constructed circuit with two FMMT417 avalanche transistors.

Initially, all the stacked ABTs are in there off-state. When a positive trigger signal is applied to the base of the first ABT (Q1), Q1 is turned 'on' and places its collector voltage near ground potential. This results in the second ABT (Q2) having twice the collector-emitter voltage, thus creating the desired condition in terms of overvolting and therefore causes a nondestructive avalanching of Q2 and places its collector near ground potential. This creates a sequential 'knock-on' effect on the next transistor in the chain resulting in the overvolting of the first ABT, Q1, to the final ABT in in the series chain, Qn. When Qn is turned 'on', a fast rise time is produced at the load, thus allowing the CTL to discharge through the load producing a pulse with a width of 2T and a maximum amplitude of  $V_{Lmax}$ .

$$n = \frac{2V_{Lmax}}{BV_{CES}} = \frac{Vcc}{2BV_{CES}}, \quad \therefore V_{Lmax} = \frac{nBV_{CBO}}{2}$$

(4)

IV. RESULT AND ANALYSIS

In the design presented here, Fig 4, a FMMT417 ABT were with avalanche breakdown voltages  $BV_{CEO}$  of 100V and  $BV_{CBO}$  of 320V was used to implement the design [12].

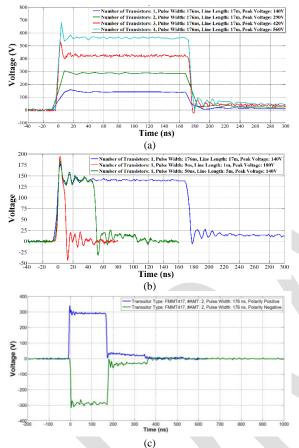

Fig. 5: (a) Measured observed pulse at load when increasing the number of avalanche breakdown transistors staked in series (1, 2, 3 and 4 transistors), based on Fig. 4 circuit design (b) Variations in the Pulse width when various coaxial transmission line length (1 and T), using on Fig. 3a circuit design. (c) Pulse polarity at load depending on load position (Fig. 3)

Fig. 5a demonstrates that staking multiple ABT in series produces a higher pulse amplitude on  $R_L$ . With every ABT added to the stacked the pulse amplitude at  $R_L$  increases by ~140V = ~ BV<sub>CBO</sub>/2, yet the pulse width, rise and fall times remain the same if the same CTL length and ABT type are used in the circuit design in Fig. 4. This verifies (4).

Fig. 5b validates (1), as the length of the CTL determines the pulse width. Shorter the line shorter the pulse as a 1 m CTL produces a 10 ns pulse, 5 m a 50 ns pulse, and 17 m a 170 ns pulse. The CTL used had a  $\varepsilon_r = 2.2$ . Fig. 5b demonstrates that the rise time of the pulse is determine by the switching element, the ABTs, as the pulses have the same rise time and the number of ABTs (one), the CTL type are the same and the only variant in the circuits between the three pulses in Fig. 5b are the CTL length. Result in Fig. 5 are measured output from the built circuit in Fig. 4. Fig. 5c demonstrates that the placement of the load within the circuit determines the pulse polarity, thus verifying Fig. 3.

# V. CONCLUSION

This novel design implemented utilizing a CTL in conjunction with ABT stacking offers a solution for generating ultrashort electric field pulses with the following attributes.

- Adjustable pulse width determined by the CTL length, 2T;

- Maximum pulse amplitude of  $V_{cc}/2$  or (n BV<sub>CBO</sub>)/2;

- Pulse polarity; is determined by the placement of the load within the circuit. Positive going pulse if the  $R_L$  is placed between the Q1's emitter and ground; Negative going pulse if  $R_L$  is placed between the CTL outer conductor and ground;

The use of low-cost components and microwave circuit design techniques offers a viable solution for a low cost and effective solution for an ultrashort adjustable pulse width, symmetrical fast rise/fall time and adjustable amplitude electric field pulse generator for investigating electroporation of biological cells.

## ACKNOWLEDGMENT

This project has received funding from the European Union's Horizon 2020 research and innovation program under grant agreement No 737164. The authors would like to thank Creo Medical for their continued support in this project and for providing access to their equipment and expertise. Any IP that comes from this work is owned by Creo Medical Group PLC.

## REFERENCES

- "Google Scholar", Scholar.google.co.uk, 2019. [Online]. Available: https://scholar.google.co.uk/scholar?q=nanosecond+high+voltage+pul se+generator+electroporation&hl=en&as\_sdt=0%2C5&as\_ylo=2017 &as\_yhi=2020

- [2] "Google Ngram Viewer", Books.google.com, 2019. [Online]. Available:

https://books.google.com/ngrams/graph?content=electroporation&yea r\_start=1800&year\_end=2008&corpus=15&smoothing=50&share=& direct\_url=t1%3B%2Celectroporation%3B%2Cc0#t1%3B%2Celectro poration%3B%2Cc0

- [3] R. Sundararajan, Electroporation-based therapies for cancer from basics to clinical applications. Waltham, MA: Woodhead Pub, 2014.

- [4] Q. Yang, X. Zhou, Q.-g. Wang and M. Zhao, "Comparative analysis on the fast rising edge pulse source with two kinds of avalanche transistor," in Cross Strait Quad-Regional Radio Science and Wireless Technology Conference, Chengdu, 2013.

- [5] G. Yong-sheng et al., "High-speed, high-voltage pulse generation using avalanche transistor," Review of Scientific Instruments, vol. 87, no. 5, p. 054708, 2016.

- [6] J. Weaver, "Electroporation of cells and tissues", IEEE Transactions on Plasma Science, vol. 28, no. 1, pp. 24-33, 2000.

- [7] A. Pakhomov, Advanced electroporation techniques in biology and medicine, CRC Press, 2017.

- [8] W. Meiling and F. Stary, Nanosecond pulse techniques. New York: Gordon and Breach, 1970, p. 304.

- [9] W. Roehr, Switching transistor handbook. Motorola Inc., 1975.

- [10] C. Hancock, K. O'Grady and A. Owens, "Simple voltage generator for producing well-defined nanosecond pulses of amplitudes in excess of 1 kV", IEE Proceedings - Science, Measurement and Technology, vol. 144, no. 5, pp. 229-233, 1997.

- [11] M. Gao, Y. Xie and Y. Hu, "Parameter optimization for rise time of sub-nanosecond pulser based on avalanche transistors," 2017 IEEE 21st Workshop on Signal and Power Integrity (SPI), Baveno, 2017, pp. 1-3.

- [12] Diodes.com, 2019. [Online]. Available: https://www.diodes.com/assets/Datasheets/FMMT415.pdf.