# 22.8 GHz Substrate Integrated Waveguide Analog Frequency Divide-by-3 Circuit

A. Georgiadis, Senior Member, IEEE, A. Collado, Senior Member, IEEE, and K. Niotaki, Student Member, IEEE

*Abstract*— A 22.8 GHz analog frequency divide-by-3 circuit is presented based on an injection locked oscillator. Substrate integrated waveguide (SIW) technology is used to implement the input and output sections of the frequency divider circuit. The input SIW section at the gate of the active device permits the introduction of the injection signal at the third harmonic frequency of the oscillator, while the output section is designed to maximize the DC-RF conversion efficiency of the oscillator circuit. A prototype is fabricated presenting a measured DC-RF efficiency of 38.5% at 7.603 GHz output frequency with 3.7 dBm output power. An injection locking bandwidth of 301.4 MHz was obtained for a 1.5 dBm input injection signal at 22.8 GHz.

*Index Terms*— Substrate integrated waveguide (SIW), oscillator, injection locking, analog frequency divider, harmonic balance

## I. INTRODUCTION

**S** UBSTRATE integrated waveguides (SIW) and circuits (SIC) find good application in microwave and millimeter wave applications due to the fact that they combine attractive properties from both microstrip and waveguide technologies, such as ease of fabrication, high performance including good isolation and low losses, and heat handling capability [1]. As a result there are numerous implementations of passive circuits in SIW technology demonstrating its potential as an alternative to traditionally used microstrip or waveguide technologies. Furthermore, combining active devices with passive SIW structures or embedding them within the SIW itself has led to the development of active SIW circuits such as oscillators, mixers, amplifiers and active antennas [1].

Analog frequency dividers have advantages such as low dissipated power and high frequency of operation, while one of the challenges associated with their design is the limited operating input frequency range [2]-[8]. This paper presents an analog divide-by-3 frequency divider in SIW technology. The design is based on an injection locked oscillator with the input injection signal at 22.8 GHz. The circuit can be used as

part of the local oscillator frequency synthesizer circuitry of radar or communication transceivers operating at the 24 GHz Industrial, Scientific and Medical (ISM) frequency band.

The novelty of the design consists of implementing both the input and output sections of the divider in SIW technology and introducing an output section topology similar to the one used in switching amplifiers [9], oscillators [10], and multipliers [11] leading to an increased DC-RF efficiency. The use of a half-mode SIW as a high pass filter placed at the input section of an analog divider has been proposed in [8] taking advantage of the cutoff frequency of the SIW and thus minimizing the loading effect of the input to the divider at the fundamental frequency. In this work, the input section of the divider consists of two cascaded SIW sections, a first one used to set the oscillation frequency and a second one acting as a high pass filter isolating the high frequency input from loading the oscillator at the fundamental frequency. The output SIW section is designed to present a short at the second harmonic frequency at the output node of the active device of the divider. The use of SIW technology may provide a further advantage over microstrip technology in higher operating frequencies due to reduced losses [1]. A prototype was fabricated and measured presenting a 38.5% DC-RF efficiency at 3.7dBm output RF power, and a 301.4 MHz locking bandwidth for a 1.5dBm, 22.8GHz injection signal.

## II. SIW DIVIDER DESIGN

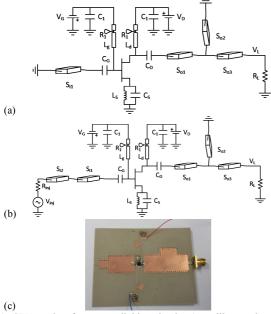

The analog divider circuit is based on a harmonically injection locked oscillator. The oscillator is designed using the NE3514S02 HEMT transistor with a shorted waveguide section S<sub>i1</sub> at its gate terminal and a parallel LC feedback at its source terminal (Fig. 1a). The oscillator output network consists of a SIW section Sol in series with a shunt SIW section So2 optimized to short the second harmonic at the device drain terminal and maximize the DC-RF efficiency. In a second step, the input section of the divider is formed by modifying the transistor gate circuit to include a 22.8 GHz input SIW section S<sub>i2</sub> (Fig. 1b). The high-pass nature of the SIW S<sub>i2</sub> allows one to minimize the effect of the input section on the oscillator performance while enabling the introduction of a harmonic injection signal. In a third and final step, the ideal waveguide components are substituted by SIW components optimized to match the ideal waveguide sections, using the commercial electromagnetic simulator Ansys HFSS (Fig. 1c).

Manuscript received May 15, 2014; manuscript revised November 17, 2014; manuscript accepted February 10, 2015. This work was supported by the Spanish Ministry of Economy and Competitiveness project TEC2012-39143, the Generalitat de Catalunya under grant 2014 SGR 1551 and the EU COST Action IC1301 Wireless Power Transmission for Sustainable Electronics.

A. Georgiadis, A. Collado and K. Niotaki are with Centre Tecnologic de Telecomunicacions de Catalunya (CTTC), Castelldefels 08860, Barcelona, Spain (e-mail: ageorgiadis@cttc.es, acollado@cttc.es, kniotaki@gmail.com).

The frequency of oscillation is set by the dimensions of the waveguide sections S<sub>i1</sub> and S<sub>o1</sub>, as well as the feedback parallel LC network at the source terminal of the transistor formed by L<sub>s</sub> and C<sub>s</sub>. The bias networks of the gate and drain terminals consist of  $3\lambda/2$  long microstrip lines and radial stubs designed at 7.9 GHz. DC-blocking capacitors C<sub>G</sub> and C<sub>D</sub> are included in order to isolate the bias current from flowing into the input and output waveguide sections. The circuit is designed to oscillate at 7.722 GHz for a drain bias  $V_D = 1.0$  V and gate bias  $V_G = -0.68$  V, corresponding to a drain current  $I_D$ = 8.18 mA. The waveguide section  $S_{o2}$  together with  $S_{o1}$  lead to the suppression of the second harmonic component at the drain terminal. The oscillating condition is optimized using harmonic balance simulation and its stability verified with transient analysis. In simulation, the oscillator dissipates 9.12 dBm and generates 6.12 dBm with an efficiency of 50.1 % at the above biasing conditions.

The circuit was fabricated on 30 mil thick Arlon A25N substrate using an LPKF Protomat C100/HF circuit board plotter using a 250 um drill bit. The via holes were metalized using LPKF Proconduct paste. The dielectric permittivity and loss tangent of the substrate were 3.38 and 0.0025 respectively. The final design layout parameters and circuit components are listed in Table I.

Fig. 1. SIW analog frequency divider circuit: a) oscillator schematic, b) divider schematic, c) photo of fabricated prototype.

| TABLE I                                                |                          |  |  |  |  |  |

|--------------------------------------------------------|--------------------------|--|--|--|--|--|

| CIRCUIT PARAMETERS AND COMPONENTS                      |                          |  |  |  |  |  |

| Parameter                                              | Value (*)                |  |  |  |  |  |

| L <sub>So1</sub> , L <sub>So2</sub> , L <sub>So3</sub> | 12.45 mm, 5 mm, 7.75 mm  |  |  |  |  |  |

| W <sub>So1</sub> , W <sub>So2</sub> , W <sub>So3</sub> | 13.5 mm                  |  |  |  |  |  |

| L <sub>Si1</sub> , L <sub>Si2</sub>                    | 19.2 mm, 6.5 mm          |  |  |  |  |  |

| $W_{Si1}$ , $W_{Si2}$                                  | 13 mm, 6.0 mm            |  |  |  |  |  |

| Cs                                                     | 0.25 pF AVX ACCU-P 0603  |  |  |  |  |  |

| $C_{D_i}C_G$                                           | 0.7 pF AVX ACCU-P 0603   |  |  |  |  |  |

| Lg, Ld, R1                                             | 15.7 mm, 15.7 mm, 5.3 mm |  |  |  |  |  |

| $C_1$                                                  | 1nF // 4.7 uF            |  |  |  |  |  |

| Ls                                                     | 0.4 nH (printed)         |  |  |  |  |  |

| Via diameter, spacing                                  | 0.8 mm, 1.6 mm           |  |  |  |  |  |

| HEMT                                                   | NE3514S02                |  |  |  |  |  |

(\*) SIW section dimensions are listed as via center to center distance.

#### III. MEASUREMENTS

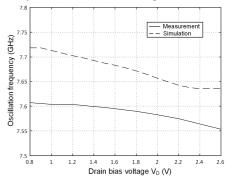

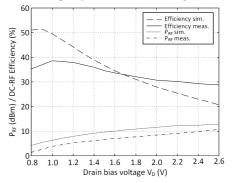

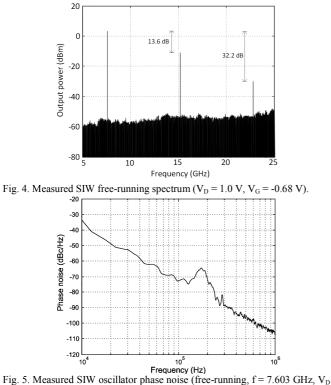

The fabricated prototype was first characterized as an oscillator, with its input port left open. Due to the high pass nature of the input SIW section the terminating impedance of the input port had a minimal effect at the oscillator performance. The measured circuit frequency, output and dissipated power and DC-RF conversion efficiency for a varying drain bias voltage and  $V_G = -0.68$  V are shown in Fig. 2, 3 and 4 respectively. Simulated results are included in the figures for comparison. The measured performance of the oscillator is 3.7 dBm output power at 7.603 GHz with 38.5 % DC-RF efficiency ( $V_D = 1.0$  V and  $V_G = -0.68$  V). The oscillator dissipated and output power are reduced compared to simulation which leads to a corresponding reduction in the obtained efficiency. The oscillator efficiency remains above 30% for a drain bias voltage tuned from 0.8 V - 2.2 V. The measured oscillator frequency is approximately 1.55% less than the value obtained in simulation. Variations are attributed to component yields and manufacturing tolerances.

Fig. 2. SIW oscillator frequency versus drain bias voltage ( $V_G = -0.68$  V).

Fig. 3. SIW oscillator output power ( $P_{RF}$ ) and DC-RF conversion efficiency versus drain bias voltage ( $V_G$  = -0.68 V).

The free-running oscillator phase noise was measured at 7.603 GHz and it is shown in Fig. 5. A phase noise value of -107.4 dBc/Hz at 1 MHz offset was obtained which corresponds to an oscillator figure of merit FoM [12] of 176.9 dB. The harmonic content of the oscillator spectrum is shown in Fig. 4. The 2<sup>nd</sup> and 3<sup>rd</sup> harmonic suppression is 13.6 dBc and 32.2 dBc respectively.

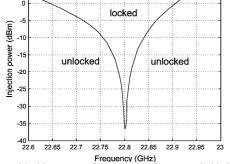

The analog divide-by-3 circuit performance was evaluated by injecting a 22.8 GHz signal at the input port of the prototype using a signal generator and an Anritsu Universal Test Fixture (Model 3680V), and varying its frequency and power to determine the locking range. The results are shown in Fig. 6. It is shown that for 1.5 dBm injection signal power a locking bandwidth of 301.4 MHz is obtained, which covers the 250 MHz frequency span of the 24 GHz ISM frequency band.

Fig. 5. Measured SIW oscillator phase noise (free-running, f = 7.603 GHz,  $V_D = 1.0$  V,  $V_G = -0.68$  V).

Fig. 6. Measured locking range of SIW analog frequency divide-by-3 circuit ( $V_D = 1.0 \text{ V}, V_G = -0.68 \text{ V}$ ).

The proposed divider is compared with other divide-by-3 circuits in Table II. It presents an increased DC-RF conversion efficiency and it combines frequency conversion and sufficient locking bandwidth for the application under consideration, while it requires an injection power that is lower than its output RF power. An increased locking bandwidth can be achieved by introducing frequency tuning or switching capability to the divider through the use of varactor diodes, PIN diodes or MEMS.

### IV. CONCLUSION

A 22.8 GHz analog divide-by-3 circuit is presented. The circuit is based on an injection locked oscillator topology, implemented in low cost SIW technology and optimized for a high DC-RF conversion efficiency of 38.5% and 3.7 dBm output power at 7.603 GHz. An injection bandwidth of 301.4 MHz at 22.8 GHz for an input power of 1.5 dBm is obtained which is sufficient for the circuit to be used as part of a local oscillator synthesizer circuit for 24 GHz ISM band applications.

| TABLE II                                        |  |  |  |  |

|-------------------------------------------------|--|--|--|--|

| ANALOG FREQUENCY DIVIDER PERFORMANCE COMPARISON |  |  |  |  |

| Ref. | Div.<br>R | Input Freq.<br>(GHz) | P <sub>RF</sub><br>(dBm) | P <sub>DC</sub> (mW)<br>(Eff. (%)) | Lock. Range<br>(MHz)/(%)<br>(P <sub>inj</sub> (dBm)) |

|------|-----------|----------------------|--------------------------|------------------------------------|------------------------------------------------------|

| [2]  | 3         | 11.77 - 16.64 (*)    | -7.25                    | (**) 4.2 (4.5)                     | 425/3.0 (0)                                          |

| [3]  | 3         | 23.17-27.49 (*)      | -                        | (**) 4.28                          | 1000/3.9 (4)                                         |

| [4]  | 3         | 14.04-15.48 (*)      | -                        | 9.02                               | 550/3.7 (0)                                          |

| [5]  | 3         | 23.4                 | -10                      | 17.82 (0.56)                       | 3200/13.7 (0)                                        |

| [6]  | 3         | 21.56-23.63 (*)      | -4.96                    | (**) 1.25 (25.5)                   | 250/1.1 (0)                                          |

| [7]  | 3         | 22.3-26.3 (*)        | -                        | 1.7                                | 100/0.42 (-12)                                       |

| [7]  | 3         | 22.3-26.3 (*)        | -                        | 7                                  | 1300/5.42 (2)                                        |

| [8]  | 9         | 27                   | -0.9                     | 12 (6.8)                           | 180/0.7 (20)                                         |

| This | 3         | 22.8                 | 3.7                      | 6.09 (38.5)                        | 301.4/1.3 (1.5)                                      |

| work |           |                      |                          |                                    |                                                      |

(\*) Varactor tuning. (\*\*) Not including buffer power consumption.

#### REFERENCES

- M. Bozzi, A. Georgiadis, K. Wu, "Review of substrate-integrated waveguide circuits and antennas," IET Microwaves, Antennas & Propagation, vol. 5, no. 8, pp. 909-920, June 2011.

- [2] J.-W. Wu, C.-C. Chen, H.-W. Kao, J.-K. Chen, M.-C. Tu, "Divide-by-Three Injection-Locked Frequency Divider Combined With Divide-by-Two Locking," IEEE Microwave and Wireless Components Letters, vol. 23, no. 11, pp. 590-592, Nov. 2013.

- [3] P.-K. Tsai, C.-Y. Liu, T.-H. Huang, and J.-W.Wu, "K-band, low-power CMOS injection-locked divide-by-three circuit using shunt-peaking and current-bleeding techniques," *Microw. Optical Tech. Lett*, vol. 54, no. 3, pp. 577–579, Mar. 2012.

- [4] S.-L. Jang, J.-C. Luo, C.-W. Chang, C.-F. Lee, J.-F. Huang, "LC-Tank Colpitts Injection-Locked Frequency Divider With Even and Odd Modulo," IEEE Microwave and Wireless Components Letters, vol. 19, no. 2, pp. 113-115, Feb. 2009.

- [5] Y.-T. Chen, M.-W. Li, H.-C. Kuo, T.-H. Huang, H.-R. Chuang, "Low-Voltage K-Band Divide-by-3 Injection-Locked Frequency Divider With Floating-Source Differential Injector," IEEE Transactions on Microwave Theory and Techniques, vol. 60, no. 1, pp. 60-67, Jan. 2012.

- [6] S.L. Jang, C.W. Chang, W.C. Cheng, C.F. Lee, M.H. Juang, "Lowpower divide-by-3 injection-locked frequency dividers implemented with injection transformers," IET Electronics Letters, vol. 45, no. 5, pp. 240-241, Feb. 2009.

- [7] S. Rong, H.C. Luong, "A 1V 1.7mW 25GHz transformer-feedback divide-by-3 frequency divider with quadrature outputs," in Proc. 2007 IEEE Asian Solid-State Circuits Conference, ASSCC '07, pp. 328-331, 12-14 Nov. 2007.

- [8] J.-L. Li, S.-W. Qu, Q. Xue, "A Ka-band frequency divider with high division ratio and low power consumption," in Proc. 2008 Asia-Pacific Microwave Conference (APMC), pp. 1-5, 16-20 Dec. 2008.

- [9] H.L. Krauss, C.W. Bostian, F.H. Raab, Solid State Radio Engineering, Ch. 7, New York: John Wiley and Sons, 1980.

- [10] E.W. Bryerton, W.A. Shiroma, and Z.B. Popovic, "A 5-GHz highefficiency class-E oscillator," IEEE Microwave and Guided Wave Letters, vol. 6, no. 5, pp. 441-443, Dec. 1996.

- [11] M. D. Weiss, Z. Popovic, "An X/K-band Class-E High-Efficiency Frequency Doubler," in Proc. 31st European Microwave Conference, pp. 1-4, 24-26 Sep. 2001.

- [12] P. Kinget, "Integrated GHz voltage controlled oscillators," in Anemualog Circuit Design: (X)DSL and other Communication Systems; RF MOST Models; Integrated Filters and Oscillators, W. Sansen, J. Huijsing, and R. van de Plassche, Eds. Boston: Kluwer, 1999, pp. 353-381.