Ferroelectric-Semiconductor capacitors on germanium.

C. Zacharaki<sup>1,2,\*</sup>, P. Tsipas<sup>1</sup>, S. Chaitoglou<sup>1</sup>, E. K. Evangelou<sup>3</sup>, C. M. Istrate<sup>4</sup>, L. Pintilie<sup>4</sup>, A. Dimoulas<sup>1</sup>

<sup>1</sup>National Centre for Scientific Research "Demokritos", 15310, Athens, Greece <sup>2</sup>Department of Physics, National and Kapodistrian University of Athens, 15772, Athens, Greece

<sup>3</sup>Department of Physics, University of Ioannina, 45110, Ioannina, Greece <sup>4</sup>National Institute for Materials Physics, 077125, Bucharest-Magurele, Romania \*Corresponding author: <u>c.zacharaki@inn.demokritos.gr</u>

## ABSTRACT

Germanium Metal-Ferroelectric-Semiconductor (MFS) capacitors based on ferroelectric Hf<sub>1</sub>.  $_x$ Zr<sub>x</sub>O<sub>2</sub> (HZO) with clean, oxide free Ge/HZO interfaces emerge as an interesting layer structure for the fabrication of FeFET non-volatile memory devices. It is shown that, at low temperature (<160 K), a semiconductor depletion forms in Ge near the interface resulting in an increase of coercive voltage by about 2 V, accompanied by a distortion of the ferroelectric hysteresis with subloop asymmetric behavior, which becomes more severe at higher frequencies of measurement. At higher temperatures, the Ge surface near the ferroelectric is easily inverted due to low energy gap of Ge, providing sufficient screening of the polarization charge by minority free carriers, in which case, nearly ideal, symmetric hysteresis curves are recovered. The depolarization field is experimentally extracted from the coercive voltage and the capacitance measurements and is found to be ~ 2.2 MV/cm in the low temperature range, comparable to the coercive field, then rapidly decreasing at higher temperatures and effectively diminishing at room temperature. This makes Ge MFS good candidates for FeFETs for low voltage nonvolatile memory with improved reliability.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

ublishing

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

Metal-Ferroelectric-Metal capacitors made of Si-compatible  $Hf_{1-x}Zr_xO_2$  with x~0.5 (HZO) ferroelectric (FE) have been extensively studied<sup>1-5</sup> for low power 1T-1C non-volatile embedded memories integrated in the back-end-of-line (BEOL) of CMOS<sup>6</sup>. A different device layer structure, namely Metal-Ferroelectric-Semiconductor (MFS) is the main building block of 1T ferroelectric field effect transistor (FeFET) non-volatile memories<sup>7</sup> which have potential advantages in terms of scaling, non-destructive reading and front-end-of-line (FEOL) integration with CMOS. Moreover, they can be used to realize artificial ferroelectric integrate-and-fire neurons<sup>8</sup> and analog synapses<sup>9, 10</sup> for neuromorphic computing<sup>11</sup>. Si MF(I)S draw a lot of attention but the presence of Si bottom electrode in direct contact with the HZO produces interfacial SiOx or Hf(Zr) silicate insulating layers which cause reliability problems for FeFETs<sup>12</sup>. Depolarization fields in particular can severely affect the hysteresis loop<sup>11, 12</sup> at room temperature (RT) by reducing the attainable switchable polarization as well as the memory window, thus directly impacting memory performance.

FeFETs on technologically important Ge<sup>13</sup> is an interesting alternative device that has already been successfully used for the fabrication of non-volatile analog memristive synapses functioning as accelerator for on-line learning in neuromorphic circuits<sup>14</sup>. Moreover, negative capacitance FETs with subthermionic steep slopes have been demonstrated in Ge/HZO FETs<sup>15</sup><sup>17</sup> suitable for low power/high performance applications.

Germanium MFS and FeFETs could help overcome some of the shortcomings of Si FeFETs. Notably, Ge/HZO interfaces are reported to be sharp and clean<sup>18-20</sup>, free of interfacial oxides, which could mitigate some of the reliability issues. Despite the absence of an interfacial insulating layer, when the MFS is biased in depletion, the screening of polarization charge weakens, potentially creating a depolarization field in the ferroelectric which could adversely impact retention and imprint of memory states. This has motivated us to systematically investigate, as a function of temperature, the build-up of a depolarization field originating from depletion in Ge at low temperatures (<160 K) creates a strong depolarization field which

2

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

severely distorts the hysteresis characteristics. However, at higher temperatures and especially at RT, due to its low energy gap ( $E_g$ ), Ge has high minority carrier population, sufficient to screen the polarization charges in Ge MFS, essentially diminishing the depolarization field. As a result, nearly ideal, symmetric polarization curves are obtained<sup>20-24</sup>.

TiN/HZO/Ge (100) MFS device layer structures were produced by plasma assisted atomic oxygen deposition in a molecular beam epitaxy chamber as described elsewhere (Ref [20]). In this work, three different samples are studied: a 12-nm-thick HZO film on a p-Ge substrate with resistivity  $\rho$ =(0.03-0.07)  $\Omega$ ·cm, a 13-nm-thick HZO on a highly doped n<sup>+</sup>-Ge (0.004-0.006  $\Omega$ ·cm) and a 13-nm-thick HZO on a lightly doped n-Ge (0.34-0.35  $\Omega$ ·cm), all with Zr composition x~ 0.6.

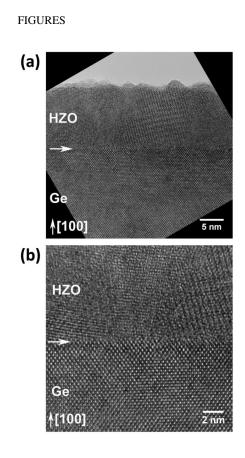

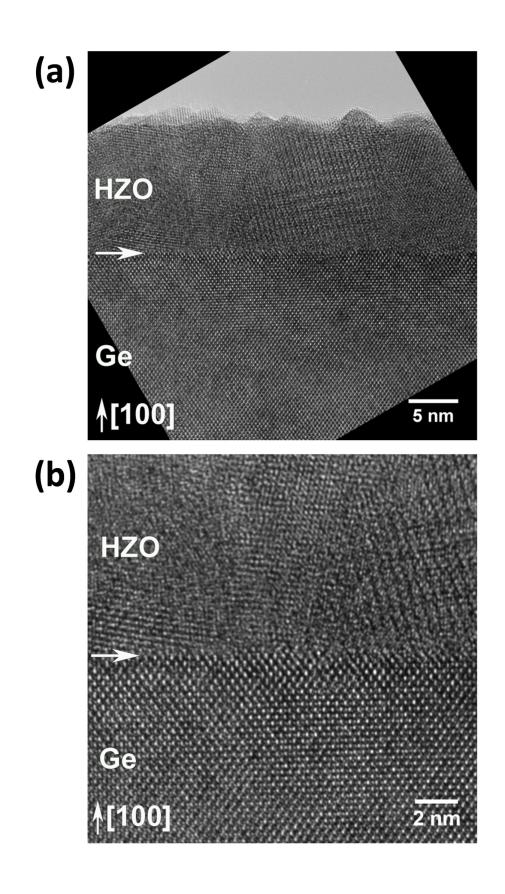

As in our previous work<sup>20</sup>, HZO is polycrystalline with grain size 15- 20 nm, comparable to the thickness as seen in Fig. 1(a). The HZO/Ge interface is crystalline and clean (Fig. 1(b)), free of interfacial oxide or germanate layers as expected<sup>18-20</sup>.

Polarization (P) and displacement current (I) of the ferroelectric capacitors were measured using an aixAcct Systems TF Analyzer 1000. The capacitors showed robust and symmetric pristine hysteresis curves at RT with no wake-up effects and good electrical endurance of 10<sup>5</sup> cycles similar to those previously reported<sup>20</sup>. Temperature measurements from RT to 77 K were performed using a micromanipulator in high vacuum conditions.

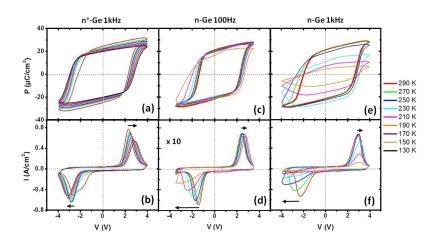

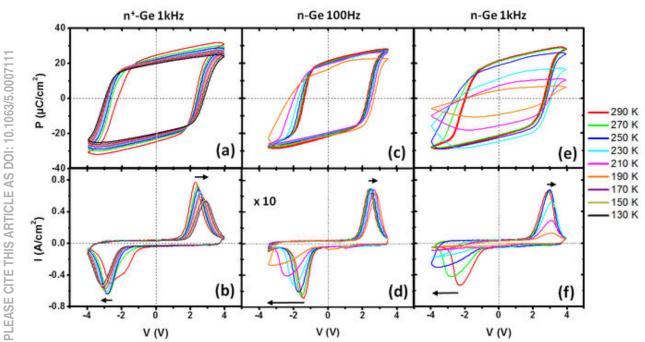

Temperature and frequency data are presented in figures 2 and 3. In the case of MFS on n<sup>+</sup>-Ge substrate (Fig. 2(a)-(b)), as temperature decreases, a slight shift of coercive voltage V<sub>c</sub> to higher values is observed ( $\Delta V$ ~0.6V), which is nearly the same for both V<sub>c</sub><sup>+</sup> and V<sub>c</sub><sup>-</sup>. This weak variation is attributed to a temperature dependence of the coercive field E<sub>c</sub> as predicted by Landau-Ginzburg mean-field theory<sup>25</sup> and previously reported<sup>26</sup>. For the MFS on n-Ge substrate (Fig. 2(c)-(f)), V<sub>c</sub><sup>+</sup> is slightly increased (only by ~ 0.4 V), whereas V<sub>c</sub><sup>-</sup> shows a significant shift of about 2 V to higher negative values as the temperature is lowered. The polarization loop gradually becomes non-ideal and asymmetric with reduced P<sub>r</sub>, similar to the one observed in Si

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

based MF(I)S capacitor<sup>11, 12</sup>. It is worth noting that at higher frequencies (Fig. 2(c)-(f)), the degradation of hysteresis loop is more pronounced and the  $V_c$  shift is larger as the temperature is reduced (see detailed discussion later).

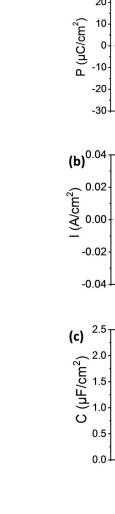

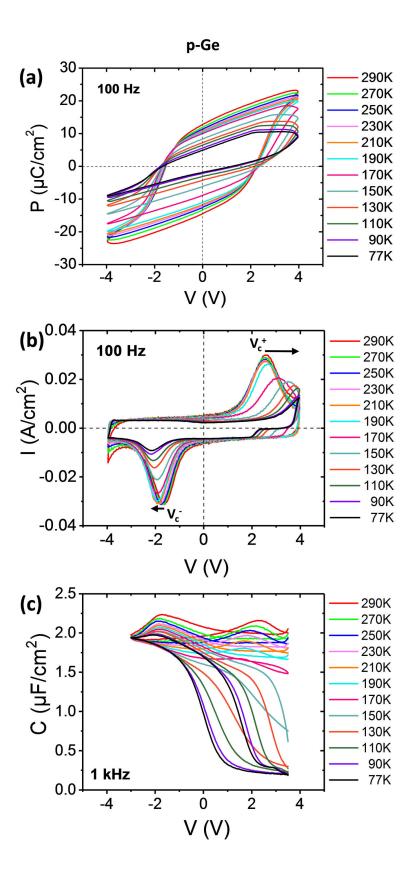

The opposite behavior is observed for the capacitor on p-Ge substrate (Fig. 3 (a)-(b)) where  $V_c^+$  shows considerable shift of about 1.4 V as the temperature is lowered, while  $V_c^-$  remains nearly unchanged (maximum shift of ~0.5 V). For an in-depth investigation, high frequency capacitance-voltage (C-V) measurements were performed for p-Ge/HZO/TiN MFS capacitor (Fig. 3 (c)). At RT the characteristic "butterfly" ferroelectric peak configuration appears, indicating that the device essentially behaves like an MFM capacitor. With decreasing temperature, the gradual transition to a typical p-type MIS behavior is clearly seen which can be correlated with the evolution of the polarization curve.

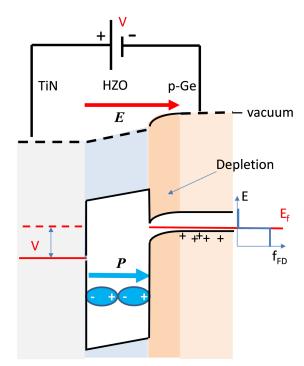

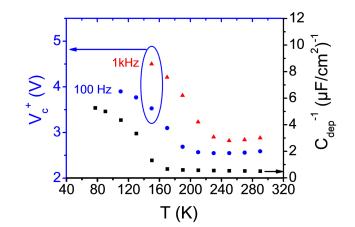

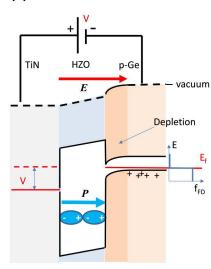

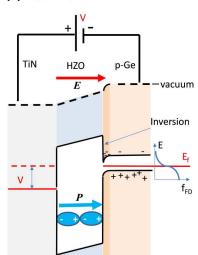

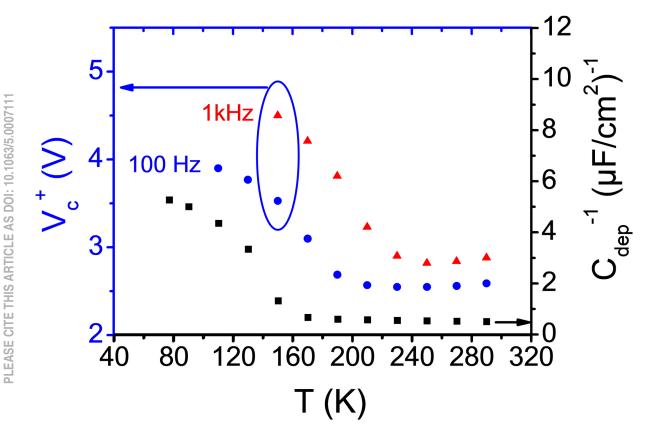

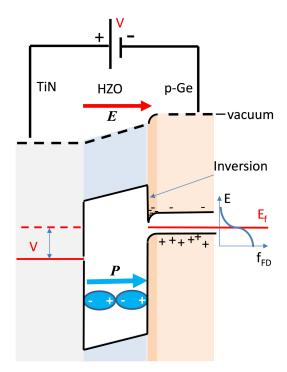

Figure 4 presents the comparison between inverse total capacitance measured at depletion (+ 3.5 V) C<sub>dep</sub><sup>-1</sup> and V<sub>c</sub><sup>+</sup>, as obtained by displacement current measurements at two different frequencies (1 kHz and 100 Hz), at each temperature. Notably, both quantities follow the same trend, which indicates that the origin of the significant  $V_c^+$  increase is the creation of a depletion region in the Ge semiconductor at low temperatures. More specifically, when positive voltage is applied on TiN top electrode at RT, the conduction band is populated, as dictated by the Fermi Dirac distribution, by a large number of electrons (minority carriers), due to low Eg of Ge, resulting in surface inversion (Fig. 5 (a)). Therefore, the free negative charge in inversion screens efficiently the positive polarization charge in such a way that the Ge bottom electrode behaves like a metal, yielding symmetric nearly ideal hysteresis as in MFM capacitors. At low temperatures, the Fermi Dirac distribution narrows so the population of the conduction band by minority carriers is diminished, while majority carriers are repelled from the interface (Fig. 5b). Therefore, the region near the interface is depleted from free carriers so the electric field penetrates the semiconductor depletion region causing an additional voltage drop and an associated depolarization field in the ferroelectric. This voltage drop explains the larger Vc+ required to attain the Ec in the HZO ferroelectric. In contrast, in accumulation at negative bias,

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

the majority carrier concentration (holes) is not affected at lower temperatures, so  $V_c^-$  remains nearly the same. Similar description holds for n-type substrates where the role of  $V_c^+$  and  $V_c^-$  is interchanged.

As already mentioned above, the effect of the depletion at low temperatures is more pronounced at higher frequencies of measurement. This is understood as follows: the few minority carriers do not respond fast enough to the electric field since electron-hole generation by interband transitions, typically mediated by mid-gap states near the interface, is a slow process. As a result, the inversion layer does not easily form at high frequencies, leaving the interface depleted from free carriers. The frequency effect could be mitigated or avoided by using highly doped substrates which show metallic behavior so the hysteresis remains near ideal at high frequency even at low temperatures (see n<sup>+</sup> Ge MFS in Fig. 2a).

For a quantitative analysis, the variation of  $V_c$  with the inverse total capacitance C per unit area at depletion is calculated as follows: The free charge per unit area  $Q_c$  stored in the capacitor can be expressed as  $Q_c=CV_c$ . On the other hand, from Gauss's law,  $Q_c=D=\epsilon_{FE}E_{FE}$ , where D is the electric displacement,  $\epsilon_{FE}$  is the dielectric constant and  $E_{FE}=E_c+E_{dep}$  is the total electric field in the ferroelectric expressed as the sum of the  $E_c$  and the depolarization field  $E_{dep}$ . Then,

$$V_{c} = \varepsilon_{FE} C^{-1} (E_{c} + E_{dep}) \qquad (1)$$

which explains the similar behavior exhibited by  $V_{\rm c}$  and  $C^{\text{-1}}$  in Fig. 4 as a function of temperature.

Equation (1) can be used to extract  $E_{dep}$  as a function of temperature from experimental data of  $V_c$  and  $C^{-1}$  as displayed in Fig. 4. This is particularly useful given that an estimate of  $E_{dep}$  is not easy to make. For example, the typically used expression  $E_{dep}$ = -P/ $\epsilon_{FE}$ (1+C<sub>s</sub>/C<sub>FE</sub>)<sup>27</sup> for the depolarization field requires the knowledge of the semiconductor capacitance C<sub>s</sub> which is not easy to extract experimentally (P is the remanent polarization and C<sub>FE</sub> is the ferroelectric capacitance).

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

This is the author's pee

ublishing

In order to extract  $E_{dep}$  from eqn (1),  $\varepsilon_{FE}=\varepsilon_0\cdot\varepsilon_r$  is estimated from the accumulation capacitance  $C_{acc}=1.94 \ \mu\text{F/cm}^2$  at -3 V (Fig. 3 (c)) and the ferroelectric thickness  $d_{FE}=12 \text{ nm}$  using  $\varepsilon_{FE}=C_{acc}\cdot d_{FE}=23.3\cdot10^{-11}$  F/m. This calculation yields a relative dielectric constant  $\varepsilon_r=26.3$ , which is in fair agreement with reported<sup>3</sup> values of ~27 for the orthorhombic crystalline phase of HZO. Moreover,  $E_c$  in eqn (1) is obtained at each temperature from  $E_c=V_c^-/d_{FE}$  by measuring  $V_c^-$  in accumulation (negative bias).

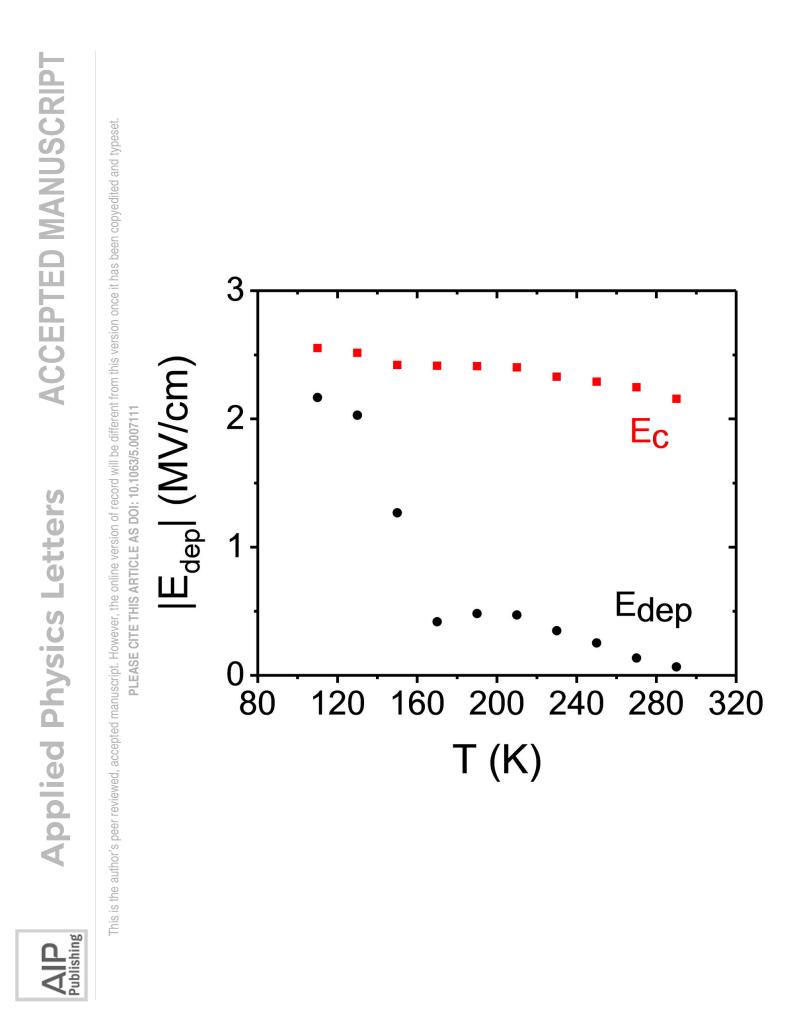

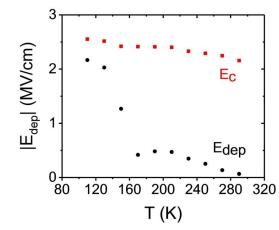

The absolute value of  $E_{dep}$  as a function of temperature is plotted in Fig. 6 along with  $E_c$  for comparison.  $E_c$  varies weakly and increases roughly linearly with decreasing temperature following the linear temperature dependence previously predicted<sup>28</sup> on the basis of Ginzbourg-Landau theory<sup>25</sup>. On the other hand,  $|E_{dep}|$  is nearly zero at RT which is expected considering the efficient screening of polarization charges and increases slightly as the temperature drops to about 160 K. At lower temperatures,  $|E_{dep}|$  increases sharply, essentially following the rapid increase of C<sup>-1</sup> in Fig. 4 which signifies the formation of a depletion region. At the lowest temperature range,  $|E_{dep}|$  reaches high values ~2.2 MV/cm which is comparable to the  $E_c$  value of 2.55 MV/cm (Fig. 6).

It should be noted that the formation of an inversion layer (Fig. 5a) may not be a roadblock for FeFET operation since the modulation from inversion to depletion can be controlled by the gate bias turning the transition from ON to OFF state as already demonstrated in the literature<sup>15-17</sup>. Any non-idealities such as low  $I_{ON}/I_{OFF}$  ratio may not affect the FeFET operation since the memory window depends mainly on the threshold voltage shift controlled by the ferroelectric state at the gate.

Although the present analysis has been performed based on Ge MFS which serves here as a model case study, the expression (1) is of general validity and holds for other semiconductor devices including Si MF(I)S, albeit with an additional complication in the analysis due to the presence of the insulating (I) layer. However, in the case of Si MF(I)S, due to the larger  $E_g$  of Si (~ 1.1 eV), a depletion layer and an associated finite  $E_{dep}$  are expected at RT, adversely affecting

the P-E characteristics which show subloop behavior and increased operation voltages, as previously reported<sup>11, 12, 24</sup>. Therefore, compared to Si devices, Ge MFS offer advantages: The absence of an insulating interfacial layer and the low  $E_g$  of Ge which prevents depletion, make depolarization fields insignificant at RT. This allows a symmetric and robust P-E hysteresis loop of Ge MFS at RT with effectively zero  $E_{dep}$ , which is essential for FeFET performance at low voltages with improved reliability.

Acknowledgements: This work is supported by the H2020 framework program of the European Commission, contract No 780302-3 $\epsilon$ FERRO.

Data Availability Statement: The data that support the findings of this study are available from the corresponding author upon reasonable request.

7

### REFERENCES

- T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, *Appl. Phys. Lett.* 99, 102903 (2011).

- J. Müller, P. Polakowski, S. Mueller, and T. Mikolajick, *ECS J. Sol. St. Sci. Technol.* 4, N30 (2015).

- M. H. Park, Y. H. Lee, H. J. Kim, Y. J. Kim, T. Moon, K. D. Kim, J. Müller, A. Kersch, U. Schroeder, T. Mikolajick, and C. S. Hwang, *Adv. Mat.* 27, 1811 (2015).

- M. H. Park, Y. H. Lee, T. Mikolajick, U. Schroeder, and C. S. Hwang, *MRS Commun.* 8, 795 (2018).

- 5) S. J. Kim, J. Mohan, S. R. Summerfelt, and J. Kim, JOM 71, 246 (2018).

- T. Francois, L. Grenouillet, J. Coignus, P. Blaise, C. Carabasse, N. Vaxelaire, T. Magis,

F. Aussenac, V. Loup, C. Pellissier, S. Slesazeck, V. Havel, C. Richter, A. Makosiej, B. Giraud, E. Breyer, M. Materano, P. Chiquet, M. Bocquet, E. Nowak, U. Schroeder, and

F. Gaillard, IEEE *International Electron Devices Meeting* (2019), p. 15.7.1.

- J. Mueller, S. Slesazeck, and T. Mikolajick, "Ferroelectricity in Doped Hafnium Oxide: Materials, Properties, and Devices", 1st ed., Elsevier, Duxford, UK 2019 Chap. 10.4.

- H. Mulaosmanovic, J. Ocker, S. Müller, M. Noack, J. Müller, P. Polakowski, T. Mikolajick, and S. Slesazeck, in *Symposium on VLSI Technology* (2017), p. T176.

- 9) M. Jerry, P. Y. Chen, J. Zhang, P. Sharma, K. Ni, S. Yu, and S. Datta, IEEE International Electron Devices Meeting (2017), p. 6.2.1.

- 10) M. K. Kim, and J. S. Lee, Nano Lett. 19, 2044 (2019).

- 11) S. Oh, H. Hwang, and I. K. Yoo, APL Mater. 7, 091109 (2019).

- 12) S. Oh, J. Song, I. K. Yoo, and H. Hwang, IEEE Electron Device Lett. 40, 1092 (2019).

- IEEE International roadmap for devices and Systems (IRDS) 2017 Edition, retrieved from https://irds.ieee.org/roadmap-2017.

- 14) W. Chung, M. Si, and P. D. Ye, IEEE International Electron Devices Meeting (2018), p. 15.2.1.

**Applied Physics Letters**

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

ublishing

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

- 15) W. Chung, M. Si, P. R. Shrestha, J. P. Campbell, K. P. Cheung, and P. D. Ye, in *Symposium on VLSI Technology* (2018), p. 89.

- 16) J. Zhou, G. Han, Q. Li, Y. Peng, X. Lu, C. Zhang, J. Zhang, Q.-Q. Sun, D. W. Zhang, and Y. Hao, IEEE *International Electron Devices Meeting* (2016), p. 310.

- 17) C.-J. Su, Y.-T. Tang, Y.-C. Tsou, P.-J. Sung, F.-J. Hou, C.-J. Wang, S.-T. Chung, C.-Y. Hsieh, Y.-S. Yeh, F.-K. Hsueh, K.-H. Kao, S.-S. Chuang, C.-T. Wu, T.-Y. You, Y.-L. Jian, T.-H. Chou, Y.-L. Shen, B.-Y. Chen, G.-L. Luo, T.-C. Hong, K.-P. Huang, M.-C. Chen, Y.-J. Lee, T.-S. Chao, T.-Y. Tseng, W.-F. Wu, G.-W. Huang, J.-M. Shieh, W.-K. Yeh, and Y.-H. Wang, in *Symposium on VLSI Technology* (2017), p. T152.

- A. Dimoulas, G. Mavrou, G. Vellianitis, E. Evangelou, and N. Boukos, *Appl. Phys. Lett.* 86, 032908 (2005).

- 19) A. Dimoulas, D. P. Brunco, S. Ferrari, J. W. Seo, Y. Panayiotatos, A. Sotiropoulos, T. Conard, M. Caymax, S. Spiga, M. Fanciulli, C. Dieker, E. K. Evangelou, S. Galata, M. Houssa, and M. M. Heyns, *Thin Solid Films* **515**, 6337 (2007).

- 20) C. Zacharaki, P. Tsipas, S. Chaitoglou, S. Fragkos, M. Axiotis, A. Lagoyiannis, R. Negrea, L. Pintilie, and A. Dimoulas, *Appl. Phys. Lett.* **114**, 112901 (2019).

- 21) X. Tian, L. Xu, S. Shibayama, T. Nishimura, T. Yajima, S. Migita, and A. Toriumi, IEEE International Electron Devices Meeting (2017), p. 816.

- 22) X. Tian, S. Shibayama, T. Nishimura, T. Yajima, S. Migita, and A. Toriumi, *Appl. Phys. Lett.* **112**, 102902 (2018).

- 23) Y. Goh, and S. Jeon, Nanotechnology 29, 335201 (2018).

- 24) P. D. Lomenzo, Q. Takmeel, C. M. Fancher, C. Zhou, N. G. Rudawski, S. Moghaddam,J. L. Jones, and T. Nishida, *IEEE Electron Device Lett.* 36, 766 (2015).

- 25) V. L. Ginzburg, J. Phys. X, 107(1946).

- 26) D. Zhou, Y. Guan, M. M. Vopson, J. Xu, H. Liang, F. Cao, X. Dong, J. Mueller, T. Schenk, and U. Schroeder, *Acta Materialia* 99, 240 (2015).

- 27) T. P. Ma, and J.-P. Han, IEEE Electron Device Lett. 23, 386 (2002).

**Applied Physics Letters**

(2010).

28) M. Vopsaroiu, J. Blackburn, M.G. Cain, and P.M. Weaver, Phys. Rev. B 82, 024109

## FIGURE CAPTIONS:

**Figure 1:** HRTEM cross-sectional images of HZO on p-Ge (100) substrate. (a) Microstructure of 13 nm ferroelectric HZO layer and (b) the sharp HZO/Ge interface, free of interfacial amorphous oxide layers.

**Figure 2:** Polarization and displacement current vs voltage measurements for MFS capacitors on (a)-(b) highly doped n<sup>+</sup>-Ge and low doped n-Ge substrate at (c)-(d) 100 Hz and (e)-(f) 1 kHz. The arrows show the shift in the coercive voltages  $V_c^+$  and  $V_c^-$  in accumulation and depletion/inversion, respectively.

Figure 3: (a) Polarization, (b) displacement current (at 100Hz) and (c) capacitance vs voltage measurements (1 kHz) at different temperatures for MFS capacitor on p-Ge substrate. The arrows in (b) show the shift of the coercive voltages  $V_c^+$  and  $V_c^-$  in depletion/inversion and accumulation, respectively.

Figure 4: Temperature dependence of positive coercive voltage  $V_c^+$  at 100 Hz (circles) and 1 kHz (triangles) and inverse capacitance  $C_{dep}^{-1}$  (squares) measured at +3.5 V in depletion for p-Ge MFS.

**Figure 5**: Schematic energy band diagrams of TiN/HZO/p-Ge device layer structure corresponding to high frequency measurements at positive applied bias V at (a) high temperature (inversion), (b) low temperature (depletion). *E* denotes the electric field vector which is largely confined in the HZO ferroelectric except in (b) where it penetrates the Ge depletion region giving rise to an additional voltage drop. *P* denotes the polarization vector in the ferroelectric.  $f_{FD}$  vs E is a schematic illustration of the Fermi Dirac distribution.

Figure 6: Temperature dependence of experimentally determined absolute value of the depolarization field  $E_{dep}$  and coercive field  $E_e$  for p-Ge MFS.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

FIGURE 1

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

FIGURE 2

p-Ge

0 V (V)

2

v,+

ż

4

4

290K 270K 250K

230K

210K 190K

170K 150K

130K 110K 90K 77K

290K 270K 250K 230K 210K 190K 150K 130K 130K 130K 090K 77K

290K 270K 250K 230K 210K 190K 170K 150K 130K

-110K 90K 77K

30 (a)

20

10

0

-10

-20 -30 100 Hz

-4

100 Hz

-2

v

ò V (V)

0 V (V)

2

4

-2

-4

1 kHz

-4

-2

0.5

0.0

FIGURE 4

(b) Low temperature

FIGURE 5

(a) High temperature

16

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

# PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0007111

# (a) High temperature

# (b) Low temperature