# **COMBINED SKEWED CMOS RING OSCILLATOR**

Sadegh Biabanifard<sup>1</sup>, S. Mehdi Hosseini Largani<sup>2</sup> and Shahrouz Asadi<sup>3</sup>

<sup>1,2</sup>Microelectronic Lab, Shahid Beheshti University, G. C, Tehran <sup>3</sup>Faculty of Electrical Engineering, Shahid Beheshti University, G.C, Tehran

#### ABSTRACT

A combined skewed ring oscillator by different type of delay stages is presented. This paper aims to drive a high stable and relatively high frequency but still use a full transistor circuit for ring oscillator with combined delay stages and skewed connections. First we propose two types of common inverters then calculate their delay time and analysis their dependence of delay time to variation of power supply voltage. The simulation results verify that delay time of these two CMOS inverters show opposite behaviour versus power supply noise. Also in order to increase oscillation frequency we have used the negative skewed delay connections. The simulation results using HSPICE for 0.18 µm CMOS shows a good agreement with analysis results. In addition in this paper the mathematical justification for improved functioning of this combined skewed ring oscillator has been proved. This justification shows appropriate agreement with the simulation results. From mathematical point of view the proposed ring oscillator has better frequency stability in comparison with other types of ring oscillators. In fact, the oscillation frequency sensitivity to supply voltage noise is reduced considerably.

#### **KEYWORDS**

CMOS, ring oscillator, frequency stability, delay time

#### **1. INTRODUCTION**

Oscillators are the essential part of any digital and analog systems [1, 11]. And ring oscillator is a circuit usually uses transistors without using passive elements [4]. The main reason of the tendency to design full transistor CMOS circuits is the ability of easy integration with absence of passive elements which reduces the die area [12-20]. The most significant feature of a ring oscillator is lower cost due to lower die area and design simplicity [1, 4, 5]. However the highest possible oscillation frequency is lower for ring oscillators than LC oscillator, negative skewed delay connections can improve the speed of ring type oscillators.

Several designs for ring oscillator have been reported in literature. In [1], a frequency stable oscillator is designed based on the opposite direction of delay time changing, which increase frequency stability but oscillation frequency reduce due to using current starved inverter. In [6] a method to enhance frequency operation of ring oscillators by negative skewed delay connections presented. Overall, most of the reported ring oscillators cannot improve both frequency stability and oscillation frequency. In this paper a novel design as combined skewed ring oscillator is presented to improve frequency stability an oscillation frequency simultaneously.

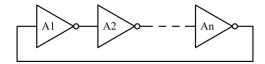

Usually a single ended ring oscillator can be implement using odd number of delay stages (Fig.1). Considering oscillation criterion the loop gain must be equal or bigger than unity and also the

loop gain must be negative which odd number of inverters can satisfy these conditions. By assuming that all stages are similar we can extract oscillation frequency from (1).

$$A_{1}(j\omega) = A_{2}(j\omega) = \dots = A_{N}(j\omega) = \frac{-g_{m}R}{1+j\omega RC}$$

$$|A_{1}(j\omega)A_{2}(j\omega)\dots A_{N}(j\omega)| = 1 \qquad (1)$$

$$\angle A_{1}(j\omega) = \theta = \tan^{-1}(\omega RC) = \frac{2K\pi}{RC}$$

Fig.1. A typical ring oscillator by odd number of inverters [2]

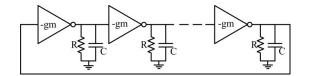

Fig.2. general linear model of a ring oscillator [1]

The above equation can leads us to estimate oscillation frequency in initial stage of oscillation but the stable oscillation frequency can be obtain from large signal analysis not from small signal mode in fig.2, since the start oscillation frequency is different with stable oscillation frequency.

A stage is an inverter and has  $t_d$  seconds delay. Since the similarity between stages is assumed, oscillation frequency can be obtained as (2).

$$f_0 = \frac{1}{2Nt_d} \tag{2}$$

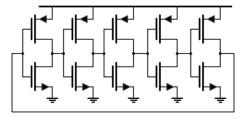

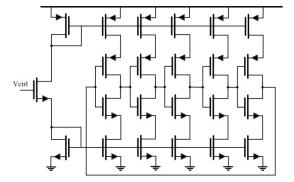

In (2) we assume that N is an odd number and illustrates the number of delay stages. In fact the starting frequency of oscillation is determined by Barkhausen criteria and stable oscillation frequency specified by inverters delay time [2]. According to (2) oscillation frequency strongly depends on delay time of delay stages. Also knowing that the number stages in a fixed structure is constant then the most significant parameters for oscillation frequency calculation is delay time. Two configurations for five stage conventional ring oscillator are shown in fig.3 and fig.4. According to fig.4 we have an option to change the oscillation frequency by adjusting Vctrl, so by using current starved inverter, voltage controlled oscillator can be designed.

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 2, June 2015

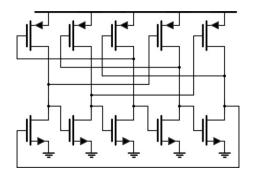

Fig.3. Five stage basic ring oscillator

Fig.4. Five stage Current Starved ring VCO

In this paper we've calculated the delay time of basic and Current Starved inverters and based on the equations a combined skewed ring VCO will be presented.

### 2. DELAY TIME OF INVERTERS

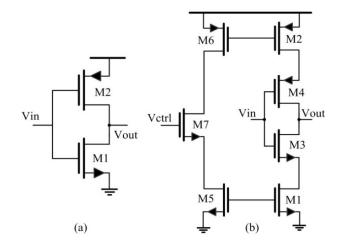

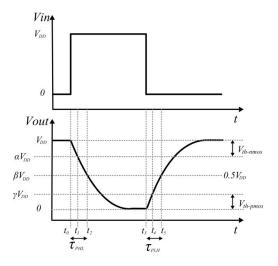

General conditions of ring oscillators were discussed in previous part. In this section delay time calculations are presented since this parameter is the only parameter which can determine the oscillation frequency. By assuming two types of inverters, basic type inverter and current starved inverter (Fig.5).By applying an ideal pulse to both of these inverters, we obtain the output signal depicted in Fig.6.

Details of calculations are brought in the appendix A.

$$t_{delay} \propto \frac{\tau_{PHL} + \tau_{PLH}}{2}$$

$$\tau_{PHL} = t_2 - t_0$$

$$\tau_{PLH} = t_5 - t_3$$

$$\tau_{PHLbasic} = \frac{2C_L (1 - \alpha)V_{DD}}{\mu_n c_{ox} \frac{W}{L} (V_{DD} - V_{th-nmos})^2}$$

$$+ \frac{C_L}{\mu_n c_{ox} \frac{W}{L} (V_{DD} - V_{th-nmos})} \ln\left(\frac{2\alpha - \beta}{\beta}\right)$$

$$\tau_{PLHbasic} = \frac{-2C_L \mathcal{W}_{DD}}{\mu_p c_{ox} \frac{W}{L} (V_{DD} - V_{th-pmos})^2}$$

(3)

3

$$+\frac{C_{L}}{\mu_{p}c_{\alpha x}}\frac{W}{L}(V_{DD}-V_{th-pmos})\ln\left(\frac{\beta-2\gamma}{\beta}\right)$$

$$\mathcal{T}_{PHLCS} \approx \frac{2C_{L}(1-\alpha)V_{DD}}{\mu_{n}c_{\alpha x}}\frac{W}{L}(V_{GS1}-V_{th-nmos})^{2}$$

$$+\frac{C_{L}}{\mu_{n}C_{\alpha x}}\frac{W}{L}(V_{DD}-V_{th-nmos})\ln\left(\frac{\alpha-\beta}{\beta}\right)$$

$$\mathcal{T}_{PLHCS} \approx \frac{-2C_{L}W_{DD}}{\mu_{p}c_{\alpha x}}\frac{W}{L}(V_{SG2}-V_{th-pmos})^{2}$$

$$+\frac{C_{L}}{\mu_{p}C_{\alpha x}}\frac{W}{L}(V_{DD}-V_{th-pmos})\ln\left(\frac{\beta-\gamma}{\beta}\right)$$

(4)

Fig.5. Basic inverter (a) and Current Starved inverter (b)

Fig.6. Input and output of inverters

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 2, June 2015 In the other word:

$$\Delta t_{Basic} \propto \frac{1}{\Delta V_{DD}} \& \Delta t_{CurrentStarved} \propto \Delta V_{DD}$$

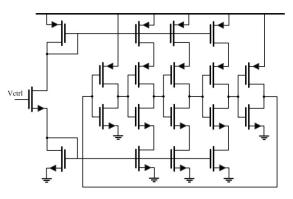

As can be seen we can conclude that delay time of these two inverters show different behaviour versus power supply changing. According to (3) and (4) delay time of basic inverter depends on power supply changing in opposite direction which delay time of current starved inverter depends on power supply changing. By considering this fact it is obvious that combined ring oscillator depicted in fig.7 can provide more stable oscillator frequency versus power supply variation. The whole loop delay in this type of oscillator can be introduce as sum of all delay times. In this case first and fifth stages are basic type inverters and other stages are current starved inverters. By summing these delay times the total delay time is less sensitive to power supply variation in comparison with basic type inverter delay time or current starved inverter delay time.

$$\boldsymbol{t}_{d} = \boldsymbol{t}_{d1} + \boldsymbol{t}_{d2} + \boldsymbol{t}_{d3} + \boldsymbol{t}_{d4} + \boldsymbol{t}_{d5} \tag{5}$$

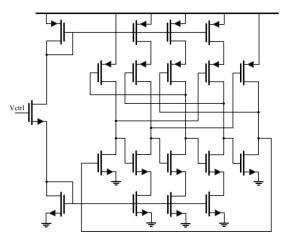

Fig.7. Combined ring VCO

Then, if all inverters are the same type  $t_1, \ldots, t_n$  will have the same variation. Meaning that all become smaller or bigger. In the other words changing oscillation frequency is inevitable. But in combined structure two types of inverters show opposite behaviours to power supply changing which considerably reduces the dependence of whole circuit to power supply noise. However combined ring VCO has the lower oscillation frequency compared with simple ring oscillators. By using NSD stages we can increase oscillation frequency of combined ring VCO.

### **3. NEGATIVE SKEWED DELAY SCHEME**

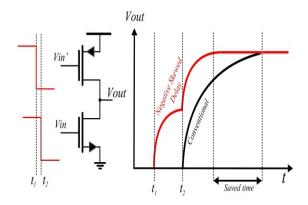

In conventional inverters both PMOS and NMOS have the same input signals. NSD is a technique that reduces delay of inverters. Fig.8 shows the concept of NSD. In fact in NSD inverter input signal to PMOS arrives earlier than to the NMOS and output changing become faster as illustrated in fig.8.[6].

By using NSD stage to design a ring oscillator we need to modify the connections as shown fig.9. Also for combined ring VCO the circuit of fig.10 is suggested. The minimum number of stages in

skewed ring oscillator is five because when the number of stage is tree, the skewed ring oscillator yields a PMOS diode- connected load. By using NSD connection for combined ring oscillator we can compensate decreased oscillation frequency by changing configuration.

Fig. 8. NSD inverter

Fig. 9. Skewed ring oscillator

Fig. 10. Proposed Combined Skewed ring VCO

### **4. SIMULATION RESULTS**

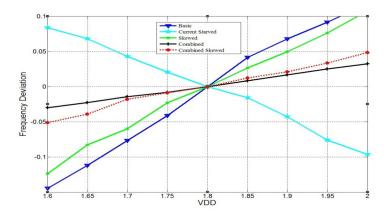

In order to validate the previous discussion, five structures in fig.3, fig.4, fig.7, fig.9 and fig.10 have been simulated with HSPICE using TSMC 180 nm technology. The nominal supply voltage and Vctrl have been selected equal to 1.8 V and 1.5 V respectively. Also a factor as frequency deviation is defined in [1] to compare operational performance of simulated circuits. This factor is described in (6).

$$\frac{\Delta f}{f} = \frac{f\left(V_{DD} + \Delta V_{DD}\right) - f\left(V_{DD}\right)}{f\left(V_{DD}\right)}$$

(6)

In this definition f ( $V_{DD}+\Delta V_{DD}$ ) is the oscillation frequency when supply voltage is  $V_{DD}+\Delta V_{DD}$  [1].

Fig. 11 shows frequency deviation factor for five ring oscillator that obtained from simulation. And table.1 presents a comparison between these five type ring oscillators. The simulation results verify the analysis and mathematical justifications since simple combined structure and combined structure with NDS connections show considerable reduction in frequency deviation factor. In addition using NDS connection increases the oscillation frequency for combined ring oscillator from 960MHz to 3.31GHz. The proposed combined skewed ring oscillator is a VCO due to using current starved inverter. Table.1 reports the important parameters for simulated oscillators. According to this table the proposed ring oscillator can work in higher frequencies with lower frequency deviation in compared with simple structures.

Fig. 11. Frequency deviation factor of five ring oscillators.

| 5 Stage Ring Oscillator                                       | Baic [2] | Current<br>Starved<br>[4] | Skewed<br>[6] | Combined[1] | Combined<br>skewed<br>(this work) |

|---------------------------------------------------------------|----------|---------------------------|---------------|-------------|-----------------------------------|

| Number of basic type                                          | 5        | 0                         | 5             | 2           | 2                                 |

| Number of Current Starved                                     | 0        | 5                         | 0             | 3           | 3                                 |

| Number of Transistor                                          | 10       | 23                        | 10            | 19          | 19                                |

| $\Delta f \ / f \left( V_{\rm DD} \pm 0.2 V_{\rm DD} \right)$ | %13      | 14%                       | %12           | %3          | %5                                |

| $\Delta f / f (temp \pm 25^{\circ})$                          | %4       | 5%                        | %4            | %0.6        | %0.8                              |

| Oscillation Frequency                                         | 3.39GHZ  | 632MHz                    | 5.65GHz       | 960MHz      | 3.31GHz                           |

| Is VCO?                                                       | No       | Yes                       | No            | Yes         | Yes                               |

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 2, June 2015 Tab. 1. Simulation results for five type ring oscillators

## **5. CONCLUSION**

Ring oscillators are one of the basic blocks of integrated circuits. This paper presents two types of CMOS inverters with detailed delay time calculations and then suggests combined structure for implementing an efficient VCO regarding frequency deviation. Oscillation frequency of combined ring VCO is low in respect to simple one. For increasing oscillation frequency we used NSD stages in combined structure that significantly increased oscillation frequency. The results of simulation by HSPICE for  $0.18\mu$ m CMOS approve the analysis results. According to simulation results the proposed VCO can work in higher frequencies with less frequency deviation.

#### A.1. Appendix A

$$\alpha = \frac{V_{DD} - V_{th-nmos}}{V_{DD}}$$

$$\beta = \frac{V_{DD}}{2}$$

$$\gamma = \frac{V_{th-pmos}}{V_{DD}}$$

In order to calculate delay time of Basic type inverter (Fig.5 (a)) we can write:

$for t_0 < t < t_1$   $nmos \rightarrow saturation$

$$I_{Dn} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{in} - V_{ih-nmos})^2 = -I_{CL} = -C_L \frac{dV_{out}}{dt}$$

for  $V_{DD} - V_{ih-nmos} < V_{out} < V_{DD}$

$V_{DD} - V_{ih-nmos} = \alpha V_{DD} \rightarrow 0 < \alpha < 1$

$$\int_{t_0}^{t_1} dt = -C_L \int_{V_{DD}}^{\alpha V_{DD}} \frac{1}{I_{Dn}} dV_{out}$$

$$\int_{0}^{t_{1}} dt = \frac{-2C_{L}}{\mu_{n} C_{ax} \frac{W}{L} (V_{DD} - V_{ih-nmos})^{2}} \int_{V_{DD}}^{dV_{DD}} dV_{out}$$

$$t_{1} - t_{0} = \frac{2C_{L} (1 - \alpha)V_{DD}}{\mu_{n}c_{ax} \frac{W}{L} (V_{DD} - V_{ih-nmos})^{2}} \qquad (1A)$$

$$t_{1} < t < t_{2} \quad nmos \rightarrow Linear$$

$$I_{Dn} = \mu_{n} C_{ax} \frac{W}{L} (V_{in} - V_{ih-nmos})V_{out} - \frac{1}{2}V_{out}^{2}$$

$$\mu_{n} C_{ax} \frac{W}{L} (V_{in} - V_{ih-nmos})V_{out} - \frac{1}{2}V_{out}^{2} = -C_{L} \frac{dV_{out}}{dt}$$

for  $V_{out} < V_{DD} - V_{ih}$

$$\int_{t_{1}}^{t_{2}} dt = -C_{L} \int_{dV_{DD}}^{dV_{DD}} \frac{1}{I_{Dn}} dV_{out}$$

$$t_{2} - t_{1} = \frac{2C_{L}}{\mu_{n} C_{ax} \frac{W}{L} (V_{DD} - V_{ih-nmos})} \ln \left(\frac{2\alpha - \beta}{\beta}\right) \qquad (2A)$$

$$\mathcal{T}_{PHL} < t_{2} - t_{0} = (t_{2} - t_{1}) + (t_{1} - t_{0})$$

$$(1A) + (2A) \xrightarrow{yields} \mathcal{T}_{PHL}$$

$$\mathcal{T}_{PHL} = \frac{2C_{L} (1 - \alpha)V_{DD}}{\mu_{n}c_{ax} \frac{W}{L} (V_{DD} - V_{ih-nmos})} \ln \left(\frac{2\alpha - \beta}{\beta}\right)$$

$$Or$$

$$\tau_{PLH} \propto t_5 - t_3 = (t_5 - t_4) + (t_4 - t_3)$$

$$\tau_{PLH} = \frac{-2C_L \mathcal{W}_{DD}}{\mu_p c_{ox} \frac{W}{L} (V_{DD} - V_{th-pmos})^2}$$

$$+ \frac{C_L}{\mu_p c_{ox} \frac{W}{L} (V_{DD} - V_{th-pmos})} \ln\left(\frac{\beta - 2\gamma}{\beta}\right)$$

Then

$$\Delta t_{Basic} \cong \frac{A_1}{\Delta V_{DD}} + \frac{A_2}{\Delta V_{DD}} + \frac{A_3}{\Delta V_{DD}} + \frac{A_4}{\Delta V_{DD}}$$

Where  $A_1, A_2, A_3, A_4$ , are constant value as follow:

$$A_1 = \frac{2C_L (1-\alpha)}{\mu_n c_{\alpha x}} \frac{W}{L}$$

$$A_{2} = \frac{C_{L}}{\mu_{n}c_{ox}} \frac{W}{L} \ln\left(\frac{2\alpha - \beta}{\beta}\right)$$

$$A_{3} = \frac{-2C_{L}\gamma}{\mu_{p}c_{ox}} \frac{W}{L}$$

$$A_{4} = \frac{C_{L}}{\mu_{p}c_{ox}} \frac{W}{L} \ln\left(\frac{\beta - 2\gamma}{\beta}\right)$$

to calculate delay time of Current Starved inverter (Fig.5(b)) we can write equally.

$$t_{0} < t < t_{1}$$

$$V_{in} = V_{DD}, V_{out} \in [V_{DD}, V_{DD} - V_{ih}]$$

$$M \rightarrow saturation, M \rightarrow saturation$$

$$M \rightarrow cut off$$

$$for V_{DD} - V_{th-nmos} < V_{out} < V_{DD}$$

$$I_{D1} = \frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS1} - V_{th-nmos})^{2}$$

$$dt = -\frac{C_{L}}{\frac{1}{2} \mu_{n} C_{ox} \frac{W}{L} (V_{GS1} - V_{th-nmos})^{2}} dV_{out}$$

$$\int_{t_{0}}^{t} dt = -C_{L} \int_{V_{DD}}^{aV_{DD}} \frac{1}{I_{Dn}} dV_{out}$$

Know that  $(V_{GS1} - V_{th-nmos}) = cte$

$$\int_{t_0}^{t_1} dt = \frac{-2C_L}{\mu_n C_{ox} \frac{W}{L} (V_{GS1} - V_{th-nmos})^2} \int_{V_{DD}}^{dV_{pD}} dV_{out}$$

$$t_1 - t_0 = \frac{2C_L (1 - \alpha)V_{DD}}{\mu_n C_{ox} \frac{W}{L} (V_{GS1} - V_{th-nmos})^2}$$

(1B)

for

$$t_1 < t < t_2$$

$M \rightarrow linear$ ,  $M \rightarrow saturation$

$$I_{D3} = \mu_n C_{ox} \frac{w}{L} (V_{GS3} - V_{th-nmos}) V_{DS3} - \frac{1}{2} V_{DS3}^2$$

$$I_{D1} = \frac{1}{2} \mu_n C_{ox} \frac{w}{L} (V_{GS1} - V_{th-nmos})^2$$

$$I_{C_{L}} \cong -I_{D3} = C_{L} \frac{dV_{out}}{dt}$$

$$for V_{out} < V_{DD} - V_{th-nmos}$$

$$\int_{1}^{t_{1}} dt = -C_{L} \int_{dV_{DD}}^{\beta V_{DD}} \frac{1}{I_{D3}} dV_{out}$$

$$\int_{1}^{t_{1}} dt = -\frac{C_{L}}{\mu_{n} C_{ox}} \int_{L}^{\beta V_{DD}} \int_{dV_{DD}}^{\delta V_{DD}} \frac{1}{(V_{GS3} - V_{th-nmos})V_{DS3} - \frac{1}{2}V_{DS3}^{2}} dV_{out}$$

$$V_{DS3} = V_{out} - V_{DS1} \cong V_{out} \quad and \quad V_{GS3} \cong V_{in} = V_{DD}$$

$$\int_{1}^{t_{2}} dt = -\frac{C_{L}}{\mu_{n} C_{ox}} \int_{L}^{\beta V_{DD}} \frac{1}{(V_{DD} - V_{th-nmos})V_{out} - V_{out}^{2}} dV_{out}$$

$$t_{2} - t_{1} = \frac{C_{L}}{\mu_{n} C_{ox}} \frac{W}{L} \frac{1}{(V_{DD} - V_{th-nmos})} \ln \left(\frac{\alpha - \beta}{\beta}\right) \quad (2B)$$

$$\mathcal{T}_{PHL} \propto t_{2} - t_{0} = (t_{2} - t_{1}) + (t_{1} - t_{0})$$

$$(1B) + (2B) \xrightarrow{yields} \mathcal{T}_{PHL}$$

$$\mathcal{T}_{PHL} \propto \frac{2C_{L} (1 - \alpha)V_{DD}}{\mu_{n} c_{ox}} \frac{W}{L} (V_{GS1} - V_{th-nmos})^{2}$$

$$+ \frac{C_{L}}{\mu_{n} C_{ox}} \frac{W}{L} (V_{DD} - V_{th-nmos}) \ln \left(\frac{\alpha - \beta}{\beta}\right)$$

or

$$\mathcal{T}_{PHL} \propto x_{t} - t_{t} = (t_{t} - t_{t}) + (t_{t} - t_{t})$$

$$\tau_{PLH} \propto \frac{-2C_L \mathcal{W}_{DD}}{\mu_p c_{ox} \frac{W}{L} (V_{SG2} - V_{th-pmos})^2} + \frac{C_L}{\mu_p C_{ox} \frac{W}{L} (V_{DD} - V_{th-pmos})} \ln\left(\frac{\beta - \gamma}{\beta}\right)$$

Then

$\Delta t_{\text{CurrentStarved}} \cong B_1 \cdot \Delta V_{DD} + \frac{B_2}{\Delta V_{DD}} + B_3 \cdot \Delta V_{DD} + \frac{B_4}{\Delta V_{DD}} \text{ where } B_1, B_2, B_3, B_4, \text{ are constant value as follow:}$

$B_{1} = \frac{2C_{L}(1-\alpha)}{\mu_{n}c_{ox}\frac{W}{L}(V_{GS1}-V_{th-mmos})^{2}}$

$$B_{2} = \frac{C_{L}}{\mu_{n} C_{ox} \frac{w}{L}} \ln\left(\frac{\alpha - \beta}{\beta}\right)$$

$$B_{3} \propto \frac{-2C_{L} \gamma}{\mu_{p} c_{ox} \frac{W}{L} \left(V_{SG2} - V_{th-pmos}\right)^{2}}$$

$$B_{4} = \frac{C_{L}}{\mu_{p} C_{ox} \frac{w}{L}} \ln\left(\frac{\beta - \gamma}{\beta}\right)$$

Or we can write:

$$B_1 + B_3 > B_2 + B_4$$

Since

$$0 < |V_{GS,SG} - V_{th-n,p}| < 1 \rightarrow |V_{GS,SG} - V_{th-n,p}|^{2}$$

$$\frac{2C_{L}(1-\alpha)}{\mu_{n}C_{ox}\frac{W}{L}(V_{GS1} - V_{th})^{2}} > \frac{2C_{L}(1-\alpha)}{\mu_{n}C_{ox}\frac{W}{L}}$$

$$\frac{2C_{L}(1-\alpha)}{\mu_{n}C_{ox}\frac{W}{L}(V_{GS1} - V_{th})^{2}} > \frac{C_{L}}{\mu_{n}C_{ox}\frac{W}{L}} \ln\left(\frac{\alpha-\beta}{\beta}\right)$$

$$\frac{-2\gamma C_{L}}{\mu_{p}C_{ox}\frac{W}{L}(V_{SG2} - V_{th-pmos})^{2}} > \frac{C_{L}}{\mu_{p}C_{ox}\frac{W}{L}} \ln\left(\frac{\beta-\gamma}{\beta}\right)$$

Then

$$B_1 > B_2 \& B_1 > B_4$$

$B_3 > B_2 \& B_3 > B_4$

So  $B_1 + B_3 > B_2 + B_4$

In summary

$$\Delta t_{Basic} \propto \frac{1}{\Delta V_{DD}}$$

$\Delta t_{\rm CurrentStarved} \propto \Delta V_{\rm DD}$

### REFERENCES

- G. G. Jovanovi'c, M. Stoj'cev, Z. Stamenkovic. A CMOS Voltage Controlled Ring Oscillator with Improved Frequency Stability. Scientific Publication of the State University of NOVI PAZAR ser. A: APPL. MATH. INFORM. AND MECH. vol. 2, 2010.

- [2] B.Razavi. RF Microelectronics. Prentice Hall PTR, 1997.

- [3] B. Razavi. Design of Analog CMOS Integrated Circuits. MacGraw-Hill,2001

- [4] G. Jovanovi'c, M. Stoj'cev. Current starved delay element with symmetric load. International Journal of Electronics, Vol. 93, 3, 2006.

- [5] Yao WANG, Jiaxin LIU, Liangbo XIE, Guangjun WEN. An Ultra-Low-Power Oscillator with Temperature and Process Compensation for UHF RFID Transponder. RADIOENGINEERING, VOL. 22, NO. 2, JUNE 2013, 505-510.

- [6] Aimad El Mourabita, Guo-Neng Lub, Patrick Pittetb, A new method to enhance frequency operation of CMOS ring oscillators, International Journal of Electronics, Vol. 99, Issue 3, 2012, 351-360.

- [7] Won-tae Leea, Jaemin Shima, Jichai Jeongb, Design of a three-stage ring-type voltage-controlled oscillator with a wide tuning range by controlling the current level in an embedded delay cell. Microelectronics Journal, Volume 44, Issue 12, December 2013, 1328–1335.

- [8] Seungjin Kim; In-Young Lee; Seok-Kyun Han, A Low-Noise Four-Stage Voltage-Controlled Ring Oscillator in Deep-Submicrometer CMOS Technology. IEEE Transactions on Circuits and Systems. 2013, Vol.60, 71-75.

- [9] S. Docking, M. Sachdev. An Analytical Equation for the Oscillation Frequency of High-Frequency Ring Oscillators. IEEE Journal of Solid State Circuits, vol.39, 3, 2004, 533-537.

- [10] Yalcin Alper Eken and John P. Uyemura, "A 5.9-GHz voltage-controlled ring oscillator in 0.18- μm CMOS" IEEE J. Solid-State Circuits, vol. 39 no. 1, Jan. 2004.

- [11] Ramazani A, Biabani S, Hadidi G, CMOS ring oscillator with combined delay stages. Int J Electron Commun (AEÜ) (2014).

- [12] Akbari, M., Biabanifard, S., Asadi, S., & Yagoub, M. C. (2014). Design and analysis of DC gain and transconductance boosted recycling folded cascode OTA. AEU-International Journal of Electronics and Communications, 68(11), 1047-1052.

- [13] Largani, H., Mehdi, S., Shahsavari, S., Biabanifard, S., & Jalali, A. (2014). A new frequency compensation technique for three stages OTA by differential feedback path. International Journal of Numerical Modelling: Electronic Networks, Devices and Fields.

- [14] Shahsavari, S., Biabanifard, S., Largani, S. M. H., & Hashemipour, O. (2015). DCCII based frequency compensation method for three stage amplifiers. AEU-International Journal of Electronics and Communications, 69(1), 176-181.

- [15] Shahsavari, S., Biabanifard, S., Largani, S., & Hashemipour, O. (2014, May). A new frequency compensation method based on differential current conveyor. InElectrical Engineering (ICEE), 2014 22nd Iranian Conference on (pp. 361-365). IEEE.

- [16] Akbari, M., Biabanifard, S., Asadi, S., & Yagoub, M. C. (2015). High performance folded cascode OTA using positive feedback and recycling structure. Analog Integrated Circuits and Signal Processing, 82(1), 217-227.

- [17] Biabanifard, S., Aghaee, T., & Asadi, S. Adesign GUIDE FOR COMPARATOR-BASED SWITCHED-CAPACITOR INTEGRATOR.

- [18] Biabanifard, S., Largani, S. M. H., & Asadi, S. DELAY TIME ANALYSIS OF COMBINED CMOS RING OSCILLATOR.

- [19] Largani, S., Shahsavari, S., Biabanifard, S., & Jalali, A. (2014, May). A new SMC compensation strategy for three stage amplifiers based on differential feedback path. In Electrical Engineering (ICEE), 2014 22nd Iranian Conference on (pp. 185-189). IEEE.

- [20] Akbari, M., Biabanifard, S., & Hashemipour, O. (2014, May). Design of ultra-low-power CMOS amplifiers based on flicker noise reduction. In Electrical Engineering (ICEE), 2014 22nd Iranian Conference on (pp. 403-406). IEEE.

### AUTHORS

**Sadegh Biabanifard** was born in Tehran, Iran in 1989. He received the B.Sc. degree in Electronics Engineering from Imam Reza International University, Mashhad, Iran in 2011and M.Sc. degree in Analog Electronics from Shahid Beheshti University, G.C., Tehran, Iran, in 2014. His research interests are RFIC design, analog and mixed mode integrated circuits design for Ultra-Low-Power Ultra-Low-Voltage applications, OTA, current conveyer and data converter.

**S. Mehdi Hosseini Largani** was born in Tonekabon, Iran in 1989. He received the B.S. degree in Control Engineering from K.N.Toosi University of Technology, Tehran, Iran in 2011 and M.S. degree in Analog Electronic from Shahid Beheshti University (National University of Iran) G.C., Tehran, Iran, in 2014. His research interests are analog and mixed mode circuit theory, integrated circuit design for Ultra-Low-Power Ultra-Low-Voltage applications. His is currently with Electrical Engineering Department and Microelectronic Research Laboratory in Shahid Beheshti University, G.C, Tehran, Iran.

**Shahrooz Asadi** received the B.Sc. degree in Electrical Engineering and the M.Sc. degree in Electronics both from Amirkabir University, Tehran, Iran, in 2003 and 2007, respectively and the Ph.D. degree in Electronics in the School of Information Technology and Engineering (SITE), University of Ottawa, Ottawa, ON, Canada. He joined shahid Beheshti University in 2011 where he is an assistant professor. His research interests include linear and nonlinear time-domain modeling of millimeter-wave transistors, RF design of active and passive devices, design and optimization of solid state devices and multiconductor transmission lines and printed circuit board.