### TRANSFER PRINTING FOR HETEROGENEOUS SILICON PICS

<u>G. Roelkens</u>, J. Zhang, G. Muliuk, J. Goyvaerts, B. Haq, C. Op de Beeck, A. Liles, Z. Wang, S. Dhoore, S. Kumari, J. Juvert, J. Van Campenhout, B. Kuyken, D. Van Thourhout, B. Corbett, A. Trindade, C. Bower, R. Baets

# SILICON PHOTONICS FOR SMART MICROSYSTEMS

- 1. photonic integration: Build photonic systems on a chip

- 2. silicon photonics : Use the power of silicon CMOS-technology for integrated photonics

- **3. heterogeneous integration :** Avoid the limitations of silicon through combination with other materials

- 4. enable a variety of applications

- Core and access telecom networks

- Optical interconnect and high performance computing

- Sensors and biosensors

- Biomedical instrumentation

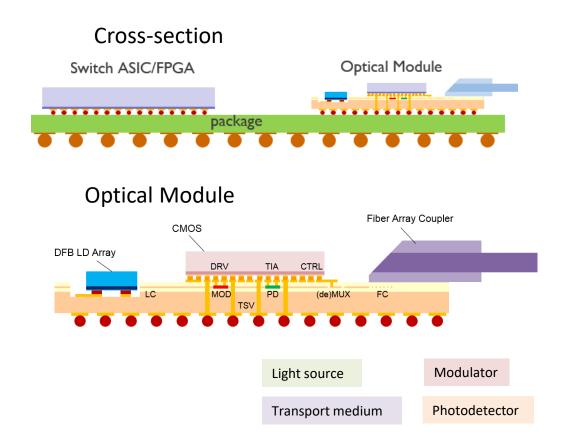

## SILICON PHOTONICS FOR SMART MICROSYSTEMS – OPTICAL I/O

| DFB LD Array | Laser array              |

|--------------|--------------------------|

| LC           | Light coupler            |

| MOD          | Modulator                |

| PD           | Photodetector            |

| (de)MUX      | (de)Multiplexer          |

| FC           | Fiber coupler            |

| TSV          | Through Silicon Vias     |

| DRV          | Electrical driver        |

| TIA          | Transimpedance Amplifier |

| CTRL         | Controller circuit       |

Michal Rakowski, Silicon Photonics Platform for 50G Optical Interconnects, In Photonics Summit and Workshop 2017.

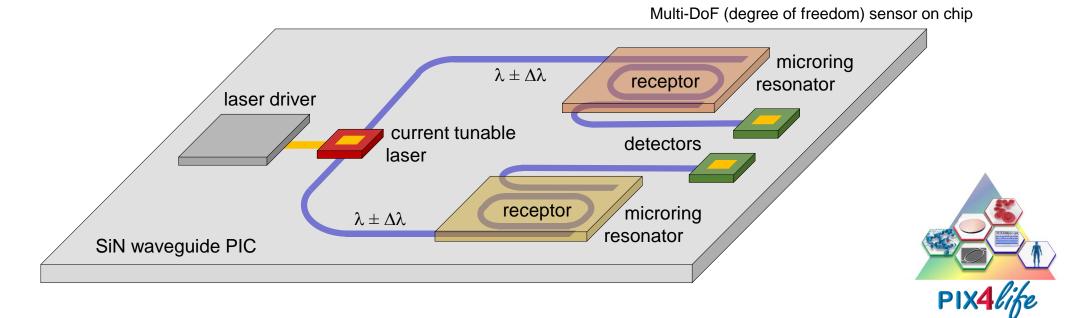

## SILICON PHOTONICS FOR SMART MICROSYSTEMS – SENSORS

### The H2020 PIX4Life project:

- Establishing a PIC pilot-line for life science applications in the VIS and VNIR (400 850 nm)

- Silicon photonics PICs with silicon nitride (SiN) WGs

- Light source integration

**CHALMERS**

(H)

BOSCH

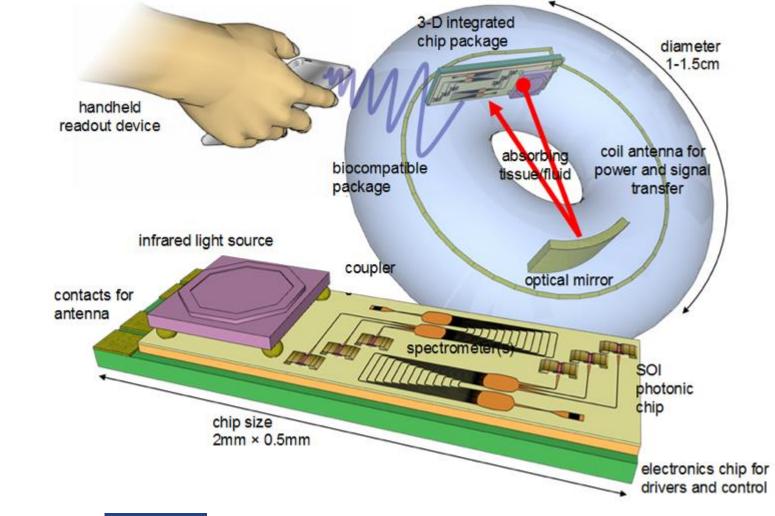

## SILICON PHOTONICS FOR SMART MICROSYSTEMS – SENSORS

Implants for Continuous Glucose Monitoring

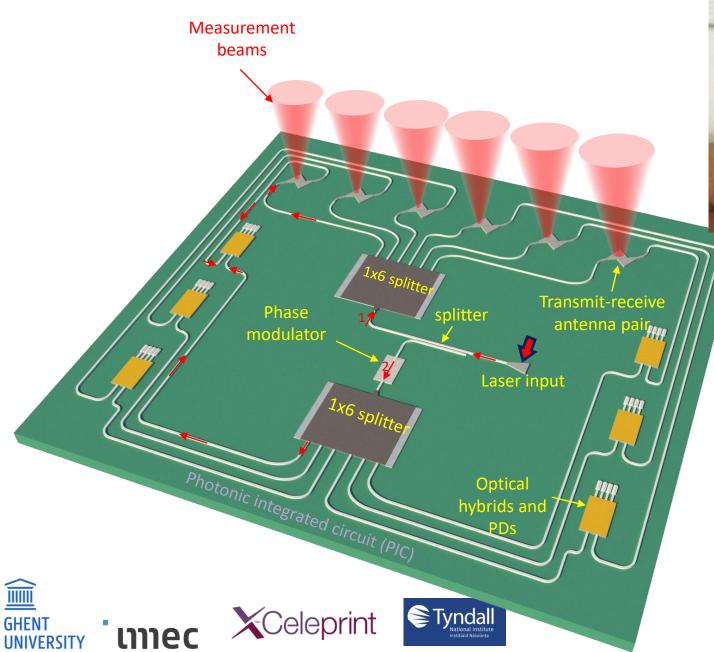

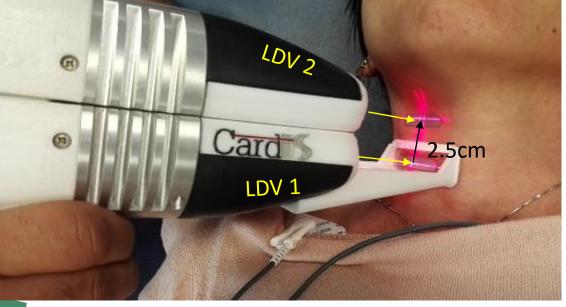

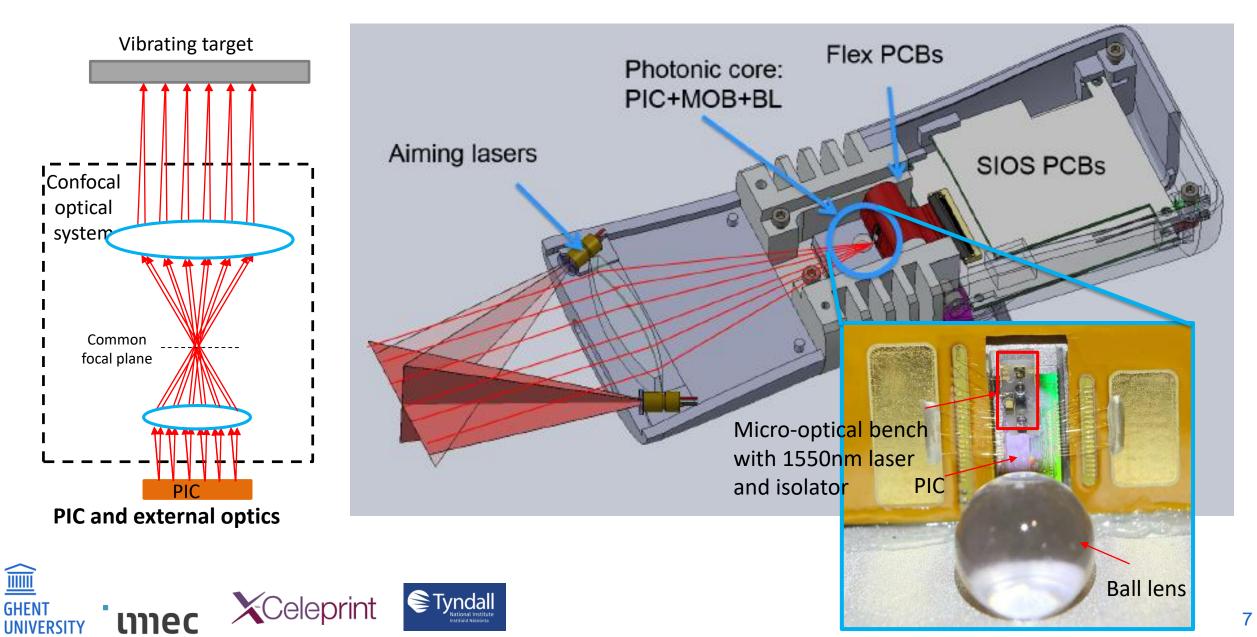

### LDV-MEASUREMENT OF BLOOD PULSE VELOCITY

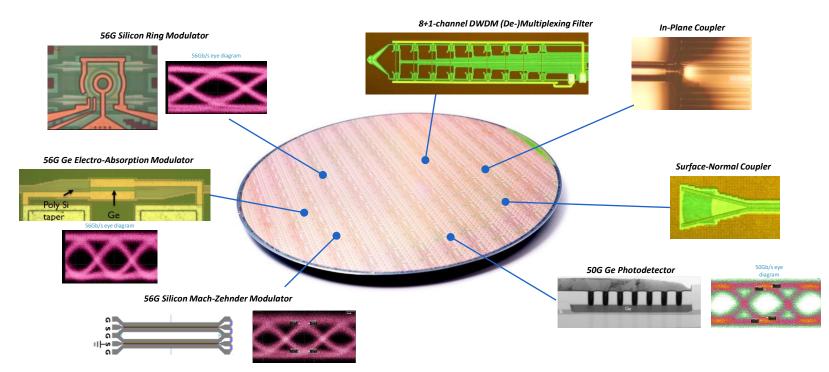

# IMEC STATE-OF-THE-ART SILICON PHOTONICS PLATFORM FULLY INTEGRATED SI PHOTONICS TECHNOLOGY

Co-integration of the various building blocks in a single platform

Today available on 200mm wafer size

95% compatible with CMOS130 in commercial foundries

No integrated laser source => need for a III-V/silicon photonic integration platform

**I** GHENT

**UNIVERSITY**

unec

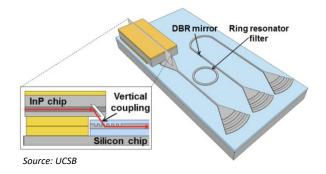

### ESTABLISHED III-V-ON-SILICON TECHNOLOGIES

GHENT UNIVERSITY

### ESTABLISHED III-V-ON-SILICON TECHNOLOGIES

LaMP

Source: Luxtera

#### Use mature III-V technology Fairly efficient optical coupling

No waveguide-in / waveguide-out devices Wafer level assembly, packaging, test and burn-in

Sequential population of SiPh wafer Currently only single wavelength lasers Can be integrated on back-end stack

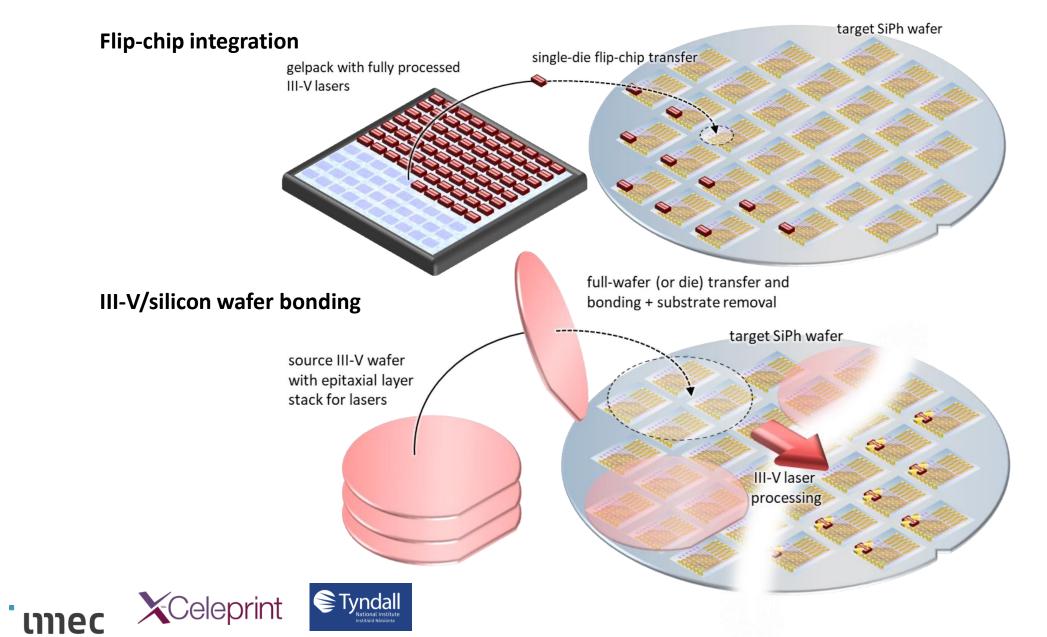

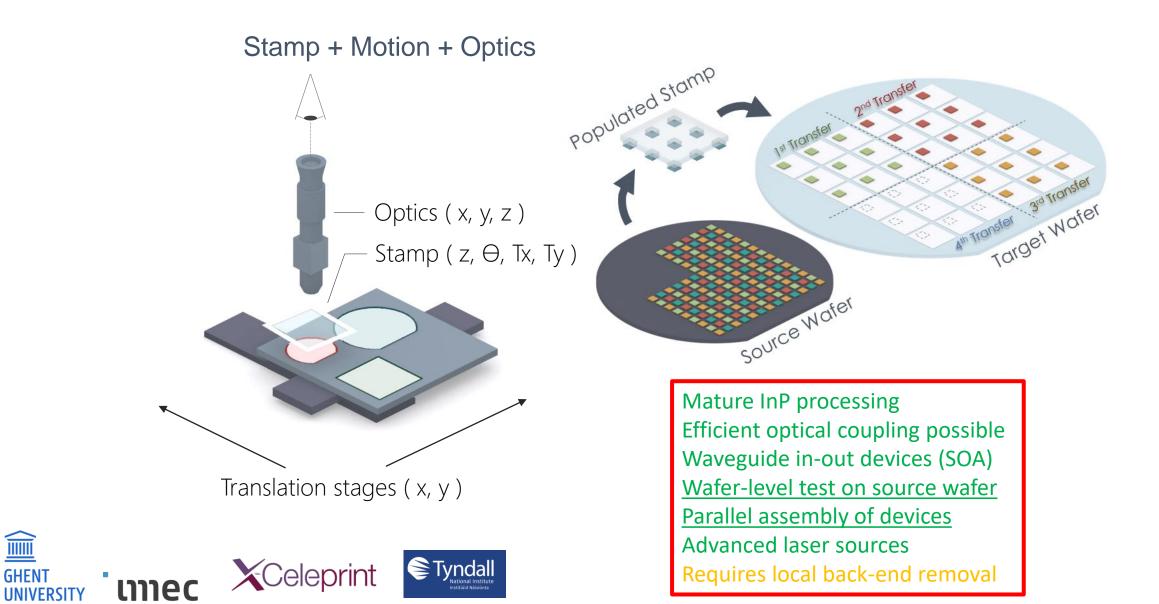

#### **Flip-chip integration**

Use mature III-V technology -> SSC Fairly efficient optical coupling Waveguide in-out devices possible (SOA) Wafer-level test and burn-in on source Sequential population of SiPh wafer Advanced laser sources can be realized Requires local back-end removal

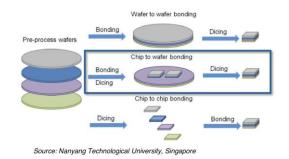

#### Die-to-wafer bonding

III-V processing on target wafer Efficient optical coupling Waveguide in-out devices (SOA) Wafer-level test and burn-in on target wafer

Parallel processing of devices Advanced laser sources Requires large area back-end removal

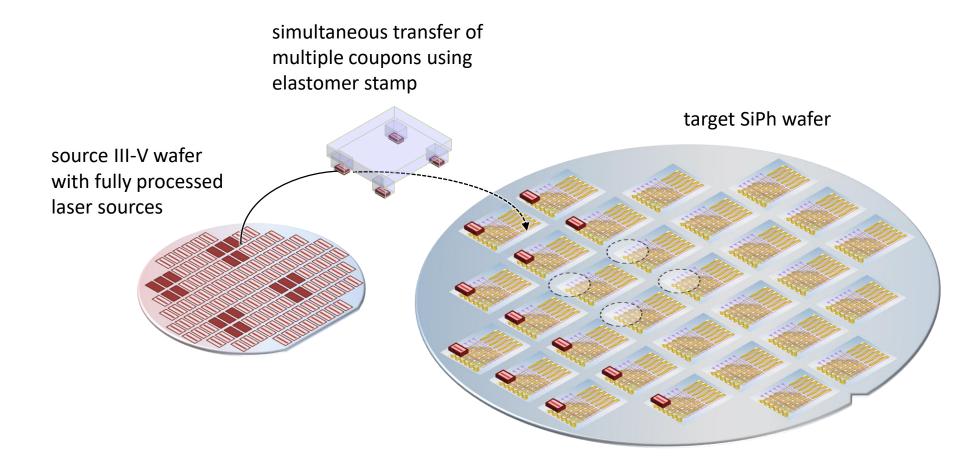

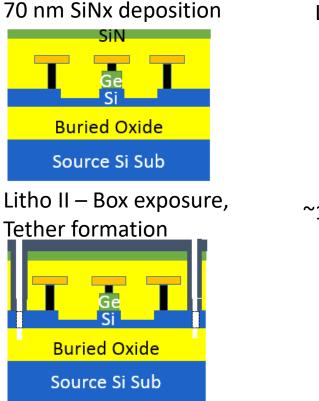

### MICRO-TRANSFER-PRINTING

$\mu TP$  combines advantages of flip-chip and die-to-wafer bonding

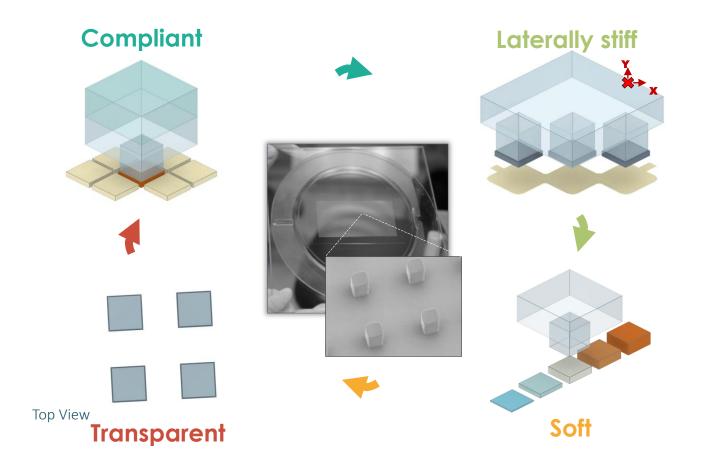

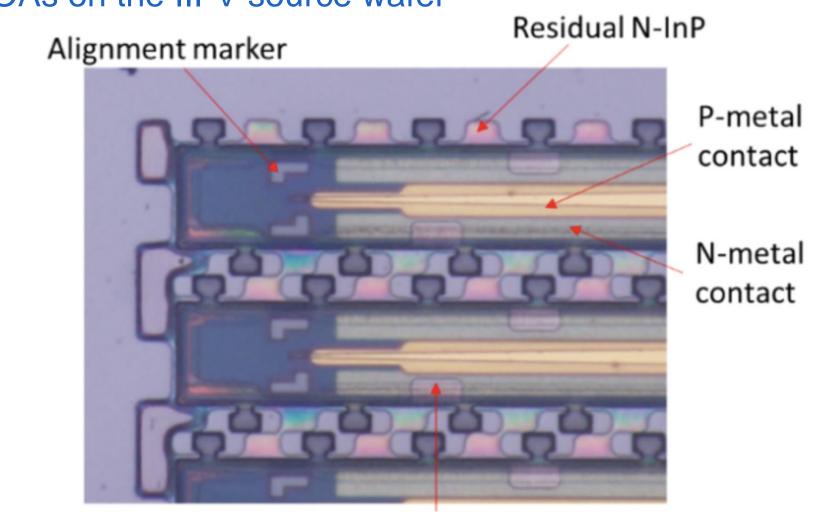

### MASS TRANSFER WITH ELASTOMER STAMPS

### MICRO-TRANSFER-PRINTING

### MICRO-TRANSFER-PRINTING

### CHARACTERISTICS OF MICRO-TRANSFER PRINTING

### **Massively parallel**

- >10,000 devices (LEDs) transferred per 45s cycle demonstrated

- Flip chip transfers individual devices.

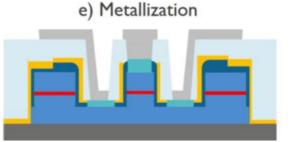

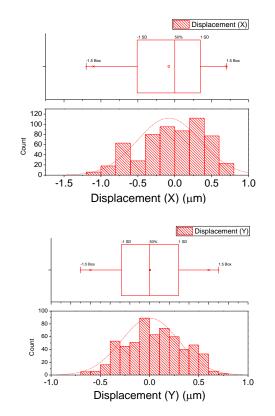

#### Position tolerance of ±1.5 $\mu$ m at 3 $\sigma$ in large arrays

- ±0.5µm and better when printed in small arrays

- Pattern recognition based

#### The highest quality source materials used

- Can be pre-processed

Different types of devices or materials can be printed close to each other Efficient use of expensive materials

- Width of devices << conventional for higher packing</li>

- Substrate can potentially be recovered

### Independent of source substrate diameter

– InP wafers 50-100mm; Si wafers 200-300mm diameter

unec

- Introduction to micro-transfer-printing technology

- Examples of III-V on Si micro-transfer-printing

- Substrate-illuminated InP PDs on full platform SOI

- InP widely tunable lasers on passive SOI

- Examples of Si on Si micro-transfer-printing

- Outlook & conclusions

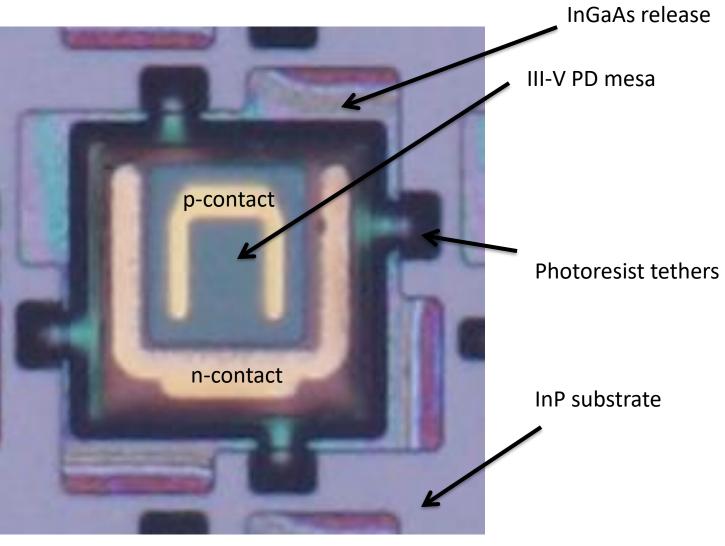

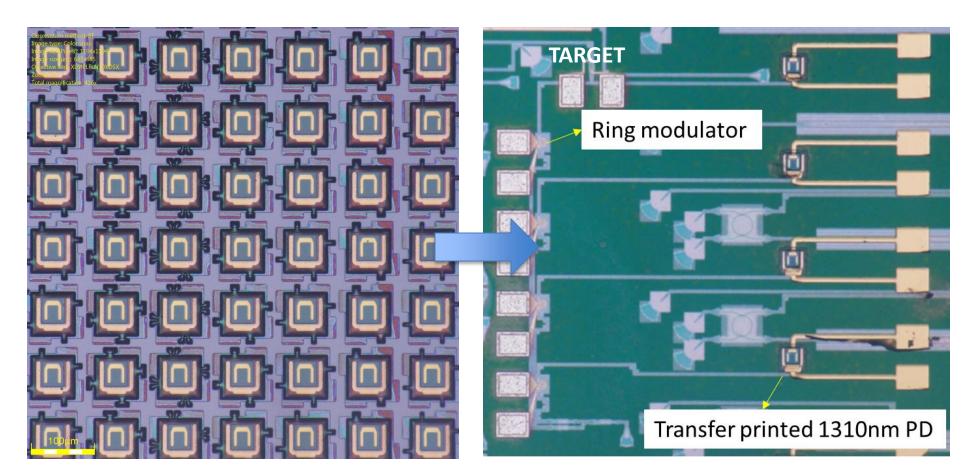

## SUBSTRATE-ILLUMINATED INP PDs

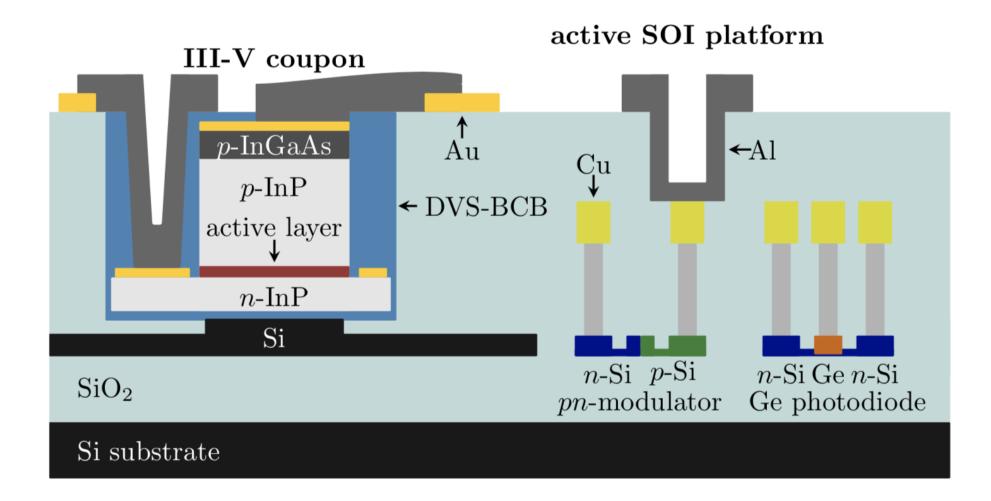

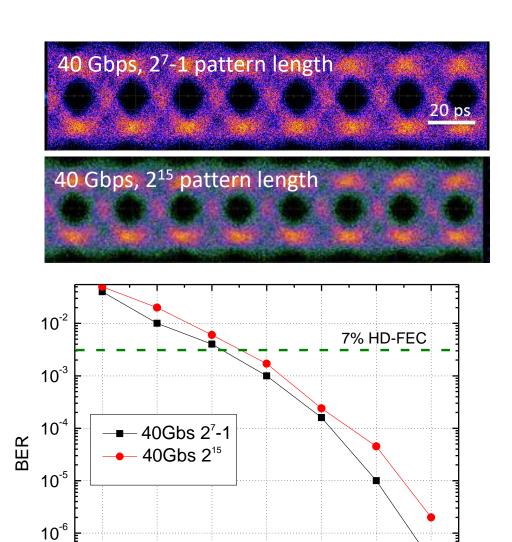

### 4x10GBPS III-V/SI TRANSCEIVER

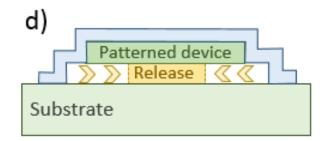

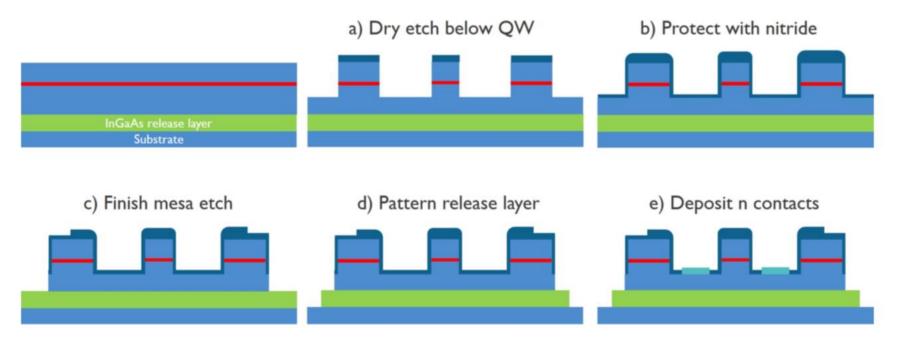

#### **III-V SOURCE WAFER**

#### SiPh TARGET WAFER

[J. Zhang et al., OE 2017]

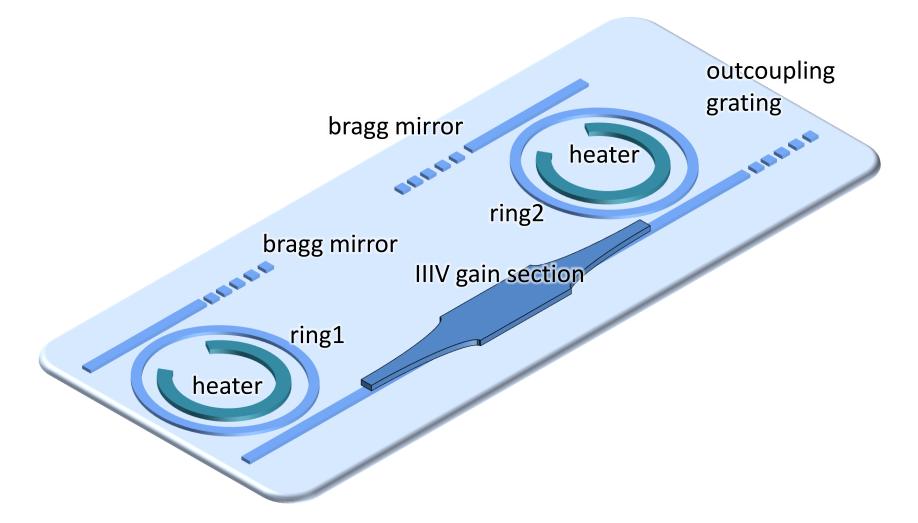

### HETEROGENEOUSLY INTEGRATED LASERS

Can be realized both using wafer bonding and transfer printing

GHENT UNIVERSITY

### TRANSFER PRINTING OF ARRAYS OF LASERS

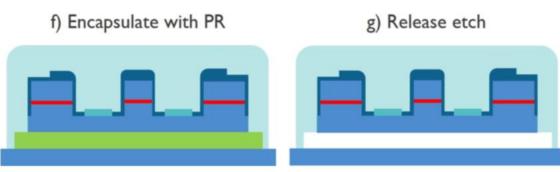

C-band SOAs on the III-V source wafer

N-via opening

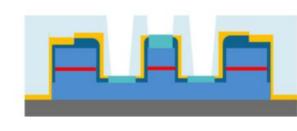

### TRANSFER PRINTING OF ARRAYS OF LASERS

d) Open vias to expose n contacts

**GHENT**

UNIVERSITY

unec

ALIGNMENT TOLERANT OPTICAL INTERFACE

GHENT UNIVERSITY

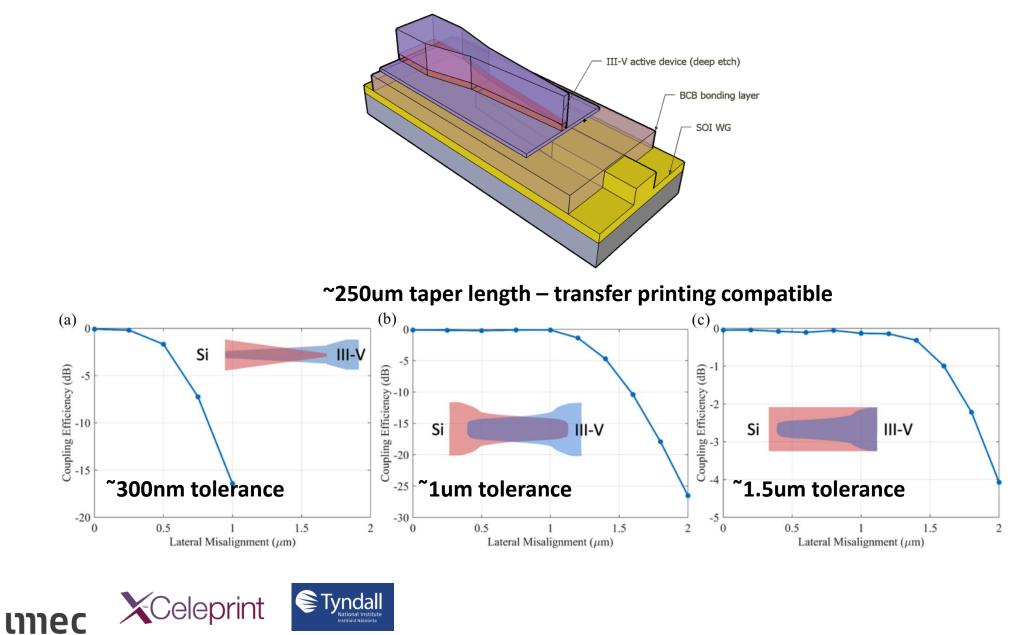

### WIDELY TUNABLE III-V-ON-SILICON LASER

**IIII** GHENT

UNIVERSITY

# OUTLINE

- Introduction to micro-transfer-printing technology

- Examples of III-V on Si micro-transfer-printing

- Examples of Si on Si micro-transfer-printing

- Ge photodiodes transfer printed on passive circuits

- Si electronics transfer printing

- Outlook & conclusions

## SI (OPTO-)ELECTRONIC DEVICE INTEGRATION

**IIII** GHENT

UNIVERSITY

### SOI (photonics / electronics) is very well suited for TP

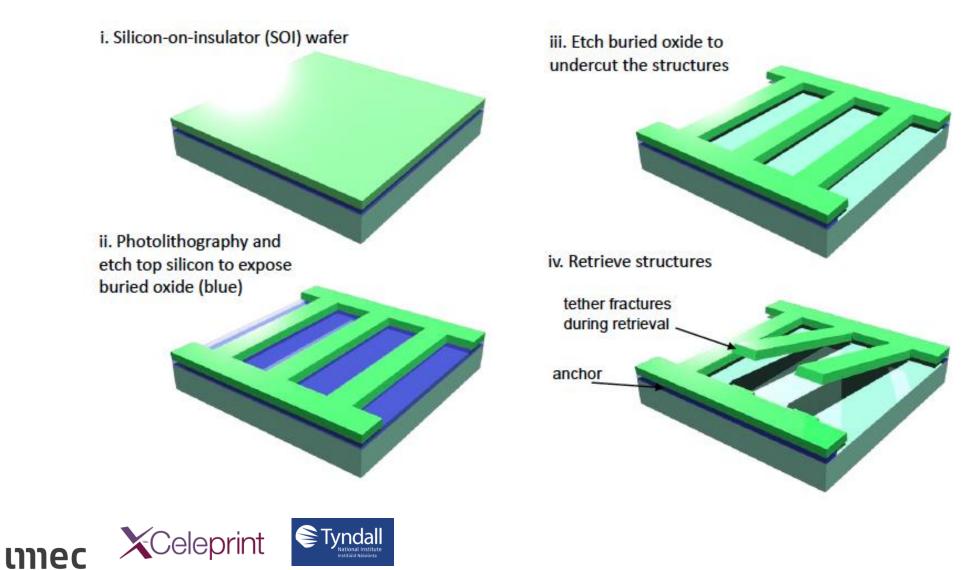

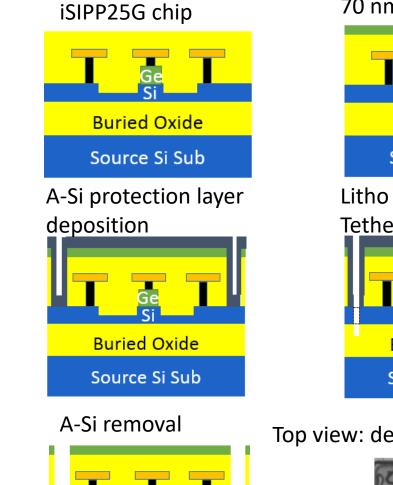

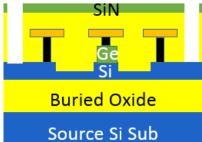

### GEPD RELEASE PROCESS FLOW

Source Si Sub

😂 Tyndall

**GHENT**

UNIVERSITY

unec

#### Litho I – coupon mesa

#### ~13 min 40% HF release

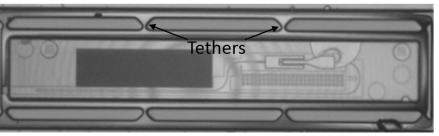

Top view: device attached to the Si barrier using ~1.2 μm wide tethers

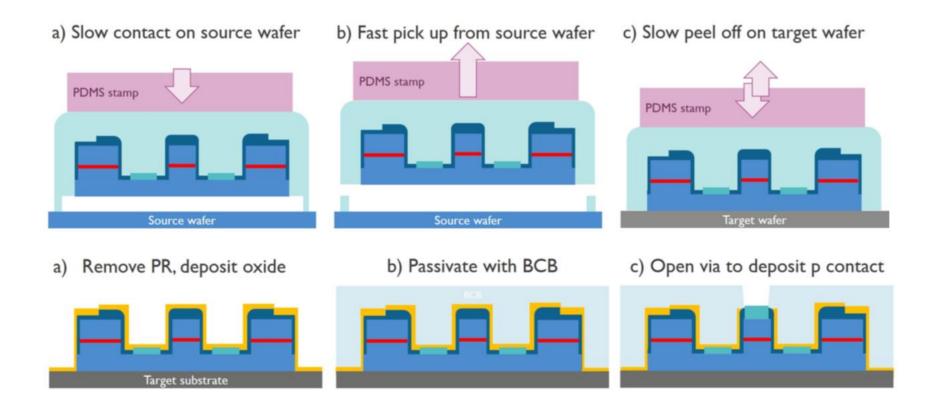

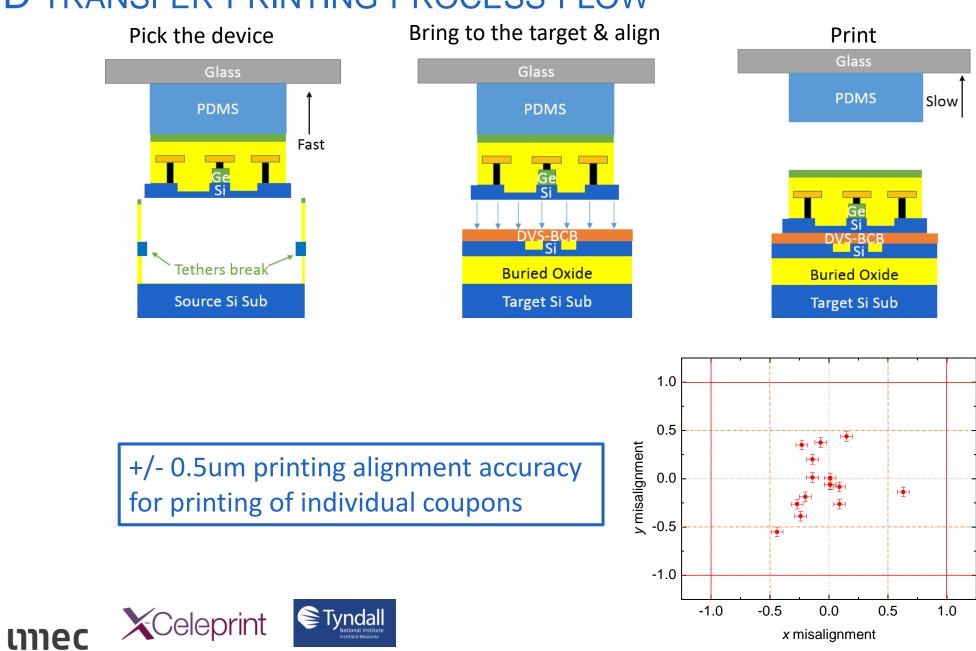

### GED TRANSFER PRINTING PROCESS FLOW

**<u>IIII</u>** GHENT

**UNIVERSITY**

### GE PD POST-PROCESSING

GHENT UNIVERSITY

ເງຍອ

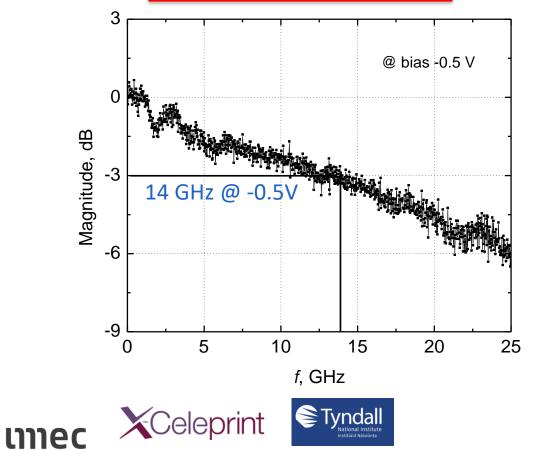

I<sub>dark</sub> = 12 nA R<sub>ser</sub> = 29.6 Ohm Responsivity > 0.6 A/W over C-band

GHENT UNIVERSITY

*P*, dBm

-5

-6

$10^{-7}$

-9

-8

-7

Measurement limit

-3

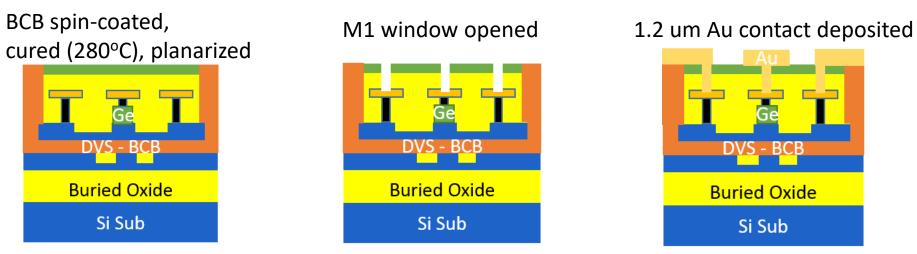

### TRANSFER PRINTED ELECTRONICS

Releasable silicon amplifier circuits realized

icro transfer printed amplifier 250μm x 50μm

"Bondpads": 10μm x 10μm

- XFAB 180nm SOI CMOS process

- $-200\mu$ m x 50 $\mu$ m x 7 $\mu$ m device size

🝧 Tyndall

Bond pads 10μm x 10μm

Celeprint

ເກາຍc

**IIII** GHENT

**UNIVERSITY**

Design: P. Ossieur

Positional accuracy better than ±1um in x and y

31

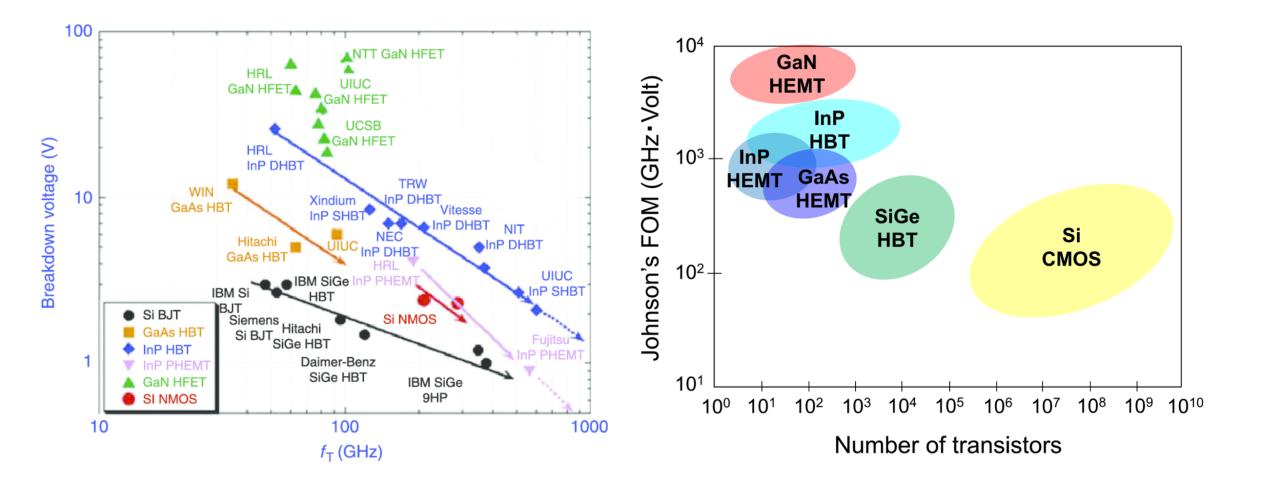

### TRANSFER PRINTED ELECTRONICS – III-V ELECTRONICS

# OUTLINE

- Introduction to micro-transfer-printing technology

- Examples of III-V on Si micro-transfer-printing

- Examples of Si on Si micro-transfer-printing

- Ge photodiodes transfer printed on passive circuits

- Si electronics transfer printing

- Outlook & conclusions

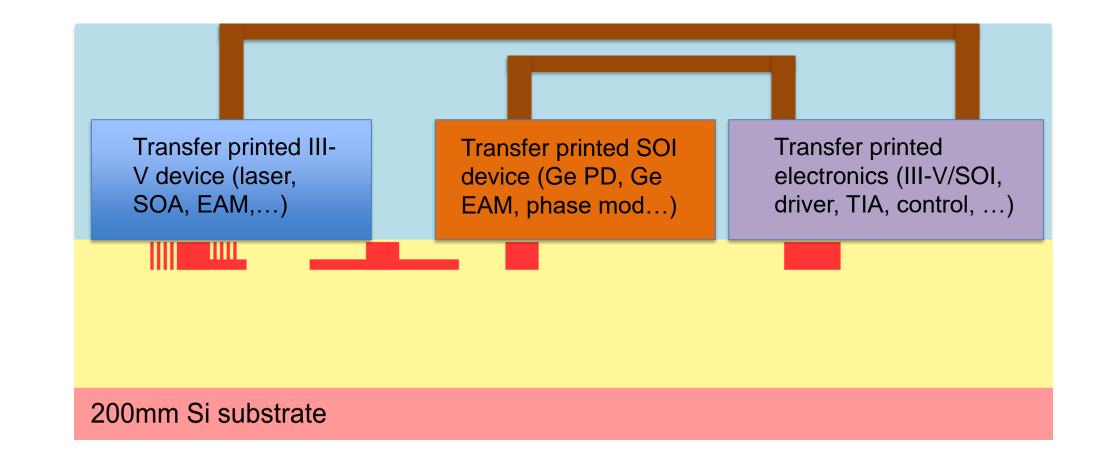

## OUTLOOK: TRANSFER PRINTING IN A FOUNDRY

- The demonstrations presented in this work were realized on a lab printer

- Transfer the µTP-technology to an industrial environment (XFAB)

- Bridging the "Valley-of-Death" to industrialization

- µTP pilot line in manufacturing environment for open access

- Development of design rules (DR) and its implementation in Process-Design-Kits (PDK)

- Development of processes for heterogeneous system integration for (Bi)CMOS, MEMS and photonics wafers

- Realization of processes for source wafer preparation, transfer printing and postprocessing on 200mm silicon wafers

- Basically any material that can be released from its substrate can be transfer printed

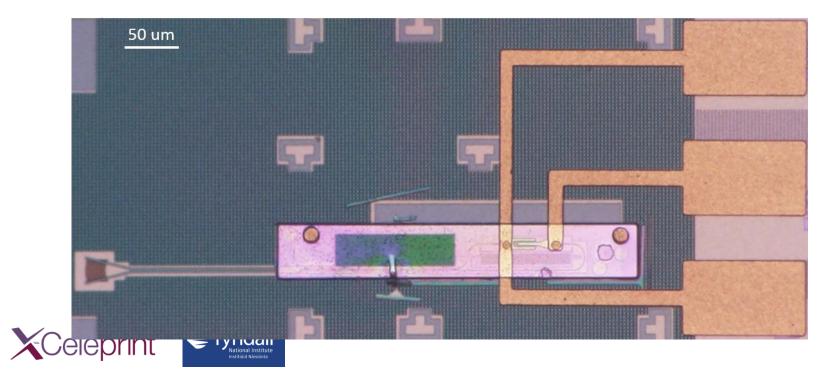

### HETEROGENEOUSLY INTEGRATED PICS

### CONCLUSIONS

- Micro-transfer-printing is an enabling technology for heterogeneous integration, combining advantages of flipchip integration and wafer bonding

- Basically any material that can be released from its substrate can be transfer printed

- III-V integration and Si device integration on SiPh demonstrated

- Current demonstrations are lab-scale, but establishing an open access pilot line for the technology is work in progress

## ACKNOWLEDGEMENTS

O/𝗊/□ Phonsi Nanophotonics by nanocrystals

PIX4 like

France-Wallonie-Vlaanderen UNION EUROPÉE

### SAFESIDE

**HENT**

UNIVERSITY