# ANALYSIS OF 6T SRAM CELL USING FINFET AT NANOMETER REGIME

Ms. M. S. Mhaske Department Of Electronics Engineering / PREC, Loni monalimhaske29@gmail.com

Mr. P. B. Vikhe Department. Of Computer Engineering / PREC, Loni vikhe.prash11@gmail.com

Prof. S. A. Shaikh

Department Of Electronics & Telecommunication Engineering / PREC, Loni sashaikh@gmail.com

#### **ABSTRACT**

The fast growing technology developments in the metal oxide semiconductor area have scaled down CMOS to the sub 32nm regime. According to International Technology Roadmap For Semiconductors projection by the 2020, the printed gate lengths will scale down to 12nm. Instead of SiO2 with AL metal gate Hafnium Oxide [HFO2] can be used as a High k material. To increased chip functionality demand, SRAM area have mostly exceed overall chip area. The stability of SRAM cell depends on variation in Process, Temperature and Voltage. This paper will discuss the detail about 6T SRAM stability in standby, read and write mode design considering Double Gate MOSFET at 32nm technology node.

**KEYWORDS:** Cell Ratio (CR), Pull up Ratio(PR), Silicon on Insulator(SOI), Static Random Access Memory(SRAM), Static Noise Margin.

#### INTRODUCTION

Static Random Access Memories are used in various microelectronics applications such as wireless, system on chip, multimedia applications, server processor etc. By using transistor scaling i.e. size reduction has increased the performance with decreasing the cost of integrated circuit. In integrated systems, SRAM cell are used for high integration density with the required performance and reliability. SRAM cell are used for increasing storage density, reducing supply voltage i.e. VDD for standby power consumption. Also used for multiple SRAM arrays and reducing size of transistor.

Decreasing the device dimension limits the performance of MOSFET due to presence of impurity, increase in gate tunneling effect and also increasing p-n junction leakage current. There are two issues while designing SRAM cell: The cell area and its stability. The overall chip density can be determines by using its cell area. Whereas the operating conditions, sensitivity of the memory to process tolerance and the soft error rate determines the cell stability.

J. Lohstroh, K. Anami and F.J. Listhave analyzed that the stability of SRAM cell can be expressed by using static noise margin. Later on in 1987 E.Sevinch found the static noise margin of SRAM cells by using analytically as well as simulated result. In 2006, Evelyn Grossar proved stability of N curve for finding stability of read and write. In 2008, Zheng derived various methods for calculating the read and write stability. Jiajing Wang, Satyanand Nalam, and Benton H. Calhoun, analyzed various parameters affecting the performance of SRAM such as power consumption, static noise margin, effect of process, temperature and power supply. Benton H. Calhoun proved that transistor scaling and word line voltage modulation affects the stability.

# **6T SRAM WORKING AND FAILURE MECHANISM:**

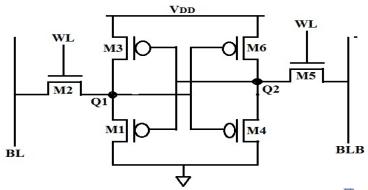

The given figure shows the basic six transistor cell formed for CMOS static random access memories. It also consist of two cross coupled CMOS inverters for storing one bit information. The two n type transistor i.e. M2 and M5 are known as access transistor which are connected to word line i.e. WL for accessing read and write operation through bit lines BL and BLB.

Figure 1: Basic 6T SRAM Cell

#### **6T SRAM WORKING**

Basically SRAM cell operates in Read, Write and Standby mode. In read mode the bit lines are pre charged to high level i.e. VDD and word line is selected by pulsing to the high level. At the cell storing side a logical low voltage i.e. '0', the bit line is discharged through the access pull down and access transistor for developing differential voltage across bit lines. For detecting the state of the cell, differential voltage should be high for sensing amplifier. Also differential voltage should not be too high to avoid the cross coupled inverters to flip in their state. For reducing the read disturbance, the cell ratio i.e. aspect ratio of the access transistor and pull down transistor should be large.

In write mode the bit lines are access in complementary voltage levels through a write driver and word line is selected. At the cell storing side the bit line voltage is logical low i.e. Of and through the access transistor, the internal storage nodes are discharged. By using cross coupled inverters the voltage gets raised on the opposite storage node. In short the restoring strength of the pullup transistor should be less than discharging strength of the access transistor. The ratio of pullup transistor to the strength of the pass gate transistor should be high to avoid write failure.

Whereas in standby mode, the cell stores the data indefinitely till it is connected to VDD. So in standby mode the word line is grounded.

# **FAILURE MECHANISMS:-**

We should take care of various SRAM cell parameters while designing SRAM to avoid failure due to read, write and hold case.

#### **READ FAILURE:**

Failure occurs while reading content of SRAM cell is known as a read failure. Consider that node X storing a logical low i.e. '0' and bit lines is discharging through M1 and M2. If the width of access transistor M2 is less than that of pull down transistor M1. Therefore, resistive divider is formed by using M1 and M2 which develops a voltage ripple. The cell state starts flip while reading only when a voltage ripple is greater than the switching threshold of the given inverter formed by M4 and M6. By rising the difference between the trip point of inverter related with the node storing logical high i.e. '1' and the voltage rise at the node storing logical low i.e. '0' can reduce the read failure in SRAM.

# WRITE FAILURE:

If the node storing logical high is unable to discharge through the access transistor during the word line turn on time causes write failure to the SRAM cell. By increasing the write access time with word line turn on time can reduce the write failure. But SRAM gets slower while increasing word line turn with write access.

#### **ACCESS FAILURE:**

If the voltage difference between the two bit lines at the time of firing sense amplifier is below the threshold voltage of the given sense amplifier causes access failure. This is caused due to the reduction of the bit line discharging current across the pull down resister and the pass transistor. Creating the stronger pull down transistor by decreasing the resistance in the discharge path can make a faster bit line discharge.

#### **HOLD FAILURE:**

A high leakage occurs at the pull down NMOS transistors connected to the node storing logical high causes hold failure. If the voltage at lower VDD is less than the trip point of the inverter storing logical low causes the cell flips in the hold mode. The hold failure can be minimized by reducing the leakage in the standby mode using high VT pull down transistor.

#### **CONCLUSION**

This paper analyzed various methods for finding the stability while designing 6T SRAM cell in read, write and standby mode. While designing various failure mechanisms such as read, write access and hold failure. Also various factors are consider such as power supply, cell ratio, bit lines, word line voltage and threshold voltage. The stability of SRAM in read mode increases with cell ratio whereas the pull up ratio affects only write mode. That means stability in write mode increases with decrease in pull up ratio. Also increase temperature decreases the stability of SRAM in read and standby mode.

# REFERENCE

- [1] S. S. Chopade, D. V. Padole, "Stability Analysis of 6T SRAM Cell for Nano scale FD-S0I Technology", ISBN: 978-1-4799-5364-6/14, 2014 IEEE.

- [2] S. S. Chopade, D. V. Padole, "Design of Double Gate MOSFET and FDSOLusing high k material for Nano scaled Circuits", ISBN: 978-1-4799-4075-2/14, 2014 IEEE.

- [3] Jawar Sing, Saraju P.Mohanty and Dhiraj K.Pradhan, Robust SRAM design and analysis", ISBN: 9781461408178, Springer, 2013

- [4] Jerome Mazurier, Olivier Weber, Francois Andrieu, Alain Toffoli, Olivier Rozeau, Thierry Poiroux, Fabienne Allain, Pierre Perreau, Claire Fenouillet-Beranger, Olivier Thomas, Marc Belleville, Olivier Faynot "On the variability in Planar FDSOI Technology: From MOSFET to SRAM Cells", IEEE Transactions on electron devices, Vol 58, No 8, August 2011.

- [5] F. J. List, "The static noise margin of SRAM cells," Digital Technical Papers, ESSCIRC, Sept. 1986, pp. 16–18. [6] Seevinck, F. List, and J. Lohstroh, "Static-noise margin analysis of MOS SRAM cells," IEEE J. Solid-State Circuits, Vol. SC-22, pp. 748–754, Oct. 1987.

- [7] Evelyn Grossar, Michele Stucchi, Karen Maex, 'Read Stability and Write-Ability Analysis of SRAM Cells for Nanometer Technologies," IEEE Journal Of Solid-State Circuits, Vol. 41, No. 11, November 2006.

- [8] Shivani Yadav, Neha Malik, Ashutosh Gupta and Sachin Rajput, "Low Power SRAM Design with Reduced Read/Write Time," International Journal of Information and Computation Technology. ISSN 0974-2239 Volume 3, Number 3 (2013), pp. 195-200

- [9] Aminul Islam and Mohd. Passan "Variability analysis of 6T and 7T SRAM cell in sub-45 technology," IIUM Engineering Journal, Vol 12, No. 1, 2011.

- [10] Ajay Gadhe, Ujwal Shirode, "Read stability and Write ability analysis of different SRAM cell structures," International Journal of Engineering Research and Applications (IJERA) ISSN: 2248-9622, Vol. 3, Issue 1, January -February 2013, pp. 1073-1078

- [11] Nahid Rahman, B. P. Singh, "Static-Noise-Margin Analysis of Conventional 6T SRAM Cell at 45nm Technology, International Journal of Computer Applications (0975 – 8887) Volume 66–No.20, March 2013.