# SIMULATION OF CASCADED H- BRIDGE MULTILEVEL INVERTER USING PD, POD, APOD TECHNIQUES

Sourabh Rathore, Mukesh Kumar Kirar and S. K Bhardwaj

Department of Electrical Engineering, MANIT, Bhopal

## ABSTRACT

Multilevel inverter (MLI) can achieve medium voltage high power efficiency inverters in industrial application. It can generate stepped waveform by reducing harmonic distortion with increase in the number of voltage level; a full bridge is known as H-bridge inverter because it shows alphabet 'H'. In this paper, Multicarrier PWM topologies and there Modulation schemes are discussed. Level Shifted [LS] Scheme is applied to the Cascade H-bridge multilevel inverter and the complete analysis of THD to 9 levels is done.

## **KEYWORDS**

Multilevel Inverter, Cascaded H-Bridge, Multicarrier (PWM) topologies.

# **1. MULTILEVEL INVERTER**

The inverter is a power electronic circuit which converts the DC to AC power, used in power backup at home [1]. Like motor, radio etc. Now days Multilevel Inverters are used in high power switching application [2-3].Multilevel Inverter consists of several switches, used in industrial applications, Railway Traction Drives and Electrical Vehicle etc. [4].

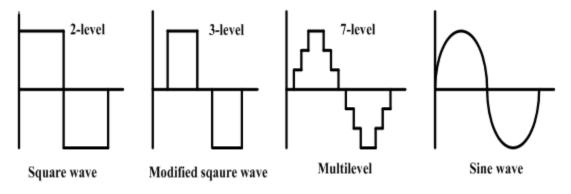

Figure 1. Inverter Output Waveform [5]

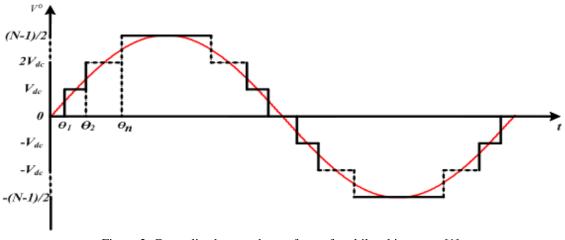

Figure 2. Generalized stepped waveform of multilevel inverters [1]

## **1.1 Classification of Multilevel Inverter**

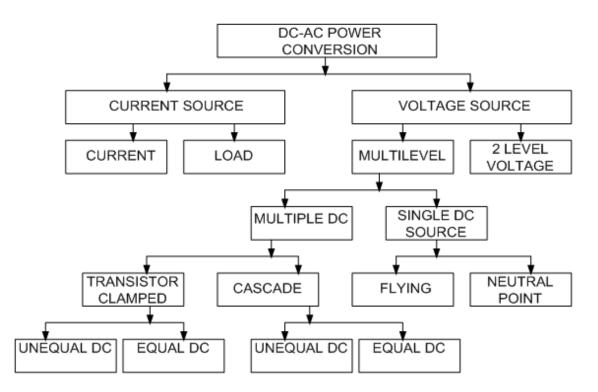

Figure 3 Shows Inverter is classified into Cascade H-Bridge Multilevel inverter (CHB-MLI), Flying Capacitor Multilevel inverter (FC-MLI), Diode Clamped inverter (NPC-MLI) [2-3].

Figure 3. Classification of Multilevel Inverter [1-3]

## 1.2 Main Topologies of MLI

- Diode Clamped Inverter

- Flying Capacitor

- Cascaded H-Bridge Inverter

#### 1.2.1 Diode Clamped Multilevel Inverter (DC-MLI)

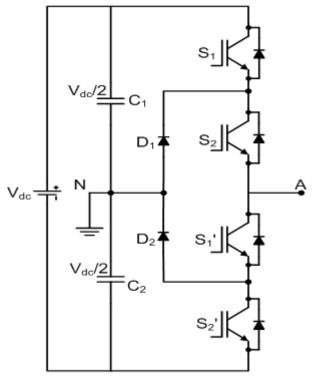

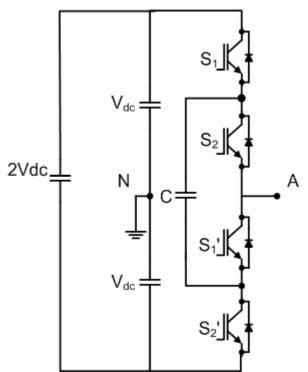

Figure 4 shows 3 level Diode clamped inverter also known as Neutral Point Clamped Inverter (NPC). The maximum output voltage is half of the input DC voltage. To remove this problem, simple control technique is applied i.e. increasing the component like switches and diodes [1-5].

Figure 4 3-level Diode-clamped inverter

Table 1. Switching Pattern of diode-Clamped Multilevel Inverter

| Output                              | Switch states |       |         |       |  |

|-------------------------------------|---------------|-------|---------|-------|--|

| Output<br>Voltage<br>$V_o = V_{an}$ | $S_1$         | $S_2$ | $S_{I}$ | $S_2$ |  |

| $V_{dc}/2$                          | 1             | 1     | 0       | 0     |  |

| 0                                   | 0             | 1     | 1       | 0     |  |

| $-V_{dc}/2$                         | 0             | 0     | 1       | 1     |  |

## Advantages:

- The Control technique is simple.

- When the number of levels increases the distortion content is reduced.

#### **Disadvantages:**

• When the number of level is high more clamping diodes are used.

#### 1.2.2 Flying Capacitor Multilevel Inverter (FC-MLI)

Figure 5 shows the 3 level Flying Capacitor Multilevel, also known as Capacitor Clamped Inverter. Clamping diodes are replaced by flying capacitors. It can control both active and reactive power flow [5-12].

Figure 5 3-level flying capacitor inverter

| Output                              | Switch states |       |       |       |  |

|-------------------------------------|---------------|-------|-------|-------|--|

| Output<br>Voltage<br>$V_o = V_{AN}$ | $S_1$         | $S_2$ | $S_1$ | $S_2$ |  |

| $V_{dc}$                            | 1             | 1     | 0     | 0     |  |

| 0                                   | 1             | 0     | 1     | 0     |  |

| 0                                   | 0             | 1     | 0     | 1     |  |

| $-V_{dc}$                           | 0             | 0     | 1     | 1     |  |

### Advantages:

- Similar to NPC inverter to avoid the needs for filters.

- A Large amount of packing capacity.

#### **Disadvantages:**

- Inverter control can be complicated.

- Switching losses are high.

#### 1.2.3 Cascaded H-Bridge Multilevel Inverter (CHB-MLI)

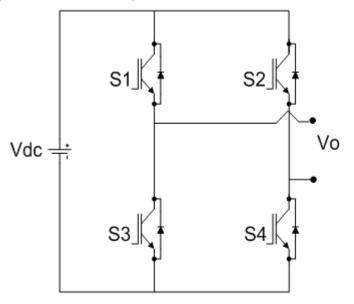

Figure 6 shows the 3 level CHB MLI consist of single H-bridge combine with a series of the power conversion cell. Cascaded H-Bridge Multilevel Inverter is better than the diode clamped inverter and flying capacitors inverter, it requires less number of the component in each switching levels. In Cascade H-Bridge Multilevel Inverter, the grouping of switches and capacitors is called H-bridge consisting of isolated DC Voltage source [10].

Figure 6 3-level cascaded H-bridge inverter

| Table 3. | Switching | Pattern of | Cascade | H-Bridge | Multilevel | Inverter |

|----------|-----------|------------|---------|----------|------------|----------|

|----------|-----------|------------|---------|----------|------------|----------|

| Output                              | Switch states  |       |       |                       |  |

|-------------------------------------|----------------|-------|-------|-----------------------|--|

| Output<br>Voltage<br>$V_o = V_{AN}$ | S <sub>1</sub> | $S_2$ | $S_3$ | <i>S</i> <sub>4</sub> |  |

| $V_o - V_{AN}$<br>$V_{dc}$          | 1              | 0     | 0     | 1                     |  |

| 0                                   | 1              | 1     | 0     | 0                     |  |

| 0                                   | 0              | 0     | 1     | 1                     |  |

| $-V_{dc}$                           | 0              | 1     | 1     | 0                     |  |

## Advantages:

- Reduced THD.

- As Compare to Diode clamped and Flying capacitor inverter it can required less number of components in each level.

## **Disadvantages:**

• It needs isolated DC voltage sources.

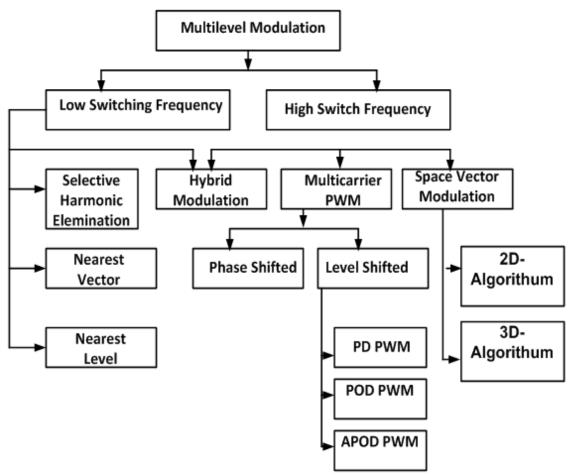

## **2. MODULATION TECHNIQUES**

Modulation Technique is Low and High switching Frequency fort high switching frequency is considered above 1 KHz [13].

Figure 7. Classification of Modulation Technique

## 2.1 Multicarrier PWM

Multiple Pulse Width Modulation Technique is used in three level or more than three levels. These are classified into two types: - Level Shift, Phase Shift.

## 2.1.1 Level Shifted PWM (LS-PWM)

N-1 carrier signals are used which are vertically shifted to each other. A level-shifted PWM can be classified in three types [14-16-17-18].

• **Phase Disposition (PD-PWM):** In Phase Disposition all the carrier signals are in same phase.

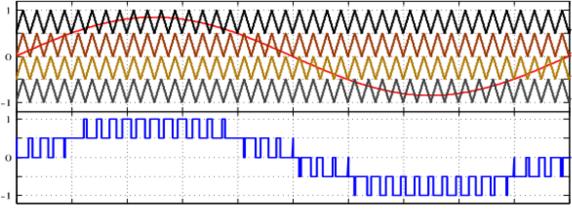

Figure 8 PD-PWM

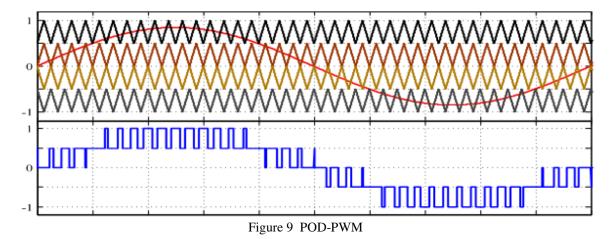

• **Phase Opposition Disposition (POD-PWM):** In Phase Opposition Disposition all the carrier signals above the zero are out of phase with those below the zero by 180°.

• Alternative Phase opposition Disposition (APOD-PWM): In Alternate Phase Opposition Disposition all the adjacent carrier signals are out of phase by 180°.

Figure 10 APOD-PWM

# **3. SIMULATION AND RESULTS**

| S.No | PWM Technique                          | No of Level | THD %  |

|------|----------------------------------------|-------------|--------|

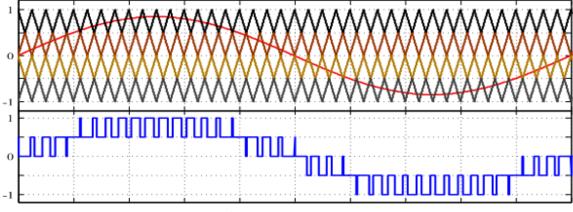

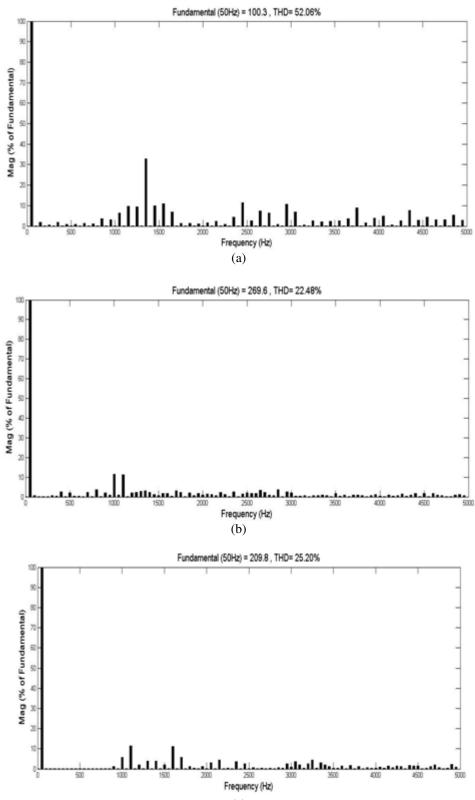

| 1.   | Phase Disposition                      | 3 Level     | 52.06% |

| 2.   | Phase Opposition Disposition           | 3 Level     | 54.17% |

| 3.   | Alternate Phase opposition Disposition | 3 Level     | 54.17% |

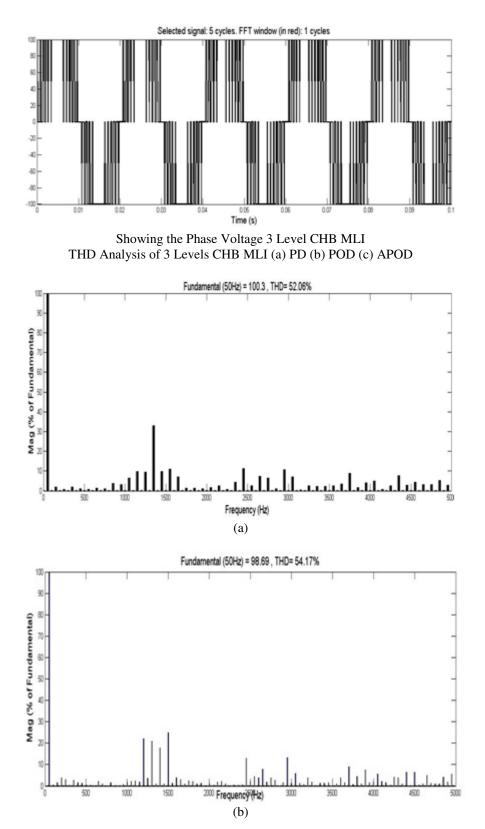

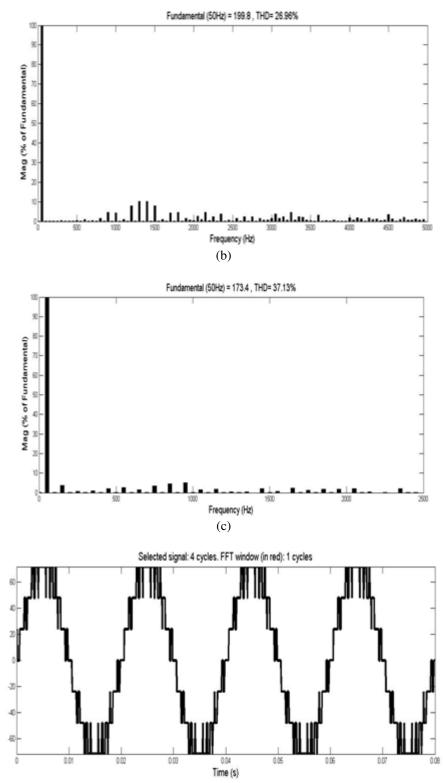

| 4.   | Phase Disposition                      | 5 Level     | 26.69% |

| 5.   | Phase Opposition Disposition           | 5 Level     | 26.96% |

| 6.   | Alternate Phase opposition Disposition | 5 Level     | 37.13% |

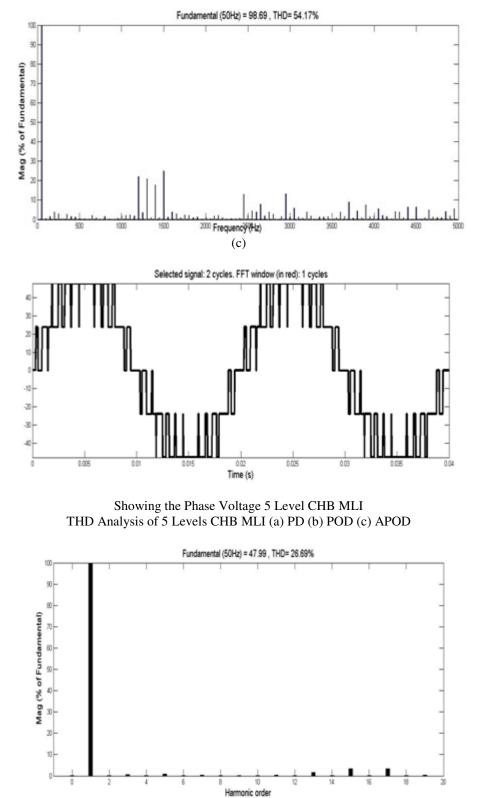

| 7.   | Phase Disposition                      | 7 Level     | 18.05% |

| 8    | Phase Opposition Disposition           | 7 Level     | 22.48% |

| 9.   | Alternate Phase opposition Disposition | 7 Level     | 25.20% |

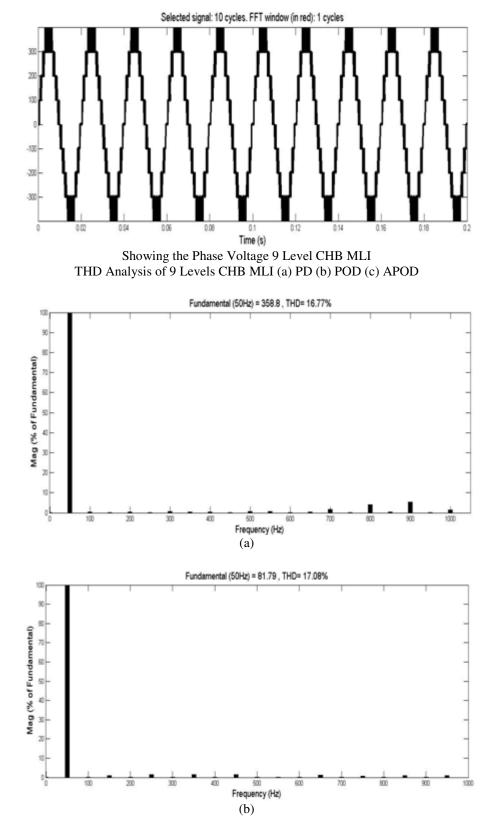

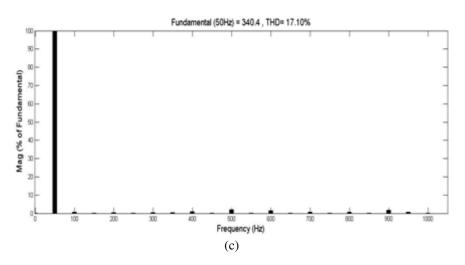

| 10.  | Phase Disposition                      | 9 Level     | 16.77% |

| 11.  | Phase Opposition Disposition           | 9 Level     | 17.08% |

| 12.  | Alternate Phase opposition Disposition | 9 Level     | 17.10% |

Table 4. THD Comparisons of PWM Technique

35

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 3, September 2015

(a)

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 3, September 2015

Showing the Phase Voltage 7 Level CHB MLI THD Analysis of 7 Levels CHB MLI (a) PD (b) POD (c) APOD

(c)

38

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 3, September 2015

Electrical & Computer Engineering: An International Journal (ECIJ) Volume 4, Number 3, September 2015

## **4.** CONCLUSION

In this paper has been Discuss the Cascade H-Bridge Topology using Phase Disposition, Phase opposition Disposition, and Alternate Phase opposition Disposition are compared. The three techniques it can conclude that the Phase Disposition Topology is better among the three topologies. Simulation results show that it can see that when we increase the number harmonics content will be reduced.

#### REFERENCES

- [1] Rodriguez, J.; Jih-Sheng Lai; Fang ZhengPeng; , "Multilevel inverters: a survey of topologies, controls, and applications," Industrial Electronics, IEEE Transactions on , vol.49, no.4, pp. 724-738, Aug 2002.

- [2] Jih-Sheng Lai; Fang ZhengPeng; , "Multilevel converters-a new breed of power converters," Industry Applications Conference, 1995. Thirtieth IAS Annual Meeting, IAS '95., Conference Record of the 1995 IEEE , vol.3, no., pp.2348-2356 vol.3, 8-12 Oct 1995.

- [3] Panagis, P.; Stergiopoulos, F.; Marabeas, P.; Manias, S.; , "Comparison of state of the art multilevel inverters," Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, vol., no., pp.4296-4301, 15-19 June 2008.

- [4] Malinowski, M.; Gopakumar, K.; Rodriguez, J.; Pérez, M.A.; , "A Survey on Cascaded Multilevel Inverters," Industrial Electronics, IEEE Transactions on , vol.57, no.7, pp.2197-2206, July 2010.

- [5] Tolbert, L.M.; Fang ZhengPeng; Habetler, T.G.; , "Multilevel converters for large electric drives," Industry Applications, IEEE Transactions on , vol.35, no.1, pp.36-44, Jan/Feb 1999.

- [6] Fang ZhengPeng; , "A generalized multilevel inverter topology with self-voltage balancing," Industry Applications, IEEE Transactions on , vol.37, no.2, pp.611-618, Mar/Apr 2001.

- [7] T. A. Meynard and H. Foch, "Multi-level choppers for high voltage applications," in Proc. Eur. Conf. Power Electron. Appl., 1992, vol. 2, pp. 45-50.

- [8] Liu, Y.; Luo, F.L.; , "Multilevel inverter with the ability of self-voltage balancing," Electric Power Applications, IEE Proceedings , vol.153, no.1, pp. 105- 115, 1 Jan. 2006.

- [9] A. Rufer, M. Veenstra, and K. Gopakumar, "Asymmetric Multilevel Converter for High Resolution Voltage Phasor Generation", in Proceedings of the European Power Electronics and Applications Conference (EPE 1999), 1999.

- [10] F. Z. Peng, J. S. Lai, J. W. McKeever, J. VanCoevering, "A Multilevel Voltage Source Inverter with Separate DC Sources for Static Var Generation," IEEE Transactions on Industry Applications, vol. 32, no. 5, Sept. 1996, pp. 1130-1138.

- [11] L. M. Tolbert, F. Z. Peng, T. G. Habetler, "Multilevel Inverters for Electric Vehicle Applications," IEEE Workshop on Power Electronics in Transportation, Oct 22-23, 1998, Dearborn, Michigan, pp. 1424-1431.

- [12] P. Steimer and M. Manjrekar, "Practical Medium Voltage Converter Topologies for High Power Applications", in Proceedings of the IEEE Industry Applications Society Annual Meeting (IAS), Vol. 3, 2001, pp. 1723–1730.

- [13] Palanivel, P.; Dash, S.S.; , "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," Power Electronics, IET , vol.4, no.8, pp.951-958, September 2011.

- [14] M. Veenstra and A. Rufer, "PWM-Control of Multi-Level Voltage-Source Inverters", in Proceedings of the IEEE Power Electronics Specialists Conference (PESC), Vol. 3, 2000, pp. 1387-1393.

- [15] Calais, M.; Borle, L.J.; Agelidis, V.G.; , "Analysis of multicarrier PWM methods for a singlephase five level inverter," Power Electronics Specialists Conference, 2001. PESC. 2001 IEEE 32nd Annual, vol.3, no., pp.1351-1356 vol. 3, 2001

- [16] Sreenivasarao, D.; Agarwal, P.; Das, B.; , "A carrier-transposed modulation technique for multilevel inverters," Power Electronics, Drives and Energy Systems (PEDES) & 2010 Power India, 2010 Joint International Conference on , vol., no., pp.1-7, 20-23 Dec. 2010.

- [17] Gupta, K.K.; Jain, S.; , "Topology for multilevel inverters to attain maximum number of levels from given DC sources," Power Electronics, IET , vol.5, no.4, pp.435-446, April 2012.

- [18] McGrath, B.P.; Holmes, D.G.; , "A comparison of multicarrier PWM strategies for cascaded and neutral point clamped multilevel inverters," Power Electronics Specialists Conference, 2000. PESC 00. 2000 IEEE 31st Annual , vol.2, no., pp.674-679 vol.2, 2000.

#### AUTHOR

Sourabh Rathore was born in Bhopal, India in 19 may 1991. He has received BE (Electrical) degree From Sagar Institute Research Technology and Science Bhopal in 2012 and pursuing his M.Tech degree in Power System from MANIT Bhopal.

Mukesh Kumar Kirar was born in Narsinghpur India in 06 Feb1983.He received the BE (Electrical) degree from Government Engg. College, Ujjain India in 2006 and M.Tech (Power System) in 2008 from MANIT Bhopal and PhD in 2014 from MANIT Bhopal. He is currently working as an assistant professor In the Department of Electrical Engineering, MANIT, Bhopal, India. His field of Interests are power system stability and control, transformer and machines.

S.K.Bharadwaj was born in India He received the BE (Electrical) degree from I.T.B.H.U. Varanasi India In 1975 and M.Tech (Power System) in 1978 from REC Kurukshetra.and PhD (Application of self Tuning Strategies to electric Drive) in 2000 from Barkatullah University. He is currently working as a professor in the Department of Electrical Engineering, MANIT, and Bhopal, India. He has 9 research papers in National Conference and 7 research papers in International Conference His field of Interest are power system and energy conservation.