# A Study of Recent Contribution on Simulation Tools for Network-on-Chip

Muthana Saleh Alalaki, Michael Opoku Agyeman

**Abstract**—The growth in the number of Intellectual Properties (IPs) or the number of cores on the same chip becomes a critical issue in System-on-Chip (SoC) due to the intra-communication problem between the chip elements. As a result, Network-on-Chip (NoC) has emerged as a system architecture to overcome intra-communication issues. This paper presents a study of recent contributions on simulation tools for NoC. Furthermore, an overview of NoC is covered as well as a comparison between some NoC simulators to help facilitate research in on-chip communication.

*Keywords*—Network-on-Chip, System-on-Chip, embedded systems, computer architecture.

### I. INTRODUCTION

THE significant improvement in scaling and nanoscale technologies will make it possible to build SoCs with billions of transistors and hundreds of cores [1], [2]. Thus, a significant number of new application developments in the field of consumer electronics, telecommunications, and system platforms are expected [3]. On the other hand, these systems will need powerful communication architectures in order to achieve different purposes. Moreover, these architectures should provide templates reusability to reduce the cost involving in design productivity [4]. The current SoCs, where the sustainable communication templates are used, primarily depend on the bus approach which includes either a hierarchy of buses or a single shared bus [5]. On the other hand, this approach has faced additional constraints which restrain the future of SoCs.

Firstly, the operating frequency of buses reduces the growth in the number of cores connected. Secondly, low-level scalability with the system size when using a hierarchy of buses of a single shared bus. Thirdly, the energy consumption increases when the wire length increases with the increase in circuit size. Finally, only one communication is allowed at a time by a bus or even in a hierarchic bus architecture [6].

To achieve the major requirements of future SoC such as scalability, reusability, parallelism while dealing with clock distribution and power constraints, a new paradigm, which is called NoCs, has emerged. It is a switching network which has been proposed as an alternative to interconnected cores in SoCs. This paper conducts a study of recent contributions of simulation tools for NoC.

The rest of the paper is structured as follows: Section II provides an overview of the NoC concepts. Section III

discusses the recently proposed simulation tools for NoCs, and Section IV concludes the paper.

#### II. NoC

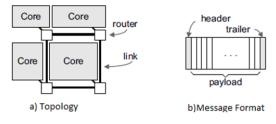

NoC (also known as packet-switched on-chip interconnection networks) is one of the agitated approaches in on-chip communication. NoCs are multi-hop interconnections networks that are integrated on one single chip [7], [8]. Table I shows a qualitative comparison between NoCs and conventional buses. NoC consists of a number of routers which are structurally interconnected by point-to-point channels as shown in Fig. 1. Each of these routers is connected to its neighbor as well as a processing core using a set of ports (known as local ports or terminals) [1].

The model of communication in NoC is called message passing because the processing cores connected to the network ports are communicating by exchanging messages, and each of these messages consists of a header, payload, and trailer.

Fig. 1 NoC concepts [1]

NoC can be characterized by its topology as well as various strategies used for routing, switching, flow control, buffering, and arbitration. The network topology describes how nodes and channels are arranged into a graph, and the routing describes the process of choosing a path in the graph for each message. Flow control contends with the channel capacity, and switching is the technique of removing the data from the input channel to the output channel. The scheduling task of the use of channel is managed by the arbitration, while the unscheduled messages are stored by the buffering task [10], [11].

## A. Topologies

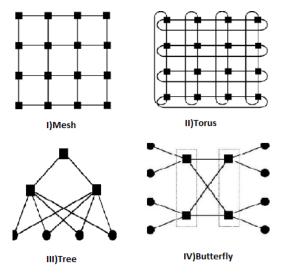

The topologies of NoCs are significant when designing NoCs because the design of any router is based on it. Many topologies have been categorized into regular and irregular depending on the distribution process of routers within the network [9]. The most well-known topologies are mesh, torus, binary tree, ring, bus, butterfly, etc. (Fig. 2) [12], [13]:

Michael Opoku Agyeman is with the Department of Computing and Immersive Technologies, The University of Northampton, UK (e-mail: Michael.OpokuAgyeman@northampton.ac.uk).

| TABLE I                      |  |

|------------------------------|--|

| NOC AND BUSES COMPARISON [9] |  |

| NoCs                                                                                                                                  | Buses                                                                                                                 |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--|--|--|

| Upgrading is significant for designers to develop a new concept.                                                                      | Simple and understandable concept.                                                                                    |  |  |  |

| The bandwidth increases with the network size                                                                                         | Limitation of bandwidth and all elements are sharing it.                                                              |  |  |  |

| Distributed routing decisions.                                                                                                        | Blockages due to delays generated by arbitrations at the bus<br>especially when the number of masters is significant. |  |  |  |

| Good and fast test coverage.                                                                                                          | Slow and problematic regarding testing.                                                                               |  |  |  |

| Delay transitions can be used by the data transfer because it has point-to-point connections.                                         | Managing the time is difficult.                                                                                       |  |  |  |

| Point-to-point interconnections of each element for all sizes of the network and the local performance are not degraded when scaling. | Parasitic capacitance will be added by each item which increases<br>the electrical performance degradation.           |  |  |  |

- a) **Mesh**: It consists of a number of columns and rows where routers are located in the intersection between to links, and the computational resources are close to the routers.

- b) Torus: It is a basic mesh network with some improvements where the heads and the tails of the columns are connected, and the left and right sides of the rows are connected as well. As a result, it requires more minimal routers and has better path diversity compared to the mesh network.

- c) **Tree**: In this topology, nodes represent the routers, and leaves represent the computational resources.

- d) Butterfly: It is a unidirectional (packets are routed from the left side which is the input to the right side which is the output) or bidirectional (all the inputs and outputs are located on the same side) and it uses a deterministic routing.

Fig. 1 NoC topologies

## B. NoC Architecture

NoC normally consists of at least three fundamental elements [10], [14]. Network adapters (known as Network Interface) are used to connect cores to the NoC and convert the bus protocol (used by Processing Elements) into network protocol (used by switches). Routing nodes are used to direct packets from source to destination based on the chosen protocol and they contain the routing strategies. Links connect the routing nodes. They consist of one or more than one logical or physical channels for data transmission as well as

connectivity between network adapters and routing nodes and between the routing nodes themselves.

#### C. Routing

Routing is the transmission of data (packets) from source to destination using defined routing strategies. In literature, the routing schemes have been classified based on several criteria [15], [16]. Source routing is a schema where the source node chooses the entire path before sending the packet to the destination. The main disadvantage of this approach is that the packet size will be increased because each one of the packets should carry the routing information through the transmission. Furthermore, the path cannot be updated or changed once the packet left the source. To solve this problem, distributed routing is used where the routing table is accessed to determine the next hop (router) to forward the packet. On the other hand, routing algorithms are also classified, based on making the decision to choose certain paths among a set of available paths, into deterministic, adaptive, and oblivious. The source and destination address completely determine the path between which is the deterministic routing algorithm. The state of the network is important to make the routing decisions, which is the adaptive routing algorithm. The better data flow can be achieved with this algorithm, but it might generate complicated nodes [17]. In oblivious routing algorithm, the state of the network is not necessary to choose the route between the source and destination nodes. There are some other routing algorithms proposed in [18]-[22], but the main purpose of this paper is to present a study of simulation tools, not the routing algorithms.

### III. NOC SIMULATION TOOLS

The NoC design space is high-dimensional and very large and includes topology optimization, congestion control methodologies, routing algorithms, the number of buffers, link capacities, and virtual channels per link, etc. In addition, the research area is expanding, which means more ideas, techniques as well as new architectures will be proposed. Thus, the demand for simulation tools for evaluating different features of different NoCs proposals and designs increases. In this section, we have explained different simulation tools for NoC. Table II shows a comparison between these simulators and other well-known simulation tools.

## A. BookSim

BookSim is a cycle-accurate and detailed simulator

designed for NoCs as well as modeling interconnection networks for different systems. The first version of it is called BookSim1, which was a generic simulator and not designed for an on-chip environment in specific. It has been used to study different network designs including routing, topology, flow control, quality-of-services, router microarchitecture as well as some new technologies like nanophotonic [23], [24]. In terms of system simulation, it provides the required flexibility in high-level simulation tools. With regard to network design, all key elements of a network router detailed modeling are provided by BookSim. Furthermore, it is intended to facilitate the modifications and addition of brand new network features. On the other hand, some of the topologies and advanced features proposed for on-chip networks are not supported by original BookSim. Thus, BookSim2 is developed to break the limitations as well as to provide models of inter-router channel delay, traffic models, router microarchitecture, highly accurate network model, and actual hardware behavior [25].

### B. DARSIM

DARSIM is a cycle-level, parallel, and a highly configurable simulator for NoC and it supports different virtual channel (VC) allocation and various routing algorithms due to its extremely parametrized table-based design. It can be driven by application traces or synthetic patterns or a built-in MIPS- based multicore simulator. Moreover, it is a parallel (multithreaded) simulation engine that splits the tasks equally between the available processor cores as well as cycle accurate precision. Furthermore, it offers periodic synchronization and permits tradeoffs between high speed and perfect accuracy. In addition, most of the hardware parameters can be configured, including bandwidth, geometry, pipeline depth, and crossbar dimensions [26].

## C. Gem5

Gem5 is one of the emerged simulators that overcome most of the limitations that faced the computer architecture researchers. It is available for many researchers with a wide range of systems evaluation capabilities as well as clean interface and modularity commitment. In [27], its infrastructure is a combination of the best features of both GEMS [28] and M5 simulator [29]. This means that it supports most the features of these two simulators such as multiple ISAs, highly configurable, diverse CPU models from M5 and flexible, detailed system, including multiple cache coherence protocols as well as interconnected models from GEMS. In addition, it supports various commercials ISAs (ALPHA, MUPS, ARM, SPARK, X86, and Power), involving booting Linux on ALPHA, x86, and ARM. Moreover, high level of collaboration is one the aspects of this simulator provided by the Gem5 community because it is a communityled project and open source. Furthermore, additional features such as parallelization and a first-class power model which might be added soon. Many versions of Gem5 simulator have emerged such as Gem5-gpu [30] and Gem5v [31].

## D. NOXIM

Noxim simulator is developed using a C++ system description library called SystemC. The reason behind choosing SystemC is the essential aim of Noxim project which includes scalable performance and allowing expansion easiness while the cycle-accurate simulation is still maintained [32]. It also supports several parameters of the configuration space which are the workload, topology and structure, simulation, and dynamic behavior. In addition, it is an open source simulator with the capabilities of cycle accurate platform, performance analysis, and power figures of both emerging Wireless NoC (WiNoC) and conventional wired based NoC [33]. Although it only supports mesh topology, it supports various traffic patterns, different routing algorithm, hotspot injection, as well as simple source code [41]. In [33], A new version of this simulator has been proposed, which supports heterogeneous wired/wireless NoC architectures. Furthermore, Access Noxim is a modified version of the original NoC that supports 3D NoC system, Beltway routing, adaptive routing (Proactive thermal budget and Thermalaware buffer allocation [42]) [43].

## E. Heterogeneous NoC Simulator (HNOCS)

It is considered as the first introduced heterogeneous NoCs simulator to provide modeling of HNoCs with different link capacities as well as the number of virtual channels per unidirectional port and it is based on OMNeT++ [32]. This simulator supports parallelism (by changing the link to unidirectional), different Quality-of-Service (QoS) mechanisms, various arbitrary technologies, many routing protocols as well as power estimation. It supports three types of routers which are asynchronous, synchronous and synchronous virtual output queue (VoQ). In addition, it is open source, fully parameterized, scalable, modular and extendable for NoC. Moreover, sufficient set of statistical measurements is provided at the packet level and the flit such as throughput, end-to-end delay, transfer latencies, VC acquisition latencies, etc. [34].

## F. Sniper

Sniper is one of the multi-core simulators based on Graphite simulation infrastructure and the interval core model. It is considered to become the next generation high speed, parallel and accurate X86 simulator for different heterogeneous and homogeneous multi-core architectures. The primary feature of this simulator is the core model which is depended on interval simulation. It is highly recommended for uncore as well as system-level studies which need more details compared to the traditional one-IPC models. SPLASH-2 benchmarks have been used to evaluate the performance and scalability of this simulator. As an added feature, it provides Python and SimAPI interfaces for controlling and monitoring its behavior at runtime [40].

| TABLE II                  |  |  |  |  |  |  |

|---------------------------|--|--|--|--|--|--|

| NOC SIMULATORS COMPARISON |  |  |  |  |  |  |

| Simulator | Year | Benchmark | Framework | Open-source | Topologies                  | Heterogeneous<br>support | GUI | Synchronous<br>/asynchronous | Ref  |

|-----------|------|-----------|-----------|-------------|-----------------------------|--------------------------|-----|------------------------------|------|

| BookSim   | 2010 | -         | C++       | +           | Many                        | -                        | -   | Synchronous                  | [25] |

| DARSIM    | 2010 | +         | C++       | +           | All                         | -                        | -   | Synchronous                  | [26] |

| Gem5v     | 2015 | +         | C++       | +           | Many                        | -                        | -   | Synchronous                  | [31] |

| NOXIM     | 2010 | -         | SystemC   | +           | Mesh                        | +                        | -   | Synchronous                  | [33] |

| HNOCS     | 2013 | -         | OMNet++   | +           | All                         | +                        | +   | Both                         | [34] |

| Gpnocsim  | 2007 | -         | Java      | +           | All                         | -                        | -   | Synchronous                  | [35] |

| gem5-gpu  | 2015 | +         | C++       | +           | All                         | +                        | -   | Synchronous                  | [30] |

| AdapNoC   | 2016 | -         | C++       | -           | Mesh Torus<br>(virtualized) | -                        | -   | Synchronous                  | [36] |

| ENoCS     | 2015 | -         | Java      | +           | Many                        | +                        | +   | Synchronous                  | [37] |

| MPSoCSim  | 2015 | +         | SystemC   | +           | Mesh                        | +                        | +   | Synchronous                  | [38] |

| DART      | 2014 | +         | SystemC   | +           | All                         | +                        | +   | Synchronous                  | [39] |

| Sniper    | 2015 | +         | SystemC   | +           | Many                        | +                        | +   | Synchronous                  | [40] |

#### IV. CONCLUSION

In this paper, we have presented an overview of NoC concepts which are significant in SoCs design. Furthermore, a study of the key but recent simulation tools dedicated for NoC is provided. Particularly, the paper highlights a comparison of these simulation tools to help researchers and developers to decide on the most suitable simulation tool for their research proposals and designs.

#### References

- C. Zeferino and A. Susin, "SoCIN: a parametric and scalable networkon-chip," in Integrated Circuits and Systems Design, 2003. SBCCI 2003. Proceedings. 16th Symposium on, Itajai, 2003.

- [2] N. Genko, D. Atienza, G. D. Micheli, L. Benini, J. Mendias, R. Hermida and F. Catthoor, "A novel approach for network on chip emulation," in Circuits and Systems, 2005. ISCAS 2005. IEEE International Symposium on, Bologna, 2005.

- [3] P. C. Diniz, Reconfigurable Computing: Architectures, Tools and Applications, Mangaratiba: Springer Science & Business Media, 2007.

- [4] S. Kumar, A. Jantsch, J.-P. Soininen, M. Forsell, M. Millberg, J. Oberg, K. Tiensyrja and A. Hemani, "A network on chip architecture and design methodology," in VLSI, 2002. Proceedings. IEEE Computer Society Annual Symposium on, Pittsburgh, 2002.

- [5] E. Salminen, V. Lahtinen, K. Kuusilinna and T. Hamalainen, "Overview of bus-based system-on-chip interconnections," in Circuits and Systems, 2002. ISCAS 2002. IEEE International Symposium on, Phoenix-Scottsdal, 2002.

- [6] R. Hofmann and B. Drerup, "Next Generation CoreConnect (TM) Processor Local Bus architecture," in Annual IEEE International ASIC/SOC Conference, Rochester, 2002.

- [7] J. Henkely, W. Wolfz and S. Chakradhary, "On-chip networks: A scalable, communication-centric embedded system design paradigm," in VLSI Design, 2004. Proceedings. 17th International Conference on, Princeton, 2004.

- [8] L. Benini and D. Bertozzi, "Network-on-chip architectures and design methods," in IEE Proceedings - Computers and Digital Techniques, 2005.

- [9] P. Guerrier and A. Greiner, "A gentic architecture for on-chip packetswitched interconnections," in Design, Automation, and Test in Europe, New York, 2000.

- [10] G. D. Micheli, C. Seiculescu, S. Murali, L. Benini, F. Angiolini and A. Pullini, "Networks on Chips: From research to products," in Design Automation Conference (DAC), 2010 47th ACM/IEEE, Lausanne, 2010.

- [11] A. Agarwal, C. Iskander and R. Shankar, "Survey of Network on Chip (NoC) Architectures & Contributions," Journal of Engineering, Computing and Architecture, vol. 4, no. 1, 2009.

- [12] N. Ashokkumar, P. Nagarajan and S.Ravanaraja3, "Survey Exploration of Network-on-Chip Architecture," Dindigul, 2009.

- [13] G. D. Micheli and L. Benini, Networks on Chips: Technology and Tools, Academic Press, 2006.

- [14] T. Bjerregaard and S. Mahadevan, "A survey of research and practices of Network-on-chip," ACM Computing Surveys (CSUR), vol. 38, no. 1, 2006.

- [15] G. Ascia, V. Catania, M. Palesi and D. Patti, "Implementation and Analysis of a New Selection Strategy for Adaptive Routing in Networkson-Chip," in IEEE Transactions on Computers, 2008.

- [16] P. Pande, C. Grecu, A. Ivanov, R. Saleh and G. D. Micheli, "Design, synthesis, and test of networks on chips," IEEE Design & Test of Computers, vol. 22, no. 5, pp. 404 - 413, 2005.

- [17] A. B. Achballah and S. B. Saoud, "A Survey of Network-On-Chip Tools," International Journal of Advanced Computer Science and Applications (IJACSA), vol. 4, no. 9, 2013.

- [18] G.-M. Chiu, "The Odd-Even Turn Model for Adaptive Routing," IEEE Transactions on Parallel and Distributed Systems, vol. 11, no. 7, pp. 729 - 738, 2000.

- [19] D. Linder and J. Harden, "An adaptive and fault tolerant wormhole routing strategy for k-ary n-cubes," IEEE Transactions on Computers, vol. 40, no. 1, pp. 2-12, 2002.

- [20] J. Wang, X. Wang, L. Huang, T. Mak and G. Li, "A Fault-Tolerant Routing Algorithm for NoC Using Farthest Reachable Routers," in IEEE 11th International Conference on Dependable, Autonomic and Secure Computing, Chengdu, 2013.

- [21] B. B. Sayankar, P. Agrawal and S. S. Dorle, "Routing Algorithms for NoC Architecture: A Relative Analysis," in 6th International Conference on Emerging Trends in Engineering and Technology, Nagpur, 2013.

- [22] Y. Dong, Z. Lin and T. Watanabe, "An efficient hardware routing algorithms for NoC," in IEEE Region 10 Conference, Fukuoka, 2010.

- [23] Y. Pan, P. Kumar, J. Kim, G. Memik, Y. Zhang and A. Choudhary, "Firefly: illuminating future network-on-chip with nanophotonics," in Proceedings of the 36th International Symposium on Computer, 2009.

- [24] N. Jiang, J. Kim and W. J. Dally, "Indirect adaptive routing on large scale interconnection networks," in Proceedings of the 36th International Symposium on Computer Architecture, 2009.

- [25] N. Jiang, J. Balfour, D. U. Becker, B. Towles, W. J. Dally, G. Michelogiannakis and J. Kim, "A detailed and flexible cycle-accurate Network-on-Chip simulator," in Performance Analysis of Systems and Software (ISPASS), 2013 IEEE International Symposium on, Austin, 2013.

- [26] M. Lis, K. S. Shim, M. H. Cho, P. Ren, O. Khan and S. Devadas, "DARSIM: a parallel cycle-level NoC simulator," in IEEE Asian Solid-State Circuits Conference, Saint Malo, 2010.

- [27] N. Binkert, B. Beckmann, G. Black, S. K. Reinhardt, A. Saidi, A. Basu, J. Hestness, D. R. Hower, T. Krishna, S. Sardashti, R. Sen, K. Sewell, M. Shoaib, N. Vaish and D. A. Wood, "The gem5 Simulator," ACM SIGARCH Computer Architecture News, vol. 39, no. 2, pp. 1-7, 2011.

- [28] D. J. S., B. M. B., M. R. M., M. X., A. R. A., K. E. M., M. D. H., D. A. W. and Milo M.K. Martin, "Multifacet's General Execution-driven Multiprocessor Simulator (GEMS) Toolset," Computer Architecture News (CAN), vol. 33, no. 4, pp. 92 99, 2005.

- [29] N. L. Binkert, R. G. Dreslinski, L. R. H. K. T. Lim, A. G. Saidi and S. K. Reinhardt, "The M5 Simulator: Modeling Networked Systems," in IEEE Micro, 2006.

- [30] J. Power, J. Hestness, M. S. Orr, M. D. Hill and D. A. Wood, "gem5-

477

gpu: A Heterogeneous CPU-GPU Simulator," IEEE Computer Architecture Letters, vol. 14, no. 1, pp. 34 - 36, 2014.

- [31] S. H. Nikounia and S. M. author, "Gem5v: a modified gem5 for simulating virtualized systems," The Journal of Supercomputing, vol. 71, no. 4, p. 1484–1504, 2015.

- [32] M. Amoretti, "Modeling and Simulation of Network-on-Chip Systems with DEVS and DEUS," Scientific World Journal, 2014.

- [33] V. Catania, A. Mineo, S. Monteleone, M. Palesi and D. Patti, "Noxim: An Open, Extensible and Cycle-accurate Network on Chip Simulator," in Application-specific Systems, Architectures and Processors (ASAP), 2015 IEEE 26th International Conference on, Toronto, 2015.

- [34] Y. Ben-Itzhak, E. Zahavi, I. Cidon and A. Kolodny, "HNOCS: Modular open-source simulator for Heterogeneous NoCs," in Embedded Computer Systems (SAMOS), 2012 International Conference on, Samos, 2013.

- [35] H. Hossain, M. Ahmed, A. Al-Nayeem, T. Z. Islam and M. M. Akbar, "Gpnocsim - A General Purpose Simulator for Network-On-Chip," in Information and Communication Technology, 2007. ICICT '07. International Conference on, Dhaka, 2008.

- [36] H. M. Kamali and S. Hessabi, "AdapNoC: A fast and flexible FPGAbased NoC simulator," in Field Programmable Logic and Applications (FPL), 2016 26th International Conference on, Lausanne, 2016.

- [37] P. W. Viglucci and A. Carpenter, "ENoCS: An Interactive Educational Network-on-Chip Simulator," in ASEE Annual Conference & Exposition, New Orleans, 2016.

- [38] P. Wehner, J. Rettkowski, T. Kleinschmidt and D. Göhringe, "MPSoCSim: An extended OVP Simulator for Modeling and Evaluation of Network-on-Chip based heterogeneous MPSoCs," in Embedded Computer Systems: Architectures, Modeling, and Simulation (SAMOS), Samos, 2015.

- [39] D. Wang, C. Lo, J. Vasiljevic, N. E. Jerger and G. Steffan, "DART: A programmable architecture for NoC simulation on FPGAs," IEEE Transactions on Computers, vol. 63, no. 3, pp. 664 - 678, 2014.

- [40] T. Carlson, W. Heirman and L. Eeckhout, "Sniper: Exploring the Level of Abstraction for Scalable and Accurate Parallel Multi-Core Simulation," Intel Labs Europe, 2015.

- [41] K. Swaminathan, D. Thakyal, S. G. Nambiar, G. Lakshminarayanan and S.-B. Ko, "Enhanced Noxim Simulator for Performance Evaluation of Network on Chip Topologies," in Engineering and Computational Sciences (RAECS), 2014 Recent Advances in, Chandigarh, 2014.

- [42] H.-Y. Wang, C.-H. Chao, T.-C. Yin and A.-Y. Wu, "Buffer Depth Allocation for Thermal-Aware 3D Network-on-Chip Design," in Routing Algorithms in Networks-on-Chip, Springer, 2013, pp. 307-338.

- [43] K. Manna, S. Chattopadhyay and I. Sengupta, "Through silicon via placement and mapping strategy for 3D mesh based Network-on-Chip," in Very Large Scale Integration (VLSI-SoC), 2014 22nd International Conference on, Playa del Carmen, 2014.