# A Very High Speed, High Resolution Current Comparator Design

Neeraj K. Chasta

**Abstract**—This paper presents an idea for analog current comparison which compares input signal and reference currents with high speed and accuracy. Proposed circuit utilizes amplification properties of common gate configuration, where voltage variations of input current are amplified and a compared output voltage is developed. Cascaded inverter stages are used to generate final CMOS compatible output voltage. Power consumption of circuit can be controlled by the applied gate bias voltage. The comparator is designed and studied at 180nm CMOS process technology for a supply voltage of 3V.

Keywords—Current Mode, Comparator, High Resolution, High Speed.

## I. INTRODUCTION

THE information carried by any electric network is represented by Nodal voltages and branch currents, former referred to "voltage domain circuits" whereas the latter are known as "current domain circuits".

Current mode circuits are becoming designer's interests now a day, as they offer many unique and attractive properties over their voltage mode complements. This includes higher speed, higher bandwidth, reduced distortion, low supply voltage requirements and lesser sensitivity to switching noise [4].

Several current comparators are proposed in recent years [5]-[15]. The first CMOS continuous time current comparator was proposed in [5], which consists of two cascode current mirrors. The drawback of this design was in terms of speed and bandwidth. A new design has been proposed [7] which uses inverter stage in feedback with source-follower stage. But the circuit shows dead band region for low values of input currents, where input impedance is quite high and thus limiting speed of operation.

Voltage-current feedback concept is used for comparison of currents [11]-[14], where a resistive feedback is applied to a voltage amplifier, which results in impedances reduction thus improvement speed performance. Current mirror concept again used in [15]; where it uses improved Wilson current mirror for current comparison, but circuit suffers from high power consumption and higher delay introduced by gain circuitry.

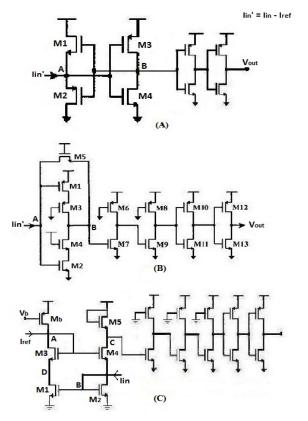

Fig. 1 Existing Current Comparators (A) H. Traff's [7] (B) L. Chen's [14] (C) V. Kasemsuwan's [15]

## II. CIRCUIT DESCRIPTION

As we think of "CASCODE" topology, it is a cascade of two Common Source (CS) and Common Gate (CG) stages, providing many useful properties.

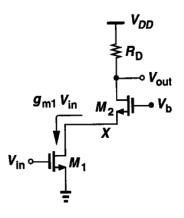

Fig. 2 shows the basic cascode configuration: where "M1" generates a small signal drain current proportional to applied voltage "Vin" and "M2" simply routes the current to " $R_D$ ". We call "M1" the input device and "M2" the cascode device [1]-[3]. Here we see that a diode connected input device "M1" will allow current input at its drain terminal, it forms the basis of this proposed idea (Fig. 3).

N. K. Chasta was with Dhirubhai Ambani Institute of Information & Communication Technology, Gandhinagar, Gujarat, India (e-mail: neeraj.chasta@gmail.com).

Fig. 2 A Cascode Stage [3]

Gate drain connected "M1" will give a small signal input impedance to input current as well as turns circuit in Common gate configuration; where voltage variation caused by input current at drain of "M1" works as input signal to common gate configured transistor "M2" which in turn produce amplified voltage output across "R<sub>D</sub>".

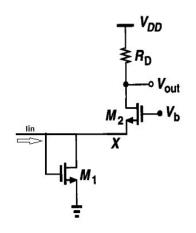

Fig. 3 Current Input to Cascode Stage

Under proper biasing conditions, we can use this circuit as a current comparator when difference of input signal & reference currents (Iin - Iref) is applied to diode connected "M1" and the corresponding voltage output is taken across a resistive load.

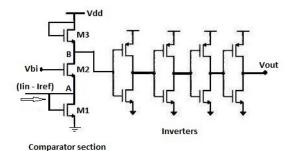

Fig. 4 Proposed Common Gate Current Comparator

Fig. 4 shows proposed current comparator, "M1-M2" are connected in configuration explained above for allowing current input and voltage output. "M3" is a diode connected load for making output impedance small. It uses four Inverters in additional gain circuitry to get rail to rail CMOS compatible voltage output. "V<sub>bi</sub>" is the biasing voltage which is chosen so that M2 stays in "saturation" at the time of zero current.

*Working:* When I<sub>in</sub>>I<sub>ref</sub> means (**I**<sub>in</sub> – **I**<sub>ref</sub>) is positive, it increases the voltage at node "A" (VA). As gate of "M2" biased with a constant voltage, Increase in VA reduces the gate-source voltage of M2. This turns M2 in more saturation and its CG configuration give rise to voltage at node B. This voltage after Gain stages produce a CMOS compatible "HIGH" output. Further increase of current will continuously start decreasing of gate to source voltage of transistor M2. At the time when Vgs2<Vm; M2 will turn "OFF" and so the high output voltage level at node B.

On the other side When  $I_{in} < I_{ref}$  means ( $I_{in} - I_{ref}$ ) is negative, it decreases the voltage at node "A" (VA) and thus turns M2 in "triode" which results in decrease of voltage at node B (as voltage at node B will start following voltage at node A). This voltage after Gain stages produce a CMOS compatible "LOW" output.

By small signal analysis we can easily see:

$$V_{B} = \frac{1}{\left[g_{m3} + g_{m1}\left(\frac{1 + g_{m3}r_{o2}}{1 + g_{m2}r_{o2}}\right)\right]} \left(I_{in} - I_{ref}\right)$$

Considering"  $g_m r_o >> 1$ " We get,

$$V_B = \frac{1}{\left[g_{m3}\left(1 + \frac{g_{m1}}{g_{m2}}\right)\right]} \left(I_{in} - I_{ref}\right)$$

If all the " $g_m$ 's" are equal then,

$$\frac{V_B}{\left(I_{in} - I_{ref}\right)} = \frac{1}{2g_m}$$

#### **III. SIMULATION RESULTS**

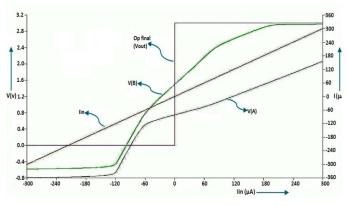

For simulation, standard BSIM  $0.18\mu m$  CMOS technology parameters have been used with 3V power supply. Circuit was designed optimally for values of speed, power and accuracy. DC transfer characteristics obtained for simulated design is shown in Fig. 5.

Fig. 5 DC Transfer Characteristics

Delays produced by circuit  $\pm 1 \mu A \& \pm 100 \mu A$  current steps are shown in Table I; at the DC power dissipation of 1.4mW (where for flexibility we have chosen V<sub>bi</sub> = V<sub>DD</sub>/2).

TABLE I Transient Response: Common Gate Comparator

| All delays in (ns)            | +/- 1μA | +/- 100µA |

|-------------------------------|---------|-----------|

| Rise delay (Comparator stage) | 0.1ns   | 0.1ns     |

| Rise delay (Gain stages)      | 0.6ns   | 0.1ns     |

| Total rise delay              | 0.7ns   | 0.2ns     |

| Fall delay (Comparator stage) | 0.1ns   | 0.1ns     |

| Fall delay (Gain stages)      | 0.6ns   | 0.1ns     |

| Total fall delay              | 0.7ns   | 0.2ns     |

|                               |         |           |

| Total Average Delay           | 0.7ns   | 0.2ns     |

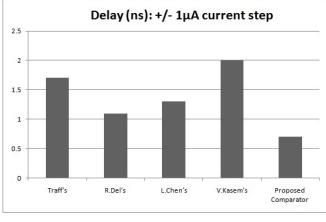

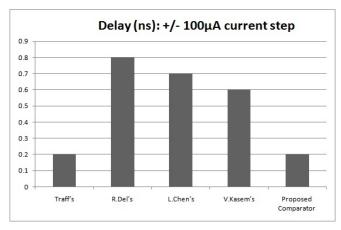

To compare the performance of proposed comparator with those of Traff's [7], R. Del's [11], L. Chen's [14] and V. Kasemsuwan's [15], LTSPICE simulations of all comparators are performed using standard BSIM 0.18µm CMOS technology parameters for optimized values of speed, power and accuracy. Transistor dimensions for proposed comparator designs are as:

| TABLE II                                  |           |            |  |

|-------------------------------------------|-----------|------------|--|

| DESIGN PARAMETERS: COMMON GATE COMPARATOR |           |            |  |

|                                           | W (Width) | L (Length) |  |

| M1, M2                                    | 0.36µm    | 0.18µm     |  |

| M3                                        | 0.18µm    | 0.72µm     |  |

|                                           |           |            |  |

| Inverter: PMOS                            | 0.54µm    | 0.18µm     |  |

| Inverter: NMOS                            | 0.18µm    | 0.18µm     |  |

Transient response for all five comparators are simulated for input square-wave currents with amplitudes of  $\pm 1 \mu A \& \pm 100 \ \mu A$ . Figs. 6 & 7 show the comparison of average delay times, it can be seen that proposed design works faster for low as well as high input current values.

Fig. 6 Average Delay (ns): Response to +/- 1µA Current Step

The DC power consumption of proposed design is little higher from that of Traff's [7] and is comparable to that of others. But in Traff's design lower power consumption is achieved with the expense of large average delay for small input current values, also it offers initial dead band region to such current values whereas proposed comparator shows high accuracy (innA range).

Fig. 7 Average Delay (ns): Response to +/- 100µA Current Step

## IV. CONCLUSION

A high speed & high resolution continuous time CMOS current comparator is proposed whose power consumption is comparable to existing current comparators. In addition proposed design has less area, simple structure, low input & output impedances and low operational complexities. The simulation results shows propagation delay of 0.7 ns & 0.2 ns to  $\pm 1 \mu A$  &  $\pm 100 \mu A$ , DC power dissipation of 1.4 mW and resolution less than 50 nA. The overall performance is better than most of the comparators nearly in terms of all design constraints and it should be useful in many digital and analog circuit applications.

## ACKNOWLEDGMENT

The author sincerely thanks Prof. Chetan Parikh for his valuable guidance in the study of Current comparators.

#### REFERENCES

- [1] D. A. Johns and K. Martin, Analog integrated circuit design. John Wiley & Sons, 1997.

- [2] R. J. Baker, CMOS: Circuit design, layout and simulation, 2nd ed. John Wiley & Sons, 2007.

- B. Razavi, Design of analog CMOS integrated circuits. India: Tata [3] McGraw Hill, 2002.

- F. Yuan, CMOS current-mode circuits for data communications. [4] Springer, 2006.

- D. A. Freitas and K. W. Current, "CMOS current comparator circuit," [5] Electron. Lett., vol. 19, no. 17, pp. 695-697, August 1983.

- [6] Z. Wang and W. Guggenbuhl, "CMOS current Schmitt trigger with fully adjustable hysteresis," Electron. Lett., vol. 25, no. 6, pp. 397-398, March 1989

- H. Traff, "Novel approach to high speed CMOS current comparators," [7] Electron. Lett., vol. 28, no. 3, pp. 310-312, January 1992.

- A.T.K. Tang and C. Toumazou, "High Performance CMOS current [8]

- comparator," *Electron. Lett.*, vol. 30, no. 1, pp. 5-6, January 1994. M. Bracey and W.R. White, "Design considerations for current domain [9] regenerative comparators," IEEE International Conference on Advanced A-D and D-A Conversion Techniques and their Applications, July 6-8, 1994.

- [10] L. Ravezzi, D. Stoppa and G.-F. Dalla Betta, "Simple high-speed CMOS current comparator," Electronics Letters, vol.33, no.22, pp.1829-1830, 23 Oct 1997.

- [11] R. Fernandez, G. Cembrano, R. Castro and A. Vazquez, "A Mismatch-Insensitive High-Accuracy High-speed Continuous-Time Current Comparator in Low Voltage CMOS," IEEE Proc. Analog and Mixed Signal IC Design, pp. 303-306, September 1997.

- [12] B.M. Min and S.W. KIM, "High performance CMOS current comparator using resistive feedback network," *Electronics Letters*, Vo1.34, N0.22, pp.2074-2076, 1998.

- [13] L. Luh, J. Choma Jr. and J. Draper, "A High-speed High-Resolution CMOS Current Comparator," IEEE Proc. Electronics, Circuits and Systems, vol. 1, pp. 111-116, August 1999.

- [14] L. Chen, B. Shi and C. Lu, "A High Speed/Power ratio continuous time CMOS current Comparator," IEEE Proc. Electronics, Circuits and Systems, vol. 2, pp. 883-886, December 2000.

- V. Kasemsuwan and S. Khucharoensin, "High Speed Low Input Impedance CMOS Current Comparator," *IEEE Trans. Fundamentals*, [15] vol. E88-A, no. 6, pp. 1549-1553, June 2005.