# AMD GPU support in GROMACS

### Andrey Alekseenko KTH Royal Institute of Technology & SciLifeLab andreyal@kth.se

#### Moore's law

- "Number of transistors in an integrated circuit doubles about every two years"

- Before ~2005: increasing single-core performance

- After ~2005: increasing the number of cores

#### $10^{7}$ Transistors (thousands) 10<sup>6</sup> Single-Thread 10<sup>5</sup> Performance (SpecINT x 10<sup>3</sup>) $10^{4}$ Frequency (MHz) $10^{3}$ **Typical Power** $10^{2}$ Watts) Number of $10^{1}$ Logical Cores $10^{0}$ 1970 1980 1990 2000 2010 2020

50 Years of Microprocessor Trend Data

Year Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2021 by K. Rupp

https://github.com/karlrupp/microprocessor-trend-data

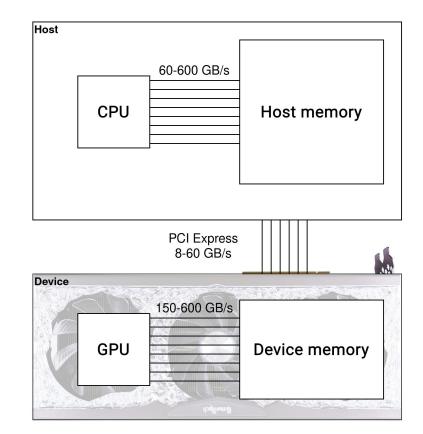

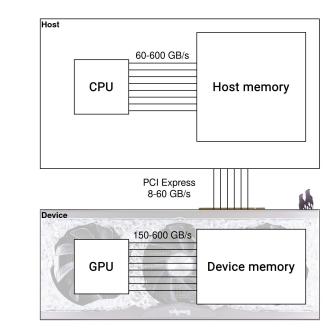

### Graphics processing units

- GPU: Most common type of *accelerator*

- Specialized hardware

- Highly parallel

- Not self-sufficient

- Separate memory

- Different programming paradigm

Figure adapted from the Carpentry GPU Programming lesson; GPU photo by @zelebb on Unsplash

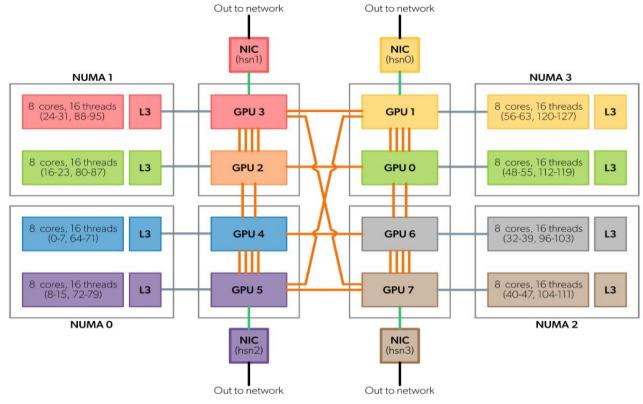

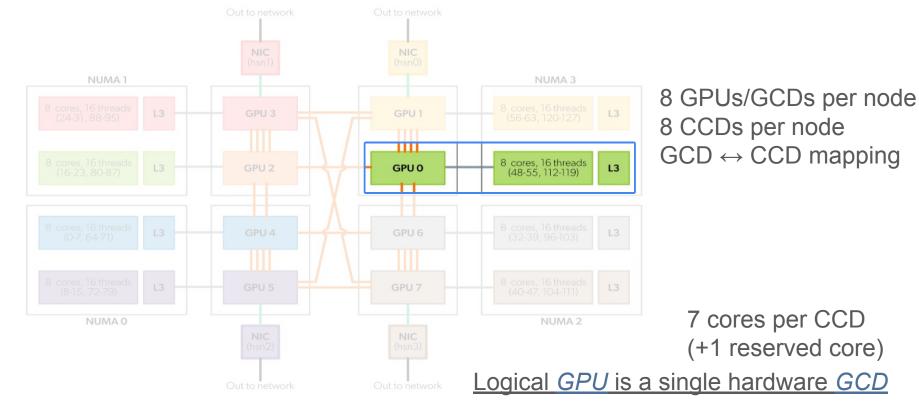

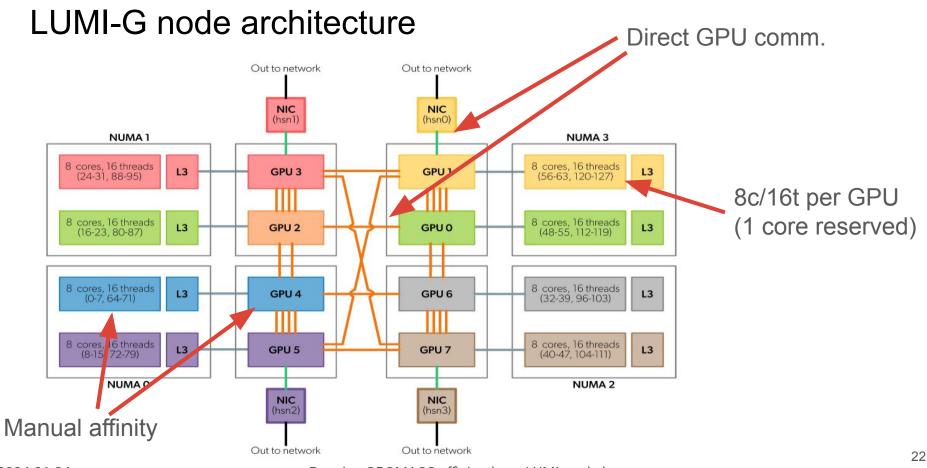

#### LUMI-G node architecture

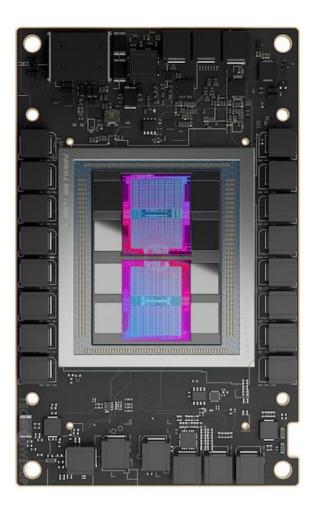

### AMD MI250X GPU

- One MI250X GPU has two GCDs

- Each GCD is a logical GPU

GCD specs:

- AMD CDNA2 architecture (gfx90a)

- Peak Engine Clock: 1700 MHz

- Peak FP32 Performance: 90 TFLOPs

- Dedicated Memory Size: 64 GB

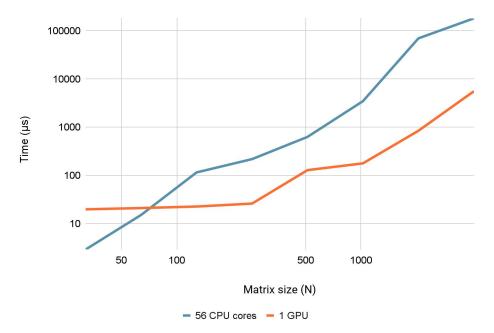

#### Bandwidth vs. latency

N×N matrix multiplication AMD Trento CPU vs. AMD MI250X GPU (LUMI)

julia using AMDGPU using BenchmarkTools

```

N = 5:12

for n in N

A = rand(2^n, 2^n);

A_d = ROCArray(A);

@btime $A * $A;

@btime begin

$A_d * $A_d;

AMDGPU.synchronize()

end

end

```

#### Homogeneous / heterogeneous acceleration

- Homogeneous: use a single type of hardware

- Accelerator challenges

- Porting effort / feature support

- Scaling

- Heterogeneous: use different hardware together

- Typically, CPU + GPU

- Challenges

- Data movement

- Latencies

- Load balancing

Figure adapted from the Carpentry GPU Programming lesson; GPU photo by @zelebb on Unsplash

### **GPU** scheduling

2024-01-24

### Using GPUs for compute

- Existing software

- Many HPC and AI codes already support GPUs

- Task-specific frameworks / libraries

- ML (PyTorch), CV (OpenCV), math (cuBLAS), ...

- High-level languages

- Python (PyCUDA, Numba), Julia (AMDGPU.jl), ...

- Directive-based methods

- OpenMP, OpenACC

- Native GPU code

- CUDA, HIP, OpenCL, SYCL, Kokkos, ...

#### Criteria:

- Effort

- Portability

- Performance

- Openness

#### GPU frameworks (subjective comparison)

|         |                           | <b>DVIDIA</b> .<br>CUDA  | ROCm         | OpenCL            | SYCL,                    |

|---------|---------------------------|--------------------------|--------------|-------------------|--------------------------|

| Ma      | turity of API / ecosystem | +++ / +++                | ++ / +       | +++ / ++          | ++ / +                   |

|         | Open standard             | X                        | Х            |                   | $\checkmark$             |

|         | Single-source model       | $\checkmark$             | $\checkmark$ | Х                 | $\checkmark$             |

|         | Modern C++ support        | $\checkmark$             | $\checkmark$ | X                 | $\checkmark$             |

| ort     |                           | X                        | $\sqrt{}$    |                   | ++                       |

| support | intel                     | X                        | X            | $\sqrt{\sqrt{1}}$ | $\sqrt{\sqrt{\sqrt{1}}}$ |

| ΗM      |                           | $\sqrt{\sqrt{\sqrt{1}}}$ | +            | $\checkmark$      | ++                       |

|         |                           |                          |              |                   | 10                       |

- Open standard

- Two independent free (libre) implementations

- Intel oneAPI DPC++

- AdaptiveCpp (aka hipSYCL) oneAPI

- Broad hardware support

- Single source, modern C++

- Standardized interoperability with native libraries

#### GPU frameworks in GROMACS 2020

|                              | <b>DVIDIA</b> .<br>CUDA | OpenCL            | SYCL. |

|------------------------------|-------------------------|-------------------|-------|

| Short-range non-bonded (-nb) | $\checkmark$            | $\checkmark$      |       |

| Long-range PME (-pme)        |                         | $\checkmark$      |       |

| Bonded (-bonded)             |                         |                   |       |

| Update (-update)             |                         |                   |       |

| PME Decomposition            |                         |                   |       |

| Direct GPU communications    |                         |                   |       |

| Graph-based scheduling       |                         |                   |       |

| Supported GPUs               | NVIDIA                  | AMD,Intel, NVIDIA |       |

|                              |                         |                   | 12    |

### GPU frameworks in GROMACS 2023

|                              | CUDA         | OpenCL                    | SYCL.              |

|------------------------------|--------------|---------------------------|--------------------|

| Short-range non-bonded (-nb) | $\checkmark$ | $\checkmark$              | $\checkmark$       |

| Long-range PME (-pme)        |              | $\checkmark$              |                    |

| Bonded (-bonded)             |              |                           | $\checkmark$       |

| Update (-update)             |              |                           | $\checkmark$       |

| PME Decomposition            | $\checkmark$ | X                         | $\sqrt{*}$         |

| Direct GPU communications    |              | Х                         | $\checkmark$       |

| Graph-based scheduling       |              | X                         |                    |

| Supported GPUs               | NVIDIA       | AMD, Apple, Intel, NVIDIA | AMD, Intel, NVIDIA |

| Ģ | GPU frameworks in G          |                         |                           |                    |

|---|------------------------------|-------------------------|---------------------------|--------------------|

|   |                              | <b>DVIDIA</b> .<br>CUDA | OpenCL                    | SYCL               |

|   | Short-range non-bonded (-nb) | $\checkmark$            | $\checkmark$              | $\checkmark$       |

| - | Long-range PME (-pme)        |                         |                           | $\checkmark$       |

| - | Bonded (-bonded)             |                         |                           | $\checkmark$       |

| - | Update (-update)             |                         |                           | $\checkmark$       |

| - | PME Decomposition            |                         | Х                         | √*                 |

| - | Direct GPU communications    |                         | Х                         | $\checkmark$       |

| - | Graph-based scheduling       |                         | X                         |                    |

| - | Supported GPUs               | NVIDIA                  | AMD, Apple, Intel, NVIDIA | AMD, Intel, NVIDIA |

### SYCL compared to HIP

- AMD suggests HIP/ROCm stack for their GPUs

- Used by most other codes targeting AMD GPUs

- SYCL is open, portable, modern

- Saved developer time: more features, less bugs

- Two supported implementations: DPC++ and AdaptiveCpp

- GROMACS recommends AdaptiveCpp (hipSYCL) for AMD GPUs

- AdaptiveCpp is built on top of HIP

- SYCL implementation, developed at Heidelberg University

- Supports AMD, NVIDIA, Intel GPUs

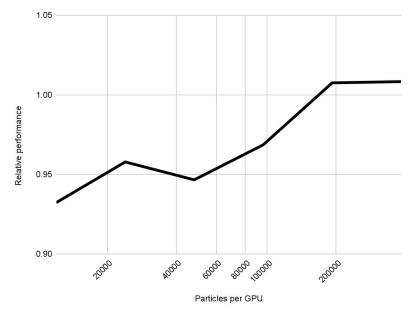

### SYCL compared to HIP

- AdaptiveCpp is a layer on top of HIP

- Same compiler

- Different runtime / scheduler

- Minimal overhead for *bandwidth-bound* simulation

- Noticeable overhead for *latency-bound* simulations (< 50k particles per GPU)

- To be improved soon

- Reducing CPU usage (lower -ntomp) can help

#### Latency-bound case

- AdaptiveCpp uses extra threads to submit work to GPU

- Theoretically, allows more flexibility

- In practice, incurs overhead

- Especially with few CPU cores

- Typically, 7 threads per GPU is fine

- But watch out when approaching the scaling limit!

#### CPU overheads: ntomp=7 / ntomp=5

8 GPUs, RF-only water box, GPU-aware MPI, fully GPU-resident, -nstlist 300

### LUMI-G node architecture

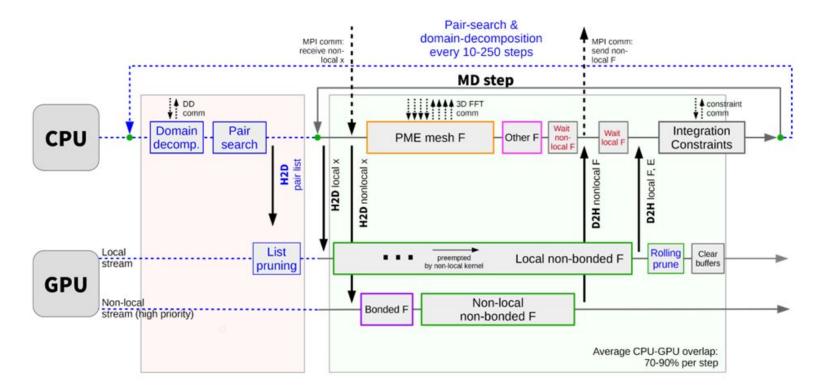

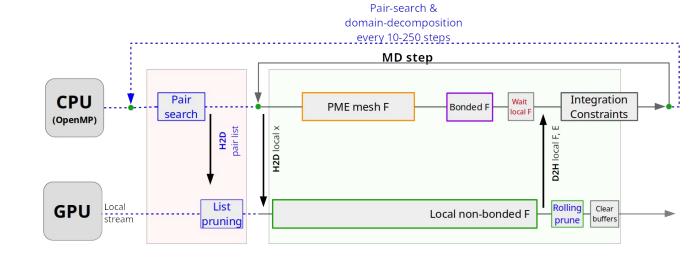

## Parallelization overview: single GPU

- 1 GPU

- 1-7 CPU cores

Resource control:

- -ntomp / OMP\_NUM\_THREADS

- -nb, -pme, -bonded, -update

- -nstlist

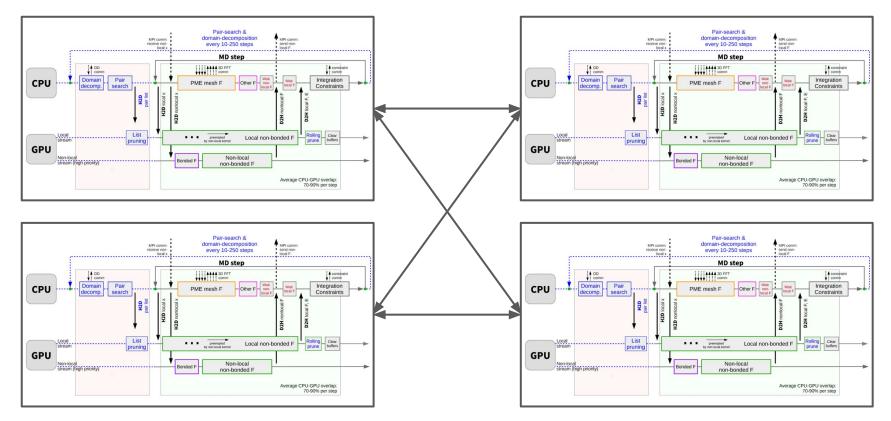

#### Parallelization overview: multiple GPUs

#### Parallelization overview: multiple GPUs

Multiple MPI ranks:

- 1 GPU per rank

- 1-7 cores per rank

8 GPUs per node, can use multiple nodes

- Better resource control when allocating full node

- Cray MPI is GPU-aware if you tell it to be

Ranks can share the GPU

#### 2024-01-24