## University of Torino

# DOCTORAL SCHOOL ON SCIENCE AND HIGH TECHNOLOGY

COMPUTER SCIENCE DEPARTMENT

## **DOCTORAL THESIS**

# Parallel Programming with Global Asynchronous Memory: Models, C++ APIs and Implementations

Author:

Maurizio DROCCO

Cycle XXIX

Supervisor: Prof. Marco Aldinucci

A thesis submitted in fulfillment of the requirements for the degree of Doctor of Philosophy

"Thinking doesn't guarantee that we won't make mistakes. But not thinking guarantees that we will."

Leslie Lamport

## UNIVERSITY OF TORINO

## **Abstract**

Computer Science Department

Doctor of Philosophy

## Parallel Programming with Global Asynchronous Memory: Models, C++ APIs and Implementations

by Maurizio DROCCO

In the realm of High Performance Computing (HPC), message passing has been the programming paradigm of choice for over twenty years. The durable MPI (Message Passing Interface) standard, with send/receive communication, broadcast, gather/scatter, and reduction collectives is still used to construct parallel programs where each communication is orchestrated by the developer-based precise knowledge of data distribution and overheads; collective communications simplify the orchestration but might induce excessive synchronization.

Early attempts to bring shared-memory programming model—with its programming advantages—to distributed computing, referred as the Distributed Shared Memory (DSM) model, faded away; one of the main issue was to combine performance and programmability with the memory consistency model. The recently proposed Partitioned Global Address Space (PGAS) model is a modern revamp of DSM that exposes data placement to enable optimizations based on locality, but it still addresses (simple) dataparallelism only and it relies on expensive sharing protocols.

We advocate an alternative programming model for distributed computing based on a Global Asynchronous Memory (GAM), aiming to *avoid* coherency and consistency problems rather than solving them. We materialize GAM by designing and implementing a *distributed smart pointers* library, inspired by C++ smart pointers. In this model, public and private pointers (resembling C++ shared and unique pointers, respectively) are moved around instead of messages (i.e., data), thus alleviating the user from the burden of minimizing transfers. On top of smart pointers, we propose a high-level C++ template library for writing applications in terms of dataflow-like networks, namely GAM nets, consisting of stateful processors exchanging pointers in fully asynchronous fashion.

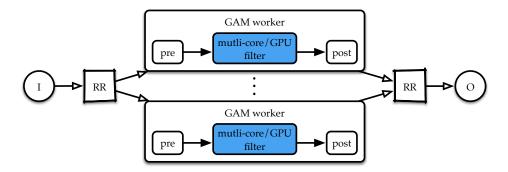

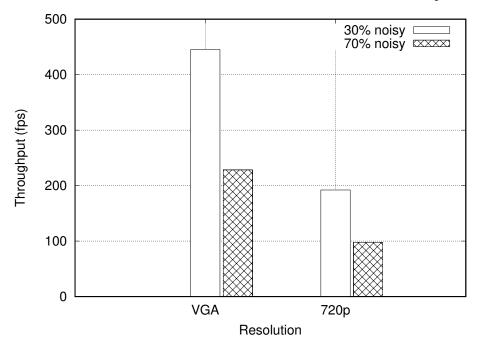

We demonstrate the validity of the proposed approach, from the expressiveness perspective, by showing how GAM nets can be exploited to implement both standalone applications and higher-level parallel programming models, such as data and task parallelism. As for the performance perspective, preliminary experiments show both close-to-ideal scalability and negligible overhead with respect to state-of-the-art benchmark implementations. For instance, the GAM implementation of a high-quality video restoration filter sustains a 100 fps throughput over 70%-noisy high-quality video streams on a 4-node cluster of Graphics Processing Units (GPUs), with minimal programming effort.

# Acknowledgements

Walking all the way through a meaningful PhD program is an act of pure masochism. In addition to "the willingness to fail all the time" (cit. J. Backus), one needs to get comfortable with the constant feeling that your understanding on anything is wrong or, at best, incomplete. Therefore, getting some proper teachers along the way is essential to survive.

First, I would like to thank professor Tremblay for his inestimable help with this thesis. Guy, I hope to have eventually acquired, by osmosis, a small fraction of your impressive ability in building visions over any research topic. Furthermore, if native English readers can read this thesis without getting hurt to death, it is due to your corrections and lessons, that I hope to have learned, at least partially.

I would like to thank the reviewers for dedicating part of their time, impressive knowledge, and experience to improve this thesis. I perceived all your suggestions and remarks as a privilege, that made me feel "standing on the shoulders of giants".

I owe special thanks to professor Aldinucci for being much more than my supervisor during the last seven years. Marco, in your shop I built my special glasses for seeing both computer science and the world under a different light. You assisted me throughout the whole spectrum of my endless torments, from false sharing to teenage heartaches. Last but not least, it is your fault if I felt in love with the two most dangerous and beautiful beasts I met so far: parallel computing and Claudia.

My walk would not have been that funny without my colleagues, as masochist as me. Guys, together we went through a bunch of though challenges, from squeezing twenty hours of working plus five hours hanging around into a twenty-four day, to mastering the art of collecting receipts, which were never enough. I really enjoyed each step with you all.

Back to where my walk began, I owe a mix of thanks and apologies to my relatives. Dad, I spent whole days trying to mimic your artisan's hands, I steadily failed but at least I learned the concept of a job well done. Mom, thank you for showing me how honesty, humbleness, and solidarity can be more that beautiful words. Emi, you have always been my favorite brother, I have to thank you at least for all the advices and recipes that made me a slightly better cooker along the way.

Besides playing with doughs, I tend to be a theoretician, in the sense I like to spend hours searching for the right way to describe things, and of course I got accustomed to the feeling of not being completely happy with the descriptions I build. Walking with you, Claudia, has always been a different story: every day you gift me the exact colors that I need to define the perfect world. I wish I had a fraction of your wiseness and I will never ever understand "perché fra i tanti, bella, che hai colpito, ti sei gettata addosso proprio a me" (cit. F. Guccini).

# **Contents**

| 1 | Intr | oductio | on                                        | 1  |

|---|------|---------|-------------------------------------------|----|

|   | 1.1  | Resul   | ts and Contributions                      | 2  |

|   | 1.2  | Limita  | ations                                    | 5  |

|   | 1.3  | List of | f Papers                                  | 6  |

|   |      | 1.3.1   | Publications by Topic                     | 6  |

|   |      | 1.3.2   | Publications by Type                      | 8  |

| 2 | Bac  | kgroun  | ad .                                      | 13 |

|   | 2.1  | Parall  | el Computing Platforms                    | 13 |

|   |      | 2.1.1   | SIMD computers                            | 14 |

|   |      | 2.1.2   | Shared-Memory Multiprocessors             | 15 |

|   |      | 2.1.3   | Many-Core Processors                      | 16 |

|   |      | 2.1.4   | Distributed Systems, Clusters, and Clouds | 17 |

|   | 2.2  | Parall  | lel Programming Models                    | 18 |

|   |      | 2.2.1   | Types of Parallelism                      | 18 |

|   |      | 2.2.2   | Memory and Communication Model            | 19 |

|   |      | 2.2.3   | Low-Level Programming Models              | 20 |

|   |      | 2.2.4   | High-level Programming Models             | 22 |

|   | 2.3  |         | lel Memory Models                         | 26 |

|   |      | 2.3.1   | Cache Coherence                           | 26 |

|   |      | 2.3.2   | Memory Consistency                        | 27 |

|   | 2.4  |         | ries Used by our Implementation           | 28 |

|   |      | 2.4.1   | C++ Smart Pointers                        | 28 |

|   |      | 2.4.2   | FastFlow                                  | 29 |

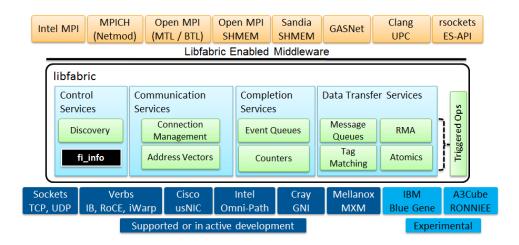

|   |      | 2.4.3   | Libfabric                                 | 32 |

| 3 | Glo  | hal Ası | ynchronous Memory                         | 35 |

| 0 | 3.1  |         | m Model                                   | 35 |

|   | 5.1  | 3.1.1   |                                           | 36 |

|   |      | 3.1.2   | Comparison with Cache-Coherent Systems    | 37 |

|   | 3.2  |         | ational Semantics                         | 37 |

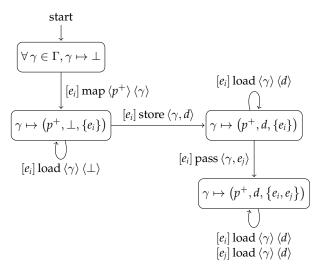

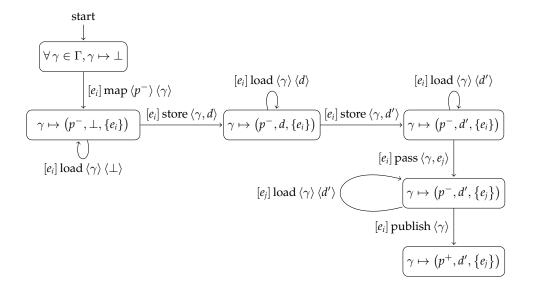

|   | 3.2  | 3.2.1   |                                           | 38 |

|   |      |         | Memory Transitions                        | 38 |

|   |      | 3.2.2   | Memory Transitions                        |    |

|   | 2.2  | 3.2.3   | State Machine Representation              | 40 |

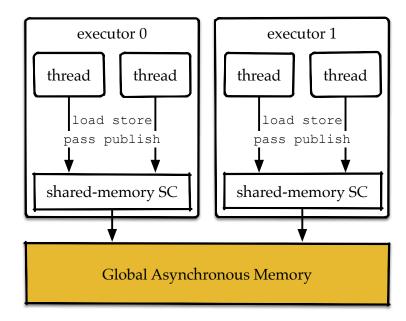

|   | 3.3  |         | elism                                     | 43 |

|   |      | 3.3.1   | Intra-Executor Parallelism                | 43 |

|   |      | 3.3.2   | Inter-Executor Parallelism                | 44 |

|   | 0.1  | 3.3.3   | Parallel Memory Model                     | 45 |

|   | 3.4  |         | mplementation                             | 46 |

|   |      | 3.4.1   | Programming Environment                   | 47 |

|   |      | 3.4.2   | Runtime Architecture                      | 48 |

|   |      | 2 / 2   | Primitivos                                | 50 |

| 4 | Sma                        | rt GAN    | M Pointers                            | 55  |  |  |

|---|----------------------------|-----------|---------------------------------------|-----|--|--|

|   | 4.1                        | Public    | Pointers                              | 55  |  |  |

|   |                            | 4.1.1     | Distributed Reference Counting        | 56  |  |  |

|   |                            | 4.1.2     | API                                   | 57  |  |  |

|   | 4.2                        | Privat    | re Pointers                           | 59  |  |  |

|   |                            | 4.2.1     | Distributed Memory Releasing          | 60  |  |  |

|   |                            | 4.2.2     | Two Flavors of Private Pointers       | 61  |  |  |

|   |                            | 4.2.3     | API                                   | 62  |  |  |

|   | 4.3                        | Smart     | ness                                  | 63  |  |  |

|   |                            | 4.3.1     | Memory Leaks                          | 64  |  |  |

|   |                            | 4.3.2     | Dangling Pointers                     | 65  |  |  |

| 5 | Para                       | ıllel Pro | ogramming with GAM Nets               | 67  |  |  |

| J | 5.1                        |           | Nets                                  | 67  |  |  |

|   | 0.1                        | 5.1.1     | Communicators                         | 68  |  |  |

|   |                            | 5.1.2     | Processors                            | 70  |  |  |

|   |                            | 5.1.3     | Execution Model                       | 71  |  |  |

|   | 5.2                        |           | mplementation                         | 72  |  |  |

|   | 0.2                        | 5.2.1     | ±                                     | 72  |  |  |

|   |                            | 5.2.2     | Implementation                        | 75  |  |  |

|   | 5.3                        |           | atterns                               | 80  |  |  |

|   | 0.0                        | 5.3.1     | Pipeline                              | 82  |  |  |

|   |                            | 5.3.2     | Farm                                  | 83  |  |  |

|   |                            | 5.3.3     | Active Communicators                  | 86  |  |  |

| 6 | Hio                        | her-I ev  | vel Programming Models on top of GAM  | 89  |  |  |

| Ü | 6.1                        |           | erated Data Structures                | 89  |  |  |

|   | 0.1                        | 6.1.1     | Cluster-as-Accelerator Paradigm       | 90  |  |  |

|   |                            | 6.1.2     | C++ Library of Accelerated Containers | 91  |  |  |

|   |                            | 6.1.3     | Implementation                        | 91  |  |  |

|   | 6.2                        |           | pased Parallel Programming            | 92  |  |  |

|   | 0.2                        | 6.2.1     | Universal Model of Parallelism        | 93  |  |  |

|   |                            | 6.2.2     | Implementing a Task-based RTS         | 93  |  |  |

| _ |                            |           |                                       |     |  |  |

| 7 | Experimental Evaluation 99 |           |                                       |     |  |  |

|   | 7.1                        |           | ssiveness                             | 99  |  |  |

|   |                            | 7.1.1     | Two-Phase Video Restoration           | 99  |  |  |

|   |                            | 7.1.2     | High-Frequency Stock Option Pricing   | 100 |  |  |

|   |                            | 7.1.3     | CWC Systems Biology Simulator         | 101 |  |  |

|   |                            | 7.1.4     | PiCo Data Analytics Framework         | 102 |  |  |

|   | 7.2                        |           | rmance                                | 105 |  |  |

|   |                            | 7.2.1     | Setting                               | 105 |  |  |

|   |                            | 7.2.2     | Results                               | 106 |  |  |

|   |                            | 7.2.3     | Discussion                            | 107 |  |  |

| 8 | Con                        | clusior   | 18                                    | 117 |  |  |

# Chapter 1

## Introduction

In parallel computing, the *message-passing* and *shared-memory* programming models have been influencing programming at all levels of abstraction, from hardware to application design. These models have been traditionally considered a dichotomy, often mapped onto another dichotomy: *scalability* versus *productivity*.

In the shared-memory programming model, tasks share a common address space, which they read and write asynchronously. Various synchronization mechanisms may be used to control access to the shared memory. An advantage of this model from the programmer's viewpoint is that the notion of data distribution is absent, so there is no need to explicitly specify the mapping between data structures and Processing Elements (PEs). Thus, program development is generally simpler. For this to happen, the sharedmemory model must exhibit a "natural" behavior to the programmer, in the sense that it should enable the programmer to design parallel code without data races and exhibiting a deterministic behavior. This requirement amounts to having a reasonably strong memory consistency model. This implies guaranteeing some global order of access to the shared memory from many PEs, which requires (at some level in the system stack) synchronizations and results into latency of memory accesses. Here, the strength of shared memory becomes a weakness already at a moderate scale: a strong memory consistency model over a shared memory is hardly scalable, whereas a weak model makes programming counterintuitive, eventually deteriorating the major strength of the shared-memory model, that is, simplicity of programming. The Distributed Shared Memory (DSM) hype cycle, which entered in the "trough of disillusionment" in the late nineties, is a paradigmatic example of the complexity of designing both an efficient and easy to use shared-memory model. More recently, the Partitioned Global Address Space (PGAS) approach, that couples shared memory with data parallelism, revitalized the research on DSM models. Is distributed shared memory entering the Gartner's hype cycle [82] "slope of enlightenment"?

By contrast, in the message-passing model, tasks use their own local memory during computation. Multiple tasks can reside on the same physical machine as well as across an arbitrary number of machines. Tasks exchange data through communications by sending and receiving messages. Data transfers usually require cooperative operations to be performed by each process (e.g., a send operation must have a matching receive operation). More recently, one-sided communications gained progressive interest because they admit zero-copy hardware-accelerated data movements and promote loose orchestration of tasks.

The durable MPI (Message Passing Interface) standard, with send/receive communication, broadcast, gather/scatter, and reduction collectives is still used to construct parallel programs composed of tens to hundreds of thousands of communicating processes. Each communication is orchestrated by the developer-based precise knowledge of code and overhead; collective communications simplify the orchestration but induce excessive synchrony due to barriers and global synchronization induced by blocking collective operations. An MPI application is really a monolith where each single process may become a bottleneck or a single point of failure. This programming model is effective for highly regular data parallel kernels but difficult to exploit for other patterns, where dealing with data locality is difficult and beyond the control of the average user.

The endeavor for extreme scale computing, also catered by the Big Data analytics hype, certainly revamped the research on high-level parallel programming models and languages. Skeletal approach [51] evolved and, eventually, went mainstream with Intel TBB and Google MapReduce. Task-based approaches are ruling the game of large scale distributed programming; we shall discuss some of them. Notwithstanding, the run-time support of all these programming environment eventually relies on a either a message-passing or a shared-memory layer. We mainly focused on this level of abstraction, at the hardware-software interface.

In this thesis, we propose to overcome the aforementioned dichotomy, advocating a hybrid model where data is shared and data races are addressed by way of asynchronous message passing. On this cornerstone, we build an entire stack of programming models of increasing abstraction level.

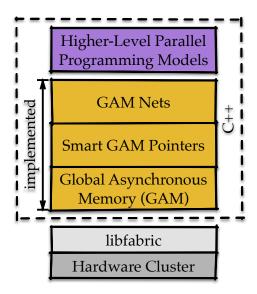

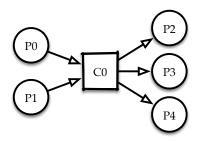

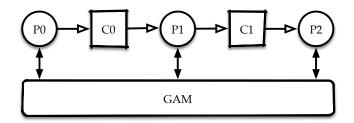

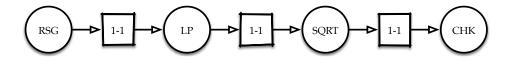

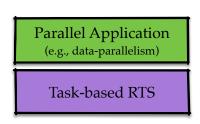

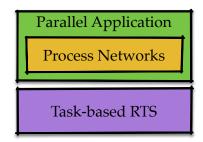

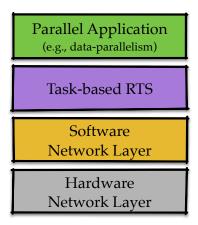

The main objective of the present thesis is to define a novel programming approach for distributed (possibly large) heterogeneous platforms, covering the complete software stack from low-level runtime systems to application programming. The main contributions of the thesis directly match the tiers of the proposed stack, which is sketched in Fig. 1.1. Each tier of the stack defines either a novel programming model or the evolution of an existing one.

## 1.1 Results and Contributions

## **Global Asynchronous Memory**

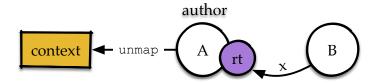

At the bottom layer of the stack in Fig. 1.1, the Global Asynchronous Memory (GAM) model consists in a set of *executors*<sup>1</sup> that share a global address space and that can make memory operations on the global addresses. A global address refers to a GAM slot, i.e., a binary object with either *public* or *private* attribute, according to the associated access capabilities. A single GAM slot is not distributed. A public slot can be accessed by any executor via load or store operations, although it cannot be updated once a value has been stored into it—i.e., GAM public slots are *single-assignment*. A public GAM slot can be replicated (cached) across different executors. Conversely, a private slot can be accessed via load and store operations,

<sup>&</sup>lt;sup>1</sup>In this thesis, the *executor* is an abstract concept, that should be thought as a mere syntactic component in the GAM model formalization.

FIGURE 1.1: Contributions of this thesis.

but only by its owner, that is, in any given moment, by the executor owning exclusive access capability over the slot. Ownership can be atomically passed from one executor to another. Overall, the GAM obeys the *sequential consistency* memory model.

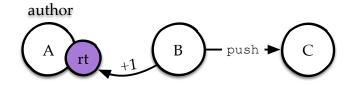

Inspired by the FastFlow programming model [17], the GAM exploits both shared memory and message passing programming models. In this new model, the executors synchronize with each other by passing messages that are *capabilities*, i.e., global memory references enriched with slot access attributes.

As discussed in Chapter 3, the GAM model avoids the problem of efficiently enforcing an adequately strong consistency model rather than solving it (as happened for DSMs). Also, it clearly differentiates itself from the PGAS approach since the partitioning, i.e., the data parallel commitment, is not deeply embedded in its definition. Nevertheless, as discussed in Chapter 6, GAM can be used to support a PGAS approach.

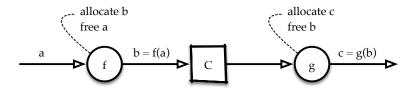

## **Smart GAM Pointers**

The GAM fits in the modern C++ realm by way of *Smart GAM Pointers*. They are a novel abstraction that extend C++11 smart pointers toward distributed memory platforms, such as multicomputers and clusters, with or without hardware-assisted remote memory access. As in the traditional shared-memory setting of C++11, smart pointers aim at facilitating the development of correct code. Smart pointers prevent most situations of *memory leaks* by making the memory deallocation automatic. In this setting, they support dynamic GAM slot allocation and make their deallocation automatic: a memory slot controlled by a smart pointer is automatically destroyed when the last (or only) owner is destroyed. Smart pointers also eliminate *dangling pointers* by postponing destruction until an object is no longer in use.

As discussed in Chapter 4, along the same line as the distinction between shared and unique pointers in C++, we propose two classes of pointers, namely *public* and *private*. Public pointers resemble shared pointers, in the sense that different *copies* of a public pointer, distributed among the executors, share the control over the underlying (public) memory slot. Symmetrically, private pointers resemble unique pointers, in the sense that each pointer has exclusive control over the underlying (private) memory slot. Private pointers are designed to be strictly coupled with move semantics.

Smart GAM Pointers are implemented by a C++11 template library. It distinguishes itself from other libraries by its attempt to minimize the conceptual gap against shared-memory programming in C++. Being simple and orthodox should be one of its strengths. We envision distributed computing as a mainstream feature of standard C++. For this, complex aspects of sharing (such as data races) should be tamed through familiar concepts by way of graceful abstractions, which do not require an exceptional expertise to be used to build distributed C++ applications. The forthcoming C++ standard releases are clearly moving toward a full embedding of parallel transformations into the Standard Template Library (STL). This effort is currently limited to (cache-coherent) shared-memory programming model. This thesis aims forward and attempts to build on the embedding of distributed memory in mainstream C++.

#### **GAM** Nets

The programming model exposed by the Smart GAM Pointer tier envisions a collection of executors that exchange C++ smart pointers to (shared) data in a global, sequentially consistent distributed memory. According to the memory model, data can be accessed without data races (and without serialization). This crucially depends on capabilities and their movement among executors. Observe that this happens in a purely message passing style—indirect addressing of smart pointers is (deliberately) not supported by the GAM.

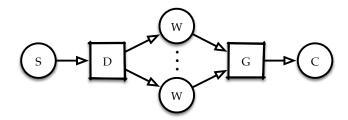

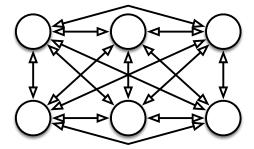

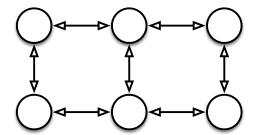

As discussed in Chapter 5, GAM Nets provide executors with message passing mechanisms to exchange pointers. In principle, they can be substituted with any message passing machinery, including MPI, as explored in preliminary work [74]. GAM Nets distinguish themselves from MPI along three main directions: 1) Computations and communications are clearly distinguished; GAM Nets provide a communication layer for executors rather than collective operations; executors have no role in supporting collective communications. 2) Communications are described by compoundable parametric patterns that can be statically evaluated for correctness and performance, e.g., mapped onto a fixed degree network such as a 2D torus. 3) GAM Nets realize fully asynchronous collective communications by design; no barriers, global or group synchronizations are necessary.

Furthermore, the GAM Nets tier represents a novel design of the "Distributed FastFlow" model [8], which addresses a number of weaknesses of the previous design (e.g., dynamic memory allocation). Moreover, the dependency on the ZeroMQ library has been replaced with a design based on the more general OFI (OpenFabrics Interface) framework.

1.2. Limitations 5

## **Higher-Level Parallel Programming Models**

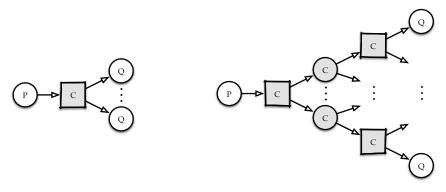

GAM Nets naturally target stream-parallel programming. However, as widely demonstrated in the literature, stream parallelism can be fruitfully exploited to implement other models. For instance, several frameworks for high-level parallel programming, such as OpenMP [116], FastFlow [17], and Flink [79], exploit stream parallelism for implementing data-parallel operations.

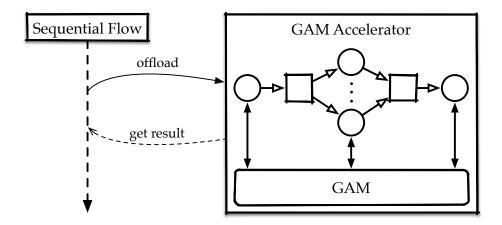

To exemplify the depicted approach, in Chapter 6, we discuss how GAM nets can be exploited to implement a library of containers with data-parallel operations, along the same line as the transformations—and their parallel variants—recently introduced in C++. We also discuss how GAM programs can be regarded as runtime systems in the context of task-based processing, targeting distributed platforms. Examples of recently proposed task-based frameworks include OCR [101] and HPX [90].

In addition to the considered examples, other models could be easily implemented in terms of GAM programs, from low-level PGAS languages (e.g., UPC [77], Chapel [45], X10 [46]) to high-level Domain-Specific Languages (DSLs).

## 1.2 Limitations

The main limitation of this thesis is the lack of a full-fledged experimental evaluation on large-scale High Performance Computing (HPC) clusters. Instead, we focused on *variety* and *heterogeneity* when selecting the platforms for the evaluation. For the former aspect, we considered three different networking hardware, namely, Ethernet, InfiniBand, and A3Cube RONNIEE; moreover, we considered both commodity and high-end workstations as cluster nodes. For the latter aspect, we considered the cluster-of-Graphics Processing Units (GPUs) architecture, including the case of multiple GPUs per cluster node, in addition to plain multi-core nodes.

Another limitation, from the programmability perspective, is the lack of any mechanism for automatizing the serialization (and de-serialization) of objects to be sent over the network by the GAM runtime. In this thesis, we assume that each value stored in the GAM memory has a representation in memory that allows the value to be copied by simply replicating its byte sequence. However, it would be easy to provide some mechanism for (semi-)automatic serialization, on top of a serialization library such as Boost.Serialize [39] or Google Protobuf [98].

Moreover, although we present smart global pointers by analogy with C++ smart pointers (see Chap. 4), we do not provide *weak* global pointers, that express non-owning references in their shared-memory counterparts. Consequently, in its current version, the proposed implementation does not support circular references of smart global pointers.

Finally, the current implementation does not exploit Remote Memory Access (RMA) primitives, though they are provided by most networking hardware nowadays. To this aim, we envision an improved implementation, in which we allocate GAM memory from RMA-capable regions of GAM executors' address space, to enable implementing GAM accesses as direct calls to RMA primitives.

## 1.3 List of Papers

In this section, I report the complete list of my publications, in reverse chronological order. Although the listed publications do not directly refer to the contributions included in the present thesis, most of them acted as either inspiration, preliminary study, or use case for the GAM stack, as we detail in the following.

We organize the publications along two dimensions. In Sect. 1.3.1, we categorize them based on the targeted *topic*, whereas in Sect. 1.3.2, we categorize them based on the publication type (i.e., journals, conferences, and others).

## 1.3.1 Publications by Topic

## **High Performance Tools for Big Data**

In recent years, an increasingly inter-connected ecosystem of heterogeneous devices has been producing larger volumes and variety of digital data. Those large volumes of dynamically changing data ought to be processed, synthesized, and eventually turned into knowledge. High-velocity data brings high value, especially to volatile business processes, mission-critical tasks, and scientific grand challenges. Some of this data lose their operational value within a short time frame, some other are simply too much to be stored. Because of this, data science is destined (sooner or later) to meet high-performance computing beyond parallel processing of batches on the file system.

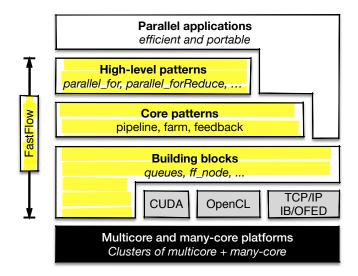

In this context, we recently proposed a novel C++14-based DSL based on a layered dataflow model for processing data collections, called PiCo (*Pipeline Composition*). The main entity of this programming model is the Pipeline, basically a Direct Acyclic Graph (DAG)-composition of processing elements. This model is intended to give the user a unique interface for both stream and batch processing, hiding completely data management and focusing only on operations, which are represented by Pipeline stages (see Sec. 7.1.4). Designing and coding an application with PiCo is easier than in Spark or Flink, and, on tested cases, PiCo is faster (sometime much faster) because it is designed according to HPC best practices. PiCo is built on top of the FastFlow library, and currently runs on shared-memory platforms. The GAM Nets tier, being fully compatible with FastFlow, will make it possible to easily port PiCo to distributed platforms. An extensive performance benchmarking of PiCo on top GAM Nets is among our future work. Related papers are the following: *J1*, *J2*, *C1*, *C2*, *C3*, *O1*.

#### **High-level Programming Models**

Parallel programming models are concerned with abstractions for parallel computing. The value of a programming model is primarily related with its expressiveness (for a given target class of algorithms) and its performance. The implementation of a parallel programming model can take the form of a library invoked from a sequential language, i.e., as an extension to an existing language, or as an entirely new language (even if the language does not necessarily define a new programming model).

We approached parallel programming convinced of the need to raise the level of abstraction with respect to the state of the art. By definition, the raison d'être for high-performance computing is... high performance. But peak Floating Point Operations Per Second (FLOPS) count is not the only measure to evaluate the impact of these technologies. Human productivity, total cost, time-to-market, reliability, energy consumption, etc., are equally, if not more important factors for any industrial follow-up. To date, attempts to develop high-level programming abstractions, tools, and environments for HPC have mostly failed. Suitable abstractions, however, are the keys to induce an industrial impact. Over the past twenty years, Web service programmers have built and embraced an ecosystem of libraries, scripting languages, software services, and tools that allowed them to create complex systems while hiding most of the underlying details of networks and computer systems. Their focus is on composition, abstraction, rapid deployment, software scaling, and human productivity. In sharp contrast, in the realm of HPC, message passing has remained the programming paradigm of choice for over twenty years.

Following the experience of algorithmic skeletons [51, 53], and using Fast-Flow as a laboratory [17], we experimented a number of parallel patterns to simplify the development of applications running on heterogeneous platforms, including multi-core platforms attached to multiple GPUs. Probably the most relevant is the hybrid Stencil-Reduce pattern, presented at Nvidia GPU Technology Conference (GTC) 2014 in San Jose, CA, USA. This approach (ported to OpenCL) significantly evolved during the "REPARA" EU FP7 to become the run-time engine of a high-level parallel programming approach based on "parallelization hints" over a standard C++ language. Differently from the mainstream OpenMP approach that uses compiler directives, in REPARA, parallelization directives are introduced as C++ attributes, which are part of the C++ standard rather than an extension to the language. A similar spirit motivated part of the present work, advocating the evolution of the C++ language to distributed systems rather than building on it yet another extension. Related papers are the following: [3, [5, [7, C4, C5, C9, C12, C16.

#### **Applications**

In parallel computing, benchmarks and applications are the standard tools to validate the research work. Parallel programming models are often concerned with several aspects of software engineering, such as scalability, portability, programmability, dependability. For this, we often invested on (complex) applications rather than kernels, as they make it possible to have a thorough evaluation of the proposed technique. Some of those applications have became research topic per se:

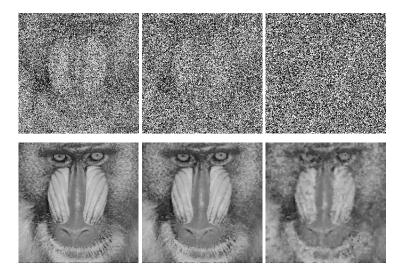

• Image and Video Restoration. This application is based on a novel algorithm for edge-preserving image processing based on variational analysis. The algorithm exhibits an exceptionally high restoration capability for images with high level of noise (e.g., 90% of impulsive noise, see Fig. 7.15) at the price of a high computational cost. The application can exploit both stream and data parallelism and is compute-bound. Also, it can greatly benefit from GPU acceleration.

- The application is also one of the use cases of this thesis (see Sec. 7.1.1). Related papers are the following: *J3*, *J5*, *J8*, *C5*, *C10*, *C13*, *O2*, *O3*.

- Next-generation Sequencing (NGS). Sequencing costs are rapidly decreasing because of new massively parallel sequencing technologies. The number of sequences available during the last years has experienced an amazing growth, making most of the existing analysis tools obsolete. In testing parallel programming models, and specifically FastFlow, a tool for the analysis of Chromosome Conformation Capture data has been proposed (called NuChart-II). Interestingly enough from the parallel computing viewpoint, this analysis requires to represent genomic information as a very large graph. The construction of the graph from raw DNA data is an irregular and memory-bound problem that is challenging to be coded in a scalable way. Its implementation on top of GAM Nets is among our possible future work. Related papers are the following: J4, J6, C6, C7, C8.

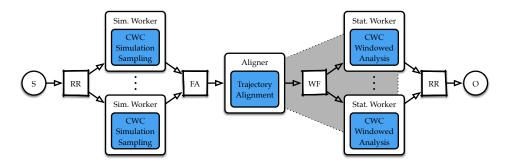

- Systems Biology. The CWC (Calculus of Wrapped Compartments) Systems Biology Simulator provides stochastic simulation of biological systems, which is a popular technique in Bioinformatics, in particular for its superior ability to describe transient and multi-stable behaviors of biological systems. However, stochastic simulation is computationally expensive, and the cost increases if the whole simulation-analysis workflow is considered. The efficient design of such a workflow is an interesting problem of parallel computing, since the frequency and size of data moved across the workflow strictly depend on the required accuracy. Indeed, it involves the merging of results from different simulation instances and possibly their statistical description or mining with data reduction techniques. The implementation of this application on top of GAM Nets is discussed in Sect. 7.1.3. Related papers are the following: J7, J8, J9, J10, C12, C14, C15, C16, C17, C18.

#### 1.3.2 Publications by Type

## **Journal Papers**

- (*J*1) C. Misale, M. Drocco, M. Aldinucci, and G. Tremblay. A comparison of big data frameworks on a layered dataflow model. *Parallel Processing Letters*, 27(01):1740003, 2017

- (J2) M. Torquati, G. Mencagli, M. Drocco, M. Aldinucci, T. De Matteis, and M. Danelutto. On dynamic memory allocation in sliding-window parallel patterns for streaming analytics. *Journal of Supercomputing*, 2017. To appear

- (*J*3) M. Aldinucci, M. Danelutto, M. Drocco, P. Kilpatrick, C. Misale, G. Peretti Pezzi, and M. Torquati. A parallel pattern for iterative stencil + reduce. *Journal of Supercomputing*, pages 1–16, 2016

- (*J4*) F. Tordini, M. Drocco, C. Misale, L. Milanesi, P. Liò, I. Merelli, M. Torquati, and M. Aldinucci. NuChart-II: the road to a fast and scalable tool for Hi-C data analysis. *International Journal of High Performance Computing Applications (IJHPCA)*, pages 1–16, 2016

- (J5) M. Aldinucci, G. Peretti Pezzi, M. Drocco, C. Spampinato, and M. Torquati. Parallel visual data restoration on multi-GPGPUs using stencil-reduce pattern. *International Journal of High Performance Computing Applications*, 29(4):461–472, 2015

- (*J6*) I. Merelli, F. Tordini, M. Drocco, M. Aldinucci, P. Liò, and L. Milanesi. Integrating multi-omic features exploiting Chromosome Conformation Capture data. *Frontiers in Genetics*, 6(40), 2015

- (J7) M. Aldinucci, C. Calcagno, M. Coppo, F. Damiani, M. Drocco, E. Sciacca, S. Spinella, M. Torquati, and A. Troina. On designing multicoreaware simulators for systems biology endowed with on-line statistics. *BioMed Research International*, 2014

- (*J8*) M. Aldinucci, M. Torquati, C. Spampinato, M. Drocco, C. Misale, C. Calcagno, and M. Coppo. Parallel stochastic systems biology in the cloud. *Briefings in Bioinformatics*, 15(5):798–813, 2014

- (*J*9) M. Coppo, F. Damiani, M. Drocco, E. Grassi, E. Sciacca, S. Spinella, and A. Troina. Simulation techniques for the calculus of wrapped compartments. *Theoretical Computer Science*, 431:75–95, 2012

- (*J*10) M. Coppo, F. Damiani, M. Drocco, E. Grassi, M. Guether, and A. Troina. Modelling ammonium transporters in arbuscular mycorrhiza symbiosis. *Transactions on Computational Systems Biology (TCS)*, 6575(13):85–109, 2011

#### **Conference Papers**

- (C1) M. Drocco, C. Misale, G. Tremblay, and M. Aldinucci. A formal semantics for data analytics pipelines. Technical report, Computer Science Department, University of Torino, May 2017

- (C2) C. Misale, M. Drocco, G. Tremblay, and M. Aldinucci. Pico: a novel approach to stream data analytics. In *Euro-Par 2017 Workshops Autonomic Solutions for Parallel and Distributed Data Stream Processing (Auto-Dasp)*, Santiago de Compostela, Spain, 2017. (Accepted)

- (C3) C. Misale, M. Drocco, M. Aldinucci, and G. Tremblay. A comparison of big data frameworks on a layered dataflow model. In *Proc. of HLPP2016: Intl. Workshop on High-Level Parallel Programming*, pages 1–19, Muenster, Germany, July 2016. arXiv.org

- (C4) M. Drocco, C. Misale, and M. Aldinucci. A cluster-as-accelerator approach for SPMD-free data parallelism. In *Proc. of Intl. Euromicro PDP* 2016: Parallel Distributed and network-based Processing, pages 350–353, Crete, Greece, 2016. IEEE

- (C5) M. Aldinucci, M. Danelutto, M. Drocco, P. Kilpatrick, G. Peretti Pezzi, and M. Torquati. The loop-of-stencil-reduce paradigm. In *Proc. of Intl. Workshop on Reengineering for Parallelism in Heterogeneous Parallel Platforms* (*RePara*), pages 172–177, Helsinki, Finland, Aug. 2015. IEEE

- (C6) F. Tordini, M. Drocco, C. Misale, L. Milanesi, P. Liò, I. Merelli, and M. Aldinucci. Parallel exploration of the nuclear chromosome conformation with NuChart-II. In Proc. of Intl. Euromicro PDP 2015: Parallel Distributed and network-based Processing. IEEE, Mar. 2015

- (C7) M. Drocco, C. Misale, G. Peretti Pezzi, F. Tordini, and M. Aldinucci. Memory-optimised parallel processing of Hi-C data. In *Proc. of Intl. Euromicro PDP 2015: Parallel Distributed and network-based Processing*, pages 1–8. IEEE, Mar. 2015

- (C8) F. Tordini, M. Drocco, I. Merelli, L. Milanesi, P. Liò, and M. Aldinucci. NuChart-II: a graph-based approach for the analysis and interpretation of Hi-C data. In C. D. Serio, P. Liò, A. Nonis, and R. Tagliaferri, editors, Computational Intelligence Methods for Bioinformatics and Biostatistics 11th International Meeting, CIBB 2014, Cambridge, UK, June 26-28, 2014, Revised Selected Papers, volume 8623 of LNCS, pages 298–311, Cambridge, UK, 2015. Springer

- (C9) M. Aldinucci, M. Drocco, G. Peretti Pezzi, C. Misale, F. Tordini, and M. Torquati. Exercising high-level parallel programming on streams: a systems biology use case. In *Proc. of the 2014 IEEE 34th Intl. Conference on Distributed Computing Systems Workshops (ICDCS)*, Madrid, Spain, 2014. IEEE

- (C10) M. Aldinucci, G. Peretti Pezzi, M. Drocco, F. Tordini, P. Kilpatrick, and M. Torquati. Parallel video denoising on heterogeneous platforms. In *Proc. of Intl. Workshop on High-level Programming for Heterogeneous and Hierarchical Parallel Systems (HLPGPU)*, 2014

- (C11) M. Drocco, M. Aldinucci, and M. Torquati. A dynamic memory allocator for heterogeneous platforms. In *Advanced Computer Architecture* and Compilation for High-Performance and Embedded Systems (ACACES) Poster Abstracts, Fiuggi, Italy, 2014. HiPEAC

- (C12) M. Aldinucci, F. Tordini, M. Drocco, M. Torquati, and M. Coppo. Parallel stochastic simulators in system biology: the evolution of the species. In *Proc. of Intl. Euromicro PDP 2013: Parallel Distributed and network-based Processing*, Belfast, Nothern Ireland, U.K., Feb. 2013. IEEE

- (C13) M. Aldinucci, C. Spampinato, M. Drocco, M. Torquati, and S. Palazzo. A parallel edge preserving algorithm for salt and pepper image denoising. In K. Djemal, M. Deriche, W. Puech, and O. N. Ucan, editors, *Proc. of 2nd Intl. Conference on Image Processing Theory Tools and Applications (IPTA)*, pages 97–102, Istambul, Turkey, Oct. 2012. IEEE

- (C14) M. Aldinucci, M. Coppo, F. Damiani, M. Drocco, E. Sciacca, S. Spinella, M. Torquati, and A. Troina. On parallelizing on-line statistics for stochastic biological simulations. In *Euro-Par 2011 Workshops, Proc.* of the 2st Workshop on High Performance Bioinformatics and Biomedicine (HiBB), volume 7156 of *LNCS*, pages 3–12, Bordeaux, France, 2012. Springer

- (C15) C. Calcagno, M. Coppo, F. Damiani, M. Drocco, E. Sciacca, S. Spinella, and A. Troina. Modelling spatial interactions in the arbuscular mycorrhizal symbiosis using the calculus of wrapped compartments. In

- I. Petre and E. P. de Vink, editors, *Proc. of Third International Workshop on Computational Models for Cell Processes (CompMod)*, volume 67 of *EPTCS*, pages 3–18, Aachen, Germany, Sept. 2011

- (C16) M. Aldinucci, M. Coppo, F. Damiani, M. Drocco, M. Torquati, and A. Troina. On designing multicore-aware simulators for biological systems. In Y. Cotronis, M. Danelutto, and G. A. Papadopoulos, editors, *Proc. of Intl. Euromicro PDP 2011: Parallel Distributed and network-based Processing*, pages 318–325, Ayia Napa, Cyprus, Feb. 2011. IEEE

- (C17) M. Coppo, F. Damiani, M. Drocco, E. Grassi, E. Sciacca, S. Spinella, and A. Troina. Hybrid calculus of wrapped compartments. In G. Ciobanu and M. Koutny, editors, *Proc. of 4th Workshop on Membrane Computing and Biologically Inspired Process Calculi (MeCBIC)*, volume 40 of *EPTCS*, pages 102–120, Jena, Germany, Aug. 2010

- (C18) M. Coppo, F. Damiani, M. Drocco, E. Grassi, and A. Troina. Stochastic calculus of wrapped compartments. In A. D. Pierro and G. Norman, editors, *Proc. of the 8th Workshop on Quantitative Aspects of Programming Languages (QAPL)*, volume 28 of *EPTCS*, pages 82–98, Paphos, Cyprus, Mar. 2010

## Other (Technical Reports, Posters, Talks, etc.)

- (O1) M. Drocco, C. Misale, G. Tremblay, and M. Aldinucci. A formal semantics for data analytics pipelines. Technical report, Computer Science Department, University of Torino, May 2017

- (O2) M. Aldinucci, M. Torquati, M. Drocco, G. Peretti Pezzi, and C. Spampinato. Fastflow: Combining pattern-level abstraction and efficiency in GPGPUs. In GPU Technology Conference (GTC 2014), San Jose, CA, USA, Mar. 2014

- (O3) M. Aldinucci, M. Torquati, M. Drocco, G. Peretti Pezzi, and C. Spampinato. An overview of fastflow: Combining pattern-level abstraction and efficiency in GPGPUs. In *GPU Technology Conference (GTC 2014)*, San Jose, CA, USA, Mar. 2014

## **Funding**

This work has been partially supported by the Italian Ministry of Education and Research (MIUR), by the EU-H2020 RIA project "Toreador" (no. 688797), the EU-H2020 RIA project "Rephrase" (no. 644235), the EU-FP7 STREP project "REPARA" (no. 609666), the EU-FP7 STREP project "Paraphrase" (no. 288570), and the 2015-2016 IBM Ph.D. Scholarship program. Experimentation was made possible thanks to the A3Cube Inc. donation of RONNIEE networking boards, and to Compagnia di SanPaolo for the donation of the OCCAM heterogeneous cluster.

# **Chapter 2**

# Background

In this chapter, we provide the background that will help the reader go through the arguments of the thesis. In particular, we discuss concepts and approaches from the literature on parallel computing, which acted as both inspiration and basis for comparison with respect to the contributions of the thesis.

This chapter proceeds as follows. In Sect. 2.1, we review the most common parallel computing platforms. In Sect. 2.2, we review state-of-the-art approaches for parallel programming. In Sect. 2.3, we introduce and discuss parallel memory models. Finally, in Sect. 2.4, we present the frameworks and libraries that we actually exploited for concretizing the contributions of the thesis.

## 2.1 Parallel Computing Platforms

Computing hardware has evolved to sustain the demand for high-end performance along two basic ways. On the one hand, the increase in clock frequency and the exploitation of instruction-level parallelism boosted the computing power of single processors. On the other hand, collections of processors have been arranged in multi-processors, multi-computers, and networks of geographically distributed machines.

After decades of continual improvement of single core chips trying to increase instruction-level parallelism, the majority of hardware manufacturers realized that the huge effort required for further improvements is no longer worth the benefits eventually achieved, notably because of power consumption. Thus, microprocessor vendors have shifted their attention to thread-level parallelism by designing chips with multiple internal cores, known as multi-cores (or chip multiprocessors). More generally, *parallelism* at multiple levels is now the driving force of computer design across all classes of computers, from small desktop workstations to large warehouse-scale computers.

We briefly recap Hennessy and Patterson's review of existing parallel computing platforms [84]. Following Flynn's taxonomy [80], we can define two main classes of architectures supporting parallel computing:

- Single Instruction Multiple Data (SIMD): the same instruction is executed by multiple processors on different data streams. SIMD computers support *data-level parallelism* by applying the same operations to multiple items of data in parallel;

- Multiple Instruction Multiple Data (MIMD): each processor fetches its own instructions and operates on its own data, and generally targets

task-level parallelism. In general, MIMD is more flexible than SIMD and thus more generally applicable to larger classes of problems, but it is inherently more expensive than SIMD.

The MIMD class can be further subdivided into two subclasses:

- Tightly coupled MIMD architectures, which exploit thread-level parallelism since multiple cooperating threads operate in parallel on the same execution context (e.g., multi-cores, discussed in Sect. 2.1.2, and many-cores, discussed in Sect. 2.1.3);

- Loosely coupled MIMD architectures, which exploit parallelism at coarser grain, where many independent tasks can proceed in parallel with little need for communication or synchronization (e.g., clusters, discussed in Sect. 2.1.4).

Although the SIMD/MIMD is a common classification, it is becoming more and more coarse, as many processors are nowadays "hybrids" of the classes above. For instance, in recent years, one of the most popular approach specifically targeting data-level parallelism consists in the use of GPUs for general-purpose computing, known as the General-Purpose computing on Graphics Processing Units (GPGPU) paradigm. Most of the GPGPU processors (cf. Sect. 2.1.3) are based on Single Instruction Multiple Thread (SIMT), a model of parallelism similar to SIMD, in which the same instruction is *possibly* executed by multiple processors on different data streams.

We proceed by providing a brief survey of the parallel platforms that can be found nowadays in HPC environments, in ascending order of parallelism degree. in Sect. 2.1.1, we discuss SIMD computers, the earliest form of parallel platforms. In Sect. 2.1.2, we discuss Symmetric Multiprocessors (SMPs), the most common form of standalone parallel computer. In Sect. 2.1.3, we discuss many-core computers, that are usually attached to standalone computers for accelerating specific computations. Finally, in Sect. 2.1.4, we discuss distributed systems, consisting in networks of interconnected computers, thus possibly aggregating all the discussed forms of parallelism.

## 2.1.1 SIMD computers

The first use of SIMD instructions was in 1970s with *vector supercomputers* such as the CDC Star-100 and the Texas Instruments ASC. Vector-processing architectures are now considered separate from SIMD machines: vector machines processed vectors one word at a time exploiting pipelined processors (though still based on a single instruction), whereas modern SIMD machines process all elements of the vector simultaneously [117].

Simple examples of SIMD computers are Intel SSE (Streaming SIMD Extensions) [87] for the x86 architecture. Processors implementing SSE (usually with a dedicated unit) can perform simultaneous operations on multiple operands in a single register. For example, SSE instructions can simultaneously perform eight 16-bit operations on 128-bit registers.

SSE evolved into AVX (Advanced Vector Extensions). Specifically, AVX-512 are 512-bit extensions to the 256-bit AVX instructions for x86 Instruction

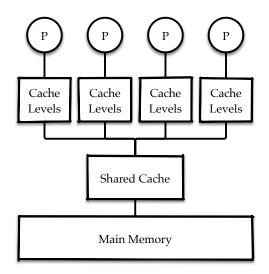

FIGURE 2.1: Structure of a 4-processor SMP.

Set Architecture (ISA), proposed by Intel in July 2013, and supported in Intel's Xeon Phi x200 (a.k.a. Knights Landing) processor [88]. Programs can pack various number of elements all within a single 512-bit vectors—e.g., eight double precision or sixteen single precision floating-point numbers, or eight 64-bit integers, or sixteen 32-bit integers. This enables processing twice the number of data elements that AVX/AVX2 can process with a single instruction and four times that of SSE.

Advantages of such approaches consist in almost negligible overhead and low hardware cost. However, they are difficult to integrate into existing code, as they actually require writing code in assembly language. Moreover, although many compilers provide automatic vectorization (e.g., collapsing independent loop iterations in a single SIMD instruction), the applicability of this technique is limited to extremely regular code.

## 2.1.2 Shared-Memory Multiprocessors

Thread-level parallelism implies the existence of multiple program counters, hence it must be exploited primarily through MIMDs. Threads can also be used to support data-level parallelism, but some overhead is introduced at least by thread communication and synchronization. This overhead means the *grain size* (i.e., the ratio of computation to the amount of communication), a key factor for efficient exploitation of thread-level parallelism, must be properly selected.

The most common MIMD computers are multiprocessors, defined as computers consisting of *tightly coupled* processors that share memory. SMPs typically feature small numbers of cores (nowadays from 12 to 24), where processors can share a single *centralized* memory, to which they all have equal access (Fig. 2.1). Among them, single-chip systems with multiple cores are known as *multi-cores*. In multi-core chips, the memory is effectively centralized, and all existing multi-cores are SMPs. SMP architectures are also sometimes called Uniform Memory Access (UMA) multiprocessors, arising from the fact that all processors have a uniform latency from memory, even if the memory is organized into multiple banks.

The alternative "asymmetric" design approach consists in using multiprocessors with physically distributed memory. To support larger numbers of processors, memory must be distributed rather than centralized—otherwise, the memory system would not be able to support the bandwidth demands of processors without incurring excessively long access latency. Such architectures are known as Non-Uniform Memory Access (NUMA), since the access time depends on the location of data in memory.

Multiprocessors usually support the caching of both shared and private data, reducing the average access time as well as the required memory bandwidth. Unfortunately, caching shared data introduces a new problem because the view of memory held by two different processors is through their individual caches, which could end up seeing two different values. This problem is generally referred to as the *cache coherence problem* and several *protocols*, referred to as cache coherence protocols, have been designed to guarantee cache coherence.

From the performance perspective, guaranteeing cache coherence introduces a number of pitfalls. For instance, *false sharing* is a subtle source of cache miss, which arises from the use of an invalidation-based coherence algorithm and multiple words block. False sharing occurs when a block is invalidated (and a subsequent reference causes a miss) because some word in the block, other than the one being read, is written into. In a false sharing miss, the block is shared, but no word in the cache is actually shared, and the miss would not have occurred if the block consisted of a single word.

On top of cache coherence, each ISA specifies a *memory consistency model*, that addresses the general problem of defining the behavior of multiple processors with respect to the memory they are attached to.

We discuss cache coherence and memory consistency in more detail in Sects. 2.3.1 and 2.3.2, respectively.

## 2.1.3 Many-Core Processors

Many-Core processors are specialized multiprocessors designed to exploit a high degree of parallelism, containing a large number of simpler, independent processor cores. They are often referred to as *hardware accelerators*. A many-core processor contains at least tens—if not hundreds—of cores and usually distributed memory, which are connected (but physically separated) by an interconnect that has a communication latency of multiple clock cycles [118]. A multiprocessor architecture (e.g., a multi-core) equipped with hardware accelerators is a form of *heterogeneous architecture*.

We can compare multi-core to many-core processors as follows:

- Multi-core: a SMP architecture containing tightly coupled identical cores that all share memory, where caches coherence is guaranteed.

- Many-Core: specialized multiprocessors designed for a high degree of parallel processing, containing a large number of simpler, independent processor cores (e.g., tens up to thousands) with a reduced cache coherency to increase performance. Indeed, as the core count increases, cache coherency is unlikely to be sustained by the hardware [48].

Although broadly different types of accelerators have been proposed, they do share some features. For instance, cores in many-core processors are typically slower with respect to multi-core processors, and the high performance is obtained by high level of parallelism rather than high speed of each core. Moreover, data transfer from the host to the accelerator is typically slower than the memory bandwidth within the host processor, therefore exploiting locality is mandatory to achieve good performance.

In the following, we recap some of the accelerators that can be found in several HPC scenarios.

- GPUs include a large number of small processing cores (from hundreds to thousands) in an architecture optimized for highly parallel workloads, paired with dedicated high performance memory. They are accelerators, used from a general purpose CPU, that can deliver high performance for some classes of algorithms.

- Intel Xeon Phi is a brand name given to a series of massively-parallel multi-core co-processors designed and manufactured by Intel, targeted at HPC. A crucial component of each co-processor's core is the Vector Processing Unit (VPU), for the execution of AVX-512 SIMD instructions. Currently, the Knights Landing family (the successor of the first Xeon Phi) features 64 to 72 cores, with 4 thread contexts per core, organized as interconnected tiles, each containing two CPU cores and two VPUs per core (i.e., four VPUs per tile).

- Field Programmable Gate Arrays (FPGAs) are semiconductor devices based around a matrix of configurable logic blocks, connected via programmable interconnects. FPGAs can be reprogrammed to desired application or functionality requirements after manufacturing. The FPGA configuration is generally specified using a hardware description language, similar to that used for an application-specific integrated circuit.

## 2.1.4 Distributed Systems, Clusters, and Clouds

In contrast with shared-memory architectures, *distributed systems* look like individual computers, each owning exclusive access to its private memory, connected by a network. With respect to Flynn's categorization, distributed systems are examples of loosely coupled MIMDs.

Clusters are generally defined as homogeneous distributed systems, in the sense that the computers in the network are identical. Therefore, both program binaries and data are represented in the same manner (e.g., endianness) on each computer in the cluster, thus allowing the computers to exchange and process data without introducing additional layers of data conversion. Moreover, users of a cluster typically have *direct* access to the computing resources, possibly mediated by some allocation mechanism. The mentioned aspects leads clusters to be considered the reference model of distributed system in the context of HPC.

Conversely, large-scale distributed systems are typically heterogeneous and they form the basis for *cloud computing*, in which an infrastructure is offered by providers according to a *pay-per-use* business model. In a common cloud model, referred to as Infrastructure-as-a-Service (IaaS), providers offer computers—either physical or (more often) virtual machines—and other resources on-demand. End users are not required to (or, depending on the

viewpoint, allowed to) take care of hardware, power consumption, reliability, robustness, security, and the problems related to the deployment of a physical computing infrastructure.

## 2.2 Parallel Programming Models

Shifting from sequential to parallel platforms, as discussed in the previous section, does not always translate into greater performance. For instance, sequential code (i.e., code not exploiting any form of parallelism) will get no performance benefits from a workstation equipped with a quad-core CPU: in such a case, running sequential code is wasting  $\frac{3}{4}$  of the machine computational power. Developers are then faced with the challenge of achieving a trade-off between performance and human productivity (total cost and time to solution) in developing and porting applications to parallel platforms.

Therefore, effective parallel programming happens to be a key factor for exploiting parallel computing, but efficiency is not the only issue faced by parallel programmers: writing parallel code that is portable on different platforms and maintainable are also issues that parallel programming models should address.

We proceed by recalling, in Sect. 2.2.1, the forms of parallelism that can be expressed in the most common parallel programming models and, in Sect. 2.2.2, some shared memory and communication models, regarded as orthogonal aspects in this thesis. Finally, in Sects. 2.2.3 and 2.2.4, we provide a survey of low-level and high-level parallel programming models, respectively, with a focus on the C++ realm.

## 2.2.1 Types of Parallelism

Parallel programming models allow to express parallelism in programs. In the following, we recall some common types of parallelism, as provided by the models proposed in various well-established parallel programming models.

- Task Parallelism consists of running independent computations (i.e., tasks) on different executors (cores, processors, etc.), according to a task-dependency graph. Tasks are concretely processed by threads or processes, which may communicate with one another as they execute. Communication takes place usually to pass data from one thread to the next as part of a graph.

- *Data Parallelism* is a method for parallelizing a single task by processing independent data elements in parallel. The flexibility of the technique relies upon stateless processing routines, implying that the data elements must be fully independent. Data Parallelism is often realized in terms of *Loop-level Parallelism*, where successive iterations of a loop working on independent or read-only data are parallelized in different flows-of-control (according to the model *co-begin/co-end*) and concurrently executed.

- *Stream Parallelism* is a method for parallelizing the execution (aka. filtering) of a stream of tasks by segmenting each task into a series of

sequential<sup>1</sup> or parallel stages. This method can be also applied when there exists a total or partial order in a computation, preventing the use of data or task parallelism. This might also come from the successive availability of input data along time (e.g., data flowing from a device). By processing data elements in order, local state may be either maintained in each stage or distributed (replicated, scattered, etc.) along streams. Parallelism is achieved by running each stage simultaneously on subsequent or independent data elements.

## 2.2.2 Memory and Communication Model

From a programming perspective, memory is represented in terms of *address spaces*, accessed by processing units (e.g., processes or threads). In the space of parallel programming models, *shared-memory* models yield programs composed of a single address space, shared by all processing units. This shared space is also referred as Global Address Space (GAS). Conversely, *distributed-memory* models yield programs in which each executor is attached to a private address space, that cannot be accessed by any other executor.

A further categorization of parallel programming models can be formulated in terms of the *communication* model among processing units. In models based on *message passing*, communications among processing units are performed via explicit messages. When processing units need to exchange data among each other, this exchange is done by *sending* and *receiving* messages, which typically requires cooperative operations among the two units involved in the communication (namely, the *sender* and the *receiver*). This aspect induces tight coupling of processing units: any send operation must have its corresponding receive operation, otherwise a deadlock can occur, since the process can be waiting indefinitely for completion.

In distributed-memory models, message passing is the only viable option for exchanging data among processing units, therefore all distributed-memory models are based on message passing as communication model. Note that exchanging data in the form of messages induces some extra effort. For instance, it typically requires data to be *serialized* and de-serialized, which introduces complexity and possible performance penalties, in particular when working with complex data structures.

In shared-memory programming, processing units share the GAS, in which they communicate implicitly via load/store primitives. The memory locations of the GAS can be used to effectively exchange data among threads, but the access to memory locations must always be coordinated (e.g., by locks/semaphores) to prevent data races, starvations or deadlocks. Some shared-memory programming model also provides communication by means of message passing, that can be exploited as an alternative synchronization and coordination mechanism, with respect to semaphores and atomic instructions.

We remark that *shared-memory* models can be implemented on top of distributed platforms (cf. Sect. 2.1.4), with the assistance of software protocols. In the simplest realization of this approach, which is historically referred as DSM, the memory interface (i.e., the Application Programming

<sup>&</sup>lt;sup>1</sup>In the case of total sequential stages, the method is also known as *Pipeline Parallelism*.

Interface (API) provided to processing units to access the GAS) is the same as a shared-memory model based on physically shared memory. According to DSM models, the GAS can be accessed by the processing units using a plain load/store API and some form of strong consistency (cf. 2.3.2) is guaranteed. Although retaining the simplicity of shared-memory models when programming distributed platforms seems attractive, the DSM approach faded away, mainly because of the inherent limits to scalability imposed by keeping memory consistent. Nevertheless, in recent years, a number of GAS models have been proposed for distributed platforms, both enriching the memory interface and relaxing the consistency model. For instance, the PGAS paradigm (cf. Sect. 2.2.3) revamped the DSM approach by adding syntactic mechanisms to control data locality.

## 2.2.3 Low-Level Programming Models

We denote as *low-level* parallel programming models that provide the programmers with a thin abstraction over the underlying parallel platform to be programmed. For instance, on top of a shared-memory multiprocessor, a low-level programming model typically provides primitives for managing the lifetime of processing units (i.e., threads), their synchronization and data sharing, typically accomplished through critical regions accessed in mutual exclusion. Low-level languages are usually extensions to well-established sequential languages, such as C/C++, Java, or Fortran, by means of external libraries, linked at compile time to the application source code (e.g., *Pthreads*, *MPI*), or enriched with specific constructs (e.g. C++ Threads).

## **Shared-Memory Platforms**

*POSIX Threads* (or Pthreads) [43], one of the most used low-level parallel programming API for shared-memory environments, are defined by the POSIX.1c standard, Threads extensions (IEEE Std 1003.1c-1995). They are present in every Unix-like operating system (Linux, Solaris, Mac OS X, etc.) and other POSIX systems, giving access to OS-level primitives for creation and synchronization of threads.

From the programming model perspective, with respect to the categorization discussed above, Pthreads provides shared-memory programming. Since no primitives are provided for explicit communication among threads, the user has to implement implicit communication by means of *concurrent data structures* (i.e., data structures accessed concurrently by multiple threads) as, for instance, First-In First-Out (FIFO) queues.

Since Pthreads is a C library, it can be used in C++ programs as well. However, a well-known report by Boehm [37] provides specific arguments that a pure library approach, in which the compiler is designed independently of threading issues, cannot guarantee correctness of the resulting code, for instance with respect to the parallel memory model (cf. Sect. 2.3). The report shows simple cases (e.g., concurrent modification, adjacent data rewriting and register promotion) in which a pure library-based approach is incapable of expressing a correct and efficient parallel algorithm. For these and similar reasons, the C++11 standard, published in 2011, introduced multithreaded programming. We remark that ISO C++ is completely

independent from POSIX and it is provided also in non-POSIX platforms. In a similar fashion, *Java* provides multi-threading for writing parallel applications according to a shared-memory programming model [113].

In contrast to Pthreads, multithreading in ISO C++ includes a complete *parallel memory model* (abbr. memory model), that defines the behavior of parallel programs with respect to memory accesses. The C++ memory model has been formulated by Boehm et al. [38], on the same line as the Java memory model [99]. As we discuss in more detail in Sect. 2.3.2, the key concept is guaranteeing safe memory behaviors for safe programs, where program safeness is ensured by either avoiding concurrent stores to the same memory location or mediating them by special operations.

CUDA (Compute Unified Device Architecture) [111] is the reference language for programming Nvidia GPUs, according to the GPGPU paradigm. Although there have been recent efforts (e.g., Nvidia Thrust library [112], discussed in Sect. 6.1.2) for partially reducing the gap between high computational power, provided by GPUs, and easiness of programming, we still regard CUDA as a low-level parallel programming approach, since, in the general case, the user has to deal with close-to-metal aspects like memory allocation and data movement between the GPU and the host platform. Moreover, CUDA programming is thread-centric, which induces non-trivial consequences when programming data-parallel applications, as discussed by Drocco et al. [74].

OpenCL (Open Computing Language) [93] is an API designed to write parallel programs that execute across heterogeneous architectures, including GPUs. It is implemented by different hardware vendors such as Intel, AMD, and Nvidia, thus making programs portable with respect to hardware accelerators. For instance, OpenCL applications are seamlessly reverted to the CPU for execution when there is no GPU in the system, and its portability makes it suitable for hybrid CPU/GPU environments. Moreover, OpenCL allows the implementation of applications onto FPGAs, allowing software programmers to write hardware-accelerated kernel functions in OpenCL C, an ANSI C-based language with additional OpenCL constructs. OpenCL represents an extension to C/C++ but, as CUDA, must be considered a low-level language, focusing on low-level features management rather than high-level parallelism exploitation patterns. Nevertheless, as for CUDA, recent efforts (e.g., SYCL [94]) aim at raising the programming level by hiding low-level details.

#### **Distributed Platforms**

MPI [115] is a language-independent communication protocol, as well as a message-passing API, that supports point-to-point and collective communication. Many general-purpose programming languages have bindings to MPI functionalities, among which: C, C++ (e.g., notably, Boost.MPI [40]), Fortran, Java, and Python. Mainly targeted to distributed architectures, MPI offers specific implementations for almost any high-performance interconnection network. At the same time, implementations exist that allow to use MPI even on standalone multiprocessor systems.

From the programming model perspective, with respect to the categorization discussed above, MPI provides message-passing communication on top of a distributed-memory model. Moreover, programming in MPI

implicitly follows the Single Program Multiple Data (SPMD) paradigm [63], in which all processing units execute the same program, each operating on its local chunk of data.

MPI allows to manage synchronization and communication functionalities among a set of processes, and provides mechanisms to deploy a virtual topology on top of the system upon which the program is executing. These features, supported by a rich set of capabilities and functions, clearly require high programming and networking skills. Nevertheless, MPI has long been the lingua franca of HPC, supporting most of the supercomputing scientists and engineers have relied upon for the past two decades.

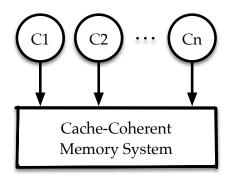

Shifting from the distributed-memory to the shared-memory programming model, UPC (Unified Parallel C) [77] is a long-standing example of the PGAS approach, expressed through a C language extension. In UPC, any processor can directly read and write variables on the partitioned address space, while each variable is physically associated with a single processor. Each thread is associated to a partition of the GAS, which is subdivided into a *local* portion and a *shared* portion. Local data can be accessed only by the thread that owns the partition, while data in the shared portion are accessible by all threads. Since PGAS is a shared-memory model, threads access shared memory addresses concurrently through standard read and write instructions. This programming model is still a low-level shared-memory environment, and uses barriers and locks to synchronize the execution flow.

Several PGAS languages and libraries have been proposed. Such languages can be categorized along a number of orthogonal dimensions, including relationship between local and shared data, model of communication among processors, representation of global memory reference (e.g., global pointers), supported forms of parallelism, and level of memory consistency. Among the most successful PGAS languages, we can mention *Global Arrays* [110], *UPC* (*Unified Parallel C*) [77], *UPC*++ [131], *Chapel* [45], and *X10* [46].

On the same line as the DSM paradigm, several Global Object Space (GOS) languages have been proposed. For instance, *Charm*++ [91] is a C++ variant providing objects with parallel semantics and supporting compilation for both shared-memory and distributed platforms. Similarly, *ADHOC* (*Adaptive Distributed Herd of Object Caches*) [15] provides virtualization of local memories (i.e., partitions) into an unique distributed object repository. Also the popular memcached [102] caching system is based on distributed memory objects, thus it can be regarded as a realization of the GOS paradigm.

## 2.2.4 High-level Programming Models

Parallel programming is intimately related to HPC environments, where programmers write low-level parallel code to retain complete control over the underlying platform, allowing them to manually optimize the code in order to exploit at best the parallel architecture. This programming methodology has become unsuitable with the fast move to heterogeneous architectures, that encompass hardware accelerators, distributed shared-memory systems and cloud infrastructures, highlighting the need for proper tools to easily implement parallel applications. Indeed, it is widely acknowledged that the main problem to be addressed by a parallel programming model

is *portability*: the ability to not only compile and execute the same code on different architectures [65], but also—and generally even more complex—the challenge of performance portability, that is, implementing applications that scale on different architectures.

A high-level approach to parallel programming is a better way to go to address this problem, so that programmers can build parallel applications and be sure that they will perform reasonably well on the wide range of parallel architectures available today [120]. For instance, threads might be abstracted out in higher-level entities that can be pooled and scheduled in user space possibly according to specific strategies to minimize cache flushing or maximize load balancing of cores. Synchronization primitives can be also abstracted out and associated to semantically meaningful points of the code, such as function calls and returns, loops, etc. Intel TBB (Threading Building Blocks) [89], OpenMP (Open Multi-Processing) [116], and Cilk [50] all provide those kinds of abstraction, each in its own way. A complete review of these parallel programming models is proposed by Sanchez et al. [119], where it is provided a comparative study and evaluation of OpenMP, TBB, Cilk, Intel ArBB (Array Building Blocks) and OpenCL. The study covers several capacities, such as task deployment, scheduling techniques, or programming language abstractions.

Arguably, the most basic form of abstraction to raise the level of abstraction and reduce the programming effort is based on *tasks*. As we discuss in more detail in Sect. 6.2.1, any parallel computation can be described in terms a graph of tasks, where independent tasks (i.e., not linked) can be performed in parallel. Following this principle, a number of frameworks for task-based parallel programming have been proposed. For instance, OCR (Open Community Runtime) [101, 71, 29] is a recently proposed task-based runtime system, targeting future extreme-scale applications.

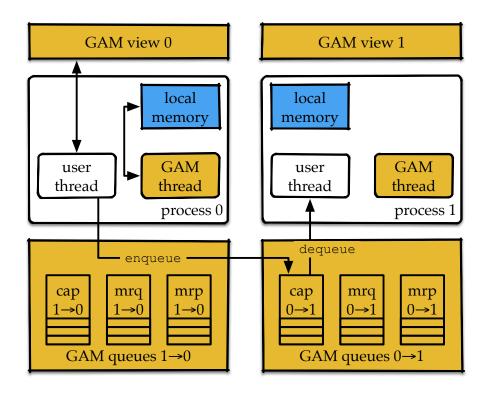

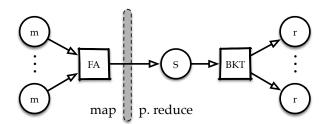

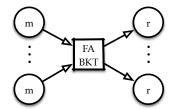

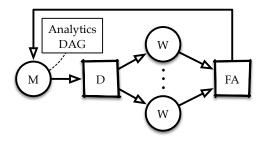

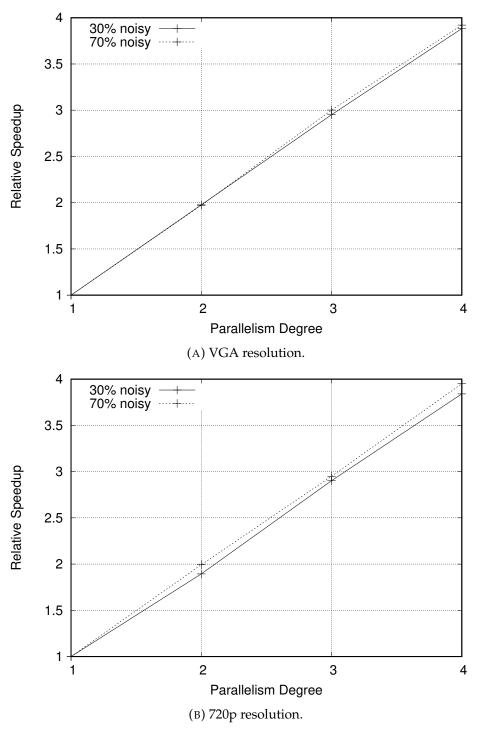

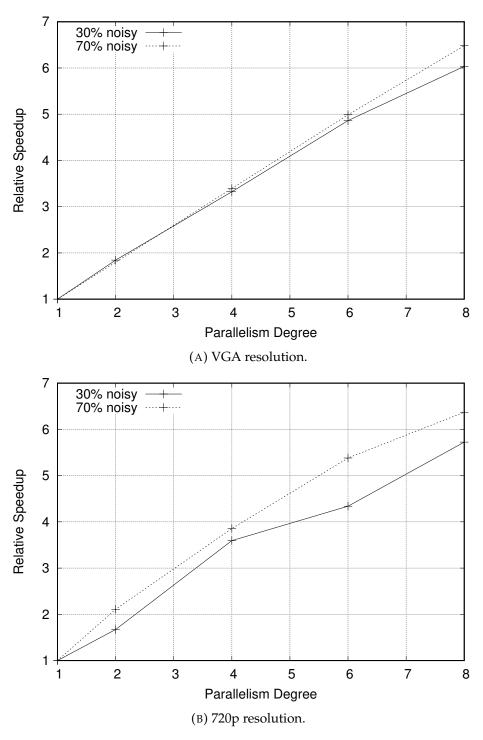

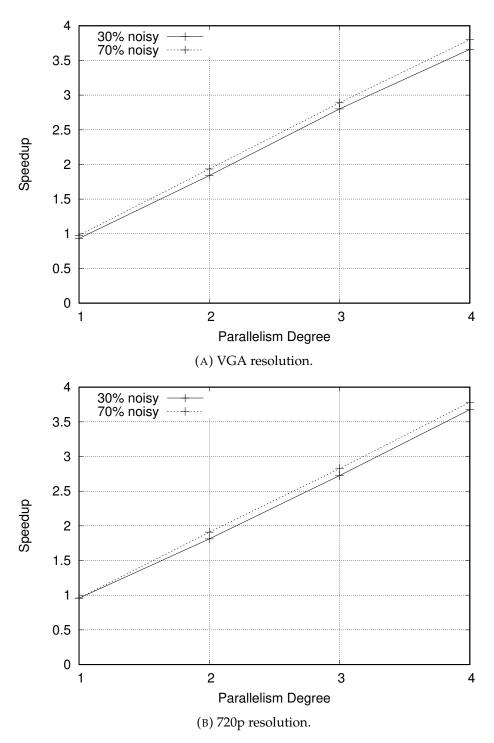

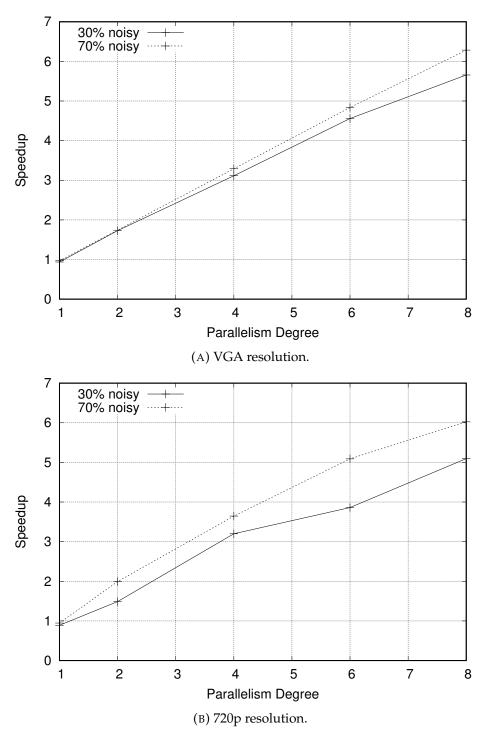

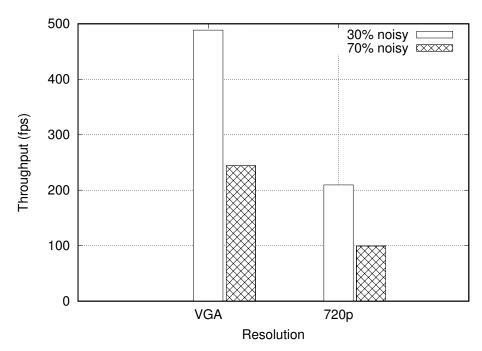

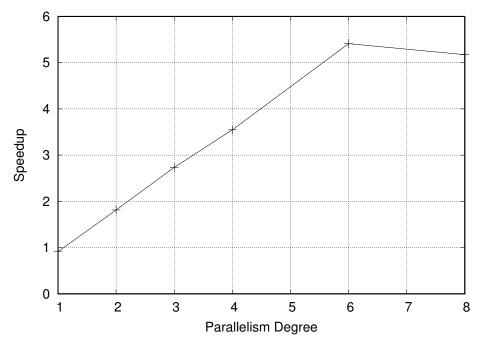

Further along the direction of raising the level of abstraction, notable results have been achieved by the algorithmic skeleton approach [52] (aka. pattern-based parallel programming), that has gained popularity after being revamped by several successful parallel programming frameworks. Algorithmic skeletons have been initially proposed by Cole [53] to provide predefined parallel computation and communication patterns, hiding parallelism management from the user. Algorithmic skeletons capture common parallel programming paradigms (e.g., Map+Reduce, ForAll, Divide and Conquer, etc.) and make them available to the programmer as high-level programming constructs equipped with well-defined functional and extrafunctional semantics [12]. Ideally, algorithmic skeletons address the difficulties of parallel programming (i.e., concurrency exploitation, orchestration, mapping, tuning) by moving them from the application design to development tools, which is done by capturing and abstracting common paradigms of parallel programming and providing them with efficient implementations. This idea can be considered at the core of structured parallel programming: expressing the parallel code as a composition of simple "building blocks".