# CARNEGIE MELLON

# Department of Electrical and Computer Engineering

Architecture Synthesis of High-Performance

Application-Specific Processors

Mauricio Breternitz Júnior

April, 1991

## CARNEGIE MELLON UNIVERSITY

# ARCHITECTURE SYNTHESIS OF HIGH-PERFORMANCE APPLICATION-SPECIFIC PROCESSORS

A DISSERTATION

SUBMITTED TO THE GRADUATE SCHOOL

IN PARTIAL FULFILLMENT OF THE REQUIREMENTS

for the degree

DOCTOR OF PHILOSOPHY  $_{\text{in}}^{\text{in}}$  ELECTRICAL AND COMPUTER ENGINEERING

by

MAURÍCIO BRETERNITZ JÚNIOR

Pittsburgh, Pennsylvania April, 1991

# Abstract

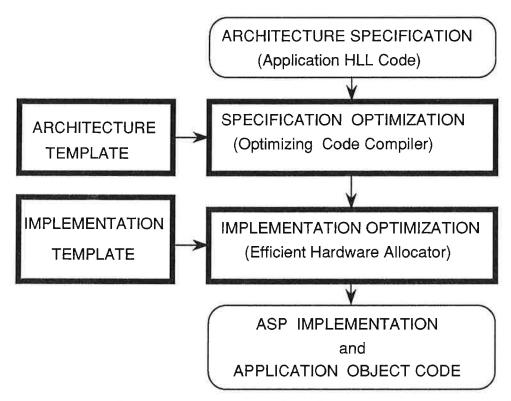

A new method to design Application-Specific Processors (ASP) for computation-intensive scientific and/or embedded applications is presented. Target application areas include scientific and engineering programs and mission-oriented signal-processing systems requiring very high numerical computation and memory bandwidths. The application code in conventional HLL such as Fortan or C is the input to the synthesis process. Latest powerful VLSI chips are used as the primitive building blocks for design implementation. The eventual performance of the application-specific processor in executing the application code is the primary goal of the synthesis task. Advanced code scheduling techniques that go beyond basic block boundaries are employed to achieve high performance via exploitation of fine-grain parallelism. The Application-Specific Processor Design (ASPD) method divides the task of designing an special-purpose processor architecture into Specification Optimization (behavioral) and Implementation Optimization (structural) phases. An architectural template resembling a scalable Very Long Instruction Word (VLIW) processor and a suite of compilation tools are used to generate an optimized processor specification. The designer quickly explores various cost versus performance tradeoff points by performing repeated compilation for scaled architectures. The powerful microcode compilation techniques of Percolation Scheduling and Enhanced Pipeline Scheduling extract and enhance parallelism in the application object code to generate highly parallelized code, which serves as the optimized specification for the architecture. Further performance/efficiency enhancement is obtained in Implementation Optimization by tailoring the implementation template to the execution requirements of the optimized processor specification. A scalable implementation template constrains the implementation style. Graph-coloring algorithms that exploit special graph characteristics are used to minimize the amount of hardware to support execution of the optimized application microcode without impairing code performance. Compilation techniques to allocate data over multiple memory banks are used to enhance concurrent access. The entire architecture synthesis procedure has been implemented and applied to numerous examples. Speedups in the range of 2.6 to 7.7 over contemporary RISC processors have been obtained. The computation times needed for the synthesis of these examples are on the order of a few seconds.

# **Dedication**

To him who is able to keep you from falling and to present you before his glorious presence without fault and with great joy — to the only God our Saviour be glory, majesty, power and authority, through Jesus Christ our Lord, before all ages now and forevermore. Amem. [Jude 24:25]

Ora, àquele que é poderoso para vos guardar de tropeços e para vos apresentar com exultação, imaculados diante da sua glória, ao único Deus, nosso Salvador, mediante Jesus Cristo, Senhor nosso, glória, majestade, império e soberania, antes de todas as eras e agora, e por todos os séculos. Amem. [Judas 24:25]

# Acknowledgements

First, I would like to thank my advisor, John Paul Shen, for his leadership during this thesis. I benefitted and learned from John's ability to help clarify rough ideas, identify key conceptual issues and express them in concise text. John's enthusiasm and open-minded researh approach, along with his clear example of Christian living challenged and taught me a number of things about life and myself.

I would also like to thank professors Daniel P. Siewiorek, Donald E. Thomas and Alex Nicolau for serving in my thesis committee. Dan and Don are credited for their leadership in the area of digital systems systhesis. Alex invented Percolation Scheduling, a fine-grained compilation technique which is a key element in this thesis. Alex's accessibility and willingness to answer questions helped smooth the way. Roni Potasman and Haigeng Wang worked on our VLIW compiler project as participants of the Percolation Scheduling group at U.C.Irvine under Alex's leadership.

Andy Wolfe, Chriss Stephens and Ron Bianchini were key members of the White Dwarf project. Chriss also helped with the VLIW compiler graphic interface, originally developed by Dan Nydick. Chris Holt and Greg Palmer created the graph coloring software package.

During my work on the VLIW project at the IBM T.J.Watson lab, I interacted with Dave George, Mickey Tsao and Kemal Ebcioglu. Dave's project leadership helped me come onboard and Mickey helped deal with IBM internals. I learned a lot while interacting with Kemal during our development of the VLIW compiler prototype.

My dear friend Jim McInerney deserves more than a paragraph, perhaps a chapter. Jim and I agree to disagree on must subjects, which makes our weekly Saturday breakfasts even more enjoyable. This helped me come to a better appreciation and understanding of this great country along with its many shortcomings. Jim has been a great *companheiro* during the inevitable ups and downs of life during Ph.D. research.

The friendship of Alberto and Noemia Elfes, Eleri Cardozo, Hudson and Susana Ribas, Haroldo and Otilia Costa Lima and Edna and Marco "Gubi" Gubitoso of the Pittsburgh brazilian community provided much needed home base support. I'll remember with saudades all those years of shared life and times together.

Finally, thanks to my wife Martha Rubio Breternitz for almost everything else. Martha temporarily forsaked her career in architecture so that I could perform this work. This research would not have been completed without Martha's patient and loving support. I thank her for being there during the hard times and for sharing with joy the good times. The arrival of our daughter Raquel helped me understand how much more can love be extended without thinning.

This work was supported in part by CNPQ of Brazil and in part by IBM.

# Contents

| 1 | Int           | Introduction                                                        |  |  |  |  |  |  |

|---|---------------|---------------------------------------------------------------------|--|--|--|--|--|--|

|   | 1.1           | Motivation                                                          |  |  |  |  |  |  |

|   | 1.2           | Background                                                          |  |  |  |  |  |  |

|   | 1.3           | Architecture Synthesis Approach                                     |  |  |  |  |  |  |

|   | 1.4           | Thesis Overview                                                     |  |  |  |  |  |  |

| 2 | $\mathbf{Ar}$ | chitecture Synthesis                                                |  |  |  |  |  |  |

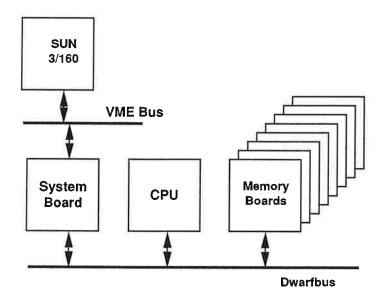

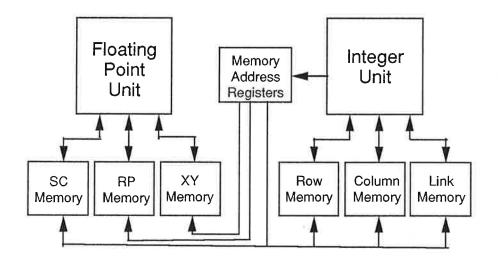

|   | 2.1           | White Dwarf Experimental Project                                    |  |  |  |  |  |  |

|   |               | 2.1.1 FEM Application                                               |  |  |  |  |  |  |

|   |               | 2.1.2 White Dwarf Design process                                    |  |  |  |  |  |  |

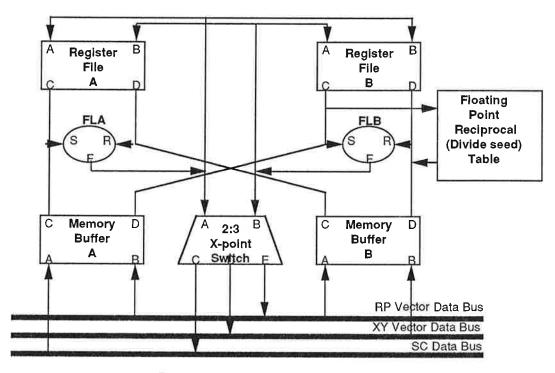

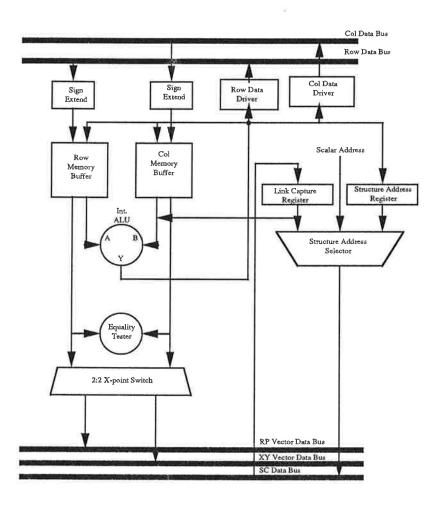

|   |               | 2.1.3 White Dwarf Processor Architecture                            |  |  |  |  |  |  |

|   |               | 2.1.4 White Dwarf Performance Evaluation                            |  |  |  |  |  |  |

|   | 2.2           | Architectural and Implementation Models                             |  |  |  |  |  |  |

|   |               | 2.2.1 The VLIW Architecture                                         |  |  |  |  |  |  |

|   |               | 2.2.2 Implementation Architectural Template                         |  |  |  |  |  |  |

|   | 2.3           | Application-Specific Processor Design (ASPD)                        |  |  |  |  |  |  |

| 3 | Sp            | ecification Optimization 29                                         |  |  |  |  |  |  |

|   | 3.1           | Specification Optimization Procedure                                |  |  |  |  |  |  |

|   | 3.2           | Intra-Iteration Techniques                                          |  |  |  |  |  |  |

|   |               | 3.2.1 Percolation Scheduling Core Transformations                   |  |  |  |  |  |  |

|   |               | 3.2.2 Percolation Scheduling with Register Renaming                 |  |  |  |  |  |  |

|   |               | 3.2.3 Computation of Unifiable-ops                                  |  |  |  |  |  |  |

|   |               | 3.2.4 Memory-Reference Disambiguation                               |  |  |  |  |  |  |

|   |               | 3.2.5 Detection of Induction Variables via Symbolic Substitution 43 |  |  |  |  |  |  |

|   | 3.3           | Inter-Iteration Techniques                                          |  |  |  |  |  |  |

|   |               | 3.3.1 Enhanced Software Pipelining                                  |  |  |  |  |  |  |

|   |               | 3.3.2 Removing Extraneous Copy Operations from Pipelining           |  |  |  |  |  |  |

| 4 | Re            | targetable Optimizing Compiler 54                                   |  |  |  |  |  |  |

|   | 4.1           | Fine-Grain/Microcode Compilation Task                               |  |  |  |  |  |  |

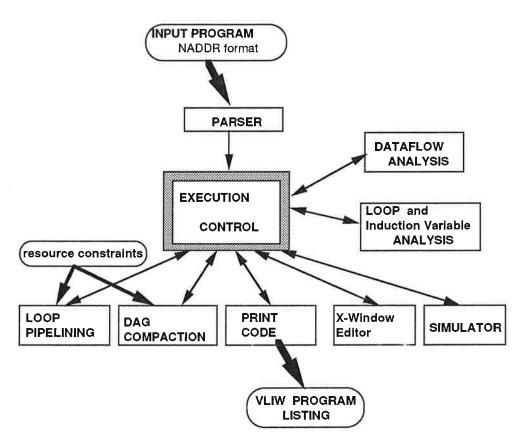

|   | 4.2           | Compilation Framework                                               |  |  |  |  |  |  |

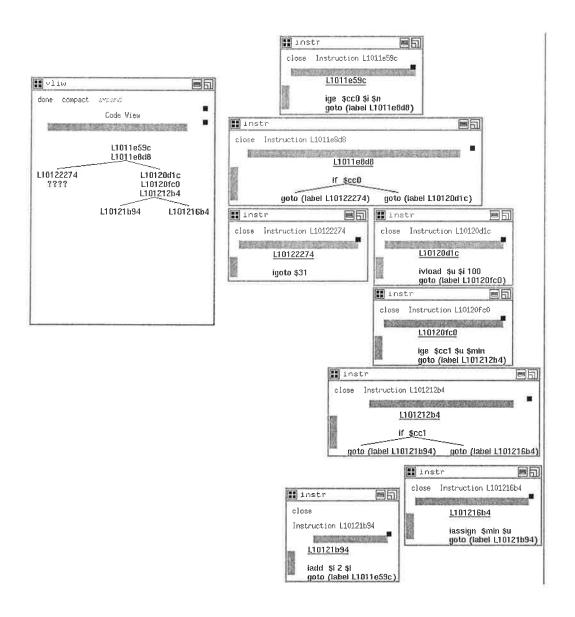

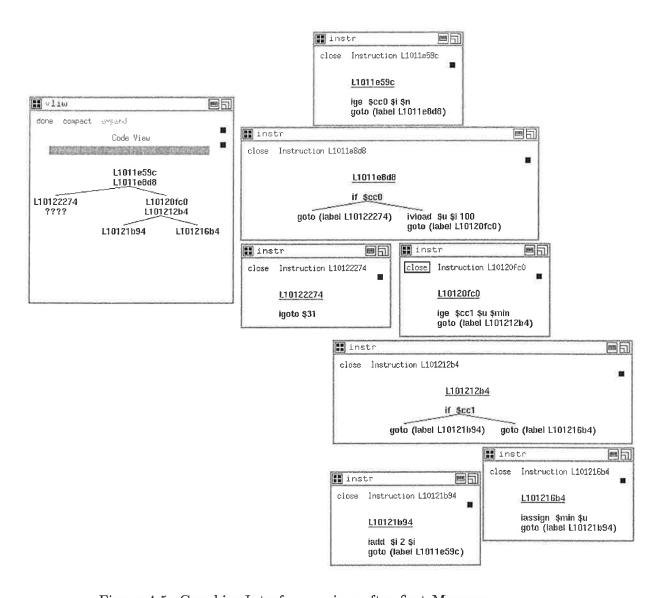

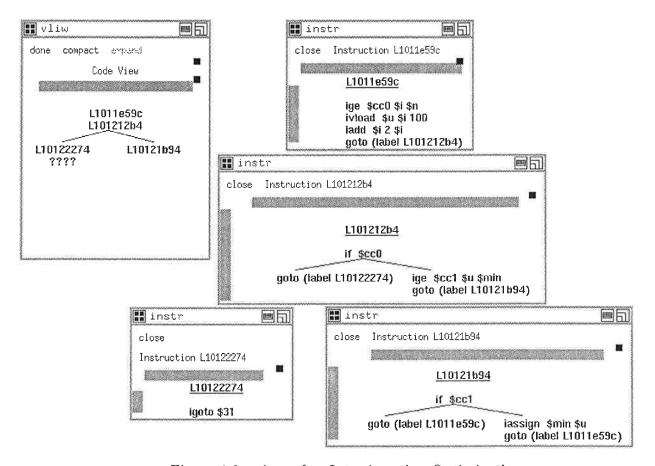

|   | 4.3           | Graphics Interface                                                  |  |  |  |  |  |  |

|   | 4.4           | Code Parallelization Techniques                                     |  |  |  |  |  |  |

|   | 4.5           | Data Structures                                                     |  |  |  |  |  |  |

CONTENTS vi

|              | 4.6<br>4.7                                   | Compilation Effectiveness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 70<br>72 |  |  |  |  |  |  |  |

|--------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

| _            |                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 74       |  |  |  |  |  |  |  |

| 5            |                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |

|              | 5.1                                          | Implementation Optimization Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74       |  |  |  |  |  |  |  |

|              | 5.2                                          | Register Files Allocation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 76       |  |  |  |  |  |  |  |

|              |                                              | 5.2.1 Graph Coloring Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78       |  |  |  |  |  |  |  |

|              |                                              | 5.2.2 Performance of ADJUST-GRAPH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 86       |  |  |  |  |  |  |  |

|              |                                              | 5.2.3 Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 90       |  |  |  |  |  |  |  |

| 6            | Memory Organization for Concurrent Access 92 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |

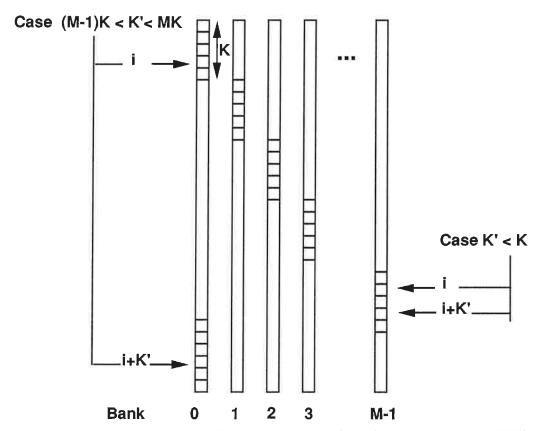

|              | 6.1                                          | Parallel Memory Access Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 92       |  |  |  |  |  |  |  |

|              | 6.2                                          | Bank Allocation by Graph Coloring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 95       |  |  |  |  |  |  |  |

|              | 6.3                                          | Concurrent Access of Array Elements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 96       |  |  |  |  |  |  |  |

|              | 6.4                                          | Implementation and Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 102      |  |  |  |  |  |  |  |

|              | 6.5                                          | Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 105      |  |  |  |  |  |  |  |

|              | 6.6                                          | Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 109      |  |  |  |  |  |  |  |

| 7            | Example Applications of ASPD Method 112      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |

|              | 7.1                                          | Synthesis, Validation and Evaluation Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 112      |  |  |  |  |  |  |  |

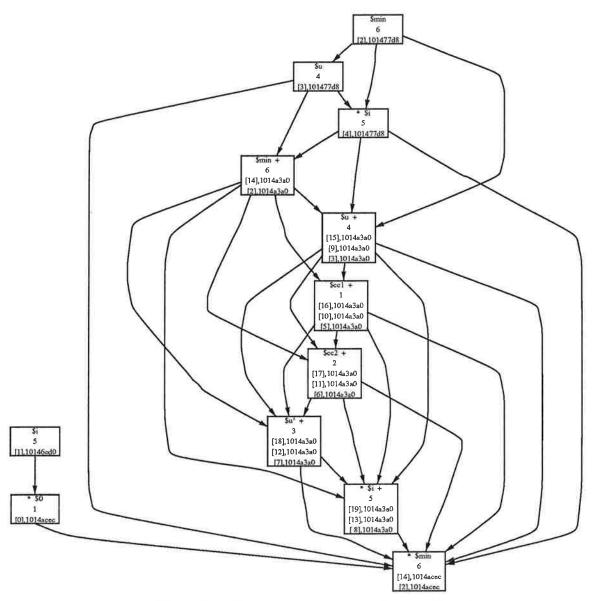

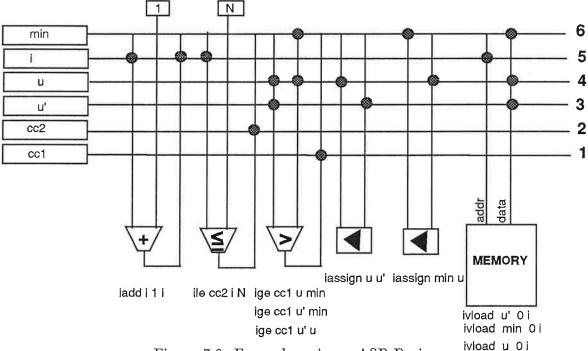

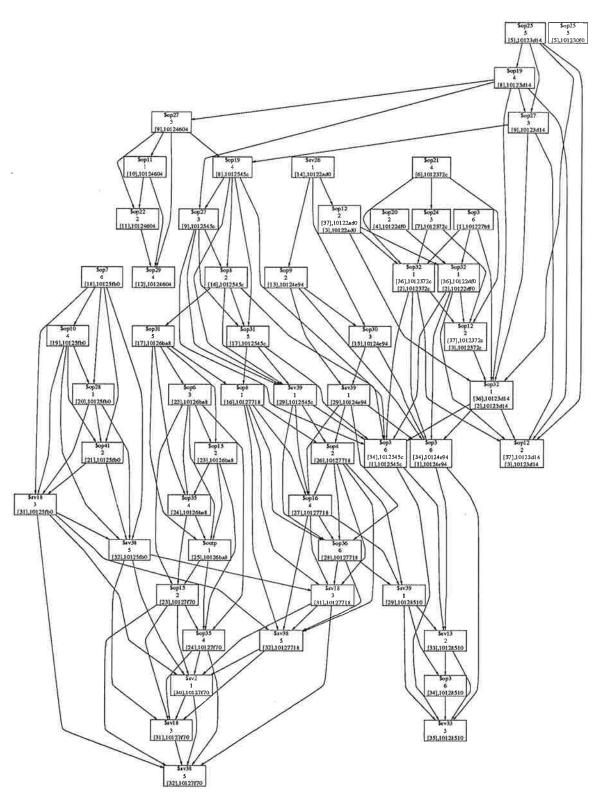

|              | 7.2                                          | Detailed Example: MIN (Livermore Kernel 24)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 113      |  |  |  |  |  |  |  |

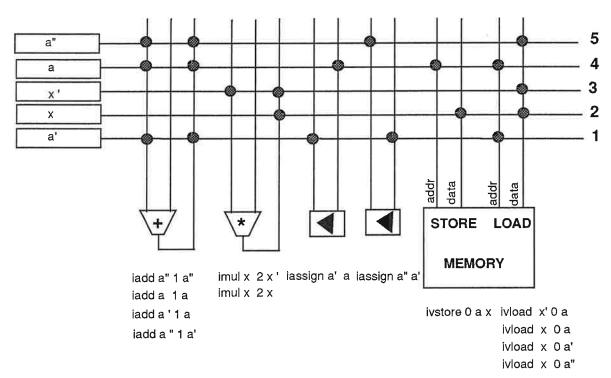

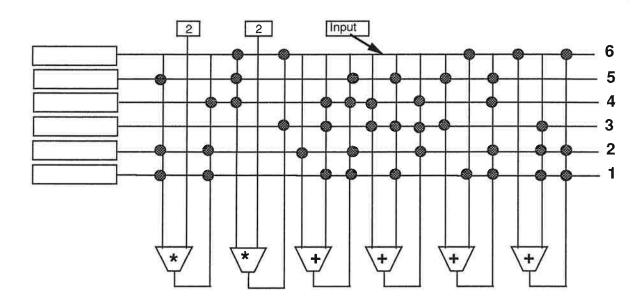

|              | 7.3                                          | Detailed Example: Vector Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 117      |  |  |  |  |  |  |  |

|              | 7.4                                          | Synthesis Benchmark: Elliptic Filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 118      |  |  |  |  |  |  |  |

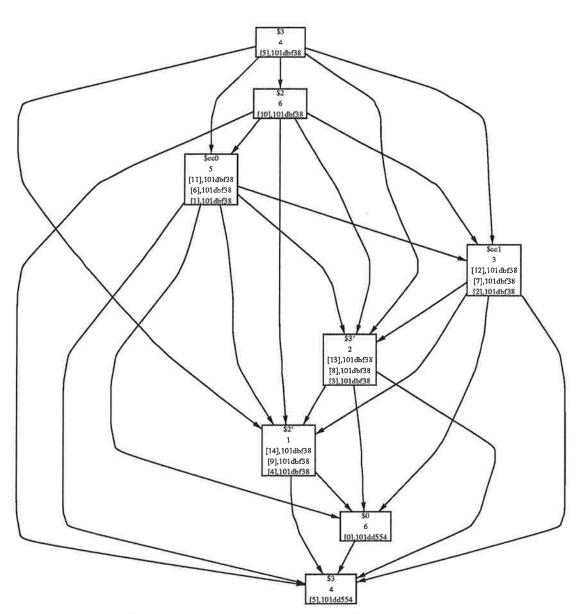

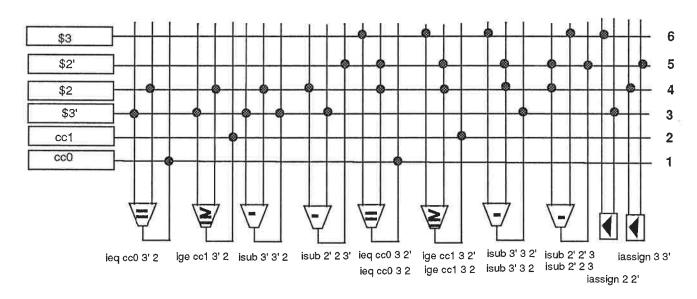

|              | 7.5                                          | Synthesis Benchmark: GCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 123      |  |  |  |  |  |  |  |

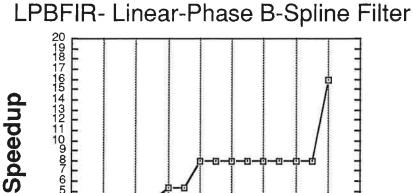

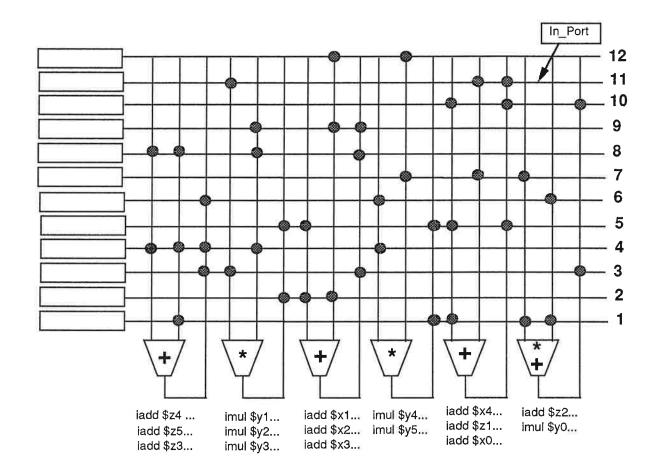

|              | 7.6                                          | Linear-Phase B-Spline Filter Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127      |  |  |  |  |  |  |  |

|              | 7.7                                          | White Dwarf FEM Solver Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 127      |  |  |  |  |  |  |  |

|              | 7.8                                          | RISC Instruction Set Processor Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 135      |  |  |  |  |  |  |  |

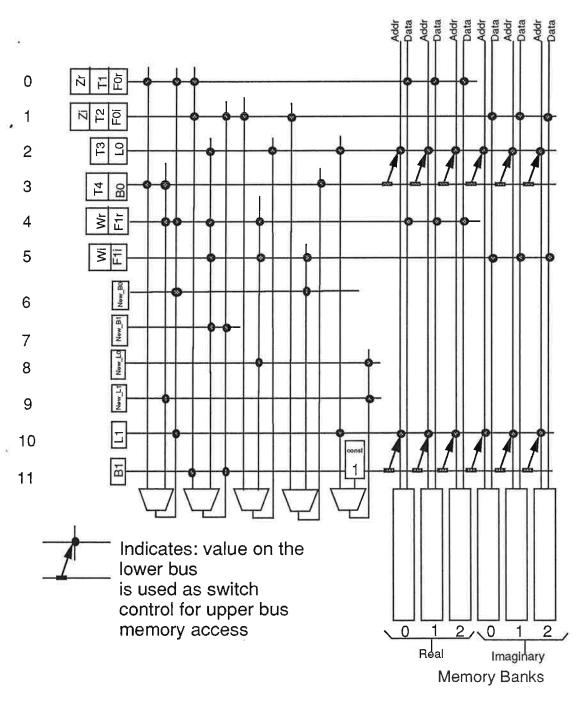

|              | 7.9                                          | FFT Processor Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138      |  |  |  |  |  |  |  |

| 8            | Summary, Conclusions and Extensions 142      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |  |  |  |  |  |  |  |

| 0            | 8.1                                          | Thesis Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |  |  |  |  |  |  |  |

|              | 8.2                                          | Key Contributions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |  |  |  |  |  |  |  |

|              | 8.3                                          | Future Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |  |  |  |  |  |  |  |

| $\mathbf{A}$ | יתית                                         | M Program Source Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 147      |  |  |  |  |  |  |  |

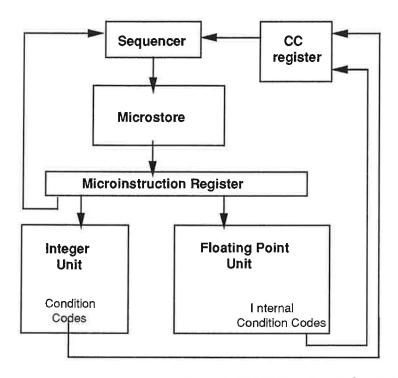

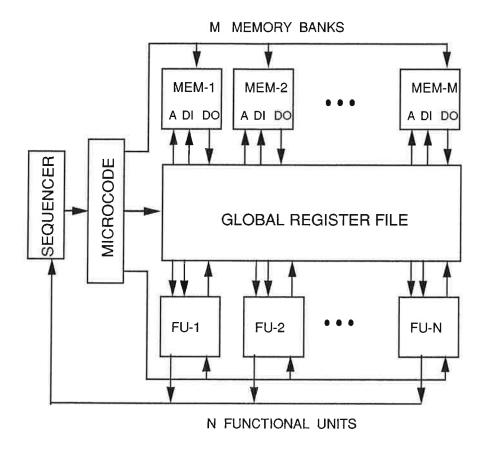

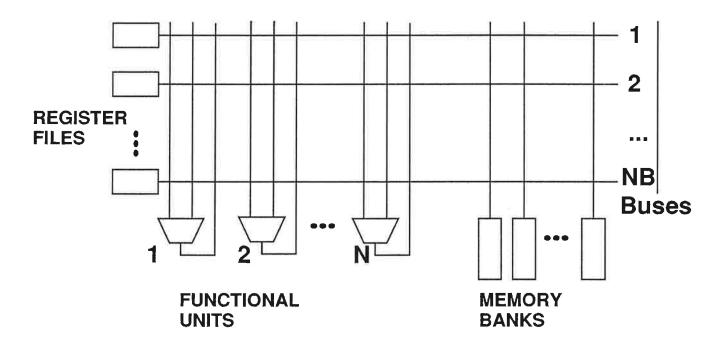

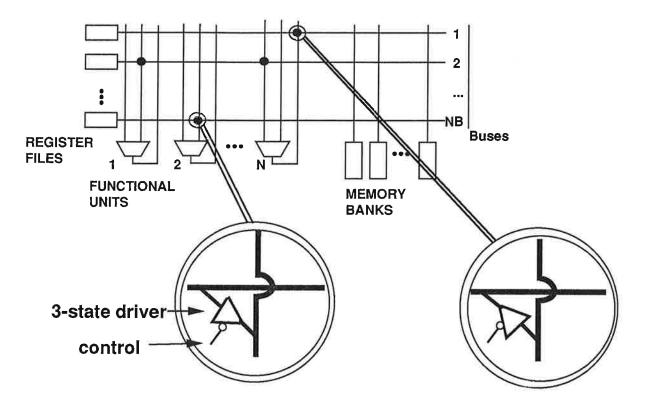

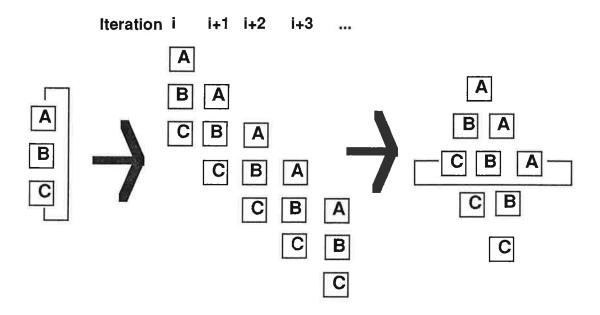

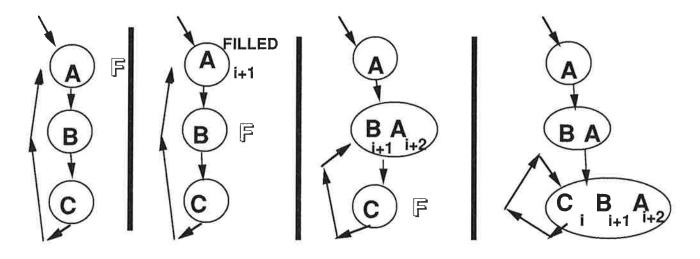

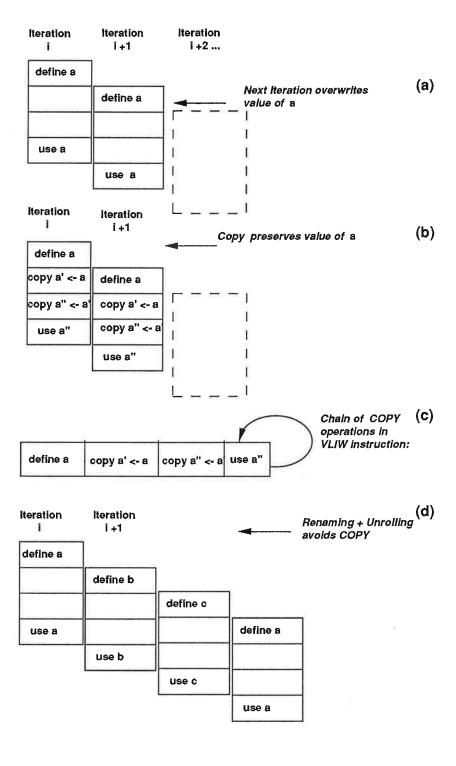

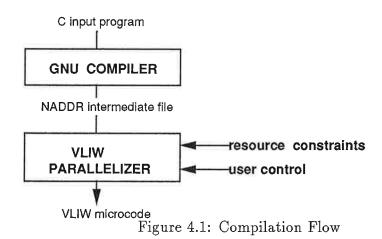

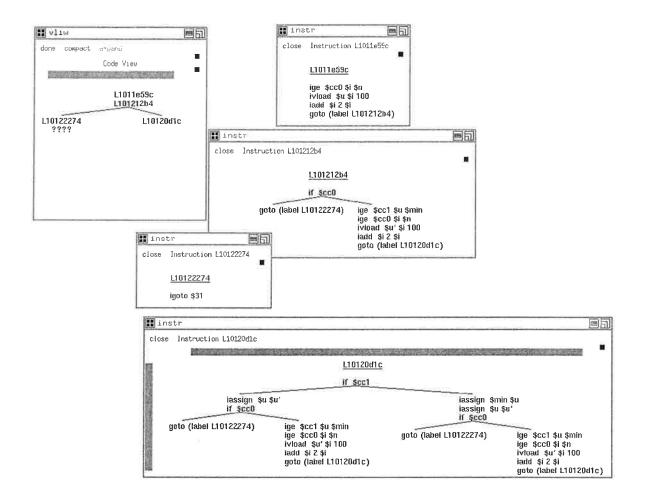

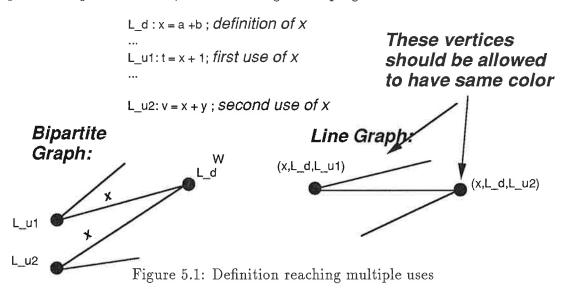

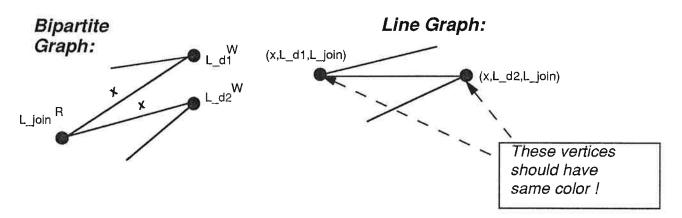

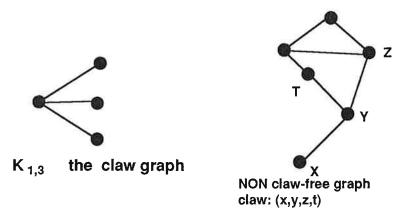

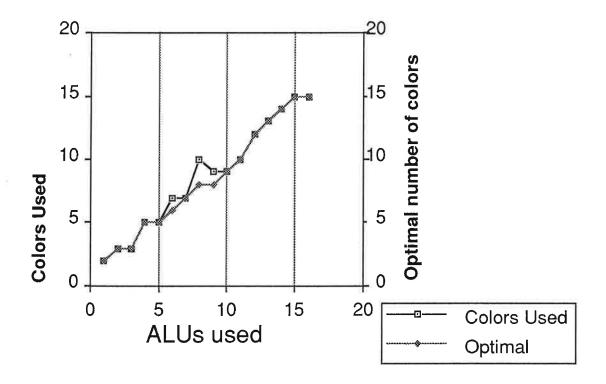

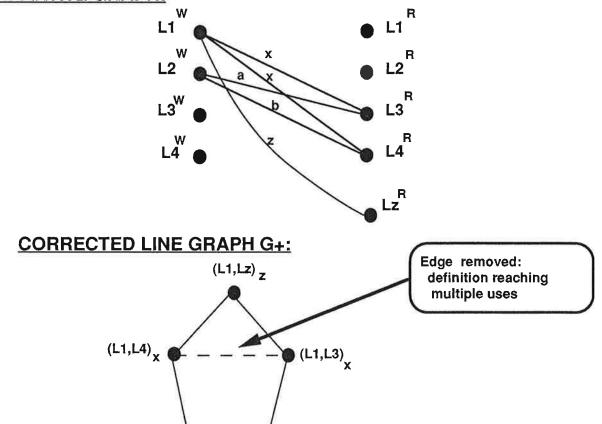

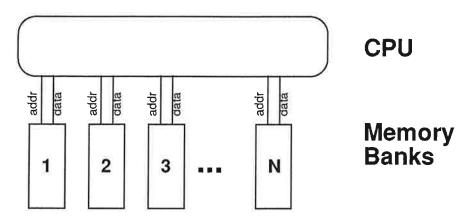

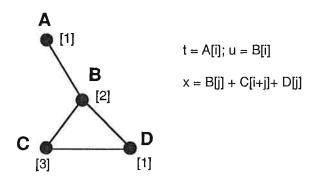

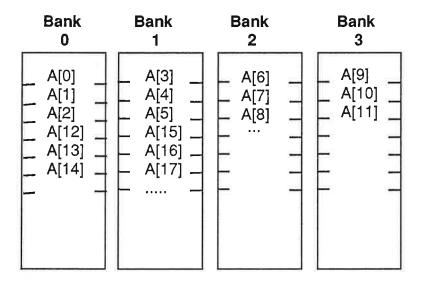

| <b>13.</b>   |                                              | BackSubstitution Routine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |  |  |  |  |  |  |  |