### SEVENTH FRAMEWORK PROGRAMME Research Infrastructures

### INFRA-2011-2.3.5 – Second Implementation Phase of the European High Performance Computing (HPC) service PRACE

#### **PRACE-2IP**

## **PRACE Second Implementation Project**

**Grant Agreement Number: RI-283493**

# D12.2 Exploration of Scalable Numerical Algorithms

#### **Final**

Version: 1.0

Author(s): Cevdet Aykanat, Ata Turk (Bilkent University)

Date: 27.08.2012

## **Project and Deliverable Information Sheet**

| PRACE Project | Project Ref. №: RI-283493                                                                                              |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|               | Project Title: PRACE Second Implementation Project                                                                     |  |  |  |  |

|               | Project Web Site: http://www.prace-project.eu                                                                          |  |  |  |  |

|               | Deliverable ID: <d12.2></d12.2>                                                                                        |  |  |  |  |

|               | Deliverable Nature: < Report>                                                                                          |  |  |  |  |

|               | Deliverable Level: PU *  Contractual Date of Delivery: 31 / August / 2012  Actual Date of Delivery: 31 / August / 2012 |  |  |  |  |

|               |                                                                                                                        |  |  |  |  |

|               |                                                                                                                        |  |  |  |  |

|               |                                                                                                                        |  |  |  |  |

|               | EC Project Officer: Leonardo Flores Añover                                                                             |  |  |  |  |

<sup>\* -</sup> The dissemination level are indicated as follows: **PU** – Public, **PP** – Restricted to other participants (including the Commission Services), **RE** – Restricted to a group specified by the consortium (including the Commission Services). **CO** – Confidential, only for members of the consortium (including the Commission Services).

#### **Document Control Sheet**

|          | Title: Exploration of Sca   | Title: Exploration of Scalable Numerical Algorithms |  |  |  |  |

|----------|-----------------------------|-----------------------------------------------------|--|--|--|--|

| Document | ID:D12.2                    |                                                     |  |  |  |  |

|          | Version:<1.0> Status: Final |                                                     |  |  |  |  |

|          | Available at:               |                                                     |  |  |  |  |

#### **Document Status Sheet**

| Version | Date       | Status        | Comments     |

|---------|------------|---------------|--------------|

| 0.1     | 25/07/2012 | Draft         | First draft  |

| 0.2     | 24/08/2012 | Draft         | Second Draft |

| 1.0     | 27/08/2012 | Final version |              |

#### **Document Keywords**

| <b>Keywords:</b> | PRACE, HPC, Research Infrastructure |

|------------------|-------------------------------------|

|                  |                                     |

#### Disclaimer

This deliverable has been prepared by the responsible Work Package of the Project in accordance with the Consortium Agreement and the Grant Agreement n°RI-283493. It solely reflects the opinion of the parties to such agreements on a collective basis in the context of the Project and to the extent foreseen in such agreements. Please note that even though all participants to the Project are members of PRACE AISBL, this deliverable has not been approved by the Council of PRACE AISBL and therefore does not emanate from it nor should it be considered to reflect PRACE AISBL's individual opinion.

#### **Copyright notices**

© 2012 PRACE Consortium Partners. All rights reserved. This document is a project document of the PRACE project. All contents are reserved by default and may not be disclosed to third parties without the written consent of the PRACE partners, except as mandated by the European Commission contract RI-283493 for reviewing and dissemination purposes.

All trademarks and other rights on third party products mentioned in this document are acknowledged as own by the respective holders.

### **Table of Contents**

| Pr( | oject and Deliverable Information Sheet                                                                                                         | i  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Do  | cument Control Sheet                                                                                                                            | i  |

| Do  | cument Status Sheet                                                                                                                             | i  |

| Do  | cument Keywords                                                                                                                                 | ii |

|     | ble of Contents                                                                                                                                 |    |

|     | st of Figures                                                                                                                                   |    |

|     | st of Tables                                                                                                                                    |    |

|     |                                                                                                                                                 |    |

|     | ferences and Applicable Documents                                                                                                               |    |

|     | st of Acronyms and Abbreviations                                                                                                                |    |

| Ex  | ecutive Summary                                                                                                                                 | 1  |

| 1   | Introduction                                                                                                                                    | 2  |

| 2   | Task Organization                                                                                                                               | 3  |

| 3   | Task 12.2 Key Research Topics and Project Overviews                                                                                             | 5  |

|     | 3.1 Reducing Synchronization Overhead in Iterative Solvers                                                                                      |    |

|     | 3.2 Enhancing Parallel Hybrid Sparse Solvers for Scalability                                                                                    | 5  |

|     | 3.3 Topology-Aware Mapping                                                                                                                      | 6  |

|     | 3.4 Enabling Hybridization in Heterogeneous Architectures                                                                                       | 6  |

|     | 3.5 Application Scalability                                                                                                                     | 7  |

| 4   | Detailed Project Descriptions                                                                                                                   | 8  |

|     | 4.1 Asynchronous Algorithms for Large Sparse Linear Systems                                                                                     | 8  |

|     | 4.2 Designing and Implementing a Single-Phase Row-Column-Parallel Sparse Matrix Vector Multiplication Algorithm based on 2D Matrix Partitioning | 9  |

|     | 4.3 Implementation and Performance Evaluation of the CA-CG Algorithm on Massively Para HPC-Clusters                                             |    |

|     | 4.4 Permuting Sparse Square Matrices into Block Diagonal Form with Overlap for Parallel H Sparse Solvers                                        |    |

|     | 4.5 A Parallel Sparse Hybrid Solver and Its Relation to Graphs and Hypergraphs                                                                  | 14 |

|     | 4.6 Topology-Aware Subdomain-to-Processor Assignment                                                                                            |    |

|     | 4.7 Multicore Parallelization of Block Cyclic Reduction Algorithm                                                                               |    |

|     | 4.8 Enabling FFTE library and FFTW3 Threading in the Quantum Espresso                                                                           |    |

|     | 4.9 A Hybrid Hermitian General Eigenvalue Solver                                                                                                |    |

|     | 4.10 A Generic Library for Stencil Computations                                                                                                 |    |

|     | 4.11 Design and Implementation of New Hybrid Algorithm and Solver for Large Sparse Linear Systems                                               |    |

|     | 4.12 Scalable and Improved SuperLU on GPU for Heterogeneous Systems                                                                             |    |

|     | 4.13 Optimization of SHAKE and RATTLE Algorithms                                                                                                |    |

|     | 4.14 Optimization of FHP Algorithms                                                                                                             |    |

|     | 4.15 FETI Coarse Problem Parallelization Strategies and Their Comparison                                                                        |    |

|     | 4.16 Computer Modeling and Simulations In Strongly Heterogeneous Nonlinear Media                                                                | 34 |

|     | 4.17 Cfd-Investigations For Assessing Aneurysm Rupture Risk For Individual Patient Using Co                                                     |    |

|     | Visual Diagnostics                                                                                                                              | 36 |

| 5   | Summary and Conclusions                                                                                                                         | 38 |

## **List of Figures**

| Figure 1: Projects in Task 12.2                                                                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2: An example project wiki page.                                                                                                                                       |    |

| Figure 3: Thematic overview of projects in Task 12.2                                                                                                                          | 4  |

| Figure 4: BDO form of a matrix and its oVS representation                                                                                                                     | 13 |

| Figure 5: Speedup curves for the solution of four different linear systems on a 64-processor syste                                                                            |    |

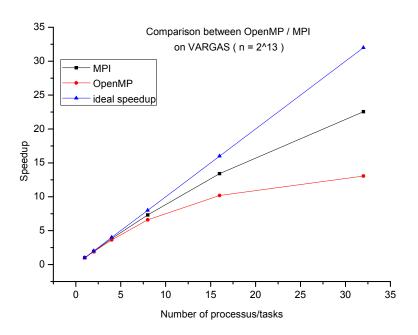

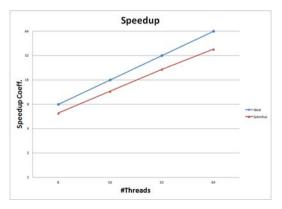

| Figure 6: Speedup curves of the two parallel algorithms on a single SMP node of Vargas                                                                                        |    |

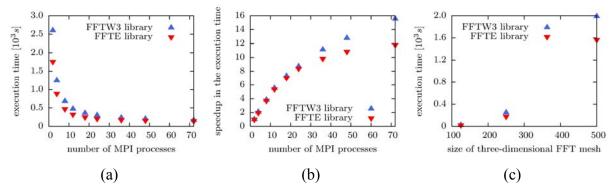

| Figure 7: Performance of QE FFTE extension compared with the QE FFTW3 implementation                                                                                          |    |

| Execution times of QE FFTW3/FFTE codes for different number of MPI processes; (b) Speedup                                                                                     |    |

| execution time of QE FFTW3/FFTE codes as functions of a number of MPI processes; (                                                                                            |    |

| FFTW3/FFTE execution times as functions of 3D FFT mesh size.                                                                                                                  | 21 |

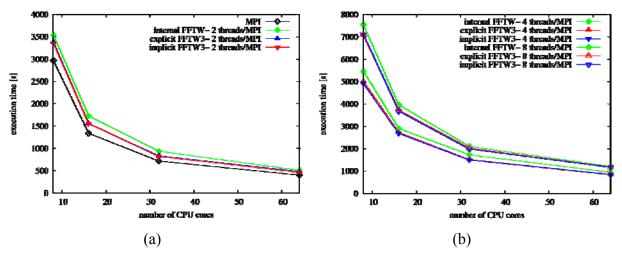

| Figure 8: Performance of the pure MPI, implicit and explicit QE FFTW3 hybrid extensions, as                                                                                   |    |

| FFTW hybrid code for various numbers of CPU cores used: (a)Execution times when pure MPI                                                                                      | -  |

| threads per MPI process hybrid versions are used; (b) Execution times when 4 and 8 threads per                                                                                |    |

| process hybrid versions are used.                                                                                                                                             |    |

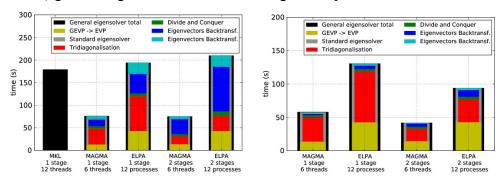

| Figure 9: Time to solution of double complex general eigensolver with matrix size 8000. On the                                                                                |    |

| the whole eigenspace is computed, on the right only 10% of the eigenvectors.                                                                                                  |    |

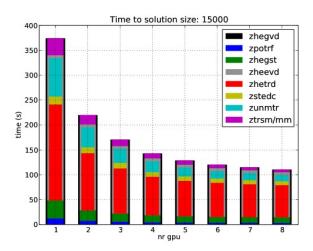

| Figure 10: Time to solution for different number of GPUs of double complex general eigensolve                                                                                 |    |

| matrix size 15000 and whole eigenspace.                                                                                                                                       |    |

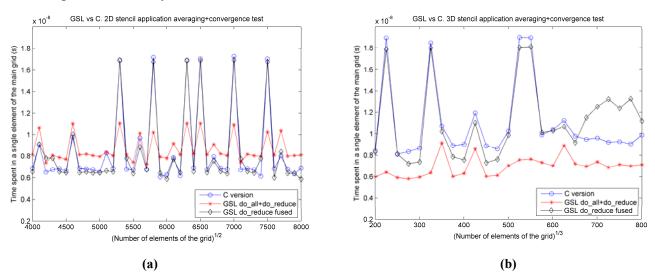

| Figure 11: Comparison of GSCL and C99 code on (a) 2D and (b) 3D grids. The fused v                                                                                            |    |

| (GSL_do_reduce fussed) is algorithmically equivalent to the C version, while the                                                                                              |    |

| (GSL_do_feduce_fussed) is algorithmically equivalent to the C version, while the (GSL do+all+do reduce) does an additional scan of the memmory since the loops are not fused. |    |

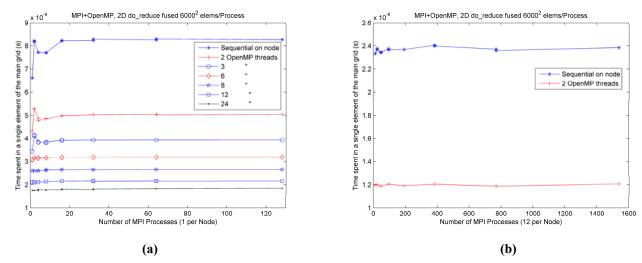

| Figure 12: Running GSCL code on a Cray XT5 machine. Each node has 24 cores divided in                                                                                         |    |

| sockets. (a) One MPI process per node is used and then a varying number of OpenMP threa                                                                                       |    |

| process are used. (b) The node is half filled with MPI processes and none or 2 OpenMP threa                                                                                   |    |

|                                                                                                                                                                               |    |

| utilized.                                                                                                                                                                     | 25 |

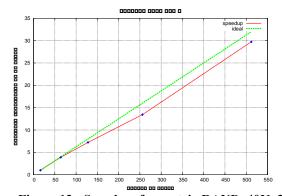

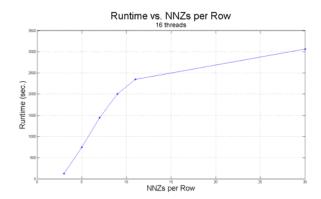

| Figure 13: Speed up for matrix RAND_40K_3.                                                                                                                                    |    |

| Figure 14: Average wall clock time as a function of various sparsity levels for randomly located                                                                              |    |

| matrices.                                                                                                                                                                     |    |

| Figure 15: Speed up for matrix RAND_40K_3.                                                                                                                                    | 28 |

| Figure 16: Average wall clock time as a function of various sparsity levels for randomly located                                                                              |    |

| matrices.                                                                                                                                                                     | 28 |

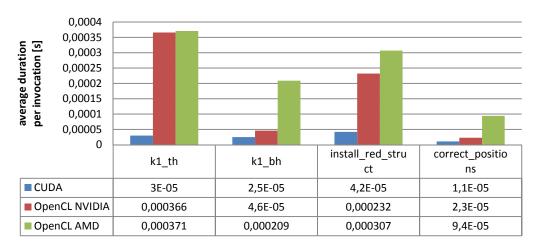

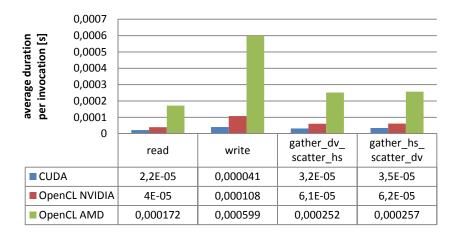

| Figure 17: CUDA vs OpenCL kernels for DL_POLY constraints shake component                                                                                                     |    |

| Figure 18: CUDA vs OpenCL I/O and communication for DL_POLY constraints shake compone                                                                                         |    |

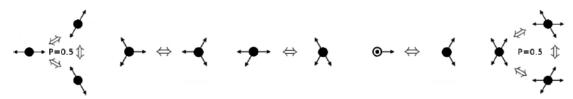

| Figure 19: FHP III collision rules.                                                                                                                                           |    |

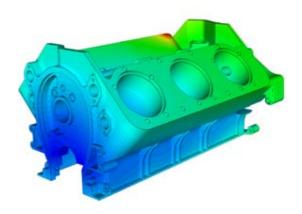

| Figure 20: Car engine block – total displacement distribution.                                                                                                                |    |

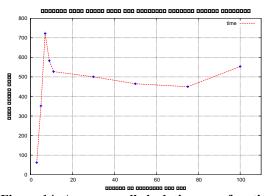

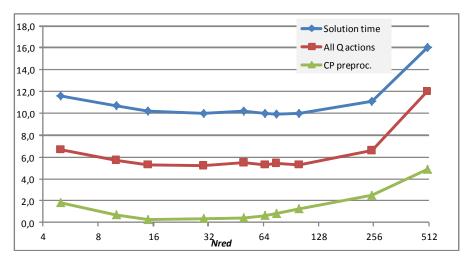

| Figure 21: Sensitivity of the solution strategy (2) to Nred                                                                                                                   |    |

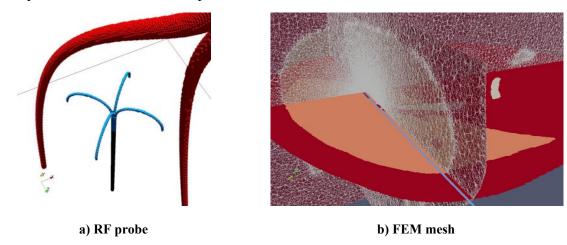

| Figure 22: Inserted RF Probe and the corresponding FEM mesh                                                                                                                   | 35 |

|                                                                                                                                                                               |    |

| List of Tables                                                                                                                                                                |    |

|                                                                                                                                                                               | 2  |

| Table 1: Overview of efforts per partner                                                                                                                                      |    |

| Table 2: HECToR MPI results summary                                                                                                                                           |    |

| Table 3: HECToR SHMEM result summary                                                                                                                                          |    |

| Table 4: Speedup values obtained on a 16-processor system.                                                                                                                    |    |

| Table 5: Performance comparison of the baseline and oGPVS algorithms in terms of total overla                                                                                 |    |

| and load imbalance for different number of processors (K)                                                                                                                     |    |

| Table 6: Performance improvement of HP over GP in terms of solution times on a 64-pro                                                                                         |    |

| system averaged over different problem categories.                                                                                                                            | 15 |

| Table 7: Average task degrees for the task interaction graphs (RN = row-net, CN = column-net).                                                                                | 16 |

| Table 8: Maximum hops for each topology                                                                                                                                       | 17 |

| Table 9: Percentage improvement (%) for tested matrices                                                                                                                       | 17 |

| Table 10: Wall clock time for randomly located sparse matrices as sparsity level decreases with 64 |

|----------------------------------------------------------------------------------------------------|

| core (8x8)                                                                                         |

| Table 11: Wall clock time using SuperLU_MT for randomly located sparse matrices as sparsity level  |

| decreases with 16 cores                                                                            |

| Table 12: Execution times for the RATTLE algorithm integrated with the DL_POLY code (in            |

| seconds)                                                                                           |

| Table 13: Computational, cost and power efficiency of FHP implementations on different processing  |

| unit types                                                                                         |

| Table 14: Results of the best strategy (2) for the problem size 98,214,55 and the number of cores  |

| (subdomains) 5,012                                                                                 |

| Table 15: Comparison on two meshes                                                                 |

| Table 16: The number of the nodes and the different type of elements use in the discretizations 36 |

| Table 17: CPU time for solving the Navier-Stokes equation on the IBM Blue Gene/P computer in       |

| Sofia 37                                                                                           |

#### **References and Applicable Documents**

- [1] U. V. Catalyurek and C. Aykanat, "Hypergraph-Partitioning-Based Decomposition for Parallel Sparse-Matrix Vector Multiplication", IEEE Transactions on Parallel and Distributed Systems, vol. 10, no. 7, pp. 673-693, 1999

- [2] T. A. Davis, "University of Florida sparse matrix collection", NA Digest, 1997.

- [3] U. V. Çatalyürek, C. Aykanat, and B. Uçar, "On two-dimensional sparse matrix partitioning: Models, methods, and a recipe", SIAM Journal on Scientific Computing, Vol. 32, pp. 656--683, 2010.

- [4] L. N. Trefethen and D. Bau, Numerical Linear Algebra, SIAM, 1997.

- [5] M. Benzi, "Preconditioning Techniques for Large Linear Systems: A Survey", Journal of Computational Physics, 182 (2002), pp. 418 477.

- [6] R. Barret, J. Demmel, J. Dongarra, "Templates for the Solution of Linear Systems: Building Blocks for Iterative Methods", SIAM, 1994.

- [7] S. Balay, J. Brown, K. Buschelman, "PETSc Users Manual", ANL-95/11 Revision 3.3, 2012.

- [8] M. A. Heroux, R. A. Bartlett, V. E. Howle, "An Overview of the Trilinos Project", ACM Transaction on Mathematical Software, vol. 31, pp. 397-423, 2005.

- [9] TOP500 PROJECT, www.top500.org

- [10] M. Hoemmen, "Communication Avoiding Krylov Subspace Methods", Ph.D. thesis, 2010.

- [11] J. Demmel, M. Hoemmen, M. Mohiyuddin and A. Yelick, "Avoiding Communication In Computing Krylov Subspace", Technical Report No. UCB/EECS-2007-123, University of California, Berkeley, 2007.

- [12] IBM PLX, www.hpc.cineca.it/hardware/ibm-plx

- [13] IBM BG/Q FERMI, www.hpc.cineca.it/hardware/ibm-bgq-fermi

- [14] G. A. A. Kahou, E. Kamgnia, and B. Philippe, "Parallel Implementation of an Explicit Formulation of the Multiplicative Schwarz Preconditioner", in CdROM Proceedings of IMACS05, 2005.

- [15] M. Naumov, M. Manguoglu, and A. H. Sameh, "A Tearing-Based Hybrid Parallel Sparse Linear System Solver", Journal of Computational and Applied Mathematics, 234 (2010), pp. 3025 3038.

- [16] G. A. A. Kahou, E. Kamgnia, and B. Philippe, "An Explicit Formulation Of The Multiplicative Schwarz Preconditioner", Applied Numerical Mathematics, 57 (2007), pp. 1197 1213.

- [17] G. A. A. Kahou, L. Grigori, and M. Sosonkına, "A Partitioning Algorithm for Block-Diagonal Matrices With Overlap", Parallel Computing, 34 (2008), pp. 332 344.

- [18] M. Manguoglu, "A Domain-Decomposing Parallel Sparse Linear System Solver", Journal of Computational and Applied Mathematics, 236(3), pp.319-325, 2011.

- [19] T. A. Davis, "University Of Florida Sparse Matrix Collection," NA Digest, 1997.

- [20] A. Bhatele, "Automating Topology Aware Mapping for Supercomputers", PhD Thesis,

- [21] The TopoManager API: http://charm.cs.uiuc.edu/research/topology

- [22] R.W. Hockney, "A Fast Direct Solution Of Poisson's Equation Using Fourier Analysis", Journal of Asso. Comput. Mach, v 8, 1965.

- [23] B.L. Buzbee, G.H Golub, C.W. Nielson, "On Direct Methods for Solving Poisson's Equation", SIAM J. Numerical Analysis, v 7, 1970.

- [24] P. Giannozzi, S. Baroni, N. Bonini, et al., "Quantum Espresso: A Modular and Open-Source Software Project for Quantum Simulations Of Materials", J. Phys.: Condens. Matter 21, 2009

- [25] FFTE: A Fast Fourier Transform Package official web site: http://www.ffte.jp/

- [26] M. Frigo, S. G. Johnson, "The Design and Implementation of FFTW3", Proceedings of the IEEE 93 (2005) 216

- [27] A. Sunderland, S. Pickles, M. Nikolic, et al., "An Analysis of FFT Performance in PRACE Application Codes", PRACE-1IP T7.5 Whitepaper (2012)

- [28] Developer's Manual for Quantum ESPRESSO (v. 5.0) http://www.quantum-espresso.org/wp-content/uploads/Doc/developer\_man.pdf

- [29] QE-SCL, Quantum Espresso extended with FFTE library and FFTW3 threading support http://www.scl.rs/QE-SCL/

- [30] Quantum Espresso official web site http://www.quantum-espresso.org/

- [31] NIIFI SC, http://www.niif.hu/en/niif\_institute/supercomputing\_service/

- [32] F. Spiga, Implementing and Testing Mixed Parallel Programming Model into Quantum ESPRESSO, Science and Supercomputing in Europe research highlights 2009, ISBN 978-88-86037-23-5, pp. 6

- [33] P. Kent, "Computational Challenges Of Large-Scale, Long-Time, First Principles Molecular Dynamics", Journal of Physics: Conference Series, vol. 125, no. 1, p. 012058, 2008. [Online]. Available: http://stacks.iop.org/1742-6596/125/i=1/a=012058

- [34] T. Auckenthaler, V. Blum, H. J. Bungartz, T. Huckle, R. Johanni, L. Krämer, B. Lang, H. Lederer, and P. R. Willems, "Parallel Solution Of Partial Symmetric Eigenvalue Problems From Electronic Structure Calculations", Parallel Comput., vol. 37, no. 12, pp. 783–794, Dec. 2011. [Online]. Available: http://dx.doi.org/10.1016/j.parco.2011.05.002

- [35] A. Haidar, H. Ltaief, and J. Dongarra, "Parallel Reduction To Condensed Forms For Symmetric Eigenvalue Problems Using Aggregated Fine-Grained And Memory-Aware Kernels", in SC11: International Conference for High Performance Computing, Networking, Storage and Analysis, Seattle, WA, USA, November 12-18 2011.

- [36] http://user.cscs.ch/hardware/castor\_ibm\_idataplex/index.html

- [37] X. S. Li, J. W. Demmel, J. R. Gilbert, L. Grigori, M. Shao, and I. Yamazaki, "SuperLU Users' Guide", Tech. Report UCB, Computer Science Division, University of California, Berkeley, CA, 1999, update: 2011.

- [38] P. R. Amestoy, I. S. Duff, J.-Y. L'Excellent, and J. Koster, "A Fully Asynchronous Multifrontal Solver Using Distributed Dynamic Scheduling", SIAM J. Matrix Anal. Appl., 23 (2001), pp. 15–41.

- [39] O. Schenk and K. Gartner, "Solving Unsymmetric Sparse Systems of Linear Equations with Pardiso", Future Generation Computer Systems, 20 (2004), pp. 475-487.

- [40] O. Schenk and K. Gartner, "On Fast Factorization Pivoting Methods For Sparse Symmetric Indefinite Systems", Electronic Transactions on Numerical Analysis, 23 (2006), pp. 158 179.

- [41] A. Duran and B.D. Saunders, Gen\_SuperLU package (version 1.0, August 2002).

- [42] A. Duran, B. D. Saunders and Z. Wan, "Hybrid Algorithms For Rank Of Sparse Matrices", Proceedings of the SIAM International Conference on Applied Linear Algebra (SIAM-LA), VA, July 15-19, 2003.

- [43] L. Li, L. Li and Y. Guangwen, "A Highly Efficient Gpu-Cpu Hybrid Parallel Implementation Of Sparse Lu Factorization", Chinese J. of Electronics, 21:7-12, 2012.

- [44] J.W. Demmel, J.R. Gilbert, and X.S. Li, "An Asynchronous Parallel Supernodal Algorithm For Sparse Gaussian Elimination", SIAM J. Matrix Analysis and Applications, 20(4):915-952, 1999.

- [45] X.S. Li, "Evaluation Of Sparse Lu Factorization And Triangular Solution On Multicore Platforms", VECPAR 2008, Springer.

- [46] X. S. Li and J. W. Demmel, "Superlu-Dist: A Scalable Distributed-Memory Sparse Direct Solver For Unsymmetric Linear Systems", ACM Trans. Math. Softw., 29 (2003), pp. 110–140.

- [47] L. Grigori, J.W. Demmel, and X.S. Li. "Parallel Symbolic Factorization For Sparse Lu With Static Pivoting", SIAM J. Scientific Computing, 29(3):1289-1314, 2007.

- [48] M.S. Celebi, A. Duran, M.Tuncel, B. Akaydin, "Scalability of SuperLU Solvers for Large Scale Complex Reservoir Simulations", SPE and SIAM Conference on Mathematical Methods in Fluid Dynamics and Simulation of Giant Oil and Gas Reservoirs, Istanbul, Turkey, September 3-5, 2012.

- [49] I.S. Duff and J. Koster, "The Design and Use of Algorithms for Permuting Large Entries to the Diagonal of Sparse Matrices", SIAM J. Matrix Anal. Appl. 20 (4) (1999) 889–901.

- [50] G. Karypis, K. Schloegel, and V. Kumar, "ParMeTiS, version 3.1", http://www-users.cs.umn.edu/~karypis/metis/parmetis/.

- [51] Karypis and V. Kumar, "MeTiS, version 4.0", http://www-users.cs.umn.edu/~karypis/metis/.

- [52] http://www.uybhm.itu.edu.tr/eng/inner/duyurular.html#karadeniz

- [53] nPartition Administrator's Guide, HP part number: 5991-1247B, 1st Edition, February 2007, Hewlett-Packard Development Company.

- [54] DL POLY Molecular Simulation Package home page:

- http://www.stfc.ac.uk/CSE/randd/ccg/software/DL POLY/25526.aspx

- [55] The DL POLY 4 User Manual:

- ftp://ftp.dl.ac.uk/ccp5/DL POLY/DL POLY 4.0/DOCUMENTS/USRMAN4.01.pdf

- The DL POLY test data: ftp://ftp.dl.ac.uk/ccp5/DL POLY/DL POLY 4.0/DATA/

- GeForce 400 series: http://en.wikipedia.org/wiki/GeForce 400 Series

- [58] AMD Radeon HD 6900: http://www.amd.com/us/products/notebook/graphics/amd-radeon-6000m/amdradeon-6900m/Pages/amd-radeon-6900m.aspx

- PRACE-1IP Public deliverable - HPC Programming Techniques: http://www.praceri.eu/IMG/pdf/d7.5 lip.pdf

- [60] U. Frish, et al., "Lattice-Gas Automata for the Navier-Stokes Equation", Phys. Rev. Lett. Vol 56: 1505-1508 (1986).

- [61] O. Bandman, "Using Cellular Automata for Porous Media Simulation", The Journal of Supercomputing 57(2): 121-131 (2011)

- [62] Y. Arai, et al., "A Latice Gas Cellular Automata Simulator on the Cell Broadband Engine", Parallel Computing: Architectures, Algorithms and Applications Vol. 38: 459-466 (2007).

- [63] N. Kosturski, S. Margenov, and Y. Vutov, "Balancing the Communications and Computations in Parallel FEM Simulations on Unstructured Grids", Parallel Processing and Applied Mathematics, LNCS, vol. 7204, pp 211-220, 2012

#### **List of Acronyms and Abbreviations**

**AMD Advanced Micro Devices AMG** Algebraic MultiGrid API Application Programming Interface **BDO** Block-Diagonal with Overlap **BiCGStab** Bi-Conjugate Gradient Stabilized **BLAS** Basic Linear Algebra Subprograms **BSC** Barcelona Supercomputing Center (Spain) CEA Commissariat à l'EnergieAtomique (represented in PRACE by GENCI, France) CFD Computational Fluid Dynamics CINECA ConsorzioInteruniversitario, the largest Italian computing centre (Italy) CN Column-Net **CPU** Central Processing Unit CSC Finnish IT Centre for Science (Finland) The Swiss National Supercomputing Centre (represented in PRACE by **CSCS** ETHZ, Switzerland) Compressed Sparse Row (for a sparse matrix) Computer Tomography

CSR

CT

Compute Unified Device Architecture (NVIDIA) CUDA

DEISA Distributed European Infrastructure for Supercomputing

Applications.EU project by leading national HPC centres.

DMA **Direct Memory Access** DNA DeoxyriboNucleic Acid

DRAM Dynamic Random Access memory Digital Subtraction Angiography DSA

EC **European Community**

European Exascale Software Initiative EESI

Edinburg Parallel Computing Centre (represented in PRACE by **EPCC**

EPSRC, United Kingdom)

**ETHZ** Eidgenössische Technische Hochschule Zuerich, ETH Zurich

(Switzerland)

**ESFRI** European Strategy Forum on Research Infrastructures; created

roadmap for pan-European Research Infrastructure.

FEM Finite Element Method FETI Finite Element Tearing and Interconnect

FFT Fast Fourier Transform

FP Floating-Point FPU Floating-Point Unit

FZJ Forschungszentrum Jülich (Germany)

GB Giga (=  $2^{30} \sim 10^9$ ) Bytes (= 8 bits), also GByte Gb/s Giga (=  $10^9$ ) bits per second, also Gbit/s

GB/s Giga (= 10<sup>9</sup>) Bytes (= 8 bits) per second, also GByte/s

GCS Gauss Centre for Supercomputing (Germany)

GÉANT Collaboration between National Research and Education Networks to

build a multi-gigabit pan-European network, managed by DANTE.

GÉANT2 is the follow-up as of 2004.

GENCI Grand Equipement National de CalculIntensif (France)

GFlop/s Giga (= 10<sup>9</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also GF/s

GHz Giga (= 10<sup>9</sup>) Hertz, frequency =10<sup>9</sup> periods or clock cycles per second

GigE Gigabit Ethernet, also GbE GLSL OpenGL Shading Language GNU GNU's not Unix, a free OS

GP Graph Partitioning

GPGPU General Purpose GPU

GPU Graphic Processing Unit

GS Gram-Schmidt

GWU George Washington University, Washington, D.C. (USA)

HDD Hard Disk Drive HE High Efficiency

HECToR High-End Computing Terascale Resource

HMPP Hybrid Multi-core Parallel Programming (CAPS enterprise)

HP Hypergraph Partitioning

HPC High Performance Computing; Computing at a high performance level

at any given time; often used synonym with Supercomputing

HPCC HPC Challenge benchmark, http://icl.cs.utk.edu/hpcc/ HPCS High Productivity Computing System (a DARPA program)

HPL High Performance LINPACK

IBM Formerly known as International Business Machines

IDRIS Institut du Développementet des Ressources en Informatique

Scientifique (represented in PRACE by GENCI, France)

IEEE Institute of Electrical and Electronic Engineers

IESP International Exascale Project IPB Institute of Physics Belgrade

IMB Intel MPI Benchmark

I/O Input/Output

ITU-UHeM Istanbul Technical University – Center of High Performance Computing

JSC Jülich Supercomputing Centre (FZJ, Germany) KB Kilo (=  $2^{10} \sim 10^{3}$ ) Bytes (= 8 bits), also KByte

KTH Kungliga Tekniska Högskolan (represented in PRACE by SNIC.

Sweden)

LBE Lattice Boltzmann Equation

LINPACK Software library for Linear Algebra

LLNL Laurence Livermore National Laboratory, Livermore, California (USA)

LQCD Lattice QCD

LRZ Leibniz Supercomputing Centre (Garching, Germany)

LS Local Store memory (in a Cell processor) MB Mega (=  $2^{20} \sim 10^6$ ) Bytes (= 8 bits), also MByte

MB/s Mega (= 10<sup>6</sup>) Bytes (= 8 bits) per second, also MByte/s

MDT Meta Data Target

MFC Memory Flow Controller

MFlop/s Mega (= 10<sup>6</sup>) Floating point operations (usually in 64-bit, i.e. DP) per

second, also MF/s

MGS Modified Gram-Schmidt

MHz Mega (= 10<sup>6</sup>) Hertz, frequency =10<sup>6</sup> periods or clock cycles per second MIPS Originally Microprocessor without Interlocked Pipeline Stages; a RISC

processor architecture developed by MIPS Technology

MKL Math Kernel Library (Intel)

Mop/s Mega (=  $10^6$ ) operations per second (usually integer or logic operations)

MoU Memorandum of Understanding

Mups Million lattice site updates per second

MPI Message Passing Interface

NCSA The National Centre for Supercomputing Applications (Sofia, Bulgaria)

oGPVS ordered Graph Partitioning by Vertex Separators

OpenCL Open Computing Language

OpenGL Open Graphic Library

Open MP Open Multi-Processing

OS Operating System

OSS Object Storage Server

OST Object Storage Target

oVS ordered Vertex Seperator

PSNC Poznan Supercomputing and Networking Center

PGI Portland Group, Inc.

pNFS Parallel Network File System

POSIX Portable OS Interface for Unix

PPE PowerPC Processor Element (in a Cell processor)

PRACE Partnership for Advanced Computing in Europe; Project Acronym

PSNC Poznan Supercomputing and Networking Centre (Poland)

QE Quantum Espresso

QR — QR method or algorithm: a procedure in linear algebra to compute the

eigenvalues and eigenvectors of a matrix

RAM Random Access Memory

RDMA Remote Data Memory Access

RISC Reduce Instruction Set Computer

RN Row-Net

RNG Random Number Generator

RPM Revolution per Minute SAN Storage Area Network

SARA Stichting Academisch Rekencentrum Amsterdam (Netherlands)

SAS Serial Attached SCSI

SATA Serial Advanced Technology Attachment (bus)

SDK Software Development Kit

SGEMM Single precision General Matrix Multiply, subroutine in the BLAS

SGI Silicon Graphics, Inc.

SHMEM Share Memory access library (Cray)

SIMD Single Instruction Multiple Data

SM Streaming Multiprocessor, also Subnet Manager

SMP Symmetric Multi Processing

SNIC Swedish National Infrastructure for Computing (Sweden)

SP Single Precision, usually 32-bit floating point numbers

SpMxV Sparse Matrix Vector multiplication

SPU Synergistic Processor Unit (in each SPE)

SSD Solid State Disk or Drive SSE Streaming SIMD Extensions

STFC Science and Technology Facilities Council (represented in PRACE by

EPSRC, United Kingdom)

STRATOS PRACE advisory group for STRAtegic TechnOlogieS TB Tera (= 240 ~ 1012) Bytes (= 8 bits), also TByte

TFlop/s Tera (= 1012) Floating-point operations (usually in 64-bit, i.e. DP) per

second, also TF/s

Tier-0 Denotes the apex of a conceptual pyramid of HPC systems. In this

context the Supercomputing Research Infrastructure would host the Tier-0 systems; national or topical HPC centres would constitute Tier-1

UFL University of Florida

UNICORE Uniform Interface to Computing Resources. Grid software for seamless

access to distributed resources.

VSB Technical University of Ostrava

WCSS Wrocławskie Centrum Sieciowo-Superkomputerowe (Wrocław Centre

for Networking and Supercomputing)

WP Work Package

### **Executive Summary**

Work Package 12 (WP12) "Novel Programming Techniques" performs research and development in four key areas for future multi-petascale and exascale systems. The work in WP12 focuses on auto tuned and automatic techniques to be applied in parallel programming model runtimes (Task 12.1: "Auto-tuned runtime Environments"), performance tools (Task 12.3: "Development environments and tools") and file systems (Task 12.4: "File system optimization"). Furthermore, as it is widely accepted that the key to exploiting future highend systems will be based on research on new numerical algorithms as well as advancing the parallel processing technology used for higher scalability in numerical applications; consequently WP12 also focuses on research studies exposing more scalability for numerical algorithms (Task 12.2: "Scalable numerical algorithms").

The key research topics investigated in Task 12.2 are:

- Reducing Synchronization Overhead in Iterative Solvers

- Enhancing Parallel Hybrid Sparse Solvers for Scalability

- Topology-Awareness

- Enabling Hybridization in Heterogeneous Architectures

- Application Scalability

Task 12.2 evaluated different algorithms, methods, and approaches and demonstrated the scalability of the algorithms using simple ad-hoc programs. In total 17 complementary areas organized as individual *projects* were covered. This document is a summary of the projects' results. It contains high-level summaries of all projects as well as brief description of covered topics. In most of the summaries, links to PRACE white papers or scientific publications are given for those readers that are interested in more detailed information.

#### 1 Introduction

It is widely accepted that new numerical algorithms will be key to exploit future high-end systems and the focus of this deliverable is on exploring new algorithms and methods for enhancing the scalability of parallel numerical algorithms to meet the demands of petascale computing. The aim of Task 12.2 "Exploration of Scalable Numerical Algorithms" is to address the scalability of parallel numerical algorithms by focusing research on the following key topics:

- Reducing Synchronization Overhead in Iterative Solvers: Exploring new numerical algorithms and parallel computing methodologies to reduce the synchronization overhead in parallel iterative solvers,

- Enhancing Parallel Hybrid Sparse Solvers for Scalability: Exploiting algorithms and solvers that contain both direct and iterative components to reduce the global synchronization overhead by efficient and effective preconditioning that decrease the number of iterations while increasing the amount of computation per iteration,

- *Topology-Awareness*: Achieving topology-awareness in task-to-processor mapping to minimize the adverse effect of large processor-to-processor distances on communication overhead in large-scale parallel systems,

- Enabling Hybridization in Heterogeneous Architectures: Enabling hybridization of numerical operations and kernels via combining MPI programming paradigm with OpenMP-, threading-, CUDA- and OpenCL-based approaches,

- Application Scalability: Facilitating the usage and the embedding of state-of-the-art parallel processing technology to some target applications for enhancing scalability.

The focus of this deliverable is on the algorithms and methods but not on their integration on specific production applications. However, along with simple ad-hoc programs demonstrating the scalability of the algorithms, whenever possible, efforts towards initial embeddings of the proposed schemes to existing and widely used scientific applications are performed as well.

The deliverable itself is quite concise in order to allow people to easily identify the projects that are of particular interest for them and to encourage further reading in the accompanying white papers or the referred publications.

The rest of the deliverable is organized as follows. Chapter 2 provides a description of the organization of Task 12.2. Brief discussions on the main research topics as well as brief overviews of the Task 12.2 projects categorized according to these key topics are given in Chapter 3. Chapter 4 provides detailed descriptions of the Task 12.2 projects along with obtained results and discussions. Chapter 5 presents the conclusions.

#### 2 Task Organization

Table 1 displays a rough per partner PM distribution of Task 12.2. Around 130 PMs were allocated for this work and experts from nine countries are participating in Task 12.2. In total 17 projects have been completed. Most of the projects have been carried out with 4-7 PMs.

| Country        | Partner  | PMs  |

|----------------|----------|------|

| France         | IDRIS    | 6.0  |

| UK             | EPCC     | 7.0  |

| Switzerland    | ETHZ     | 14.0 |

| Poland         | WCSS     | 7.0  |

| Turkey         | UHeM-ITU | 12.0 |

|                | Bilkent  | 36.0 |

| Bulgaria       | NCSA     | 12.0 |

| Czech Republic | VSB      | 25.0 |

| Serbia         | IPB      | 4.0  |

| Italy          | CINECA   | 6.0  |

|                | Sum      | 129  |

Table 1: Overview of efforts per partner

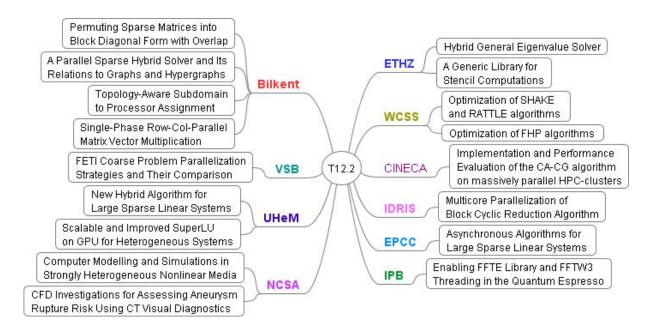

List of projects in Task 12.2 and their distribution among the 3rd parties is given in Figure 1.

Figure 1: Projects in Task 12.2

In order to structure work in Task 12.2, firstly, all projects defined the extent and purpose of their works in short statement of works (SOWs). Following these SOWs, to allow easy overview of all projects and to ensure that progress of all projects could be easily monitored, dedicated wiki pages have been set up and augmented with regular status reports. Figure 2 shows an example screen shot of one of the project wiki pages.

DL-POLY module to use OpenCL kernels).

#### Optimization of SHAKE and RATTLE algorithms The group will optimize the SHAKE and RATTLE algotithms using as a base for the study the DL-POLY application. We plan to evaluate the algorithms and further develop the OpenCL versions of the main parts of them (Leapfrog Verlet and Velocity Verlet integration scheme). The main goal is to increase the potential of the algorithms to support asynchrony and check the possibility of improving the accuracy of the GPU code (as there are some issues reported). We will also investigate the possibilities of developing a hybrid version of proposed algorithms, using the Principle Investigator: Mariusz Uchronski (WCSS) (mariusz.uchronski@pwr.wroc.pl) Contributors: Mariusz Uchronski (WCSS), Marcin Gebarowski (WCSS), Agnieszka Kwiecien (WCSS) 1. 31.01.2012 - Analysis of the status of the available code (CUDA/Fortran implementation of RATTLE and SHAKE algorithms used in DL-POLY, OpenCL partial implementation as an output from PRACE 1IP). Contacts and discussions with DL-POLY authors/developers. 2. 29.02.2012 - Implementation of OpenCL versions of RATTLE and SHAKE algorithms for target architectures 3, 31.03.2012 - Algorithms' evaluation and tests on single GPU/APU machine. Bugs and problems fixing 4. 30.04.2012 - Code optimization in order to achieve higher performance 5. 31.05.2012 - Investigate possibilities of developing a hybrid version MPI+OpenCL of RATTLE and SHAKE algorithms. Integration of OpenCL SHAKE and RATTLE algorithms with DL-POLY application. 6. 30.06.2012 - Tests on a cluster with GPUs and/or a cluster with AMD APUs (depending on the availability). 7. 31.08.2012 - Tests continuation. Collecting test results, writing the report and sending it to the sub-task leader • [31.01.2011] - Fortran/CUDA code of RATTLE and SHAKE algorithms used in DL\_POLY analysed. • [14.02.2012] - Implementation of SHAKE algorithm with OpenCL done. • [16.03.2012] - Developing RATTLE algorithm in OpenCL ongoing. • [29.03,2012] - Face to face discussion with DL POLY principal investigator about further OpenCL implementation. • [06.04.2012] - SHAKE algorithm test runs on different hardware (NVIDIA/AMD GPUs) in order to investigate possible performance bottlenecks. • [18.04.2012] - RATTLE algorithm still under development. • [30.05.2012] - Implementation of RATTLE algorithm done. Integration of the kernels into the DL-POLY code is ongoing (implementation of the interfaces to Fortran, modifications of the

Figure 2: An example project wiki page.

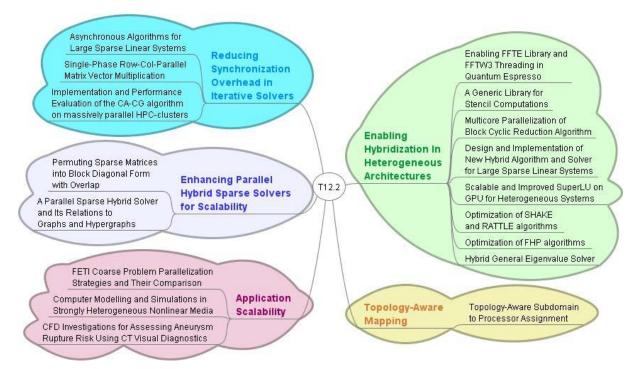

As stated before, Task 12.2 covers topics such as topology-awareness, reducing synchrony, and new numerical algorithms. Figure 3 gives a schematic overview of the projects in Task 12.2; it also illustrates how the covered major topics are distributed across projects.

Figure 3: Thematic overview of projects in Task 12.2.

#### 3 Task 12.2 Key Research Topics and Project Overviews

In this section, we present an overview of the 17 projects in Task 12.2 categorized according to the above-mentioned key research topics. For each topic, we also provide a brief introduction stating the importance of each topic.

#### 3.1 Reducing Synchronization Overhead in Iterative Solvers

Iterative algorithms have become the de-facto approach for the solution of sparse linear systems of equations on large-scale parallel systems due to their amenability to parallelization. Iterative algorithms have been successfully used for the solution of such linear systems on small-to-medium scale parallel systems. However, especially under peta-scale computing setups, bottlenecks in the parallelization of these algorithms have been observed. All iterative algorithms used for the solution of linear systems require a number of global synchronization operations (e.g., all\_reduce) for computing global scalars as well as a number of local synchronization operations due to the point-to-point communications incurred by the sparse matrix-vector operations. These local and global synchronization operations create barriers beyond which computation cannot proceed until all participating processors have reached that point. Projects in Sections 4.1, 4.2, and 4.3 can be considered as research efforts towards reducing synchronization overheads.

Section 4.1, entitled "Asynchronous Algorithms for Large Sparse Linear Systems" exploits asynchronous techniques that avoid the blocking behavior of synchronization operations by permitting processors to operate on whatever data they have, even if new data has not yet arrived from other processors. This project provides an experimental evaluation of the asynchronous approach on the Jacobi method, which is one of the simplest iterative algorithms.

Section 4.2, entitled "Designing and Implementing a Single-Phase Row-Column-Parallel Sparse Matrix Vector Multiplication Algorithm based on 2D Matrix Partitioning" proposes to address the two-phase communication bottleneck of the row-column-parallel SpMxV operation so that 2D nonzero-based matrix partitioning models and methods can be successfully utilized. This project also proposes and implements a two-stage approach to produce a *good* partition for the proposed single-phase row-column-parallel SpMxV algorithm.

Section 4.3, entitled "Implementation and Performance Evaluation of the CA-CG Algorithm on Massively Parallel HPC-Clusters", tries to deepen the understanding of an emerging class of methods (Communication Avoiding Krylov subspace methods) devised to overcome limitations due to synchronization issues in parallel sparse linear system solvers. The project evaluates the feasibility of implementation and testing the overall performance of the CA-CG algorithm on a set of benchmark platforms.

#### 3.2 Enhancing Parallel Hybrid Sparse Solvers for Scalability

Recently a number of hybrid algorithms and solvers that contain both direct and iterative components are proposed. These algorithms are promising in terms of robustness and scalability on parallel computing platforms. These algorithms are also utilized for reducing the above-mentioned global synchronization overhead by efficient and effective preconditioning that decreases the number of iterations while increasing the amount of computation per iteration. Here, effectiveness refers to decrease in the number of iterations required to convergence, whereas efficiency refers to the computational overhead introduced by the preconditioning steps and the amenability of the preconditioning operations to

parallelization. Projects in Sections 4.4 and 4.5 can be considered as research efforts towards reducing synchronization overheads through the use of hybrid linear system solvers.

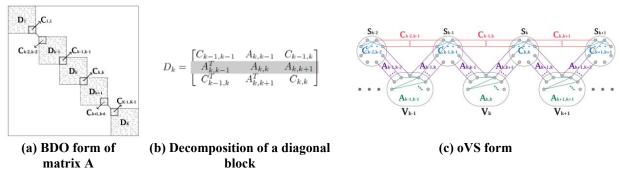

Section 4.4, entitled "Permuting Sparse Matrices into Block Diagonal Form with Overlap", proposes and implements a matrix reordering scheme for permuting a square sparse matrix into block-diagonal form with overlap for efficient parallelization of the multiplicative Schwarz and the DDKrylov preconditioners. The permutation objective of minimizing the overlap size also has a positive impact on the effectiveness of the Shwarz preconditioner via minimizing an upper bound on the iteration count.

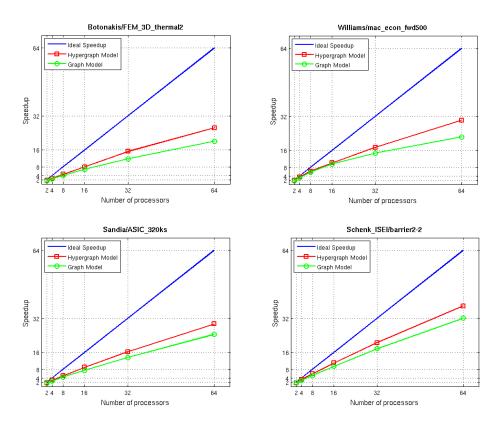

Section 4.5, entitled "A Parallel Sparse Hybrid Solver and Its Relations to Graphs and Hypergraphs", proposes and implements two different (graph- and hypergraph-based) matrix reordering schemes that enables the extraction of a small reduced system from a square sparse matrix for a successful *DS* factorization preconditioning scheme.

#### 3.3 Topology-Aware Mapping

The task-to-processor mapping in parallel systems can be vital for the performance of the executed programs. Especially for architectures that consist of thousands of processors (such as IBM BlueGene/P), the poor mapping of tasks to processors can lead to message contention since the network resources are usually shared by multiple communication tasks. This causes increase in message latencies and degrades the overall system performance. In such architectures, the message latencies are not independent of the number of links between two processors, which is counter to the assumption made by the cut-through and wormhole routing. Hence, the number of links (or hops) between processors becomes important when mapping tasks to processors. Taking this observation into account, careful mapping of tasks to processors which exploits the topology of the parallel architecture and the interaction between tasks can be very beneficial for the overall performance of the parallel system.

Section 4.6, entitled "Topology-aware subdomain-to-processor assignment" proposes and implements a two-phase framework for topology-aware task-to-processor mapping by considering both the task interaction and processor organization graphs. The first phase groups highly interacting tasks into K clusters, where K is equal to the number of processors, and the second phase performs one-to-one task-cluster-to-processor mapping with the objective of minimizing a metric defined on the volumes and distances of communication operations.

#### 3.4 Enabling Hybridization in Heterogeneous Architectures

The hybrid approach, combining MPI programming paradigm across computing nodes and OpenMP-, threading-, CUDA- and OpenCL-based approach within individual nodes, have been widely adopted by the computational science community for developing programs that execute on heterogeneous platforms (CPU multi-core processors combined with multi-core and/or accelerator technology). Sections 4.7, 4.8, 4.9, 4.10, 4.11, 4.12, 4.13 and 4.14 are all efforts towards exploiting the benefits of hybridization in large-scale computing performance.

Section 4.7, entitled "Multicore Parallelization of Block Cyclic Reduction Algorithm" investigates efficient parallelization of the Buneman's variant of block cyclic reduction algorithm for the solution of linear systems with coefficient matrices of block-tridiagonal form. Performance comparisons are given for a small-scale system using OpenMP and MPI.

Section 4.8, entitled "Enabling FFTE Library and FFTW3 Threading in the Quantum Espresso" investigates the effects of replacing the FFT routines in Quantum Espresso with better performing FFTE and FFTW3 libraries that support hybrid OpenMP + MPI approach.

Section 4.9, entitled "A Hybrid Hermitian General Eigenvalue Solver" proposes and develops general dense eigenvalue solvers based on single-node CPUs + GPU and CPUs + GPUs hybridization. The project provides an experimental comparison of the developed hybrid eigenvalue solvers against both a shared memory and a distributed memory library.

Section 4.10, entitled "A Generic Library for Stencil Computations" investigates the programmability issues, such as productivity and portable efficiency in parallel algorithm design and software development for HPC clusters and machines with accelerators. To this end, the project develops a domain specific C++ generic library for stencil computations, like PDE solvers. The library features high level constructs such as *do\_all* and *do\_reduce* and allows the development of parallel stencil computations with very limited effort.

Section 4.11, entitled "Design and Implementation of New Hybrid Algorithm and Solver for Large Sparse Linear Systems" describes the efforts towards improving the scalability of the direct linear system solver SuperLU via utilizing the MPI+OpenMP hybrid programming approach that combines the advantages of the two SuperLU libraries that are available for distributed and shared memory architectures.

Section 4.12, entitled "Scalable and Improved SuperLU on GPU for Heterogeneous Systems" describes the efforts towards improving the scalability of the direct linear system solver SuperLU via utilizing the MPI+CUDA hybrid programming approach.

Section 4.13, entitled "Optimization of Shake and Rattle Algorithms", investigates optimization of SHAKE and RATTLE algorithms, which are widely used in molecular dynamics simulations, through embedding CUDA and OpenCL implementations of these algorithms into the DL\_POLY molecular simulation package.

Section 4.14, entitled "Optimization of FHP Algorithms" investigates the possibility of accelerating FHP algorithms, which are used to solve Navier-Stokes equations derived from Newtonian Mechanics to describe the motion of fluid substances, using POSIX Threads, MPI, SSE, AVX and NVIDIA CUDA.

#### 3.5 Application Scalability

In the parallelization of applications, both due to the nature of the underlying application together with the adopted parallelization scheme certain parallelization overheads such as sequential components, synchronization overheads, and load imbalance may be tolerable up to a certain number of processors. However, when the level of parallelization reaches towards petascale, each of these parallelization overheads should be investigated and minimized in order to achieve a decent speedup on such large-scale systems. Sections 4.15, 4.16, and 0 are all efforts towards exploiting various algorithms and methods for increasing the scalability of the parallelization of their target applications.

Section 4.15, entitled "FETI Coarse Problem Parallelization Strategies and Their Comparison" investigates the parallelization of the Finite Element Tearing and Interconnecting (FETI) methods. For small-to-medium scale parallelization, the coarse-grain problem, which is obtained from subdomain interfaces, is solved sequentially on the master core. However, this is infeasible for petascale computing settings, because of the increase in memory requirements and decrease in scalability, which is due to the substantial increase in number of subdomains. The project investigates a number of methods for improving the scalability via parallel solution of the coarse system at different parallelization and redundant computation levels.

Section 4.16, entitled "Computer Modeling and Simulations in Strongly Heterogeneous Nonlinear Media" investigates incorporating selection of efficient parallel preconditioners,

parallel implementation of aggressive coarsening algorithms and adaptive time-stepping in the parallelization of the Finite Element Method (FEM) simulation of thermal and electrical fields in strongly heterogeneous nonlinear media on structured and unstructured meshes.

Section 0, entitled "CFD-Investigations for Assessing Aneurysm Rupture Risk for Individual Patient Using CT Visual Diagnostics" perform numerical experiments using the preconditioned *BiCGStab* (Bi-conjugate gradient stabilized) algorithm with incomplete factorization for the parallel solution of 3D Navier-Stokes equations for incompressible fluids, which is used in the modeling of the blood flow in cerebral aneurisms.

#### 4 Detailed Project Descriptions

In this chapter, detailed descriptions of the Task 12.2 projects along with obtained results and discussions are provided. All projects contain links to accompanying white papers or publications. All PRACE technical white papers are available on the PRACE-RI web site [https://bscw.zam.kfa-juelich.de/bscw/bscw.cgi/787675].

#### 4.1 Asynchronous Algorithms for Large Sparse Linear Systems

Supported by: Mark Bull and Iain Bethune (EPCC, University of Edinburgh)

**Whitepaper**: Mark Bull and Iain Bethune, "Asynchronous Algorithms for Large Sparse Linear Systems", http://eprints.ma.man.ac.uk/1838/.

Modern high-performance computing systems are typically composed of many thousands of cores linked together by high bandwidth and low latency interconnects. Over the coming decade core counts will continue to grow as efforts are made to reach Exaflop performance. In order to continue to exploit these resources efficiently, new software algorithms and implementations will be required that avoid tightly-coupled synchronization between participating cores and that are resilient in the event of failure.

This project investigates one such class of algorithms. The solution of systems of linear equations of the form  $A\mathbf{x}=\mathbf{b}$ , where A is a large, sparse n by n matrix and  $\mathbf{x}$  and  $\mathbf{b}$  are column vectors of size n, lies at the heart of a large number of scientific computing kernels, and so efficient solution implementations are crucial. Existing iterative techniques for solving such systems in parallel are typically synchronous, in that all processors must exchange updated vector information at the end of every iteration, and scalar reductions may be required by the algorithm. This creates barriers beyond which computation cannot proceed until all participating processors have reached that point, i.e. the computation is globally synchronized at each iteration. Such approaches are unlikely to scale to millions of cores.

This project is focused on developing asynchronous techniques that avoid this blocking behavior by permitting processors to operate on whatever data they have, even if new data has not yet arrived from other processors. To date there has been work on both the theoretical and the practical aspects of such algorithms. To reason about these algorithms one needs to understand what drives the speed of their convergence, but existing results merely provide sufficient conditions for the algorithms to converge, and do not help in answering some of the questions arising in the use of asynchronous techniques in large, tightly coupled parallel systems of relevance to exascale computing. This project tries to obtain insights by investigating the performance of the algorithms experimentally.

Taking Jacobi's method, one of the simplest iterative algorithms, one traditional synchronous and two asynchronous variants are implemented, using three parallel programming models - MPI, SHMEM and OpenMP. The performance of these implementations is investigated in

detail at scale on a Cray XE6, and some counter-intuitive properties which are of great interest when implementing such methods are discussed.

The performance of these algorithms depends on two key factors - the efficiency and scalability of the implementation, and the effect of asynchrony on the number of iterations taken to converge - both of which vary with the number of cores used. Table 2 and Table 3 show the number of iterations and execution time required to converge a heat diffusion problem on HECToR, a Cray XE6 system with 32 AMD Interlagos cores per node. *sync* is the synchronous version, *async* is a race-free asynchronous version and *racy* is an easier-to-program asynchronous version that includes deliberate race conditions: all three version are implemented in both MPI and SHMEM.

Results presented in Table 2 and Table 3 show that (except on the very largest core counts) SHMEM can provide a more efficient implementation of asynchronous message-passing than MPI, and that for problems that require on the order of thousands of cores, asynchronous algorithms can outperform their synchronous counterparts by around 10%. OpenMP (results not shown here) was found to give good performance for asynchronous algorithms, and was also very easy to program compared to either MPI or SHMEM. Although it has limited scalability due to the number of cores in a shared memory node, we suggest that OpenMP might be applicable in a hybrid model with MPI, for example, particularly since we found asynchronous Jacobi in OpenMP to be 33% faster than the synchronous equivalent even on a relatively modest 32 cores. In addition, asynchronous algorithms are expected to be tolerant to hardware performance defects, which could be an advantage on systems with millions of cores.

| Processes |        | Execution      |        |          |

|-----------|--------|----------------|--------|----------|

| Version   | Min.   | Min. Mean Max. |        | Time (s) |

| 32        |        |                |        |          |

| sync      | 1      | 9100           |        | 28.4     |

| async     | 10737  | 11245          | 12231  | 33.8     |

| racy      | 8952   | 9307           | 10140  | 27.7     |

| 512       |        |                |        |          |

| sync      |        | 37500          |        | 132.1    |

| async     | 36861  | 44776          | 51198  | 146.9    |

| racy      | 32377  | 38763          | 44623  | 126.4    |

| 8912      |        |                |        | 1        |

| sync      |        | 68500          |        | 247.1    |

| async     | 60612  | 82381          | 96700  | 272.5    |

| racy      | 61453  | 77952          | 90099  | 264.9    |

| 32768     |        |                |        |          |

| sync      |        | 112000         |        | 405.2    |

| async     | 101053 | 136337         | 165366 | 454.4    |

| racy      | 86814  | 118967         | 144902 | 419.4    |

| Processes |       | Execution      |        |          |

|-----------|-------|----------------|--------|----------|

| Version   | Min.  | Min. Mean Max. |        | Time (s) |

| 32        |       |                |        |          |

| sync      |       | 9100           |        | 27.6     |

| async     | 8724  | 9136           | 10784  | 26.7     |

| racy      | 8496  | 9088           | 10725  | 26.3     |

| 512       |       |                |        |          |

| sync      | 1     | 37500          |        | 130.1    |

| async     | 32356 | 38285          | 43178  | 117.9    |

| racy      | 32377 | 38416          | 46291  | 117.9    |

| 8912      |       |                |        |          |

| sync      |       | 68500          |        | 251.5    |

| async     | 32612 | 67417          | 77382  | 215.5    |

| racy      | 47231 | 70087          | 80620  | 219.3    |

| 32768     |       |                |        |          |

| sync      |       | 112000         |        | 491.1    |

| async     | 11265 | 229266         | 331664 | 858.5    |

| racy      | 10173 | 231919         | 314208 | 817.6    |

**Table 2: HECToR MPI results summary**

**Table 3: HECToR SHMEM result summary**

## 4.2 Designing and Implementing a Single-Phase Row-Column-Parallel Sparse Matrix Vector Multiplication Algorithm based on 2D Matrix Partitioning

Supported by: B. Ucar (CNRS), E. Kayaaslan, O. Ozturk, C. Aykanat (Bilkent University)

**Whitepaper**: E. Kayaaslan, B. Ucar, O. Ozturk, C. Aykanat, "Designing and Implementing a Single-Phase Row-Column-Parallel Sparse Matrix Vector Multiplication Algorithm based on 2D Matrix Partitioning", PRACE technical white paper.

Sparse matrix vector multiplication (SpMxV) is a kernel operation repeatedly performed in iterative linear system solvers. There are mainly three types of parallel SpMxV algorithms used in the scientific community: row-parallel, column-parallel and row-column-parallel. The row-parallel algorithm involves expand-type point-to-point communication operations on the local input vector entries before the local SpMxV operations; whereas column-parallel

algorithm involves fold-type point-to-point communication operations on the local output vector results after the local SpMxV operations. The row-column-parallel algorithm necessitates two-phase communication: expand operation before local SpMxVs and fold operation after the local SpMxVs. 1D rowwise and columnwise partitioning of the coefficient matrix are used for row-parallel and column-parallel SpMxV algorithms, respectively, whereas 2D-nonzero partitioning of the coefficiant matrix is used for row-column-parallel SpMxV algorithms. Several hypergraph partitioning models and methods have been successfully used for sparse matrix partitioning for efficient row-parallel, column-parallel and row-column-parallel SpMxV operations. In all these models the partitioning objective is to minimize the total volume of communication whereas the partitioning constraint is to minimize the computational load balance. 2D nonzero based partitioning models are both more scalable and perform considerably better than the 1D partitioning models in terms of communication volume metric. However, 1D models perform considerably better than 2D models in terms of speedup values due to the increased number of messages in the rowcolumn-parallel SpMxV algorithm. In this project, a one-phase row-column-parallel SpMxV algorithm is proposed to address this bottleneck of the row-column-parallel SpMxV operation so that 2D nonzero-based matrix partitioning models and methods can be successfully utilized.

In this project, a two-stage approach is proposed and adopted to produce a *good* partition for the above-mentioned one-phase row-column-parallel SpMxV algorithm. In the first stage, a *K*-way row/column partition and initial nonzero partition, either using one-dimensional (coarse-grain) [1] or two-dimensional (fine-grain) [3] partitioning approaches, is obtained for a *K* processor system. At the end of this stage, for each ordered pair of parts a submatrix whose nonzeros will be determined to be hold by either receiver or sender processor is obtained. The second stage refines the nonzero partition obtained in the first stage by using Dulmage-Mendhelson decomposition of these submatrices. In case of one-dimensional partitioning in the first stage, the off-diagonal submatrices are used, whereas in case of two-dimensional partitioning, in order to keep load balance, for each ordered pair of parts, the subset of the off-diagonal submatrix that is comprised of only nonzeros assigned to neither receiver nor sender processor is used. In the refinement step, the nonzeros that lie inside the horizontal blocks are assigned to sender, and the remaining nonzeros of the submatrices are assigned to receiver processor.

| Parallel algorithm          | row-parallel | column-parallel | row-column-parallel |        |        |

|-----------------------------|--------------|-----------------|---------------------|--------|--------|

| # of communication phases   | 1 phase      | 1 phase         | 2 phase 1 phase     |        | nase   |

| Part. scheme in first stage | 1D           | 1D              | 2D                  | 1D     | 2D     |

| bundle1                     | 8.326        | 8.003           | 5.739               | 5.918  | 8.342  |

| cbuckle                     | 9.545        | 10.622          | 8.612               | 9.819  | 10.605 |

| finan512                    | 13.575       | 13.504          | 11.640              | 13.677 | 13.682 |

| poisson3Da                  | 6.892        | 6.907           | 4.154               | 7.179  | 6.718  |

| rgg n 2_17_s0               | 12.701       | 13.240          | 11.137              | 13.180 | 12.868 |

| shuttle_eddy                | 6.079        | 5.991           | 3.743               | 6.177  | 6.180  |

| tube1                       | 11.263       | 11.233          | 9.505               | 11.149 | 8.668  |

| vibrobox                    | 5.181        | 6.017           | 3.415               | 6.123  | 4.933  |

| ASIC_320ks                  | 11.504       | 11.578          | 10.422              | 12.104 | 12.293 |

| msc10848                    | 11.789       | 11.786          | 9.862               | 11.539 | 11.466 |

Table 4: Speedup values obtained on a 16-processor system.

The validity of the proposed one-phase row-column-parallel SpMxV and the associated two-stage partitioning schemes is experimentally evaluated in terms of speedup values obtained on a 16-node PC-cluster located at Bilkent University. The test matrices are obtained from the

Florida Matrix Collection [2]. Table 4 presents these speedup values. In the table, a bold value in a row indicates the best speedup value obtained for the parallelization of the SpMxV associated with the respective test matrix. As seen in the table, these initial results are promising and extensive experimentation on a 512-node system is underway.

## 4.3 Implementation and Performance Evaluation of the CA-CG Algorithm on Massively Parallel HPC-Clusters

Supported by: G. Erbacci, M. Culpo, M. Guarrasi (CINECA)

Sparse linear systems lie at the core of many scientific computing applications. They can be solved by direct or iterative methods; the former preferred for their robustness when the problem size is small enough to make them affordable, the latter preferred due to their better asymptotic complexity and the high degree of parallelism they generally expose [4] when the systems to be solved are large enough.

In particular, fostered by the need to solve engineering problems of ever-growing complexity, modern iterative methods based on Krylov subspaces received a lot of attention in the last two decades [5]. This led to remarkable improvements in the underlying mathematical algorithms and to careful studies on the optimal way to implement them [6], producing as a result a number of widely known software packages that are proven to scale up to roughly a few thousands cores [7], [8].

While this state-of-the-art fits nicely into the framework of Tier-1 supercomputers, it becomes soon inadequate if Tier-0 resources are instead to be efficiently exploited. The main cause of this inadequacy is to be found in the current trends driving the HPC world towards architectures composed of millions of relatively slow cores that can reach, nowadays, performances up to almost 20 PetaFlop/s [9]. A rough comparison with the architecture of previous generation machines makes evident that algorithms need to increase their scalability by almost two orders of magnitude to effectively exploit the latest technologies. A request of such a kind cannot be satisfied by the standard Krylov subspace algorithms, as the amount and type of communications they require makes them too much synchronous for this task.

This project tries therefore to deepen the understanding of an emerging class of methods (Communication Avoiding Krylov subspace methods) [10], [11] precisely devised to overcome these limitations. This is done by evaluating the feasibility of implementation and testing the overall performance of the CA-CG algorithm on a set of benchmark platforms.

CA methods are based on the assumption that the cost of an algorithm includes both computations and communications<sup>1</sup>: rather than minimizing the computational cost only, they try therefore to minimize the overall cost. As for technological reasons communication costs are much higher than computational costs, this directly leads to the key idea that the best performance is obtained trying to avoid communication as much as possible, even if this may require some redundant arithmetic operations.

This strategy is realized in the CA-CG algorithm through the use of the Matrix Power Kernel and Block Inner Product algorithms. Though for a mathematically sound treatment the interested reader is referred to [10], it is anticipated that the CA-CG algorithms will require in the end a factor of  $\Theta(s)$  fewer messages if compared to standard CG, where s is the number of basis vectors generated by the matrix power kernels.

The framework used for the parallel implementation of the CA-CG algorithm is the one provided by PETSc [7], as this choice allows for a fair comparison with the standard CG

<sup>&</sup>lt;sup>1</sup> The term "communications" includes in this framework both the bandwidth terms (communication among different memory levels) and the latency terms (communication among different nodes)

algorithm available in the library. The two algorithms have been tested on a selected set of Sparse Positive Definite (SPD) matrices taken from the UFL database [2]. Finally, the tests have been conducted on both PLX [12] and FERMI [13] supercomputers.

While for the detailed results of the benchmarks we refer to the associated white paperwe can say that in many cases non-negligible increases of performances were found. This strengthened our conviction on the fact the CA algorithms may be considered the most promising line of research among the ones trying to improve parallelism and performance of Krylov subspace linear solvers.

In the near future CINECA plans to continue the testing activity on CA algorithms even outside of the PRACE framework, probing in particular the effectiveness of the currently available preconditioners for CA-CG and the efficiency of others CA algorithms (e.g. CA-GMRES) on a wider set of benchmarks. The long term aim in case of sufficiently good results is to incorporate these algorithms in production codes that are commonly used on FERMI.

## 4.4 Permuting Sparse Square Matrices into Block Diagonal Form with Overlap for Parallel Hybrid Sparse Solvers

Supported by: S. Acer, E. Kayaaslan, C. Aykanat, T. Dayar (Bilkent University)

**Whitepaper**: S. Acer, E. Kayaaslan, T. Dayar, C. Aykanat, "Permuting Sparse Matrices into Block Diagonal Form with Overlap for Parallel Hybrid Sparse Solvers", PRACE technical white paper.