# Low-Cost Fully Autonomous Piezoelectric Energy Harvesting Interface Circuit with up to 6.14x Power Capacity Gain

Berkay Çiftci<sup>1</sup>, Salar Chamanian<sup>1</sup>, Hasan Uluşan<sup>1</sup>, Halil Andaç Yiğit<sup>1</sup>, Aziz Koyuncuoğlu<sup>2</sup>, Ali Muhtaroğlu<sup>3</sup>, Haluk Külah<sup>1,2</sup>

<sup>1</sup>Electrical and Electronics Engineering Department, METU, Ankara, Turkey <sup>2</sup>METU-MEMS Center, Ankara, Turkey <sup>3</sup>Electrical and Electronics Engineering Department, METU-NCC, Güzelyurt, Mersin 10, Turkey

{cberkay,salar.chamanian,ayigit,hulusan}@metu.edu.tr akoyuncuoglu@mems.metu.edu.tr {amuhtar,kulah}@metu.edu.tr

Abstract—This paper presents a novel self-powered and fully autonomous interface circuit to extract piezoelectric energy from vibrations available in the environment for supplying DC voltage to electronic loads. A new energy extraction technique called Synchronized Switch Harvesting on Capacitor-Inductor (SSHCI) is utilized, which reduces system cost through a downsized inductor in the range of tens of µH's, while achieving as high voltage flipping efficiency as conventional SSHI circuits. Fabricated in 180 nm standard CMOS technology, the interface circuit has been tested on a MEMS piezoelectric energy harvester with 2 nF intrinsic capacitance in presence of vibrations at 415 Hz resonant frequency. SSHCI circuit provides 6.14x relative improvement over maximum output power of an ideal full-bridge rectifier (FBR) by utilizing a 68 µH inductor to charge a 453 nF storage capacitance. A maximum power conversion efficiency of 90.1% has been measured for SSHCI operation due to low power design techniques and optimized switching time for charge flipping.

# Keywords—Self-powered, autonomous, low-profile, piezoelectric energy harvester, IC, SSHCI, charge flipping time detection.

## I. INTRODUCTION

Proliferation of wireless sensor networks (WNSs) in daily life applications evokes the problem of maintaining the power they need for proper operation. Since batteries do not shrink at the same rate as sensor electronics, their use results in bulky sensor systems [1]. Furthermore, in some embedded WSN applications, replacement of batteries is problematic. An alternative power supply for WSNs can be obtained by harvesting energy from environment.

Piezoelectric energy harvesters (PEHs) are highly popular vibration transducers due to their relatively high output voltage levels and ease of integration. As PEHs generate AC voltage, a rectification circuit is needed to maintain stable DC voltage required for proper operation of electronic loads. The well-known interface circuit for AC-DC conversion is the full-bridge rectifier, which is adversely affected by the small inherent capacitance of PEH [2]. Therefore, nonlinear energy extraction approaches have been developed to increase the extracted power from PEHs [3]–[7]. Energy investment [3] and Synchronous Electric Charge Extraction (SECE) [4]–[6] techniques can provide load independent operation; however, their performance

regarding extracted power level is inferior compared to Synchronized-Switch Harvesting on Inductor (SSHI) technique [7]. Nevertheless, all of these methods require large external inductors to attain high levels of efficiency and power extraction gain. Large inductors increase overall system volume and cost. Inductorless designs presented in [8] and [9] utilize charge flipping capacitors instead of inductors to flip voltages, which reduces the system volume significantly. However, numerous switches required by such approaches curtail power conversion efficiency and extracted output power severely due to high switching losses. Moreover, interface circuits in [7]–[9] need external calibration of charge flipping time to obtain maximum output power for each PEH type and environmental conditions.

In this paper, a fully autonomous energy harvesting interface circuit is presented based on a new Synchronized Switch Harvesting on Capacitor-Inductor (SSHCI) technique to extract power from PEHs while utilizing a low-profile external inductor. In the following section, the operation of SSHCI is explained together with circuit design specifics. Measurement results from the fabricated chip are presented in Section III. Finally, Section IV concludes the paper.

# II. INTERFACE CIRCUIT DESIGN

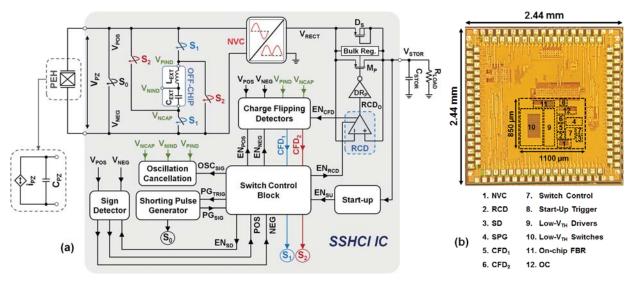

SSHCI circuit depicted in Fig. 1(a) utilizes a low-profile external inductor,  $L_{EXT}$ , in the range of tens of  $\mu$ H's to achieve voltage flipping through LC resonance between this inductor, the PEH capacitance C<sub>PZ</sub>, and external capacitance C<sub>EXT</sub>. A series capacitor is employed to limit the maximum resonating current. This leads to two-step flipping process to successfully invert charge of CPZ. SSHCI interface can achieve high power conversion efficiency and improved power capacity with lowprofile external components. The design can charge the storage capacitance C<sub>STOR</sub> from 0 V through a negative voltage converter (NVC) and an on-chip diode D<sub>S</sub>. After the charge conduction to  $C_{STOR}$ , the remaining charge on  $C_{PZ}$  is flipped with the resonance circuit established by C<sub>PZ</sub>, external capacitor C<sub>EXT</sub>, and external inductor L<sub>EXT</sub>. Unlike [7]–[9], optimum charge flipping instants are detected automatically using sensing comparators during charge flipping process. Utilizing conventional SSHI structure associated with capacitor-inductor flipping method, the circuit can deliver power conversion

Fig. 1. (a) Synchronized Switch Harvesting on Capacitor-Inductor (SSHCI) interface circuit, and (b) die micrograph of the implemented SSHCI chip.

efficiency as high as 90.1% and 6.14x higher power than maximum output power of an ideal full-bridge rectifier (FBR).

## A. Operation Phases

SSHCI circuit is composed of eight units as depicted in Fig. 1(a): Start-up trigger, NVC, reverse current detector (RCD), charge flipping detectors (CFDs), oscillation cancellation (OC), shorting pulse generator (SPG), sign detector (SD), and switch control block. Die micrograph of the SSHCI chip fabricated with 180 nm CMOS technology is shown in Fig. 1(b).

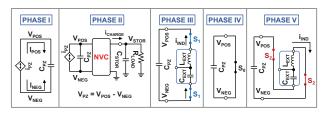

The enable trigger generated by the start-up unit indicates that there exists sufficient charge on C<sub>STOR</sub> to maintain proper operation of the SSHCI circuit. The interface has five operational phases illustrated with the equivalent circuits established in Fig. 2. As the PEH output swings, some amount of electrical charge is accumulated on CPZ due to the stress applied on the piezoelectric material (Phase I). The generated AC voltage is rectified through NVC. When the output of NVC, V<sub>RECT</sub>, exceeds storage voltage V<sub>STOR</sub>, RCD allows C<sub>STOR</sub> to be charged through the swing of PEH (Phase II). Charging process continues until  $V_{RECT} < V_{STOR}$  and then, RCD stops conduction by turning MP OFF. In addition, RCD enables CFD and turns S1 switches ON. During phase III, energy left on C<sub>PZ</sub> is transferred to the external capacitance C<sub>EXT</sub> through S<sub>1</sub> switches. C<sub>EXT</sub> is chosen to be equal to CPZ in order to achieve matched impedance for maximum power transfer. Considering the sign of piezoelectric voltage (V<sub>PZ</sub>) detected with SD, CFD is activated to find the instant at which maximum amount of energy is transferred from  $C_{PZ}$  to  $C_{EXT}$ . Following the energy transfer from CPZ to CEXT, CPZ is shorted in phase IV to discard the possible residual charge. The energy on CEXT is transferred back to CPZ in the reverse polarity by means of S<sub>2</sub> switches in phase V to complete the charge flipping process. CFD again monitors the moment that the maximum energy transfer from C<sub>EXT</sub> to C<sub>PZ</sub> is attained. Finally, system turns back to phase I in which all switches are OFF, and nodes VPIND, VNIND, and VNCAP are shorted to ground to eliminate any residual charge on CEXT and  $L_{EXT}$ , hence preventing oscillation. Measured waveforms of  $V_{PZ}$  reverse current detector output RCD\_0, and inductor current  $i_{IND}$  during operation phases are shown in Fig. 3.

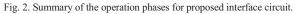

#### B. Negative Voltage Converter

Rectification of the AC voltage coming from PEH is conducted by NVC presented in Fig. 4(a). Two NMOS switches

Fig. 3. Measured waveforms of piezoelectric voltage  $V_{PZ}$ , reverse current detector output RCD<sub>0</sub>, and inductor current  $i_{IND}$  during operation phases.

Fig. 4. (a) Implementation of negative voltage converter (NVC) and (b) the comparator utilized inside NVC circuit.

$M_{N1}$  and  $M_{N2}$  are controlled by two comparators shown in Fig. 4(b). Comparators have current-follower input stages to monitor PEH terminal voltages  $V_{POS}$  and  $V_{NEG}$ . They decide which terminal is connected to ground for rectification purposes. Cross-coupled PMOS switches  $M_{P1}$  and  $M_{P2}$  driven by PEH terminals help governing the charge flow path to supply a positive voltage. Mismatching created by different aspect ratios of  $M_3$  and  $M_4$  provides a more stable operation by preventing oscillation during transitions.

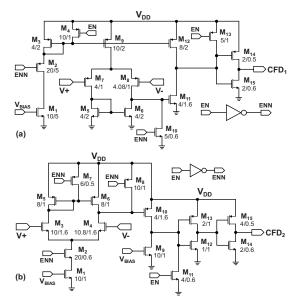

# C. Charge Flipping Detectors

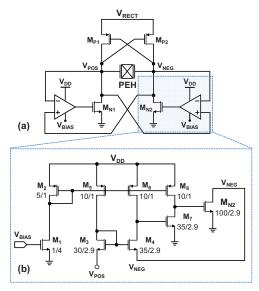

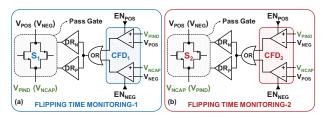

Flipping time monitoring configurations for the autonomous flipping operations conducted by  $S_1$  and  $S_2$  switches are depicted in Fig. 5. In addition, Fig. 6 illustrates the details of the charge flipping detector circuits. For the detection of maximum energy transfer point from  $C_{PZ}$  to  $C_{EXT}$  in phase III, PMOS input pairs were used, since compared voltage levels are below half of the supply voltage level ( $V_{STOR}=V_{DD}$ ), which better fits to common mode range of PMOS input pairs. Similarly, NMOS input pairs were utilized in phase V to find the maximum energy transfer instant from  $C_{EXT}$  back to  $C_{PZ}$ , as compared voltage levels are above the half of  $V_{STOR}$ . MOSFETs  $M_{11}$  in CFD<sub>1</sub> and  $M_{10}$  in CFD<sub>2</sub> are of low threshold type ( $V_{TH}\approx 300$  mV). This extends the common mode voltage range, and increases the bandwidth. To avoid waste of power, both circuits are completely disabled during the phases they are not used.

## **III. EXPERIMENTAL RESULTS**

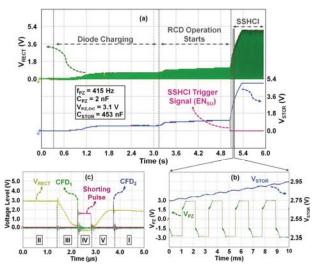

A custom-made MEMS PEH with  $C_{PZ}=2$  nF was utilized to validate the performance of the interface. A 453 nF capacitor was utilized for  $C_{STOR}$ , and three different SMD inductors (68, 47, and 27 µH) were employed as  $L_{EXT}$  together with  $C_{EXT}=C_{PZ}$ . Fig. 7 depicts the measured waveforms of  $V_{PZ}$ ,  $V_{RECT}$ ,  $V_{STOR}$ , and overall enable signal for charging from  $V_{STOR}=0$  V after start-up. RCD operation is initiated before the overall enabling signal to speed up the start-up operation. Charging of  $V_{STOR}$  with aforementioned SSHCI operation phases through optimum

Fig. 5. Flipping time monitoring configurations established for (a)  $S_1$  and (b)  $S_2$  switching operations.

Fig. 6. Schematics of (a) charge flipping detector-1  $(CFD_1)$  and (b) charge flipping detector-2  $(CFD_2)$ .

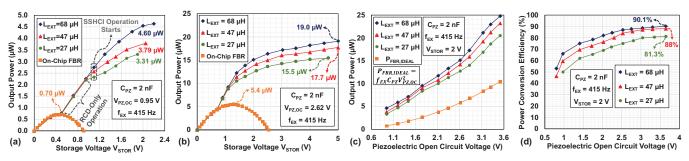

charge flipping detection is also illustrated in the Fig. 7. Fig. 8 shows measured output power of SSHCI circuit for different piezoelectric open circuit voltage (VPZ,OC) amplitudes. During these measurements, the shaker table was excited with 415 Hz which is the resonant frequency of the MEMS PEH. SSHCI is able to provide 6.14x relative performance improvement over maximum output power of an ideal FBR for VPZ,OC=0.95 V. For larger V<sub>PZ,OC</sub> levels, relative performance improvement reduces due to larger damping and lower displacements of the transducer. Measured power conversion efficiency ( $\eta = P_{OUT}/P_{IN}$ ) for different L<sub>EXT</sub> values given in Fig. 8(d) reveals that the circuit achieves around 90.1% conversion efficiency for  $L_{EXT}=68 \mu H$ , which is higher than the efficiency reported by previous designs with large inductors [2]–[7]. Table I provides comparison of the SSHCI test chip performance against the state of the art. Although flipping capacitor rectifier (FCR) in [8] provides an inductorless design, its figure of merit (FOM), which is defined as FOM= $P_{OUT}/f_{EX}V_{PZ,OC}^2C_{PZ}$ , and power conversion efficiency are inferior to SSHCI. Besides, compared to the literature, SSHCI circuit, which has a fully autonomous charge flipping time detection, can achieve higher efficiency and FOM by utilizing low-profile inductors.

## IV. CONCLUSION

A low-profile fully autonomous interface circuit has been presented in this paper. A new SSHCI technique with automatic

Fig. 7: Measured waveforms of SSHCI circuit illustrating (a) start-up, (b) charging, and (c) control signals generated during voltage flip operations.

charge flipping detection has been introduced to attain high power conversion efficiency and output power by utilizing inductors in the range of tens of  $\mu$ H's. The fabricated IC yields a maximum of 6.14x relative performance improvement over maximum output power of an ideal FBR, and 90.1% power conversion efficiency. SSHCI circuit supplies energy to microelectronic devices while downsizing the volume (cost) of the external components compared to alternatives.

## ACKNOWLEDGMENT

This work has received funding from the European Research Council (ERC) under the European Union's Horizon 2020 research and innovation programme (grant no:682756).

## REFERENCES

- [1] R. J. M. Vullers et al., "Energy Harvesting for Autonomous Wireless Sensor Networks," IEEE Solid-State Circuits Mag., vol. 2, no. 2, 2010.

- [2] Y. K. Ramadass and A. P. Chandrakasan, "An Efficient Piezoelectric Energy Harvesting Interface Circuit Using a Bias-Flip Rectifier and Shared Inductor," JSSC, vol. 45, no. 1, pp. 189-204, 2010.

- [3] D. Kwon and G. A. Rincon-Mora, "A Single-Inductor 0.35 µm CMOS Energy-Investing Piezoelectric Harvester," ISSCC, pp. 78-80, 2013.

- T. Hehn et al., "A fully autonomous integrated interface circuit for [4] piezoelectric harvesters," JSSC, vol. 47, no. 9, pp. 2185–2198, 2012.

- [5] S. Chamanian et al., "An Adaptable Interface Circuit with Multi-Stage Energy Extraction for Low Power Piezoelectric Energy Harvesting MEMS," *IEEE TPEL*, 2018.

- M. Dini et al., "A Nanopower Synchronous Charge Extractor IC for Low-[6] Voltage Piezoelectric Energy Harvesting with Residual Charge Inversion," IEEE TPEL, vol. 31, no. 2, pp. 1263-1274, 2016.

- [7] D. A. Sanchez et al., "A 4µW-to-1mW Parallel-SSHI Rectifier for Piezoelectric Energy Harvesting of Periodic and Shock Excitations with Inductor Sharing, Cold Start-up and up to 681% Power Extraction Improvement," ISSCC, vol. 59, pp. 366-367, 2016.

- Z. Chen et al., "A 1.7mm<sup>2</sup> Inductorless Fully Integrated Flipping-[8] Capacitor Rectifier (FCR) for Piezoelectric Energy Harvesting with 483% Power-Extraction Enhancement," ISSCC, vol. 60, pp. 372-374, 2017.

- S. Du et al., "An Inductorless Bias-Flip Rectifier for Piezoelectric Energy Harvesting," *JSSC*, vol. 52, no. 10, pp. 2746–2757, 2017. [9]

Fig. 8: (a, b) Measured output power by SSHCI circuit compared to on-chip full-bridge rectifier (FBR) with different piezoelectric open circuit voltage levels V<sub>PZ,OC</sub>, and (c) ideal FBR, and (d) power conversion efficiency of the operation. TADIEI

|                                                        |                      |                         |                 |                                     | 1                                  | ABLEI                         |                               |                                                           |                                                               |                         |

|--------------------------------------------------------|----------------------|-------------------------|-----------------|-------------------------------------|------------------------------------|-------------------------------|-------------------------------|-----------------------------------------------------------|---------------------------------------------------------------|-------------------------|

| COMPARISON OF THE IMPLEMENTED IC WITH STATE OF THE ART |                      |                         |                 |                                     |                                    |                               |                               |                                                           |                                                               |                         |

| Ref.                                                   | Tech.                | Scheme<br>Type          | $C_{\text{PZ}}$ | Excitation<br>Frequency             | Inductor<br>(Volume)               | Flipping<br>Time<br>Detection | Cold<br>Start-up              | Peak<br>Conversion<br>Efficiency                          | Power Extraction<br>Improvement<br>(FOM <sup>(1)</sup> x100)  | Chip<br>Size            |

| [2]                                                    | 350 nm               | SSHI                    | 12 nF           | 225 Hz                              | 820-22 μH<br>(NA)                  | External<br>Adjustment        | NO                            | 85 <sup>(2)</sup> % (47 μH)<br>87 <sup>(2)</sup> % (22μH) | 420 <sup>(5)</sup> % (820 μH)<br>257 <sup>(5)</sup> % (22 μH) | 4.25<br>mm <sup>2</sup> |

| [3]                                                    | 350 nm               | Energy<br>Investment    | 15 nF           | 143 Hz                              | 330 μH<br>(126 mm <sup>3</sup> )   | NA                            | NO                            | 69.2%                                                     | 360%                                                          | 2.34<br>mm <sup>2</sup> |

| [6]                                                    | 320 nm               | SECE                    | 52 nF           | 60 Hz                               | 10 mH<br>(NA)                      | NA                            | YES                           | 85.3 <sup>(3)</sup> %                                     | 351%                                                          | 0.95<br>mm <sup>2</sup> |

| [7]                                                    | 350 nm               | SSHI                    | 26 nF           | 225 Hz                              | 3.3 mH<br>(20.14 cm <sup>3</sup> ) | External<br>Adjustment        | YES                           | 88 <sup>(4)</sup> %                                       | 440%                                                          | 0.72<br>mm <sup>2</sup> |

| [8]                                                    | 180 nm               | FCR                     | 80 pF           | 110 kHz                             | NO                                 | External<br>Adjustment        | YES                           | NA                                                        | 483 <sup>(6)</sup> %                                          | 1.70<br>mm <sup>2</sup> |

| This<br>Work                                           | 180 nm               | SSHCI                   | 2 nF            | 415 Hz                              | 68-27 μH<br>(18 mm <sup>3</sup> )  | Autonomous<br>Adjustment      | YES                           | 90.1% (68 μH)<br>88% (47 μH)<br>81.3% (27 μH)             | 614% (68 μH)<br>506% (47 μH)<br>441% (27 μH)                  | 0.94<br>mm <sup>2</sup> |

| (1) FOI                                                | $M = P_{OUT}/f_{ET}$ | VPZ,OC <sup>2</sup> CPZ |                 | (2) It is only for DC-DC converter. |                                    |                               | (3) External supply was used. |                                                           |                                                               |                         |

(4) Calculated from paper.

(3) External supply was used.

(6) Calculated with respect to on-chip FBR.

<sup>(2)</sup> It is only for DC-DC converter. (5) Calculated with respect to off-chip FBR.