David L. Blackburn and David W. Berning

Semiconductor Devices and Circuits Division National Bureau of Standards Washington, DC 20234

### ABSTRACT

Three temperature-sensitive electrical parameters are compared as thermometers for power MOSFET devices. The parameters are the forward drain-body diode voltage, the source-gate voltage, and the on-resistance. The results are also compared with temperatures measured with an infrared microradiometer. The procedure, apparatus, and circuits required to use each of the parameters as a thermometer are described. Some general considerations for measuring the temperature of power semiconductor devices are also discussed. Each parameter is found to be satisfactory for measuring the temperature of power MOSFETs. The sourcegate voltage measures a temperature nearest to the peak device temperature, and the drainbody diode voltage shows the least variation in calbiration from device to device.

#### INTRODUCTION

Power Metal Oxide Semiconductor Field Effect Transistors (power MOSFETs) are relatively recent innovations. These devices are rapidly finding uses in many new as well as established applications because of their fast switching speeds and their relative freedom from thermal instabilities as compared to bipolar transistors. Because power MOSFETs are relatively new devices and because they are still in a state of evolution, measurement methods for characterizing many of their important electrical and thermal properties are in a rudimentary phase.

One of the most important parameters of any semiconductor device is its operating temperature. The operating temperature is important in determining the reliability and operating life of the device, and it also has a strong influence on many of the electrical parameters of the device. The thermal resistance of a device,  $R_{\theta}$  (°C/W), is given by:

$$R_{\theta} = \frac{\Delta T_R}{P}$$

where  $\Delta T_R$  (°C) is the rise in device temperature with respect to the temperature of a specified reference point and P (W) is the power dissipated by the device. Ideally, thermal resistance

is a device specification that permits the user to establish the temperature for any power level. In order for a device manufacturer to specify and for a user to verify the device thermal resistance, an accurate, reliable method for measuring the device temperature is required. Ideally, the method would be nondestructive. Traditionally, temperature-sensitive electrical parameters (TSEPs) are used to measure the temperature of a semiconductor device.

The purpose of this paper is to provide a comparison of three techniques using three different TSEPs for measuring the temperature of power MOS-FETs and to compare each with the temperature determined using an infrared microradiometer (IRM). The three TSEPs used in this study as device thermometers are the source-gate voltage measured at a low level drain current, the forward voltage of the drain-body diode, and the device on-resistance. In addition, a brief discussion of some general considerations for power semiconductor device temperature measurement is given.

## TEMPERATURE-SENSITIVE ELECTRICAL PARAMETERS

A temperature-sensitive electrical parameter is usually used as a thermometer to nondestructively measure the temperature of a semiconductor device. Many device electrical parameters are temperature sensitive, but the TSEP must satisfy several criteria if it is to be considered as a practical device thermometer. First, its variation with temperature must be large enough to be readily measured and to provide sufficient temperature resolution for the application at hand. Most practical TSEPs vary by several mV/°C (or equivalent). Second, the TSEP must be monotonic and ideally vary linearly with temperature. This allows easy calibration of the TSEP. Third, the TSEP should be stable and repeatable for at least as long as it takes to perform the measurement. Fourth, the TSEP should indicate a temperature that is representative of that of the device being measured. For device reliability and operating life considerations, this temperature would be the maximum device temperature (the device temperature is nearly always nonuniform). Finally, the TSEP should be a device parameter that is easily and quickly measured with a minimum of interference from other device parameters.

U.S. Government work not protected by U.S. copyright.

DRAIN CONTACT REGION (n+)

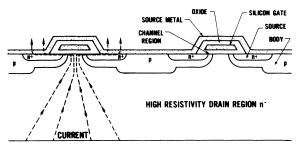

Figure 1. A cross-sectional view of a typical power MOSFET.

A cross-sectional view of a typical n-channel, vertical, double diffused power MOSFET (VDMOS) showing the charge flow when the transistor is conducting and the critical device elements pertinent to the following discussion is given in figure 1. A practical power MOSFET will contain several thousand of the "cells" shown in the figure. Each of the TSEPs examined in this study will be discussed with reference to this figure.

## Drain-Body Diode Forward Voltage, $V_{DB}$

The drain-body diode is formed at the junction of the opposite conductivity type drain and body regions (p-type body and n-type drain for the nchannel device of fig. 1). The forward voltage of the diode can be directly sensed at the sourcedrain terminals because the source metallization overlaps and makes electrical contact to the body region. The source-metal contact to the body provides a low resistance path for "stray" minority carriers that may enter the body region (such as due to leakage or avalanche current generated at the drain-body junction) and thus inhibits their injection into the source. Injection of minority carriers into the source can turn on the parasitic bipolar transistor comprised of the source-body-drain causing the gate to "lose control" of the MOSFET. The metal contacting both body and source thus enhances the safe operating limits of the MOSFET.

A substantial body of knowledge exists concerning the temperature sensitivity of a forward-biased diode (1). For constant current:

$$\frac{\partial \mathbf{v}_{\mathrm{DB}}}{\partial \mathbf{T}} \left|_{\mathbf{I}_{\mathrm{DB}}} = -\frac{\left(\frac{\mathbf{E}_{go}}{\mathbf{q}} - \mathbf{v}_{\mathrm{DB}}\right)}{\mathbf{T}}\right|$$

where  $V_{DB}$  (V) is the forward voltage of the drain-body diode, T (°C) is the diode temperature,  $E_{go}$  (eV) is the 0 K band gap energy, and q (C) the electron charge. It is found that typically  $\left( \frac{\partial V_{DB}}{\partial T} \right) |_{IDB} \sim -2 \text{ mV/°C}$ . For the power MOSFET of figure 1, the drain-body diode forward voltage senses the temperature in the immediate vicinity of the diode.

## Drain-Source On-Resistance, R<sub>DS</sub>(on)

The drain-source on-resistance of a power MOSFET is comprised primarily of the channel resistance plus the drain resistance and is given by (2):

$$R_{DS}(on) = R_{Ch} + R_{D} = \frac{1}{\beta (V_{G} - V_{T})} + k \rho_{D}$$

,

where  $R_{\rm Ch}~(\Omega)$  is the channel resistance and  $R_{\rm D}~(\Omega)$  is the drain resistance, and  $V_{\rm G}~(V)$  is the gate-source voltage,  $V_{\rm T}~(V)$  is the threshold voltage,  $\rho_{\rm D}~(\Omega^{\bullet}\,{\rm cm})$  is the drain region material resistivity, k (cm^{-1}) is a geometrical factor depending upon the relative dimensions of the device structure, and  $\beta$  is given by:

$$\beta = (W/L) \cdot C \cdot \mu ,$$

where W (cm) is the channel width, L (cm) is the channel length,  $C_0$  (f·cm<sup>-2</sup>) is the gate oxide capacitance per unit area, and  $\mu_e$  (cm<sup>2</sup>·V<sup>-1</sup>·S<sup>-1</sup>) is the electron mobility in the channel inversion layer.

Both  $R_{Ch}$  and  $R_D$  are temperature sensitive. The channel resistance varies with temperature because both  $V_T$  and  $\mu_e$  are temperature sensitive. The drain resistance varies with temperature because  $\rho_D$  is temperature sensitive. When the device is turned on with a large gate voltage  $(V_G >> V_T)$ , the channel resistance contributes very little to  $R_{DS}(\text{on})$ . For this condition, both  $R_{DS}$  and  $\left( \frac{\partial R_{DS}(\text{on})}{\partial T} \right) \big|_{ID}$  are dominated by the drain resistance.

Over the temperature range of interest, the drain resistivity temperature variation is dominated by the temperature dependence of the bulk mobility which is dominated by lattice scattering. Computed values of the temperature coefficient of resistance  $(1/\rho) \cdot (d\rho/dT)$  vary from about +0.007/°C for 1  $\Omega$  cm n-type material to about +0.008/°C for 100  $\Omega \cdot cm$  n-type material at room temperature (3). A less than 1-percent change in drain region resistance (and thus R<sub>DS</sub>(on)) occurs for a 1°C change in temperature. For a "typical" device with  $R_{DS}(on) = 1 \Omega$ , the variation of  $R_{DS}(on)$ with temperature is about +7  $m\Omega/\circ C$ . The drainsource on-resistance primarily senses the temperature in the active drain region of the device.

## Source-Gate Voltage, VSG

The source-gate voltage controls the on/off state of the MOSFET. The threshold voltage,  $V_{\rm T},$  is approximately equal to the value of  $V_{\rm SG}$  required to begin to turn on the MOSFET. When  $V_{\rm SG}$  is used as a thermometer in this work, the device is barely "turned on" and  $V_{\rm SG} \approx V_{\rm T}.$

The drain current,  $I_{\rm D},$  is related to  $V_{\rm SG}$  by:

$$I_{\rm D} = \frac{\beta}{2} (V_{\rm SG} - V_{\rm T})^2$$

(1)

Equation (1) is valid when the MOSFET is operating in the saturation mode, i.e., when the drain-source voltage,  $V_{\rm DS}$  >  $V_{\rm SG}$ . In this work, when using  $V_{\rm SG}$  as a thermometer,  $V_{\rm DS}$  >>  $V_{\rm SG}$ .

From equation (1):

$$\frac{\partial \mathbf{V}_{SG}}{\partial \mathbf{T}} \bigg|_{\mathbf{I}_{D}} = \left(\frac{2\mathbf{I}_{D}}{\beta^{3}}\right)^{1/2} \cdot \frac{d\beta}{d\mathbf{T}} + \frac{d\mathbf{V}_{T}}{d\mathbf{T}} .$$

(2)

For small values of  $I_D$  (~10 mA),  $V_{\rm SG} \sim V_{\rm T}$  and the magnitude of the first term on the right of equation (2) is small compared to the second term  $\left({\rm d}V_T/{\rm d}T\right)$ . The temperature variation of  $V_{\rm T}$  results from the temperature variation of the Fermi level in the channel region. Thus, when used as a thermometer, the source-gate voltage senses the temperature in the channel region of the device. For practical devices,  ${\rm d}V_T/{\rm d}T \sim -2$  to -6 mV/°C.

#### APPARATUS, CIRCUITS, AND PROCEDURES

The apparatus for making a measurement of the device temperature for each of the techniques investigated consists of a temperature-controlled heat sink for the device, an electronic temperature control system, and the respective electronic switching and measurement circuitry. Each of these items as well as the measurement procedure will be discussed.

## Measurement Procedure

The measurement procedure is essentially the same for each of the TSEPs investigated. Only steadystate measurements will be discussed, but most of what follows also applies to transient measurements. The general procedure used is to repetitively power the device under test (DUT) with "normal" (heating) operating conditions and to then rapidly switch to a "measurement" (cooling) condition. The duty cycle (heating power time/measurement time) is typically about 99 percent. The case temperature of the device (only JEDEC TO-3 encased devices were studied) is held constant by the temperature-controlled heat sink and is continuously monitored.

During the measurement time, the TSEP is monitored. An oscilloscope was used in this study to enable the entire TSEP waveform to be measured as a function of time. The ability to monitor the TSEP during the entire measurement time permits one to determine the rate at which the device is cooling. This is important for determining the actual temperature at the instant the device is switched from the heating to the measurement condition as well as for determining when extraneous, nonthermal effects are interfering with the measurement. These concepts will be discussed in more detail in a later section.

The required calibration of the TSEP is accomplished by monitoring the TSEP as the neat-sink temperature (and thus the DUT temperature) is varied with only measurement conditions applied

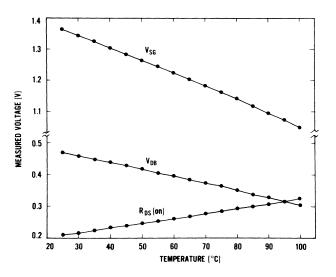

Figure 2. Examples of calibration curves for each of the TSEPs.

and no heating power applied to the DUT (0percent duty cycle). Examples of a calibration curve for each of the TSEPs investigated in this study are shown in figure 2. To determine the device temperature for the actual measurement, the value of the TSEP obtained during the measurement is matched with the calibration curve. It is assumed that the same device temperatures give the same value for the TSEP during measurement and calibration.

# Temperature-Controlled Heat Sink

In order for the measured temperature to be a meaningful parameter, some well-defined reference point associated with the device must be maintained at a constant temperature during measurement. The reference point chosen in this work is on the bottom outside of the transistor case directly below the semiconductor chip. The temperature is monitored by either a glass bead thermistor or a thermocouple using the washer technique (4). The DUT is firmly clasped to a temperaturecontrolled heat sink to maintain a constant reference point temperature. The heat sink is made of a copper block which contains water channels for the flow of chilled water as well as several "heating" resistors. The heat-sink temperature control is achieved by electronically controlling the power supplied to the heating resistors. The flow rate of chilled water is manually controlled. The electronic temperature controller uses the glass bead thermistor (thermocouple) to sense the temperature for control purposes. Care is taken to assure that the heat sink surface is flat and "burr free." The DUT attaching screws are screwed down with the same torque, and a thermal grease is used between the device and heat sink for all measurements.

#### Measurement Circuits

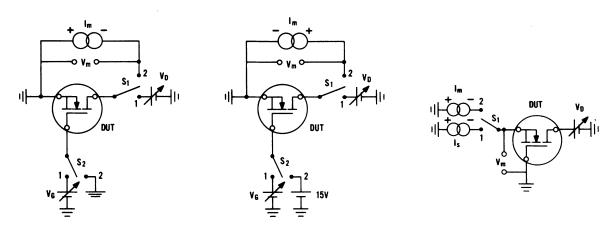

Simplified schematics of the measurement circuits used for each of the TSEPs are shown in figure 3.

(a) Drain-Body Voltage

(b) Drain-Source On-Resistance

(c) Source-Gate Voltage.

Figure 3. Schematics of measurement circuits for each TSEP.

A brief description of the operation of each circuit follows.

Drain-Body Forward Voltage Measurement Circuit. The circuit used to control the device and to measure the temperature using the forward voltage of the drain-body diode as a TSEP is shown in figure 3a. The circuit consists of the DUT, two power supplies, a current source, and two electronic switches. During the heating phase of the measurement, switches  $S_1$  and  $S_2$  are in position 1. The values of  $V_C$  and  $V_D$  are adjusted to achieve the desired values of  $I_D$  and  $V_{DS}$  for the "heating" conditions.

To measure the temperature, switches  $S_1$  and  $S_2$  are each switched to position 2. Thus, the gate is grounded and current source  $I_m$  supplies a forward measurement current to the drain-body diode. The polarity of the current source is such that the voltages applied to the MOSFET source and drain are opposite to those employed during normal MOSFET operation; i.e., for the measurement for an n-channel device, the drain is biased negative with respect to the source. The magnitude of  $I_m$ is typically 1 to 10 mA. The drain-to-source voltage required to maintain the constant  $I_m$  is equal to the forward drain-body diode voltage.

Drain-Source On-Resistance Measurement Circuit. The circuit used to measure the temperature using the on-resistance as the TSEP is shown in figure 3b. The circuit consists of the DUT, three power supplies, a constant current source, and two electronic switches. During the heating phase of the measurement, switches  $S_1$  and  $S_2$  are in position 1 and  $V_D$  and  $V_G$  are adjusted to achieve the desired  $I_D$  and  $V_{DS}$ .

To measure the temperature, both  $\rm S_1$  and  $\rm S_2$  are switched to position 2. This supplies 15 V to the gate terminal with respect to the source and also maintains a constant drain current,  $\rm I_m$ . The magnitude of  $\rm I_m$  is kept constant for a particular measurement but varies from device to device (from 0.1 to 1 A) depending upon the magnitude of  $\rm R_{DS}(on)$ . The value of  $\rm I_m$  is adjusted so that

$V_{\rm DS} \sim$  0.5 V. The voltage  $V_{\rm DS}$  =  $V_m$  is measured and is related to  $R_{\rm DS}(\text{on})$  by:

$$R_{DS}(on) = V_m / I_m$$

Source-Gate Voltage Measurement Circuit. The circuit for controlling the device and measuring its temperature using the source-gate voltage as a thermometer is shown in figure 3c. The circuit consists of the DUT, two current sources, one power supply, and one electronic switch. During the heating phase, switch  $S_1$  is in position 1. Thus, the drain current is equal to  $I_S$  and the drain-source voltage is equal to  $V_{D^*}$ . To measure the temperature,  $S_1$  is switched to position 2 changing the drain current to  $I_m$ . For this measurement,  $I_m << I_S$ , and  $I_m \sim 1$  to 10 mA. The source-gate voltage is monitored during the measurement phase  $(V_m)$  and is the TSEP.

#### EXPERIMENTAL RESULTS

Temperature measurements using the three TSEPs as thermometers as well as with an infrared microradiometer (IRM) have been made on a wide variety of power MOSFET devices. The maximum voltage rating as specified by the manufacturer varied from 60 to 450 V. Only n-channel devices were included in the study, but similar results would be expected on p-channel devices with the appropriate measurement circuit polarity reversals.

## Calibration

Typical calibration curves are shown in figure 2. Each of the TSEPs is sufficiently linear with temperature and demonstrates a large enough change with temperatures to be considered as a practical TSEP. The amount of time required to generate a calibration curve depends upon the number of calibration points desired and the time required to externally heat the device (no internal device power dissipation) to the desired temperatures. Because each curve is relatively straight, only a few calibration points are required. In this

| Table | Ι |

|-------|---|

|-------|---|

| Device | v <sub>sg</sub> (v)* | dV <sub>SG</sub> /dT(mV/°C) | v <sub>DB</sub> (v)* | dV <sub>DB</sub> /dT(mV/°C) | R <sub>DS</sub> (Ω) <sup>*†</sup> | dR <sub>DS</sub> /dT(mΩ/°C) |

|--------|----------------------|-----------------------------|----------------------|-----------------------------|-----------------------------------|-----------------------------|

| 1      | 3.699                | 6.08                        | 0,567                | 2.29                        | 0.640                             | 5.92                        |

| 2      | 3.672                | 6.13                        | 0.573                | 2.28                        | 0.700                             | 6.42                        |

| 3      | 3.716                | 6.05                        | 0.557                | 2.31                        | 0.648                             | 5.96                        |

| 4      | 4.108                | 6.48                        | 0.568                | 2.30                        | 0.642                             | 5.92                        |

\* Measured at a temperature of 25°C.

+ Measured at a current of 0.5 A; to convert to measured terminal voltage, multiply each value by 0.5.

work, each calibration curve was generated in about 15 min.

#### Measured Temperature Comparisons

For production measurements, where a large number of "identical" devices are measured, the variability of the calibration curve from device to device is of interest. Ideally, all devices of a given type would have identical (or at least sufficiently similar) calibration curves so that each device would not have to be calibrated. If the slope of the calibration curve does not vary from device to device, then a single calibration point is sufficient, even if the parameter itself is variable. Samples of some calibration results for each TSEP for several devices of the same type (i.e., same manufacturer, part number, and date code) are shown in table I. The devices for this example are representative of those used in this study. Not unexpectedly, the most stable parameter is  $V_{DB}$ . Only a 2- or 3-percent variation in  $V_{DB}$ was usually observed between identical devices, with an even smaller variation observed in  $dV_{DB}/dT$ . Most devices exhibited a 2- or 3percent variability in both V<sub>SG</sub> and R<sub>DS</sub>(on), but a few devices (5 to 10 percent) exhibited a 10- to 20-percent difference from the norm. The variations in dV<sub>SG</sub>/dT and dR<sub>DS</sub>(on)/dT were comparable to but less than the variations in the parameters themselves. These results suggest that a "constant" variability with temperature for each parameter may be assumed for most devices of a given type, but care should be taken to detect "outliers" and perhaps a separate calibration performed for them if  $V_{SG}$  or  $R_{DS}(on)$  are used as the TSEP.

The results of temperature measurements on several devices for a number of operating conditions using the three TSEPs as well as the Infrared Microradiometer are given in table II. The IRM temperature is the peak temperature of the MOSFET semiconductor chip as determined by the IRM. It has been found that temperatures measured using  $V_{SG}$  as the TSEP are usually about 95 to 100 percent of the temperatures measured with  $V_{DB}$  or  $R_{DS}(on)$  as the TSEP are usually about 80 to 90 percent of the IRM. The TSEP are usually about 80 to 90 percent of the IRM result. The TSEP temperatures listed in table II are extrapolated results using a procedure described previously (5).

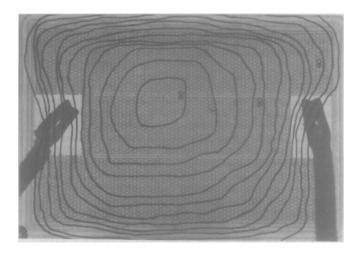

Whereas the TSEPs measure some "average" chip temperature, the IRM can be used to map the temperature distribution on the chip surface. The isotherms determined with the IRM for a particular device are superposed on a picture of the device in figure 4. The individual "cells" are visible as multisided "dots" on the transistor. The isotherms were determined from temperature measurements made in a matrix pattern at positions 25 µm apart (about equal to the spatial resolution of the IRM) on the device surface. These isotherms indicate a very uniform dissipation of power within the chip. This is in contrast to a bipolar device which usually shows more nonuniformity of temperature, with the hottest areas positioned about the emitter fingers or sometimes in a hot spot. Because the temperature of the MOSFET is relatively uniform, it is not surprising that

| Device | Operating<br>Conditions | J    | Cemperature     | Rise Above      | Case (°C)            |

|--------|-------------------------|------|-----------------|-----------------|----------------------|

| Number | $I_{D}(A)/V_{DS}(V)$    | IRM  | v <sub>sg</sub> | v <sub>DB</sub> | R <sub>DS</sub> (on) |

| 1      | 0.5/60                  | 33.5 | 31.0            | 28.8            | 25.7                 |

|        | 1.0/30                  | 33.5 | 31.0            | 28.8            | 26.6                 |

|        | 1.5/20                  | 33.5 | 31.0            | 27.8            | 28.0                 |

| 2      | 0.5/60                  | 38.0 | 35.0            | 36.5            | 33.4                 |

|        | 1.0/30                  | 38.0 | 35.0            | 36.1            | 32.2                 |

|        | 1.5/20                  | 38.0 | 35.0            | 36.1            | 33.2                 |

| 3      | 1.0/60                  | 80.0 | 80.3            | 70.7            | 69.2                 |

|        | 1.5/40                  | 80.0 | 80.3            | 70.4            | 68.6                 |

| 4      | 0.5/60                  | 37.0 | 36.8            | 36.1            | 33.0                 |

|        | 1.0/30                  | 37.0 | 36.8            | 36.1            | 35.0                 |

|        | 1.5/20                  | 37.0 | 36.8            | 35.0            | 35.0                 |

| 5      | 1.5/40                  | 73.0 | 69.0            | 62.0            | 56.0                 |

| 6      | 1.0/20                  | 34.3 | 31.4            | 28.1            | 28.2                 |

Table II

Figure 4. Isotherms determined using the IRM superposed on a picture of the device. The peak temperature isotherm is 98°C. Isotherms are shown for 2°C increments.

TSEPs can be used to measure temperatures between 80 to 100 percent of the peak temperature as demonstrated by the results in table II.

For four of the devices in table II, a number of different operating conditions are included, but the power dissipation for each  $(I_D \times V_{DS})$  is the same. The peak temperature as indicated by the IRM is the same for each condition. The temperature of the power MOSFET depends only upon the power level and not upon the combination of  $I_D$  and  $V_{DS}$  used to achieve that power. This is also in contrast to the bipolar power transistor for which the peak temperature depends strongly upon the operating conditions (6).

## GENERAL CONSIDERATIONS AND DISCUSSION

There are a number of "universal" difficulties encountered in measuring the temperature of a semiconductor device, whether it is a bipolar device or a MOSFET, a discrete power device or an integrated circuit. Some of these will be discussed in this section, and it will be noted how they impact the temperature measurements for power MOSFETs.

## Nonthermal Switching Transients

The term "nonthermal switching transient" refers to extraneous components of the measured TSEP waveform that are introduced as a result of switching from the heating to the measurement condition. That is, the measured TSEP has an extraneous, electrical component not present during calibration (no switching occurs during calibration). The TSEP must usually be measured with a resolution of at least 1 mV. Thus, even though one might consider the device to be fully "switched" for a typical circuit application, this is not the case for temperature measurement applications. Nonthermal switching transients are difficult to immediately discern, because the device is naturally cooling during the measurement phase (heating power has been removed) and the TSEP shows a natural thermal transient due to the temperature decay.

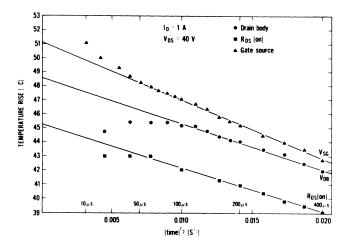

Example of waveforms obtained using each of the TSEPs during the measurement phase are shown in figure 5. It is expected that for times greater than t = 0 (the instant the device is switched from heating to measurement), the TSEP should indicate the device to be cooling. (In each display, the polarity is adjusted so that a rising voltage indicates cooling.) This is the case for  $V_{SG}$  for all t > 0. It is not immediately obvious, though, how much of the decay is due to nonthermal switching transients and how much is due to the cooling. For the case for which  $V_{DB}$  is the TSEP, it is obvious that for t <  $30 \ \mu$ s, nonthermal switching transients dominate the waveform. For these times,  $V_{\rm DB}$  indicates the device is heating, which is obviously incorrect. For t > 30  $\mu \, \text{s}$  ,  $V_{\rm DB}$  indicates the device is cooling, but how much of the effect is due to nonthermal switching transients is again not obvious from the oscilloscope trace.

Figure 5. Oscilloscope traces of the TSEP waveform during measurement. The TSEP voltages change with time because of nonthermal switching transients and because the device is cooling.

Figure 6. Temperature obtained using each TSEP. The linear region occurs when nonthermal transient have subsided. The temperatures in this region are extrapolated to t = 0 to obtain the measured temperature at the instant switching occurred for each TSEP.

MOSFET and is primarily limited by the magnitude of the gate capacitance with respect to the source, drain, and channel. On the other hand, the physical area of the drain-body diode is very large, being nearly equal to the total chip area. This means that the voltage dependent capacitance of the diode is intrinsically very large. In addition, the diode must be switched from a large reverse bias (smallest capacitance) to a forward bias (largest capacitance). Also, the carrier lifetime in the diode region is not closely controlled and is quite long. The end result is that it takes a long time (t > 30  $\mu$ s) to fully switch the diode.

For the case of  $R_{DS}(on)$ , there is also a time during which the device appears to be heating and thus the TSEP is obviously dominated by nonthermal switching transients. Again, it is not obvious when the nonthermal transients totally disappear. The time to fully switch  $R_{DS}(on)$  is somewhat longer than  $V_{SG}$  because the drain-body diode voltage is switched for the measurement.

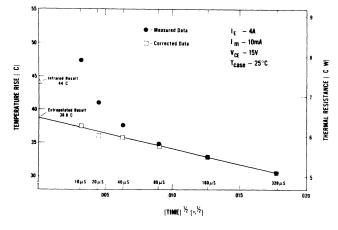

There are techniques for determining the presence of and correcting for nonthermal switching transients. It has been demonstrated that for the first 250 µs after switching, the device cools as if the flow of heat were strictly one-dimensional (4). This means that  $|\Delta T| \propto t^{1/2}$  where  $\Delta T$  is the temperature change from the instant switching occurred (t = 0) until time, t. If the measured temperature is plotted versus  $\sqrt{t}$ , a straight line relationship occurs if the nonthermal switching transients have subsided. Examples of such a plot for the temperature measured using each TSEP is shown in figure 6. The figure indicates that the linear region of the temperature versus square root of time can be used to extrapolate the results to t = 0 to estimate the temperature at the instant of switching. This procedure was used to obtain the results reported in this work.

## Magnetic Leads and the Skin Effect

The nature of the nonthermal switching transient was discussed above, but the physical cause was only briefly touched upon. A portion of the nonthermal switching transients is related to stored charge and the time required to charge and discharge device capacitances (both voltage dependent and voltage independent), to charge transit times, and to measurement circuit switching times. A significant and sometimes dominant portion of the nonthermal switching transients can result from the presence of the skin effect in magnetic leads (7). It is well known that high frequency alternating currents tend to be forced to the surface of a conductor. The "effective" conductor resistance due to this skin effect increases as the square root of the magnetic permeability of the conductor. Hermetic transistor packages typically have leads that are made of a material similar to kovar (~15 percent cobalt, 31 percent nickel, 54 percent iron) and are highly magnetic. When trying to rapidly switch from heating to measurement conditions, the increased lead resistance due to the high frequency components of the switching waveform can contribute significant nonthermal switching transient components to the TSEP waveform.

A technique has been developed for correcting for this effect (7) using a "dummy" package to replace the DUT. The "dummy" consists of a package with the leads used in the measurement internally shorted to one another such that a measurement of the TSEP voltage only measures the voltage across the leads. An example for a bipolar transistor of the "uncorrected" temperature and the temperature measured using the correction technique discussed above is shown in figure 7. The results may be in considerable error for the device in figure 7 if a

Figure 7. Example of temperature measurement using a TSEP for which compensation for the skin effect is made. The magnitude of the skin effect is determined using a dummy package with the TSEP measurement leads internally shorted to one another.

single measurement before 50  $\mu$ s is made or if extrapolation to t = 0 using measurements before 50  $\mu$ s is done unless compensation is made for the magnetic material skin effect.

#### Case Temperature Measurement Probe Location

The temperature at a specific location on the case of the transistor is maintained constant during the measurement of the device temperature. Because the temperature of the case is not uniform, it is important to be able to always measure the temperature at the same location on the case. The position chosen in this work is directly beneath the semiconductor chip on the outside surface of the case. Even though the device was placed on a temperature-controlled heat sink (the bottom surface was in contact with the heat sink with a thermal grease applied to the bottom surface), a significant temperature gradient can exist along the bottom surface while the device is dissipating power. The magnitude of the gradient depended upon the case material. For 60 W of power dissipation, a copper case had a temperature difference from an extreme edge of the bottom to a point on the bottom directly beneath the chip (a distance of about 2 cm) of about 2°C, an aluminum package had a difference of about 3°C, and a kovar or steel package, a temperature difference of about 6°C. Because most packages are made of kovar or of a similar material, it is very important to measure the temperature each time at the same location on the case.

#### CONCLUSIONS

Each of the three TSEPs investigated appear to be suitable for measuring the temperature of a power MOSFET device. The simplest circuit is the one using  $V_{SG}$  as the TSEP, which requires a single electronic switch, while the other two circuits require two electronic switches. In addition, the  $V_{SG}$  circuit is configured identically to the bipolar transistor with the bipolar transistor emitter-base-collector being replaced by the MOSFET source-gate-drain (8). The most stable calibration curve on the other hand is that for  $V_{\rm DB}$  which makes  $V_{\rm DB}$  perhaps more suited as a TSEP when a very large number of devices are to be measured. The most accurate TSEP, i.e., the one which indicates a temperature most near the peak temperature, is  $V_{\rm SG}.$  Also,  $V_{\rm SG}$  is typically the most temperature sensitive of the parameters, varying by about -6 mV/°C. Although R<sub>DS</sub>(on) is a suitable parameter for measuring temperature, there does not appear to be any particular circumstances for which it is superior to V<sub>SG</sub> or V<sub>DB</sub>.

Infrared surface temperature profiles show the temperature of the power MOSFET to be relatively

uniform, and the peak temperature as determined by the IRM is not a function of operating conditions; i.e., the peak temperature for a given power dissipation does not depend upon the drain-currentdrain voltage combinations used to obtain that power. These results are in sharp contrast to what is usually observed for bipolar transistors.

Finally, a number of universal temperature measurement difficulties have been discussed. Power MOSFET transistors are as susceptible to these difficulties as are power bipolar transistors.

#### REFERENCES

- P. E. Gray, D. DeWitt, A. R. Boothroyd, and J. F. Gibbons, "Physical Electronics and Circuit Models of Transistors", SEEC Series, Volume 2 (John Wiley and Sons, New York, New York, 1964), pp 47-50.

- (2) S. C. Sun and J. D. Plummer, "Modeling of the On-Resistance of LDMOS, VDMOS and VMOS Power Transistor", IEEE Trans. Electron Devices, ED-27, pp 356-367; 1980.

- (3) P. Norton and J. Brandt, "Temperature Coefficient of Resistance for p- and n-Type Silicon", Solid State Electronics, 21, pp 969-974; 1978.

- S. Rubin and F. F. Oettinger, "Semiconductor Measurement Technology: Thermal Resistance Measurements on Power Transistors", NBS Special Publication 400-14; 1979.

- (5) D. L. Blackburn and F. F. Oettinger, "Transient Thermal Response Measurements of Power Transistors", PESC '74 Record, IEEE Power Electronics Specialists Conference, Murray Hill, New Jersey, pp 140-148; June, 1974.

- (6) F. F. Oettinger, D. L. Blackburn, and S. Rubin, "Thermal Characterization of Power Transistors", IEEE Trans. Electron Devices, ED-23, pp 831-838; Aug, 1976.

- (7) D. W. Berning and D. L. Blackburn, "The Effect of Magnetic Package Leads on the Measurement of Thermal Resistance of Semiconductor Devices", IEEE Trans. Electron Devices, ED-28, pp 609-611; May, 1981.

- (8) Thermal Resistance Measurements of Conduction Cooled Power Transistor, EIA Recommended Standard RS-313-B (Revision of RS-313-A), October 1975 (Electronics Industries Association, 2001 Eye Street, NW, Washington, DC 20006).